Изобретение относится к цифровой электроизмерительной технике и может быть использовано в хроматографах и других цифровых измерительных приборах, а также в измерительных системах.

Известен аналого-цифровой преобразователь, состоящий из источника образцового напряжения, цифроаналогового преобразователя, усилителя разности, вспомогательного аналого-цифрового преобразователя и блока управления, причем входом всего аналого-цифрового преобразователя является первый вход усилителя разности, выход которого соединен с входом вспомогательного аналого-цифрового преобразователя, выход цифроаналогового преобразователя соединен с вторым входом усилителя разности, выход источника образцового напряжения соединен с аналоговым входом цифроаналогового преобразователя [1] .

Недостатком данного устройства является невысокая точность.

Известно устройство аналого-цифрового преобразователя, содержащее усилитель разности, первый вход которого является входной шиной, выход соединен с входом аналого-цифрового преобразователя, выходы которого соединены с соответствующими первыми входами первого сумматора, выходы которого подключены к информационным входам первого регистра, второй регистр, выходы которого соединены с вторым входом первого сумматора и с соответствующими цифровыми информационными входами цифроаналогового преобразователя, аналоговый вход которого подключен к выходу источника образцового напряжения, а выход - к второму входу усилителя разности, блок управления, первый, второй, третий и четвертый выходы которого соединены соответственно с входом управления аналого-цифрового преобразователя, входами записи первого и второго регистров и входом сброса второго регистра, и второй сумматор [2] .

Недостатком данного устройства является достаточно высокая статическая составляющая погрешности, так как отсутствуют цифроаналоговые преобразователи в микроисполнении с числом разрядов не менее 19 бит и погрешностью дифференциальной линейности не более 0,0002% . На основе микросхемы малоразрядного цифроаналогового преобразователя типа У2ПА2091, который может быть заключен, например, по схеме [3] , можно построить цифроаналоговый преобразователь с относительно малой погрешностью линейности. Основную долю в состав этой погрешности вносит аналоговый усреднитель, построенный на базе аналогового запоминающего устройства: из-за ограниченного времени хранения с требуемой точностью и абсорбционных явлений в конденсаторах аналоговых запоминающих устройств. Кроме того, наличие аналогового усреднителя увеличивает динамическую погрешность аналого-цифрового преобразователя, связанную с изменением входного сигнала. Между тем в ряде применений, например при хроматографическом анализе газовой смеси, требуются аналого-цифровые преобразователи с разрешающей способностью не менее 20 бит и с погрешностью дифференциальной линейности не более 0,0001% при скорости изменения входного сигнала до 2 В/с.

Целью изобретения является повышение точности аналого-цифрового преобразования.

Цель достигается тем, что в устройстве аналого-цифрового преобразования, содержащем усилитель разности, первый вход которого является входной шиной, выход соединен с входом аналого-цифрового преобразователя, выходы которого соединены с соответствующими первыми входами первого сумматора, выходы которого подключены к информационным входам первого регистра, второй регистр, выходы которого соединены с вторым входом первого сумматора и с соответствующими цифровыми информационными входами цифроаналогового преобразователя, аналоговый вход которого подключен к выходу источника образцового напряжения, а выход - к второму входу усилителя разности, блок управления, первый, второй, третий и четвертый выходы которого соединены соответственно с входом управления аналого-цифрового преобразователя, входами записи первого и второго регистров и входом сброса второго регистра, и второй сумматор, дополнительно соединены выходы первого сумматора с соответствующими информационными входами второго регистра, выходы которого подключены к первым входам второго сумматора, вторые входы которого соединены с выходами первого регистра, а выходы являются выходной шиной, при этом пятый выход блока управления соединен с цифровым управляющим входом цифроаналогового преобразователя, при этом цифроаналоговый преобразователь выполнен на преобразователе напряжение - ток, вход которого является аналоговым входом преобразователя, n делителях тока, n переключателях и n-разрядных ключах, информационные входы которых соединены с первыми выходами соответствующих переключателей, входы управления являются соответствующими цифровыми информационными входами преобразователя, первые выходы объединены и являются выходом преобразователя, а вторые выходы объединены и подключены к шине нулевого потенциала, выход преобразователя напряжение - ток соединен с входами первого делителя тока вход i-го из остальных делителей тока соединен с вторым выходом (i-1)-го переключателя, входы управления переключателей объединены и являются цифровым управляющим входом преобразователя, а их первые и вторые информационные входы соединены с одноименными выходами соответствующих делителей тока, при этом второй выход n-го переключателя является шиной нулевого потенциала.

В отличие от прототипа в предлагаемом решении имеются новые признаки: выходы первого сумматора соединены с соответствующими информационными входами второго регистра, выходы которого подключены к первым входам второго сумматора, вторые входы которого соединены с выходами первого регистра, а выходы являются выходной шиной, при этом пятый выход блока управления соединен с цифровым управляющим входом цифроаналогового преобразователя, а цифроаналоговый преобразователь выполнен на преобразователе напряжение - ток, вход которого является аналоговым входом преобразователя, n делителях тока, n переключателях и n-разрядных ключах, информационные входы которых соединены с первыми выходами соответствующих переключателей, входы управления являются соответствующими цифровыми информационными входами преобразователя, первые выходы объединены и являются выходом преобразователя, а вторые выходы объединены и подключены к шине нулевого потенциала, выход преобразователя напряжение - ток соединен с входами первого делителя тока, вход i-го из остальных делителей тока соединен с вторым выходом (i-1)-го переключателя, входы управления переключателей объединены и являются цифровым управляющим входом преобразователя, а их первые и вторые информационные входы соединены с одноименными выходами соответствующих делителей тока, при этом второй выход n-го переключателя является шиной нулевого потенциала.

Положительный эффект достигается за счет того, что при коммутационном инвертировании выходного сигнала цифроаналогового преобразователя, выполненного на основе делителей тока пополам, переключателей тока и разрядных ключей, а также при подключении выходов первого сумматора к соответствующим информационным входам второго регистра, выходы которого подключены к первым входам второго сумматора, вторые входы которого соединены с выходами первого регистра, а выходы являются выходной шиной, при этом пятый выход блока управления соединен с цифровым управляющим входом цифроаналогового преобразователя, цифровым усреднением удается скомпенсировать погрешность дифференциальной линейности цифроаналогового преобразователя и тем самым значительно повысить линейность характеристики преобразования устройства.

Сравнение заявляемого решения не только с прототипом, но и с другими техническими решениями в данной области техники не позволило выявить в них признаки, аналогичные заявляемому решению, что позволяет сделать вывод о соответствии критерию "существенные отличия".

На фиг. 1 представлена схема предлагаемого устройства (УПЦП), содержащая источник 1 образцового напряжения, цифроаналоговый преобразователь (ЦАП) 2, усилитель 3 разности (УР), аналого-цифровой преобразователь (АЦП) 4, блок 5 управления (БУ), первый сумматор (СМ1) 6, первый регистр 7 (РГГ1), второй регистр (РГ2) 8, второй сумматор (СМ2) 9.

Элементы схемы соединены следующим образом. Входом УАЦП является первый вход блока 3, выход блока 1 соединен с аналоговым входом блока 2, цифровой управляющий вход управления последнего подключен к пятому выходу блока 5, первый выход которого соединен с входом управления блока 4, выход блока 2 соединен с вторым входом блока 3, выход блока 3 соединен с входом блока 4, выходы которого соединены с соответствующими первыми входами блока 6, выходы которого соединены с информационными входами блоков 7 и 8, выход блока 7 подключен к второму входу блока 9, первый вход которого соединен с выходом блока 8, вторыми входами блока 6 и цифровыми информационными входами блока 2, выход блока 9 является выходной шиной УАЦП, вход записи блока 7 соединен с вторым выходом блока 5, вход записи блока 8 соединен с четвертым выходом блока 5.

На фиг. 2 показана схема блока 2 (ЦАП). Схема содержит: 2.1 - преобразователь напряжение-ток, 2.2.1 - 2.2. n - разрядные ключи 2.3.1 - 2.3. n - переключатели токов, 2.4.1 - 2.4. n - делители токов пополам, где n - число разрядов ЦАП.

Элементы схемы соединены следующим образом. Аналоговый вход блока 2 соединен с входом блока 2.1, выход которого соединен с входом блока 2.4.1, выходы блоков 2.4.1 - 2.4. n соединены с входами соответствующих блоков 2.3.1 - 2.3. n, первые выходы которых соединены с входами соответствующих блоков 2.2.1 - 2.2. n, вторые выходы которых соединены с входами последующих блоков 2.4.2 - 2.4. n, второй выход последнего переключателя тока соединен с шиной нулевого потенциала, входы управления блоков 2.3.1 - 2.3. n соединены между собой и являются цифровым входом управления блока 2, первые выходы блоков 2.2.1 - 2.2. n соединены между собой и являются выходом блока 2, входы управления блоков 2.2.1 - 2.2. n являются цифровыми информационными входами блока 2.

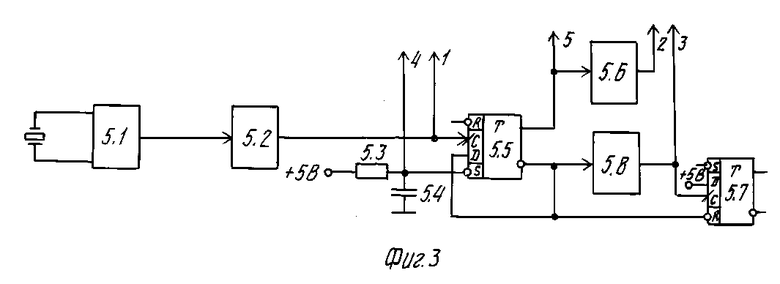

На фиг. 3 приведен вариант схемы блока 5 (БУ). Схема содержит: 5.1 - генератор тактовой частоты с кварцевым резонатором, 5.2, 5.6 - одновибраторы, 5.3 - резистор R1, 5.4 - конденсатор С1, 5.5, 5.7 - триггеры.

На фиг. 4 приведены временные диаграммы работы блока 5 (БУ). На диаграмме А - импульсы тактовой частоты блока 5.1, на диаграмме Б - команда пуска блока 4 (выход 1 блока 5), на диаграмме В - команда управления блоком 2 (выход 5 блока 5), на диаграмме Г - команда записи выходного кода блока 6 в блок 8 (выход 3 блока 5), на диаграмме Д - команда записи выходного кода блока 6 в блок 7 (выход 2 блока 5).

УАЦП работает следующим образом.

При включении питания +5 В происходит предварительная установка РГ2 (блок 8) и триггера (блок 5.5) с помощью интегрирующей цепочки R1C1 (блоки 5.3 и 5.4). При этом на цифровых информационных входах ЦАП (блок 2) устанавливается код Niнач.

Входное напряжение УАЦП (Uвх) поступает на первый вход УР (блок 3), при этом его выходное напряжение равно

UIвых = (Uвых - U1цап)К1н, где U'цап - значение выходного напряжения ЦАП (блок 2) до коммутационного инвертирования внутреннего состояния, соответствующее коду Niнач; К1н - номинальный коэффициент усиления УР (блок 3).

Напряжение U'вых преобразуется по команде (диаграмма Б, фиг. 5), от БУ (блок 5) с помощью АЦП (блок 4) в цифровой код N1

N1 = K1н К2н(Uвх - U'цап), где К2н - номинальный коэффициент преобразования АЦП (блок 5).

По команде (диаграмма Д, фиг. 5) от БУ (блок 5) происходит запись кода N1 в РГ1 (блок 7) и коммутационное инвертирование внутреннего состояния ЦАП (блок 2) (диаграмма Б, фиг. 6). При этом выходное напряжение УР (блок 3) становится равным

U"вых = (Uвх- U"цап)К1н, где U"цап - значение выходного напряжения ЦАП (блок 2) после коммутационного инвертирования внутреннего состояния, соответствующее коду Niнач.

По команде (диаграмма Б, фиг. 5) от БУ (блок 5) напряжение U"выхпреобразуется с помощью АЦП (блок 4) в цифровой код N2.

N2 = K1нК2н(Uвх - U"цап),

По команде (диаграмма Г, фиг. 5) от БУ (блок 5) происходит запись кода N2 в РГ2 (блок 8).

Коды N1 и N2, соответствующие напряжениям U'вых и U"вых, поступают на входы СМ1 (блок 6). При этом на выходе СМ1 (блок 6) имеем соответственно коды

N3' = Niнач + N1,

N3" = Niнач + N2.

При этом на цифровых входах ЦАП (блок 2) устанавливается код N3",который используется при следующем аналого-цифровом преобразовании входного сигнала.

На выходе СМ2 (блок 9) тем временем образуется результирующий код УАЦП

Nвых = (2Niнач + N1 + N2)/2.

Деление на два осуществляется отбрасыванием младшего значащего разряда кода Nвых.

Аналогично, результатом следующего АЦ преобразования уже будет код

N'вых = (2N3" + N4 + N5)/2, где N4 и N5 - выходные коды АЦП (блок 4) при очередном АЦ преобразовании. Перезапуск УАЦП осуществляется автоматически от блока 5.1 (диаграмма А, фиг. 4).

Достижение повышения точности в предлагаемом устройстве обеспечивается следующим образом.

Для входного кода ЦАП (блок 2) Niнач, полагая для простоты анализа K1н = 1, получим выражения для абсолютной погрешности ЦАП (блок 2), приведенной к входу УАЦП соответственно до и после коммутационного инвертирования внутреннего состояния ЦАП = Niнач К3н - U'цап, (1)

= Niнач К3н - U'цап, (1) = Niнач К3н - U"цап, (2) где К3Н - номинальный коэффициент преобразования ЦАП (блок 2).

= Niнач К3н - U"цап, (2) где К3Н - номинальный коэффициент преобразования ЦАП (блок 2).

Абсолютная погрешность АЦП (блок 4), приведенная к входу УАЦП соответственно до и после коммутационного инвертирования внутреннего состояния ЦАП при входном коде Niнач, равна = N1/K2н - U'вх, (3)

= N1/K2н - U'вх, (3) = N2/K2н - U"вх, (4) где U'вх и U"вх - значения входных напряжений АЦП (блок 4) соответственно до и после коммутационного инвертирования внутреннего состояния ЦАП при входном коде Niнач, причем

= N2/K2н - U"вх, (4) где U'вх и U"вх - значения входных напряжений АЦП (блок 4) соответственно до и после коммутационного инвертирования внутреннего состояния ЦАП при входном коде Niнач, причем

U'вх = Uвх - U'цап, (5)

U"вх = Uвх - U"цап. (6)

Абсолютная погрешность УАЦП по входу соответственно до и после коммутационного инвертирования внутреннего состояния ЦАП при входном коде Niнач равна = Niнач К3н + Ni/К2н- U'вх, (7)

= Niнач К3н + Ni/К2н- U'вх, (7) = Niнач К3н + N2/K2н- U"вх. (8)

= Niнач К3н + N2/K2н- U"вх. (8)

Решая систему уравнений (1)-(8), получим выражения для абсолютных погрешностей УАЦП по входу соответственно до и после коммутационного инвертирования внутреннего состояния ЦАП при входном коде Niнач =

=  +

+

=

=  +

+

Представим погрешности  и

и  " в виде

" в виде =

=  + δм2 Uцап' +

+ δм2 Uцап' +  +

+  (9)

(9) =

=  + δм2 Uцап" -

+ δм2 Uцап" -  +

+  (10) где

(10) где  иΔа2" - напряжения смещения нуля ЦАП соответственно до и после коммутационного инвертирования внутреннего состояния ЦАП при входном коде Niнач, δм2- относительная погрешность коэффициента преобразования ЦАП,

иΔа2" - напряжения смещения нуля ЦАП соответственно до и после коммутационного инвертирования внутреннего состояния ЦАП при входном коде Niнач, δм2- относительная погрешность коэффициента преобразования ЦАП,  - погрешность линейности ЦАП (блок 2), соответствующая входному коду Niнач.

- погрешность линейности ЦАП (блок 2), соответствующая входному коду Niнач.

После выполнения операции цифрового усреднения результатов аналого-цифрового преобразования напряжений U'вых и U"вых в соответствии с выражениями (9)-(10), поскольку погрешность  при коммутационном инвертировании внутреннего состояния ЦАП изменяет знак, получим погрешность, приведенную к входу УАЦП

при коммутационном инвертировании внутреннего состояния ЦАП изменяет знак, получим погрешность, приведенную к входу УАЦП  =

= + δм2 Uцап+

+ δм2 Uцап+ +

+ где

где  - остаточная погрешность линейности ЦАП, соответствующая входному коду Niнач, приведенная к входу УАЦП. Таким образом, скомпенсирована погрешность линейности ЦАП для точки Niнач диапазона преобразования до уровня

- остаточная погрешность линейности ЦАП, соответствующая входному коду Niнач, приведенная к входу УАЦП. Таким образом, скомпенсирована погрешность линейности ЦАП для точки Niнач диапазона преобразования до уровня  причем

причем <<

<<  л2.

л2.

При выборе значения (К1н К2н), равным 5000, а в качестве блока 4 - микросхему типа КР1108ПВ2А, погрешность  не превысит значения 3 мкВ, (0,00003% для номинального входного диапазона 10В). Выбрав в качестве блока 2 микросхемы типа У2ПА2091 и М2ПАЦ4171А, погрешность

не превысит значения 3 мкВ, (0,00003% для номинального входного диапазона 10В). Выбрав в качестве блока 2 микросхемы типа У2ПА2091 и М2ПАЦ4171А, погрешность  не превысит значения 7 мкВ (0,00007% ), в то время как типичное значение

не превысит значения 7 мкВ (0,00007% ), в то время как типичное значение  примерно равно 1 мВ (0,01% ). Следовательно, погрешность линейности УАЦП уменьшена на два порядка. Блоки схемы фиг. 3 можно реализовать на основе следующих микросхем: 5.1 - КР580ГФ24; 5.2, 5.6 и 5.8 - К555АГ3; 5.5 и 5.7 - К555ТМ2; Блоки 3 и 1 можно реализовать соответственно по схемам [4] и [5] , блоки 6 и 9 - на основе микросхем типа К555ИМ1, блоки 7 и 8 - на основе микросхем типа К155ИР13.

примерно равно 1 мВ (0,01% ). Следовательно, погрешность линейности УАЦП уменьшена на два порядка. Блоки схемы фиг. 3 можно реализовать на основе следующих микросхем: 5.1 - КР580ГФ24; 5.2, 5.6 и 5.8 - К555АГ3; 5.5 и 5.7 - К555ТМ2; Блоки 3 и 1 можно реализовать соответственно по схемам [4] и [5] , блоки 6 и 9 - на основе микросхем типа К555ИМ1, блоки 7 и 8 - на основе микросхем типа К155ИР13.

Указанные выше преимущества обеспечивают повышение точности УАЦП до 0,0001% . (56) 1. Бахтиаров Г. Д. , Малинин В. В. , Школин В. П. Аналого-цифровые преобразователи. М. : Советское радио, 1980, рис. 7.28, с. 204.

2. Авторское свидетельство СССР N 1490712, кл. Н 03 М 1/18, 1987.

3. Авторское свидетельство СССР N 1064453, кл. Н 03 К 13/02, 1985.

4. Бахтиаров Г. Д. , Малинин В. В. , Школин В. П. Аналого-цифровые преобразователи. М. : Советское радио, 1980, рис. 3.6-б, с. 52.

5. Бахтиаров Г. Д. , Малинин В. В. , Школин В. П. Аналого-цифровые преобразователи, М. : Советское радио, 1980, рис. 3.20-б, с. 71.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1989 |

|

SU1691962A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1989 |

|

SU1709526A1 |

| Устройство для вычисления массы нефти и нефтепродуктов в резервуарах | 1983 |

|

SU1117653A1 |

| СОСТАВНОЙ БЫСТРОДЕЙСТВУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2006 |

|

RU2311731C1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Преобразователь аналог-код | 1978 |

|

SU766001A1 |

| Аналого-цифровой преобразователь с автоматической коррекцией функции преобразования | 1988 |

|

SU1667246A1 |

| Аналого-цифровой преобразователь | 1990 |

|

SU1730722A2 |

| Аналого-цифровое устройство | 1981 |

|

SU1018239A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1336237A1 |

Изобретение относится к цифровой электроизмерительной технике и может быть использовано в хроматографах и других цифровых измерительных приборах, а также в измерительных системах. Целью изобретения является повышение точности устройства аналого-цифрового преобразователя. Цель достигается тем, что в устройстве аналого-цифрового преобразования, содержащем источник образцового напряжения, цифроаналоговый преобразователь, усилитель разности, аналого-цифровой преобразователь, сумматоры, регистры и блок управления, выходы регистров подключены к входам второго сумматора, выход первого сумматора - к информационным входам второго регистра, а в качестве цифроаналогового преобразователя (ЦАП) используется схема на преобразователе напряжение - ток, делителях тока, разрядных ключах и переключателях, управляющие входы которых объединены и являются цифровым управляющим входом ЦАП, который подключен к одному из выходов блока управления. Благодаря этому удается скомпенсировать погрешности дифференциальной и интегральной линейности цифроаналогового преобразователя без увеличения динамической погрешности. 1 з. п. ф-лы, 4 ил.

Авторы

Даты

1994-05-30—Публикация

1991-06-28—Подача