Изобретение относится к микроэлектронике, в частности к технологии полупроводниковых приборов на эпитаксиальных структурах арсенида галлия.

Известен метод изготовления микросхем с поликремниевыми резисторами (Патент США N 4256515, авторское свидетельство СССР N 1195862, авторское свидетельство СССР N 1819070)

Известны способы изготовления микросхем с резисторами из аморфного кремния (Патент RU 2170474).

Прототипом предлагаемого способа изготовления является технологический процесс, реализованный в ОАО «ОКБ-Планета», г. Великий Новгород, в технологическом маршруте 7610849.10200.00254, при котором интегральные элементы микросхемы формируются на (в) эпитаксиальных слоях GaAs при помощи протонирования (здесь и далее протонирование - операция ионного легирования при помощи ионов водорода и протонов) и жидкостного травления эпитаксиальных слоев арсенида галлия.

Прототип содержит следующие основные технологические операции: формирование омических контактов; создание рабочих областей интегральных элементов микросхемы при помощи операций протонирования и жидкостного травления; пассивацию поверхности микросхемы диэлектриком; формирование верхнего слоя металлизации.

Недостатком такого способа изготовления является то, что во время жидкостного травления разные области GaAs травятся с разной скоростью в зависимости от их размера, количества и площади омических контактов, гальванически связанных с областью травления и окружающих эту область. (Т.С. Петрова, «Влияние конструктивных и технологических особенностей на статические параметры МИС на GaAs на основе ПТШ с углубленным затвором». Доклады ТУСУPa, No. 1 (19), часть 1, 2009). Расстояние от омических контактов до травящейся области так же влияет на скорость травления.

В результате для разных интегральных элементов получаем разную толщину эпитаксиального n-слоя, в котором формируются рабочие области интегральных элементов, разная толщина слоя приводит к их разному слоевому сопротивлению. Как следствие, получаем большой технологический разброс величин характеризующих эти элементы, особенно для интегральных элементов с разной топологией. Например, для разных транзисторов полученные значения токов насыщения будут в различной степени отличаться от заданных, а для разных резисторов значения сопротивлений будут по-разному отклоняться от номиналов. Получается, что при подгонке с помощью жидкостного травления параметра одного элемента, другой элемент либо остается «недотравленным», либо «перетравливается». Критичным для многих типов микросхем является и тот факт, что при неравномерном травлении нарушается соотношение величин разных интегральных элементов, заданное при проектировании схемы. Это требует от разработчиков принятия специальных мер, например дополнительной выборочной подгонки сопротивлений различными способами, специальной корректировки топологии и т.д.

Техническая проблема, решаемая изобретением, - минимизация технологического разброса параметров интегральных элементов микросхемы, которые формируются при помощи жидкостного травления в эпитаксиальных структурах арсенида галлия.

Техническим результатом предлагаемого способа изготовления интегральных элементов микросхемы на эпитаксиальных структурах арсенида галлия является обеспечение равенства слоевых сопротивлений для различных интегральных элементов, рабочая область которых формируется в эпитаксиальных структурах арсенида галлия при помощи жидкостного травления.

Технический результат достигается за счет того, что в способе изготовления интегральных элементов микросхем на эпитаксиальных структурах арсенида галлия, включающем формирование омических контактов, создание рабочих областей интегральных элементов микросхемы при помощи операций протонирования и жидкостного травления, пассивацию поверхности микросхемы диэлектриком и формирование верхнего слоя металлизации, причем создание рабочих областей интегральных элементов микросхемы происходит в два этапа, на первом этапе, при помощи первого протонирования, формируются топологически одинаковые для интегральных элементов микросхемы области, которые травятся жидкостным травлением до достижения необходимого слоевого сопротивления эпитаксиального n-слоя, при этом размер и топология этих областей определяются типом интегральных элементов микросхемы, номинальными значениями их параметров и топологией микросхемы в целом, а на втором этапе, при помощи второго протонирования, в полученных областях формируются рабочие области интегральных элементов микросхемы, разные для различных интегральных элементов.

Введение двух этапов при создании рабочих областей интегральных элементов микросхемы делает возможным на первом этапе оперировать с топологически одинаковыми областями, назовем такие области «заготовками для изготовления рабочих областей интегральных элементов» или просто «заготовками», что в свою очередь позволяет, при жидкостном травлении, выровнять скорость травления заготовок для различных интегральных элементов конкретной микросхемы. Что обеспечивает равенство слоевых сопротивлений в рабочих областях интегральных элементов. Из этого можно сделать вывод о том, что технический результат достигнут полностью.

Далее в полученных заготовках, которые уже имеют одинаковое слоевое сопротивление, создается, при помощи второго протонирования, необходимая планарная форма рабочих областей интегральных элементов микросхемы, разная для различных интегральных элементов.

Равенство слоевых сопротивлений для различных интегральных элементов существенно снижает разброс параметров и обеспечивает соотношение значений параметров различных интегральных элементов в пределах конкретной микросхемы близким к заданному при проектировании. Таким образом решается поставленная техническая проблема.

Предлагаемый способ изготовления применим как для отдельных типов интегральных элементов микросхемы, т.е. таким способом изготавливаются только резисторы, или только транзисторы, а остальные элементы изготавливаются другими - «обычными» способами, так и для совместного изготовления «разнотипных» интегральных элементов микросхемы, но формирующихся в эпитаксиальных структурах арсенида галлия при помощи жидкостного травления, например - из одинаковых заготовок формируются как, транзисторы, так и резисторы, а, возможно, и другие интегральные элементы микросхемы, которые формируются в эпитаксиальных структурах арсенида галлия при помощи жидкостного травления. При этом во всех случаях возможно параллельное формирование любых других интегральных элементов.

Пример

Предлагаемый способ изготовления интегральных элементов микросхем на эпитаксиальных структурах арсенида галлия проиллюстрирован на примере изготовления интегральных резисторов в составе монолитной интегральной схемы аттенюатора, где разброс и соотношение величин электрических сопротивлений резисторов играет определяющую роль.

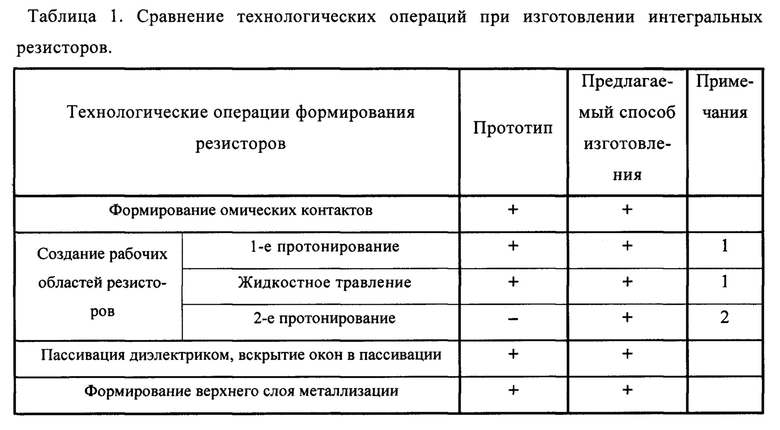

В таблице 1 приведено сравнение последовательности технологических операций при изготовлении полупроводниковых резисторов формируемых в эпитаксиальных слоях арсенида галлия в составе микросхемы для прототипа и для предлагаемого способа.

Примечания:

1 - для предлагаемого способа изготовления относится к этапу создания заготовок интегральных резисторов, для прототипа относится к созданию рабочих областей резисторов

2 - для предлагаемого способа изготовления относится к этапу формирования рабочих областей резисторов, для прототипа отсутствует.

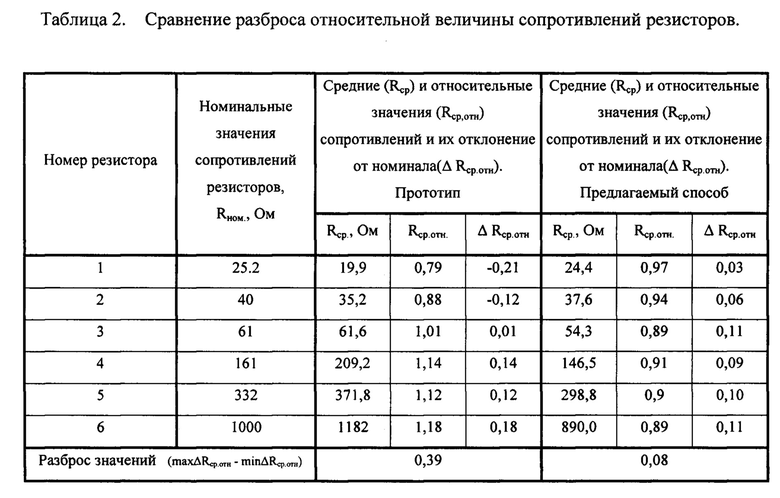

В таблице 2 представлены сравнительные результаты изготовления интегральных резисторов по прототипу и в соответствии с предлагаемым способом изготовления.

Для того чтобы сравнить результаты по всем группам резисторов, от «низкоомных» до «высокоомных», сравниваются не абсолютные, а относительные значения их сопротивлений, т.е. средние реальные значения сопротивлений, отнесенные к номинальным, очевидно, что для относительных значений номиналом является единица.

Для сравнения результатов выбрана величина технологического разброса значений электрического сопротивления резисторов, определяемая как разница между максимальной и минимальной величиной отклонения относительных значений от единицы, т.е. от номинального значения.

Из таблицы видно, что разброс относительной величины сопротивлений для прототипа составляет 0.39, а при предлагаемом способе изготовления интегральных элементов микросхемы на эпитаксиальных структурах арсенида галлия - 0.08, что почти в 5 (4,875) раз меньше, и это подтверждает решение изобретением поставленной технической проблемы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ изготовления электрически изолированных резисторов микросхем | 2017 |

|

RU2648295C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВЫХ ОГРАНИЧИТЕЛЬНЫХ ДИОДОВ СВЕРХВЫСОКОЧАСТОТНОГО ДИАПАЗОНА ГРУППОВЫМ МЕТОДОМ | 2011 |

|

RU2452057C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ АРСЕНИД-ГАЛЛИЕВОЙ ИНТЕГРАЛЬНОЙ СХЕМЫ | 1987 |

|

SU1491262A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МОЩНЫХ ТРАНЗИСТОРОВ СВЧ | 2011 |

|

RU2463683C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВОГО ПРИБОРА С УПРАВЛЯЮЩИМ ЭЛЕКТРОДОМ СУБМИКРОННОЙ ДЛИНЫ | 1991 |

|

RU2031481C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МОЩНЫХ ТРАНЗИСТОРОВ СВЧ | 2005 |

|

RU2285976C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛЕВОГО ТРАНЗИСТОРА С БАРЬЕРОМ ШОТТКИ | 2007 |

|

RU2349987C1 |

| Способ изготовления мощного полевого транзистора СВЧ на полупроводниковой гетероструктуре на основе нитрида галлия | 2022 |

|

RU2787550C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ЧИПОВ НАНОГЕТЕРОСТРУКТУРЫ И ТРАВИТЕЛЬ | 2012 |

|

RU2485628C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ФОТОЭЛЕМЕНТА НА ОСНОВЕ GaAs | 2015 |

|

RU2607734C1 |

Изобретение относится к микроэлектронике, в частности к технологии полупроводниковых приборов на эпитаксиальных структурах арсенида галлия. Техническим результатом предлагаемого способа изготовления интегральных элементов микросхемы на эпитаксиальных структурах арсенида галлия является обеспечение равенства слоевых сопротивлений для различных интегральных элементов, рабочая область которых формируется в эпитаксиальных структурах арсенида галлия при помощи жидкостного травления. Это позволяет решить поставленную техническую проблему - минимизацию технологического разброса параметров интегральных элементов изготавливаемой микросхемы. В способе изготовления интегральных элементов микросхем на эпитаксиальных структурах арсенида галлия, включающем формирование омических контактов, создание рабочих областей интегральных элементов микросхемы при помощи операций протонирования и жидкостного травления, пассивацию поверхности микросхемы диэлектриком и формирование верхнего слоя металлизации, создание рабочих областей интегральных элементов микросхемы происходит в два этапа. На первом этапе при помощи первого протонирования формируются топологически одинаковые для интегральных элементов конкретной микросхемы области, которые травятся жидкостным травлением до достижения необходимого слоевого сопротивления эпитаксиального n-слоя. На втором этапе при помощи второго протонирования в полученных областях формируется необходимая планарная форма рабочих областей интегральных элементов микросхемы, разная для различных интегральных элементов. Полученное при таком способе изготовления равенство слоевых сопротивлений в тех областях эпитаксиальной структуры, где формируются интегральные элементы микросхемы, приводит к минимальному разбросу параметров этих интегральных элементов. 2 табл.

Способ изготовления интегральных элементов микросхем на эпитаксиальных структурах арсенида галлия, включающий формирование омических контактов, создание рабочих областей интегральных элементов микросхемы при помощи операций протонирования и жидкостного травления, пассивацию поверхности микросхемы диэлектриком и формирование верхнего слоя металлизации, отличающийся тем, что создание рабочих областей интегральных элементов микросхемы происходит в два этапа, на первом этапе при помощи первого протонирования формируются топологически одинаковые для интегральных элементов конкретной микросхемы области, которые травятся жидкостным травлением до достижения необходимого слоевого сопротивления эпитаксиального n-слоя, при этом размер и топология этих областей определяются типом интегральных элементов микросхемы, номинальными значениями их параметров и топологией микросхемы в целом, а на втором этапе при помощи второго протонирования в полученных областях формируются рабочие области интегральных элементов микросхемы, разные для различных интегральных элементов.

| СПОСОБ ИЗГОТОВЛЕНИЯ АРСЕНИД-ГАЛЛИЕВОЙ ИНТЕГРАЛЬНОЙ СХЕМЫ | 1987 |

|

SU1491262A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВОЙ СТРУКТУРЫ | 2010 |

|

RU2445722C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВЫХ ПРИБОРОВ | 2006 |

|

RU2303316C1 |

| СПОСОБ ПОЛУЧЕНИЯ ЛОКАЛЬНЫХ ЭПИТАКСИАЛЬНЫХ СТРУКТУР | 1985 |

|

SU1316488A1 |

| US 20150357229 A1, 10.12.2015 | |||

| US 20160329398 A1, 10.11.2016 | |||

| US 5418375 A, 23.05.1995. | |||

Авторы

Даты

2018-08-29—Публикация

2017-12-01—Подача