ОБЛАСТЬ ТЕХНИКИ ИЗОБРЕТЕНИЯ

[0001] Настоящее изобретение относится к области техники воспроизведения изображений, а в частности, к пиксельному блоку с тонкопленочным транзистором из низкотемпературного поликристаллического кремния и способу его изготовления.

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ ИЗОБРЕТЕНИЯ

[0002] Процедура формирования тонкопленочного транзистора (TFT - Thin-Film Transistor) из низкотемпературного поликристаллического кремния (LTPS - Low Temperature Poly-silicon) в соответствии с предшествующим уровнем техники состоит в следующем: сначала осаждают буферный слой, а затем формируют слой полупроводниковой структуры. Кроме того, другие элементы пиксельного блока с тонкопленочным транзистором из низкотемпературного поликристаллического кремния, такие как изоляционный слой, затвор и т.д., формируют на слое полупроводниковой структуры.

[0003] В соответствии с предшествующим уровнем техники слой полупроводниковой структуры формируют на буферном слое пиксельного блока с тонкопленочным транзистором из низкотемпературного поликристаллического кремния, в результате этого слой полупроводниковой структуры является выпуклым вверх относительно буферного слоя, и формируемый затем изоляционный слой образует ступенчатые выпуклые структуры на обоих краях слоя полупроводниковой структуры. Так, зазоры между затвором и слоем полупроводниковой структуры, формируемом на буферном слое, еще не приводят к возникновению побочного эффекта. Но с другой стороны, существуют ступенчатые структуры буферного слоя, и в процессе передачи сигналы становятся нестабильными и тем самым влияют на электрические свойства пиксельного блока с тонкопленочным транзистором из низкотемпературного поликристаллического кремния.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

[0004] Цель настоящего изобретения состоит в том, чтобы предложить пиксельный блок с тонкопленочным транзистором из низкотемпературного поликристаллического кремния, позволяющий уменьшить побочный эффект и улучшить его электрические свойства.

[0005] Для достижения вышеуказанных целей в настоящем изобретении используется следующее техническое решение: предложен способ изготовления пиксельного блока с тонкопленочным транзистором из низкотемпературного поликристаллического кремния, причем способ содержит этапы, на которых: подготавливают подложку и формируют буферный слой на подложке; на буферном слое формируют слой полупроводниковой структуры и первый изоляционный слой, имеющие одинаковую толщину, и с расположением их в одном и том же слое; причем этап формирования буферного слоя на подложке включает этап, когда последовательно формируют слой нитрида кремния и слой оксида кремния на подложке; этап формирования на буферном слое слоя полупроводниковой структуры и первого изоляционного слоя, имеющих одинаковую толщину, и с расположением их в одном и том же слое включает этапы, на которых формируют аморфный кремниевый слой на буферном слое и осуществляют процесс кристаллизации аморфного кремниевого слоя для формирования поликристаллического кремниевого слоя; структурируют аморфный кремниевый слой с помощью первого процесса фотолитографии для формирования слоя полупроводниковой структуры; формируют слой нитрида кремния на слое полупроводниковой структуры и буферном слое там, где слой полупроводниковой структуры не сформирован, при этом толщина слоя нитрида кремния совпадает с толщиной слоя полупроводниковой структуры; наносят негативный фоторезист на слой нитрида кремния в местах, не совпадающих с расположением слоя полупроводниковой структуры; структурируют слой нитрида кремния с помощью второго процесса фотолитографии; затем травят слой нитрида кремния на слое полупроводниковой структуры, чтобы удалить травлением слой нитрида кремния со слоя полупроводниковой структуры, для формирования первого изоляционного слоя, при этом толщина первого изоляционного слоя совпадает с толщиной слоя полупроводниковой структуры на обоих краях слоя полупроводниковой структуры.

[0006] Предлагаемый способ также включает этапы, на которых формируют нормальную область и сильнолегированные области с двух сторон нормальной области на слое полупроводниковой структуры с помощью третьего процесса фотолитографии и первого процесса легирования; затем формируют слаболегированную область между нормальной областью и сильнолегированными областями на слое полупроводниковой структуры с помощью четвертого процесса фотолитографии и второго процесса легирования.

[0007] Предлагаемый способ также включает этапы, на которых формируют второй изоляционный слой на слое полупроводниковой структуры и первом изоляционном слое; формируют слой затвора на втором изоляционном слое и структурируют слой затвора с помощью пятого процесса фотолитографии для формирования затвора; формируют третий изоляционный слой на затворе; формируют исток и сток блока тонкопленочного транзистора из низкотемпературного поликристаллического кремния на третьем изоляционном слое, причем исток и сток подсоединяют к слою полупроводниковой структуры, используя первые сквозные отверстия, выполненные во втором изоляционном слое и третьем изоляционном слое, соответственно; формируют четвертый изоляционный слой поверх истока и стока, формируют пиксельный электрод на четвертом изоляционном слое, который электрически подсоединяют к истоку или стоку, используя второе сквозное отверстие, выполненное в четвертом изоляционном слое.

[0008] Далее способ включает этапы, на которых формируют пятый изоляционный слой между четвертым изоляционным слоем и истоком и стоком; затем формируют общий электрод между пятым изоляционным слоем и четвертым изоляционным слоем, используемый вместе с пиксельным электродом для формирования жидкокристаллического конденсатора.

[0009] Для достижения вышеуказанных целей в настоящем изобретении используется еще одно техническое решение: предложен способ изготовления пиксельного блока с тонкопленочным транзистором из низкотемпературного поликристаллического кремния, причем способ включает этапы, на которых подготавливают подложку и формируют буферный слой на подложке; на буферном слое формируют слой полупроводниковой структуры и первый изоляционный слой, имеющие одинаковую толщину, и с расположением их в одном и том же слое.

[0010] Этап формирования буферного слоя на подложке включает этапы, когда последовательно формируют слой нитрида кремния и слой оксида кремния на подложке.

[0011] Этап формирования на буферном слое слоя полупроводниковой структуры и первого изоляционного слоя, имеющих одинаковую толщину, и с расположением их в одном и том же слое включает этапы, на которых формируют аморфный кремниевый слой на буферном слое и осуществляют процесс кристаллизации аморфного кремниевого слоя для формирования поликристаллического кремниевого слоя; структурируют аморфный кремниевый слой с помощью первого процесса фотолитографии для формирования слоя полупроводниковой структуры; формируют слой нитрида кремния на слое полупроводниковой структуры и буферном слое там, где слой полупроводниковой структуры не сформирован, при этом толщина слоя нитрида кремния совпадает с толщиной слоя полупроводниковой структуры; наносят негативный фоторезист на слой нитрида кремния в местах, не совпадающих с расположением слоя полупроводниковой структуры; структурируют слой нитрида кремния с помощью второго процесса фотолитографии; затем травят слой нитрида кремния на слое полупроводниковой структуры, чтобы удалить травлением слой нитрида кремния со слоя полупроводниковой структуры, для формирования первого изоляционного слоя, при этом толщина первого изоляционного слоя совпадает с толщиной слоя полупроводниковой структуры на обоих краях слоя полупроводниковой структуры.

[0012] Предлагаемый способ также включает этапы, на которых формируют нормальную область и сильнолегированные области с двух сторон нормальной области на слое полупроводниковой структуры с помощью третьего процесса фотолитографии и первого процесса легирования; затем формируют слаболегированную область между нормальной областью и сильнолегированными областями на слое полупроводниковой структуры с помощью четвертого процесса фотолитографии и второго процесса легирования.

[0013] Предлагаемый способ также включает этапы, на которых формируют второй изоляционный слой на слое полупроводниковой структуры и первом изоляционном слое; формируют слой затвора на втором изоляционном слое и структурируют слой затвора с помощью пятого процесса фотолитографии для формирования затвора; формируют третий изоляционный слой на затворе; формируют исток и сток блока тонкопленочного транзистора из низкотемпературного поликристаллического кремния на третьем изоляционном слое, причем исток и сток подсоединяют к слою полупроводниковой структуры, используя первые сквозные отверстия, выполненные во втором изоляционном слое и третьем изоляционном слое, соответственно; формируют четвертый изоляционный слой на истоке и стоке, формируют пиксельный электрод на четвертом изоляционном слое, который электрически подсоединяют к истоку или стоку, используя второе сквозное отверстие, выполненное в четвертом изоляционном слое.

[0014] Далее способ включает этапы, на которых формируют пятый изоляционный слой между четвертым изоляционным слоем и истоком и стоком; затем формируют общий электрод между пятым изоляционным слоем и четвертым изоляционным слоем, используемый вместе с пиксельным электродом для формирования жидкокристаллического конденсатора.

[0015] Для достижения вышеуказанных целей в настоящем изобретении используется еще одно техническое решение: предложен пиксельный блок с тонкопленочным транзистором из низкотемпературного поликристаллического кремния, причем пиксельный блок с тонкопленочным транзистором из низкотемпературного поликристаллического кремния содержит: подложку; буферный слой, расположенный на подложке; слой полупроводниковой структуры и первый изоляционный слой, расположенные в одном слое и имеющие одинаковую толщину.

[0016] Буферный слой содержит слой нитрида кремния и слой оксида кремния, последовательно сформированные на подложке.

[0017] Пиксельный блок с тонкопленочным транзистором из низкотемпературного поликристаллического кремния также содержит: второй изоляционный слой, расположенный на слое полупроводниковой структуры и первом изоляционном слое; затвор, расположенный на втором изоляционном слое; третий изоляционный слой, расположенный на затворе; исток и сток, расположенные на третьем изоляционном слое, причем исток и сток подсоединяют к слою полупроводниковой структуры, используя первые сквозные отверстия, выполненные во втором изоляционном слое и третьем изоляционном слое, соответственно; четвертый изоляционный слой, расположенный на истоке и стоке; пиксельный электрод, расположенный на четвертом изоляционном слое, который электрически подсоединяют к истоку или стоку, используя второе сквозное отверстие, выполненное в четвертом изоляционном слое.

[0018] Пиксельный блок с тонкопленочным транзистором из низкотемпературного поликристаллического кремния также содержит: пятый изоляционный слой, расположенный между четвертым изоляционным слоем и истоком и стоком; общий электрод, расположенный между пятым изоляционным слоем и четвертым изоляционным слоем и используемый вместе с пиксельным электродом для формирования жидкокристаллического конденсатора.

[0019] Преимущества настоящего изобретения отличаются от условий, известных из предшествующего уровня техники, в настоящем изобретении формируют слой полупроводниковой структуры и первый изоляционный слой, расположенные в одном и том же слое, при этом они имеют одинаковую толщину, для того чтобы второй изоляционный слой, формируемый позже, мог иметь плоскую форму без выпуклых структур. Таким образом, слой затвора может располагаться на плоском втором изоляционном слое, чтобы обеспечивать постоянный зазор для слоя полупроводниковой структуры и предотвратить возникновение побочных эффектов из-за неравномерного зазора между слоем затвора и слоем полупроводниковой структуры, обусловленного наличием отдельных выпуклых структур во втором изоляционном слое. При этом можно улучшить электрические свойства пиксельного блока с тонкопленочным транзистором из низкотемпературного поликристаллического кремния.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

[0020] На Фиг. 1 показана блок-схема способа изготовления пиксельного блока с тонкопленочным транзистором, предлагаемого в рассматриваемом варианте исполнения настоящего изобретения.

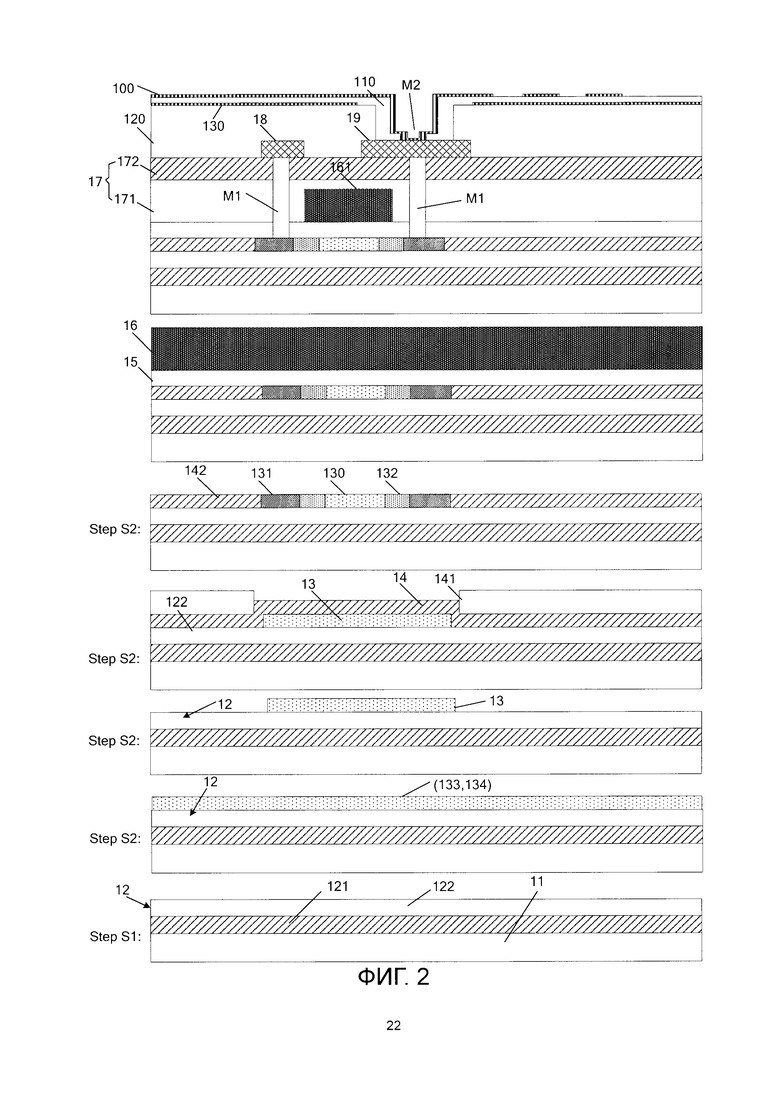

[0021] На Фиг. 2 показана схема процесса, соответствующая способу, представленному на Фиг. 1.

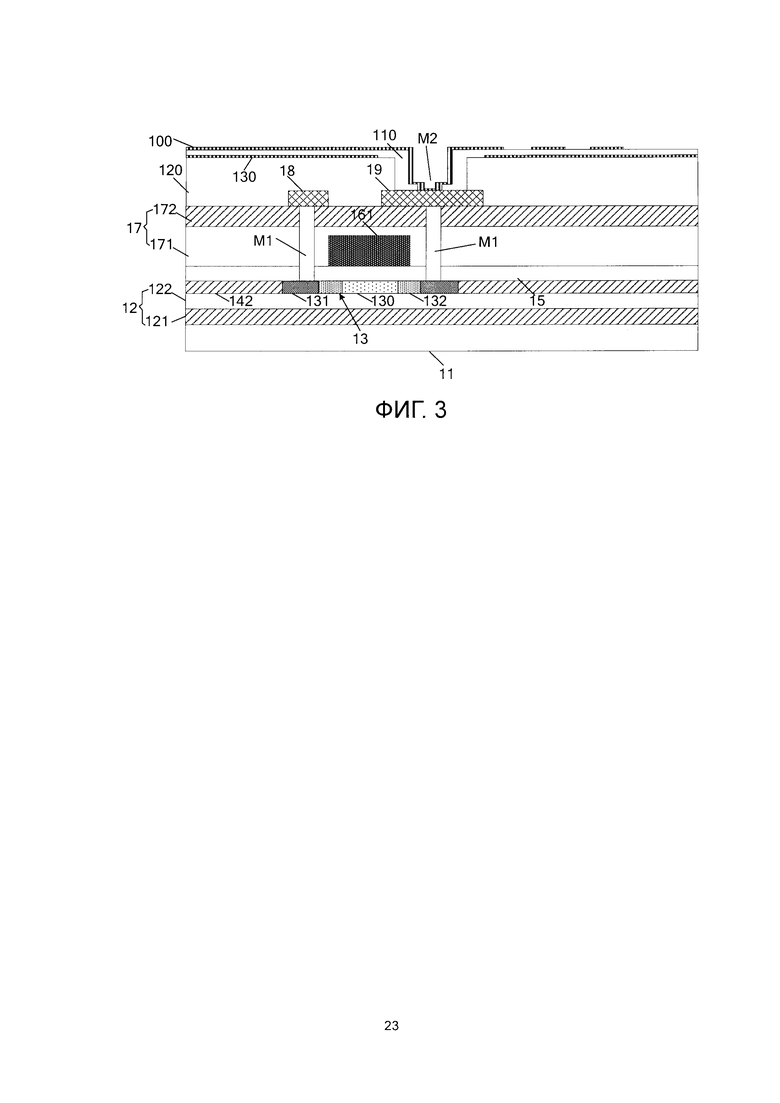

[0022] На Фиг. 3 показана структурная схема пиксельного блока с тонкопленочным транзистором, предлагаемого в рассматриваемом варианте исполнения настоящего изобретения.

ПОДРОБНОЕ ОПИСАНИЕ ЦЕЛЕСООБРАЗНЫХ ВАРИАНТОВ ИСПОЛНЕНИЯ

[0023] Обратимся к Фиг. 1 и 2. На Фиг. 1 показана блок-схема способа изготовления пиксельного блока с тонкопленочным транзистором, предлагаемого в рассматриваемом варианте исполнения настоящего изобретения, а на Фиг. 2 показана схема процесса, соответствующая способу, представленному на Фиг. 1. Как показано на Фиг. 1 и Фиг. 2, способ изготовления, предлагаемый в рассматриваемом варианте исполнения настоящего изобретения содержит следующие этапы:

[0024] этап S1, когда подготавливают подложку 11 и формируют буферный слой 12 на подложке 11.

[0025] В частности, на подложке последовательно формируют слой 121 нитрида кремния и слой 122 оксида кремния, чтобы получить буферный слой 12;

[0026] этап S2, когда формируют слой 13 полупроводниковой структуры и первый изоляционный слой 14, имеющие одинаковую толщину, и с расположением их в одном и том же слое.

[0027] Данный этап, в частности, заключается в следующем: в первую очередь формируют аморфный кремниевый слой 133 на буферном слое 12, а именно в этом варианте исполнения аморфный кремниевый слой 133 формируют на слое 122 оксида кремния. Затем осуществляют процесс кристаллизации аморфного кремниевого слоя 133 для формирования поликристаллического кремниевого слоя 134. В частности, кристаллизация может быть выполнена с помощью отжига эксимерным лазером (ELA - Excimer Laser Annealing), а затем аморфный кремниевый слой 134 структурируют с помощью первого процесса фотолитографии для формирования слоя 13 полупроводниковой структуры. Кроме того, слой 14 нитрида кремния, толщина которого совпадает с толщиной слоя 13 полупроводниковой структуры, формируют на слое 13 полупроводниковой структуры и буферном слое 12 там, где не сформирован слой 13 полупроводниковой структуры, в частности на слое 122 оксида кремния. Негативный фоторезист 141 наносят на слой 14 нитрида кремния в местах, не совпадающих с расположением слоя 13 полупроводниковой структуры, и слой 14 нитрида кремния структурируют с помощью второго процесса фотолитографии. Кроме того, травят слой 14 нитрида кремния на слое полупроводниковой структуры, чтобы травлением удалить слой 14 нитрида кремния со слоя 13 полупроводниковой структуры для формирования первого изоляционного слоя 142, при этом толщина первого изоляционного слоя совпадает с толщиной слоя 13 полупроводниковой структуры на обоих краях слоя 13 полупроводниковой структуры.

[0028] Этап структуризации аморфного кремниевого слоя 134 с помощью первого процесса фотолитографии, в частности, включает этапы, на которых в первую очередь на аморфный кремниевый слой 134 наносят фоторезист, а затем осуществляют экспонирование и проявление и т.д. для удаления лишнего аморфного кремниевого слоя 134. Вполне понятно, что принцип последующих процессов фотолитографии такой же, как и первый процесс фотолитографии, за исключением отдельных пунктов.

[0029] После того, как сформируют первый изоляционный слой 142, далее на слое 13 полупроводниковой структуры формируют нормальную область 130 и сильнолегированные области 131 с двух сторон нормальной области 130 с помощью третьего процесса фотолитографии и первого процесса легирования; затем на слое 13 полупроводниковой структуры формируют слаболегированную область 132 между нормальной областью 130 и сильнолегированными областями 131 с помощью четвертого процесса фотолитографии и второго процесса легирования.

[0030] Сильнолегированные области 131 и слаболегированная область 132 обе относятся к N-типу, вводимому с помощью ионного легирования. Различия вносятся за счет разных соотношений.

[0031] Способ в данном варианте исполнения также включает этапы, на которых формируют второй изоляционный слой 15 на слое 13 полупроводниковой структуры и первом изоляционном слое 142; формируют слой 16 затвора на втором изоляционном слое 15. Поскольку толщина слоя 13 полупроводниковой структуры и первого изоляционного слоя 142 одинаковая, поверхность второго изоляционного слоя 15 может иметь плоскую форму. Таким образом, можно устранить неравномерность поверхности второго изоляционного слоя 15. Например, побочные эффекты могут возникать из-за отдельных выпуклых структур, которые делают неравномерным зазор между слоем 16 затвора и слоем 13 полупроводниковой структуры. Соответственно, можно обеспечить более стабильную последующую передачу сигналов и улучшить электрические свойства пиксельного блока с тонкопленочным транзистором из низкотемпературного поликристаллического кремния.

[0032] В этом варианте исполнения настоящего изобретения слой 16 затвора также обрабатывают с помощью процесса фотолитографии для формирования затвора 161. Кроме того, формируют третий изоляционный слой 17 поверх затвора 161, причем в этом варианте исполнения третий изоляционный слой 17 содержит слой 171 оксида кремния и слой 172 нитрида кремния.

[0033] Кроме того, на третьем изоляционном слое 17 формируют исток 18 и сток 19 блока 10 тонкопленочного транзистора из низкотемпературного поликристаллического кремния, причем процедура формирования истока 18 и стока 19 аналогична процедуре формирования затвора 161. Повторное описание здесь не приводится. В этом варианте исполнения исток 18 и сток 19 подсоединяют к слою 13 полупроводниковой структуры с помощью первых сквозных отверстий М1, выполненных во втором изоляционном слое 15 и в третьем изоляционном слое 17, соответственно.

[0034] Кроме того, поверх истока 18 и стока 19 формируют четвертый изоляционный слой 110, а на четвертом изоляционном слое 110 формируют пиксельный электрод 100, который электрически подсоединяют к истоку 18 или стоку 19 с помощью второго сквозного отверстия М2, выполненного в четвертом изоляционном слое 110. В этом варианте исполнения пиксельный электрод 100 электрически соединен со стоком 19. В других вариантах исполнения пиксельный электрод 100 может быть электрически соединен с истоком 18.

[0035] Кроме того, между четвертым изоляционным слоем 110 и истоком 18 и стоком 19 формируют пятый изоляционный слой 120. Кроме того, между пятым изоляционным слоем 120 и четвертым изоляционным слоем 110 формируют общий электрод 130, используемый вместе с пиксельным электродом 100 для формирования жидкокристаллического конденсатора.

[0036] Следовательно, пиксельный блок 10 с тонкопленочным транзистором из низкотемпературного поликристаллического кремния, изготовленный в соответствии со способом, предлагаемым в рассмотренном варианте исполнения настоящего изобретения, обладает меньшим побочным эффектом и лучшими электрическими свойствами.

[0037] На основе вышеуказанного способа, в данном варианте исполнения настоящего изобретения также предлагается пиксельный блок с тонкопленочным транзистором из низкотемпературного

поликристаллического кремния. Обратимся к Фиг. 3 для описания изобретения.

[0038] Как показано на Фиг. 3, пиксельный блок 10 с тонкопленочным транзистором из низкотемпературного поликристаллического кремния, предлагаемый в рассматриваемом варианте исполнения настоящего изобретения, содержит подложку 11, буферный слой 12, слой 13 полупроводниковой структуры и первый изоляционный слой 142.

[0039] Буферный слой 12 содержит слой 121 нитрида кремния и слой 122 оксида кремния, при этом слой 121 нитрида кремния и слой 122 оксида кремния последовательно формируют на подложке 11.

[0040] Слой 13 полупроводниковой структуры и первый изоляционный слой 142 расположены в одном и том же слое, формируемом на слое 122 оксида кремния, при этом толщина слоя 13 полупроводниковой структуры и первого изоляционного слоя 142 одинаковая. Изготовление слоя 13 полупроводниковой структуры и первого изоляционного слоя 142 раскрыто выше. Повторное описание здесь не приводится.

[0041] В этом варианте исполнения слой 13 полупроводниковой структуры также содержит нормальную область 130 и сильнолегированные области 131 с двух сторон нормальной области 130. Кроме того, слой 13 полупроводниковой структуры также содержит слаболегированную область 132 между нормальной областью 131 и сильнолегированными областями 132.

[0042] Кроме того, пиксельный блок 10 с тонкопленочным транзистором из низкотемпературного поликристаллического кремния также содержит второй изоляционный слой 15, затвор 161, третий изоляционный слой 17, исток 18, сток 19, четвертый изоляционный слой 110 и пиксельный электрод 100.

[0043] Второй изоляционный слой 15 расположен на слое 13 полупроводниковой структуры и первом изоляционном слое 142. Затвор 161 расположен на втором изоляционном слое 15. Третий изоляционный слой 17 включает в себя слой 171 оксида кремния и слой 172 нитрида кремния, последовательно расположенные сверху затвора 161. Исток 18 и сток 19 расположены на третьем изоляционном слое 17, при этом исток 18 и сток 19 подсоединены к слою 13 полупроводниковой структуры с помощью первых сквозных отверстий М1, выполненных во втором изоляционном слое 15 и третьем изоляционном слое 17, соответственно. Четвертый изоляционный слой 110 расположен сверху истока 18 и стока 19. Пиксельный электрод 100 расположен на четвертом изоляционном слое 110 и электрически соединен с истоком 18 или стоком 19 с помощью второго сквозного отверстия М2, выполненного в четвертом изоляционном слое 110.

[0044] Кроме того, пиксельный блок 10 с тонкопленочным транзистором из низкотемпературного поликристаллического кремния также содержит пятый изоляционный слой 120 и общий электрод 130. Пятый изоляционный слой 120 расположен между четвертым изоляционным слоем 110 и истоком 18 и стоком 19. Общий электрод 130 расположен между пятым изоляционным слоем 120 и четвертым изоляционным слоем 110 и используется вместе с пиксельным электродом 100 для формирования жидкокристаллического конденсатора.

[0045] В заключение следует отметить, что настоящее изобретение может уменьшить побочный эффект пиксельного блока 10 с тонкопленочным транзистором из низкотемпературного поликристаллического кремния и улучшить его электрические свойства.

[0046] Выше раскрыты конкретные варианты исполнения настоящего изобретения, однако объем настоящего изобретения не ограничивается ими, а изменение или замена, легко производимые любыми специалистами в данной области техники, входят в объем правовой охраны изобретения. Таким образом, объем правовой охраны изобретения должен определяться формулой изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗГОТОВЛЕНИЯ ТОНКОПЛЕНОЧНОГО ТРАНЗИСТОРА | 2012 |

|

RU2522930C2 |

| Способ изготовления быстродействующего кремниевого МОП-транзистора | 2024 |

|

RU2822006C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МОП-ТРАНЗИСТОРА НА СТРУКТУРЕ "КРЕМНИЙ НА ИЗОЛЯТОРЕ" | 2022 |

|

RU2784405C1 |

| ТОНКОПЛЕНОЧНЫЙ ТРАНЗИСТОР ИЗ НИЗКОТЕМПЕРАТУРНОГО ПОЛИКРИСТАЛЛИЧЕСКОГО КРЕМНИЯ И СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ | 2014 |

|

RU2634087C1 |

| ПОЛУПРОВОДНИКОВОЕ УСТРОЙСТВО, СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ И ДИСПЛЕЙНОЕ УСТРОЙСТВО | 2009 |

|

RU2471265C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МОП-ТРАНЗИСТОРА | 1991 |

|

RU2024107C1 |

| ПОЛУПРОВОДНИКОВОЕ УСТРОЙСТВО | 2010 |

|

RU2501117C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ СТРУКТУР МДП-ПРИБОРОВ | 1983 |

|

SU1168021A1 |

| ПОДЛОЖКА АКТИВНОЙ МАТРИЦЫ И ЖИДКОКРИСТАЛЛИЧЕСКОЕ УСТРОЙСТВО ОТОБРАЖЕНИЯ | 2008 |

|

RU2444068C2 |

| ПОЛУПРОВОДНИКОВОЕ УСТРОЙСТВО И СПОСОБ ДЛЯ ЕГО ПРОИЗВОДСТВА | 2010 |

|

RU2506661C1 |

Использование: для изготовления пиксельного блока с тонкопленочным транзистором из низкотемпературного поликристаллического кремния. Сущность изобретения заключается в том, что способ изготовления пиксельного блока с тонкопленочным транзистором из низкотемпературного поликристаллического кремния содержит: подготовку подложки и формирование буферного слоя на подложке; формирование слоя полупроводниковой структуры и первого изоляционного слоя, имеющих одинаковую толщину, и с расположением их в одном и том же слое; причем этап формирования буферного слоя на подложке включает этап: на подложке последовательно формируют слой нитрида кремния и слой оксида кремния; этап формирования на буферном слое слоя полупроводниковой структуры и первого изоляционного слоя, расположенных в одном и том же слое и имеющих одинаковую толщину, включает этапы, на которых: формируют аморфный кремниевый слой на буферном слое и осуществляют процесс кристаллизации аморфного слоя для формирования поликристаллического кремниевого слоя; структурируют аморфный кремниевый слой с помощью первого процесса фотолитографии для формирования слоя полупроводниковой структуры; формируют слой нитрида кремния, толщина которого совпадает с толщиной слоя полупроводниковой структуры, на слое полупроводниковой структуры и буферном слое там, где не сформирован слой полупроводниковой структуры; наносят негативный фоторезист на слой нитрида кремния в местах, не совпадающих с расположением слоя полупроводниковой структуры; структурируют слой нитрида кремния с помощью второго процесса фотолитографии; далее травят слой нитрида кремния на слое полупроводниковой структуры, чтобы травлением удалить слой нитрида кремния со слоя полупроводниковой структуры для формирования первого изоляционного слоя, толщина которого совпадает с толщиной слоя полупроводниковой структуры на обоих краях слоя полупроводниковой структуры. Технический результат: обеспечение возможности уменьшения побочного эффекта и улучшения электрических свойств. 3 н. и 7 з.п. ф-лы, 3 ил.

1. Способ изготовления пиксельного блока с тонкопленочным транзистором из низкотемпературного поликристаллического кремния, в котором: подготавливают подложку и формируют буферный слой на подложке; формируют слой полупроводниковой структуры и первый изоляционный слой, имеющие одинаковую толщину, и с расположением их в одном и том же слое;

причем этап формирования буферного слоя на подложке включает этап: на подложке последовательно формируют слой нитрида кремния и слой оксида кремния;

этап формирования на буферном слое слоя полупроводниковой структуры и первого изоляционного слоя, расположенных в одном и том же слое и имеющих одинаковую толщину, включает этапы, на которых: формируют аморфный кремниевый слой на буферном слое и осуществляют процесс кристаллизации аморфного слоя для формирования поликристаллического кремниевого слоя;

структурируют аморфный кремниевый слой с помощью первого процесса фотолитографии для формирования слоя полупроводниковой структуры;

формируют слой нитрида кремния, толщина которого совпадает с толщиной слоя полупроводниковой структуры, на слое полупроводниковой структуры и буферном слое там, где не сформирован слой полупроводниковой структуры;

наносят негативный фоторезист на слой нитрида кремния в местах, не совпадающих с расположением слоя полупроводниковой структуры;

структурируют слой нитрида кремния с помощью второго процесса фотолитографии;

далее травят слой нитрида кремния на слое полупроводниковой структуры, чтобы травлением удалить слой нитрида кремния со слоя полупроводниковой структуры для формирования первого изоляционного слоя, толщина которого совпадает с толщиной слоя полупроводниковой структуры на обоих краях слоя полупроводниковой структуры.

2. Способ по п. 1, в котором дополнительно:

формируют нормальную область и сильнолегированные области по двум сторонам нормальной области на слое полупроводниковой структуры с помощью третьего процесса фотолитографии и первого процесса легирования;

затем формируют слаболегированную область между нормальной областью и сильнолегированными областями на слое полупроводниковой структуры с помощью четвертого процесса фотолитографии и второго процесса легирования.

3. Способ по п. 2, в котором дополнительно:

формируют второй изоляционный слой на слое полупроводниковой структуры и первом изоляционном слое;

формируют слой затвора на втором изоляционном слое и структурируют слой затвора с помощью пятого процесса фотолитографии для формирования затвора;

формируют третий изоляционный слой поверх затвора;

формируют исток и сток блока тонкопленочного транзистора из низкотемпературного поликристаллического кремния на третьем изоляционном слое, причем исток и сток подсоединяют к слою полупроводниковой структуры с помощью первых сквозных отверстий, выполненных во втором изоляционном слое и третьем изоляционном слое соответственно;

формируют четвертый изоляционный слой поверх истока и стока, а на четвертом изоляционном слое формируют пиксельный электрод, который электрически подсоединен к истоку или стоку с помощью второго сквозного отверстия, выполненного в четвертом изоляционном слое.

4. Способ по п. 3, в котором дополнительно:

формируют пятый изоляционный слой между четвертым изоляционным слоем и истоком и стоком;

затем формируют общий электрод между пятым изоляционным слоем и четвертым изоляционным слоем, используемый вместе с пиксельным электродом для формирования жидкокристаллического конденсатора.

5. Способ изготовления пиксельного блока с тонкопленочным транзистором из низкотемпературного поликристаллического кремния, в котором:

подготавливают подложку и формируют буферный слой на подложке;

формируют слой полупроводниковой структуры и первый изоляционный слой, имеющие одинаковую толщину, и с расположением их в одном и том же слое,

этап формирования буферного слоя на подложке включает этап, на котором:

на подложке последовательно формируют слой нитрида кремния и слой оксида кремния, а

этап формирования на буферном слое слоя полупроводниковой структуры и первого изоляционного слоя, расположенных в одном и том же слое и имеющих одинаковую толщину, включает этапы, на которых:

формируют аморфный кремниевый слой на буферном слое и осуществляют процесс кристаллизации аморфного слоя для формирования поликристаллического кремниевого слоя;

структурируют аморфный кремниевый слой с помощью первого процесса фотолитографии для формирования слоя полупроводниковой структуры;

формируют слой нитрида кремния, толщина которого совпадает с толщиной слоя полупроводниковой структуры, на слое полупроводниковой структуры и буферном слое там, где не сформирован слой полупроводниковой структуры;

наносят негативный фоторезист на слой нитрида кремния в местах, не совпадающих с расположением слоя полупроводниковой структуры;

структурируют слой нитрида кремния с помощью второго процесса фотолитографии;

далее травят слой нитрида кремния на слое полупроводниковой структуры, чтобы травлением удалить слой нитрида кремния со слоя полупроводниковой структуры для формирования первого изоляционного слоя, толщина которого совпадает с толщиной слоя полупроводниковой структуры на обоих краях слоя полупроводниковой структуры.

6. Способ по п. 5, в котором дополнительно:

формируют нормальную область и сильнолегированные области по двум сторонам нормальной области на слое полупроводниковой структуры с помощью третьего процесса фотолитографии и первого процесса легирования;

затем формируют слаболегированную область между нормальной областью и сильнолегированными областями на слое полупроводниковой структуры с помощью четвертого процесса фотолитографии и второго процесса легирования.

7. Способ по п. 6, в котором дополнительно:

формируют второй изоляционный слой на слое полупроводниковой структуры и первом изоляционном слое;

формируют слой затвора на втором изоляционном слое и структурируют слой затвора с помощью пятого процесса фотолитографии для формирования затвора;

формируют третий изоляционный слой поверх затвора;

формируют исток и сток блока тонкопленочного транзистора из низкотемпературного поликристаллического кремния на третьем изоляционном слое, причем исток и сток подсоединены к слою полупроводниковой структуры с помощью первых сквозных отверстий, выполненных во втором изоляционном слое и третьем изоляционном слое соответственно;

формируют четвертый изоляционный слой поверх истока и стока, а на четвертом изоляционном слое формируют пиксельный электрод, который электрически подсоединен к истоку или стоку с помощью второго сквозного отверстия, выполненного в четвертом изоляционном слое.

8. Способ по п. 7, в котором дополнительно:

формируют пятый изоляционный слой между четвертым изоляционным слоем и истоком и стоком;

затем формируют общий электрод между пятым изоляционным слоем и четвертым изоляционным слоем, используемый вместе с пиксельным электродом для формирования жидкокристаллического конденсатора.

9. Пиксельный блок с тонкопленочным транзистором из низкотемпературного поликристаллического кремния, содержащий:

подложку;

буферный слой, расположенный на подложке;

слой полупроводниковой структуры и первый изоляционный слой, расположенные в одном и том же слое и имеющие одинаковую толщину,

причем

буферный слой включает слой нитрида кремния и слой оксида кремния, последовательно сформированные на подложке,

отличающийся тем, что дополнительно содержит:

второй изоляционный слой, расположенный на слое полупроводниковой структуры и первом изоляционном слое;

затвор, расположенный на втором изоляционном слое;

третий изоляционный слой, расположенный поверх затвора;

исток и сток, расположенные на третьем изоляционном слое, причем исток и сток подсоединены к слою полупроводниковой структуры с помощью первых сквозных отверстий, выполненных во втором изоляционном слое и третьем изоляционном слое соответственно;

четвертый изоляционный слой, расположенный поверх истока и стока;

пиксельный электрод, расположенный на четвертом изоляционном слое и электрически подсоединенный к истоку или стоку с помощью второго сквозного отверстия, выполненного в четвертом изоляционном слое.

10. Пиксельный блок с тонкопленочным транзистором из низкотемпературного поликристаллического кремния по п. 9, который содержит:

пятый изоляционный слой, расположенный между четвертым изоляционным слоем и истоком и стоком;

общий электрод, расположенный между пятым изоляционным слоем и четвертым изоляционным слоем, используемый вместе с пиксельным электродом для формирования жидкокристаллического конденсатора.

| US 7078274 B2, 18.07.2006 | |||

| US 20100047975 A1, 25.02.2010 | |||

| CN 102709284 A, 03.10.2012 | |||

| CN 103489828 A, 01.01.2014 | |||

| CN 103943630 A, 23.07.2014. |

Авторы

Даты

2018-10-19—Публикация

2015-01-28—Подача