Уровень техники

Органические материалы все шире применяются в электронных функциональных элементах в составе электронных устройств. Например, органические материалы все шире используются при изготовлении полупроводниковых и изоляционных/диэлектрических элементов транзисторных матриц.

Известная технология изготовления электронного устройства, содержащего органические материалы, предусматривает нанесение органических материалов на несущую подложку и применение процесса маскирования с целью избежать нанесения органических материалов на один или более участков в той части несущей подложки, которая должна остаться в законченном устройстве, чтобы иметь в одной или более периферийных областях устройства зоны, свободные от органического материала.

Авторы настоящего изобретения обнаружили, что устройства, изготовленные по данной технологии, имеют определенные дефекты, и идентифицировали задачу уменьшения количества таких дефектов.

Раскрытие изобретения

Таким образом, задача, решаемая изобретением, заключается в снижении частоты появления дефектов в устройствах, содержащих органические материалы.

Для решения этой задачи предлагается способ, включающий формирование на общей подложке одной или более серий многослойных электронных устройств с последующим разделением указанных устройств; каждое из которых содержит один или более слоев органического материала, при этом способ включает нанесение единственного или каждого из указанных слоев в виде слоя, имеющего протяженность по меньшей мере от одного конца одной или более серий устройств до противоположного конца одной или более серий устройств.

Согласно одному варианту способа каждое электронное устройство содержит массив транзисторов, тогда как один или более слоев органического материала, наносимых в виде одного или более непрерывных слоев, содержат один или более из следующих слоев: полупроводниковый слой, задающий полупроводниковые каналы транзисторов; диэлектрический слой, образующий диэлектрик затворов транзисторов, и один или более изоляторных слоев, нанесенных между проводящими слоями.

Согласно другому варианту электронные устройства содержат по меньшей мере один проводящий слой, задающий массив проводников, активируемых через соответствующие выходные терминалы одного или более чипов драйвера, тогда как способ включает формирование контактов для указанных одного или более чипов драйвера с локализацией указанных контактов поверх одного или более слоев органического материала, наносимых в виде непрерывных слоев, при этом указанные контакты связаны с соответствующими проводниками указанного массива через указанные один или более слоев органического материала.

Согласно следующему варианту устройства содержат по меньшей мере три проводящих слоя, расположенные на соответствующих уровнях, тогда как способ дополнительно включает осуществление сжатия периферийной области указанных одного или более слоев органического материала, нанесенных в виде непрерывных слоев; и создание одного или более проводящих перемычек между одним или более частями верхнего проводящего слоя в указанной периферийной области и одной или более частями промежуточного проводящего слоя, смещенными внутрь относительно указанной периферийной области, через одну или более частей нижнего проводящего слоя, расположенных между указанной периферийной областью и областью, смещенной внутрь относительно периферийной области.

Согласно одному варианту верхний проводящий слой задает контакты затвора и истока для массива транзисторов, а одна или более частей указанного промежуточного проводящего слоя содержат один или более проводников затвора, образующих электроды затвора для указанного массива транзисторов, и/или один или более проводников истока, образующих электроды истока для массива транзисторов.

Согласно другому варианту способ дополнительно включает:

формирование по меньшей мере одного закорачивающего проводника, связывающего группу проводников в проводящем слое, расположенных под указанными одним или более слоями органического материала, нанесенными в виде непрерывных слоев;

формирование по меньшей мере одной межслоевой проводящей перемычки между указанным закорачивающим проводником и контактом, сформированным поверх указанных одного или более слоев органического материала, через указанные один или более слоев, нанесенных в виде непрерывных слоев, и

осуществление электрического тестирования через указанный контакт с последующим изолированием закорачивающего проводника от указанной группы проводников путем удаления одной или более частей указанного проводящего слоя и одной или более частей одного или более слоев органического материала, расположенных поверх указанных одной или более частей проводящего слоя.

Краткое описание чертежей

Далее, со ссылками на прилагаемые чертежи, будет описан, только в качестве примера, вариант способа согласно изобретению.

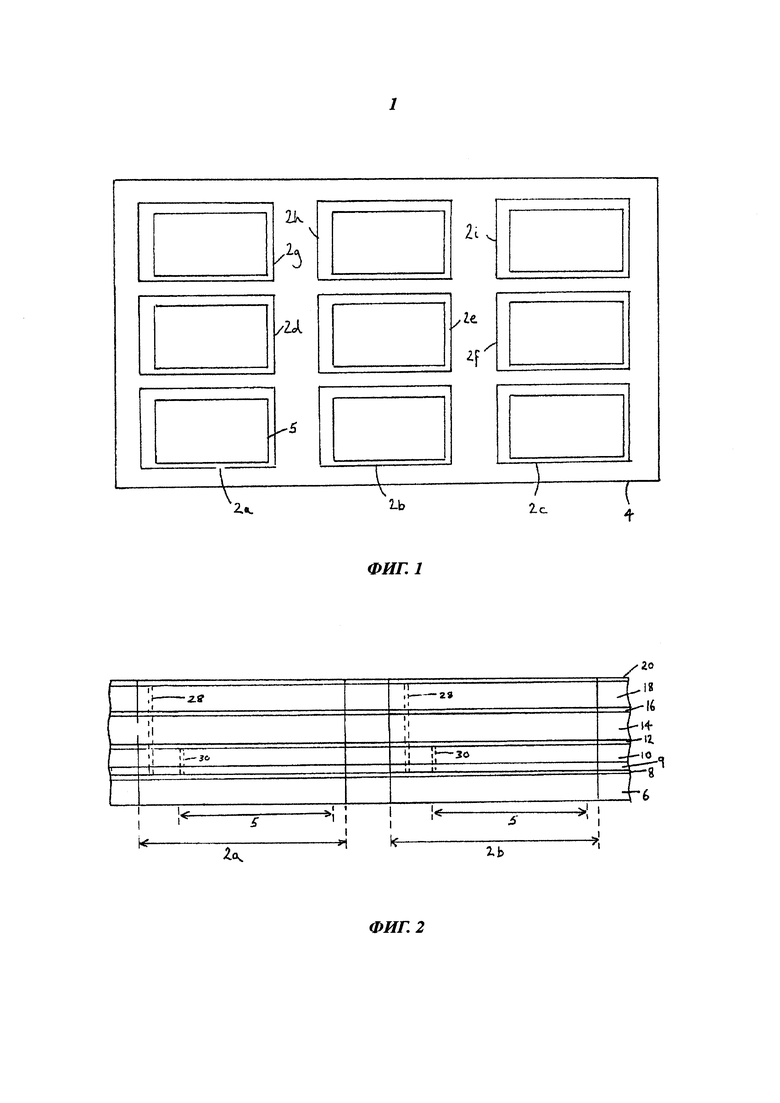

На фиг. 1 схематично иллюстрируется пример области, в которой наносятся слои, формирующие множество электронных устройств, содержащих органические материалы.

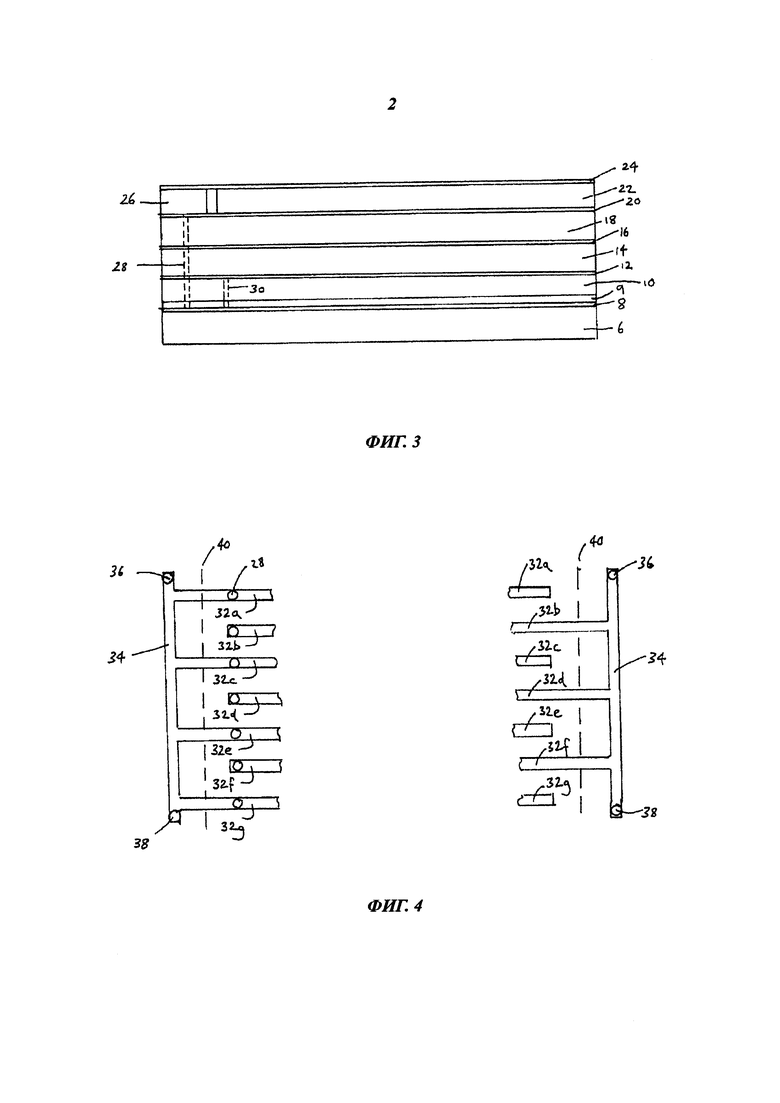

На фиг. 2 схематично проиллюстрирован пример стопы слоев для множества электронных устройств.

На фиг. 3 представлен пример расположения межслоевых проводящих перемычек между проводящими слоями.

Фиг. 4 иллюстрирует пример технологии, направленной на облегчение электрического тестирования проводников, расположенных ниже верхнего проводящего слоя.

Осуществление изобретения

Далее будет описан пример способа согласно варианту изобретения, применимый, например, при изготовлении электронных устройств, содержащих матрицу транзисторов, сконфигурированную для управления оптическими средами для дисплеев. Однако данный способ применим также к электронным устройствам других типов, а также к устройствам, содержащим транзисторную матрицу, сконфигурированную иначе, чем проиллюстрированная на чертежах. Другие примеры способов, посредством которых можно, в рамках изобретения, модифицировать проиллюстрированные на чертежах устройства, обсуждаются в конце данного описания.

Рассматриваемый пример относится к изготовлению множества электронных устройств, находящихся на одной стадии процесса изготовления на общем листе 6 несущего материала (подложки). На одной из последующих стадий электронные устройства отделяют одно от другого (область, занимаемая каждым электронным устройством после его отделения, обозначена, как 2).. У каждого электронного устройства имеется область (обозначенная, как 5), занимаемая транзисторной матрицей, и периферийная область, служащая, например, для разводки проводников затвора и истока вокруг транзисторной матрицы к одному или более контактам чипа драйвера. Область, в пределах которой на лист несущего материала в процессе изготовления устройств наносятся непрерывные слои проводящих, полупроводниковых и изоляторных/диэлектрических материалов, обозначена, как 4. Можно видеть, что эта область включает в себя всю прямоугольную зону, периметр которой совпадает с наружными краями областей 2a-2i, занятых крайними устройствами, и выходит за пределы этой зоны.

Примеры несущих материалов включают гибкие пленки из пластика, имеющие планаризованную верхнюю поверхность. В процессе изготовления такие гибкие пластиковые пленки могут временно крепиться (приклеиваться) к жесткой материнской плате (не изображена).

Как можно видеть из фиг. 2, пример процесса изготовления включает нанесение на несущий лист 6 непрерывного первого проводящего слоя 8 с последующим структурированием этого слоя, чтобы сформировать массив проводников затвора и истока для каждого электронного устройства. В этом примере структурирование первого проводящего слоя обеспечивает также формирование продолжений проводников затвора и временных закорачивающих проводников (перемычек), которые будут более подробно описаны далее. Проводники истока образуют электроды истока для транзисторов, а проводники стока образуют для соответствующих транзисторов электроды стока. Согласно одному примеру каждый проводник истока образует электроды истока для соответствующей строки транзисторов транзисторной матрицы.

Затем на структурированный первый проводящий слой 8 наносят непрерывный слой 9 органического полупроводникового материала, например полупроводникового полимера. Этот полупроводниковый слой 9 обеспечивает формирование полупроводниковых каналов для всех транзисторов всех транзисторных матриц.

После этого полупроводникового слоя 9 наносят непрерывный слой 10 диэлектрического материала (или стопу непрерывных слоев диэлектрических материалов). Слой (слои) 10 образует (образуют) диэлектрический затвор для всех транзисторов всех транзисторных матриц.

В этом примере полупроводниковый и диэлектрический слои 9, 10 затем структурируют, чтобы сформировать сквозные отверстия для межслоевых проводящих перемычек, ведущих от продолжений проводников затвора, сформированных первым проводящим слоем 8, к соответствующим проводникам затвора, которые будут сформированы на следующей стадии процесса изготовления. Поверх диэлектрического слоя (диэлектрических слоев) 10 наносят непрерывный второй слой 12 проводящего материала. Нанесение второго проводящего слоя приводит к заполнению сквозных отверстий, сформированных в полупроводниковом и диэлектрическом слоях 9, 10. Затем проводят структурирование второго проводящего слоя 12, чтобы сформировать для каждой транзисторной матрицы проводники затвора, которые образуют электроды затвора для транзисторов. В этом примере каждый проводник затвора образует электроды затвора для соответствующего столбца транзисторов матрицы. При этом проводники затвора соединены через сквозные отверстия, сформированные в полупроводниковом и диэлектрическом слоях 9, 10, с соответствующими продолжениями проводников затвора, образованными в результате структурирования первого проводящего слоя. В данном примере структурирование второго проводящего слоя 12 предусматривает также образование (а) сквозных отверстий в проводниках затвора, чтобы обеспечить возможность сформировать межслоевые проводящие перемычки между проводниками стока и соответствующими пиксельными проводниками на более высоком уровне; (b) временных закорачивающих перемычек для создания временных перемычек между проводниками затвора (как это будет более подробно рассмотрено далее) и (с) сквозных отверстий для межслоевых проводящих перемычек, которые должны быть сформированы между верхним проводящим слоем 20 и временными закорачивающими перемычками 34 (см. фиг. 4), образованными при структурировании первого проводящего слоя 8.

Затем поверх второго структурированного проводящего слоя 12 наносят непрерывный слой 14 изоляторного материала (или стопу непрерывных слоев). Функция этого изоляторного слоя (изоляторных слоев) 14 состоит в предотвращении электрических замыканий между вторым проводящим слоем 12 и третьим проводящим слоем 16 (который будет описан далее).

Непрерывный третий слой 16 проводящего материала наносят поверх изоляторного слоя 14, причем его структурируют, чтобы сформировать сквозные отверстия для (i) межслоевых проводящих перемычек между проводниками стока и соответствующими пиксельными проводниками, сформированными в верхнем проводящем слое 20, (N) межслоевых проводящих перемычек 28, соединяющих продолжения проводников затвора и проводники истока, сформированные структурированным первым проводящим слоем, с соответствующими контактами чипа драйвера, сформированными верхним проводящим слоем 20, и (iii) сквозных отверстий для межслоевых проводящих перемычек между временными закорачивающими перемычками, образованными структурированными первым и вторым проводящими слоями, и верхним проводящим слоем 20. Этот, третий проводящий слой 18 функционирует как экранирующий слой, который устраняет влияние электрических потенциалов, возникающих на нижележащих проводниках, на электрические потенциалы, присутствующие на пиксельных проводниках, заданных верхним проводящим слое 20.

После этого поверх структурированного третьего проводящего слоя 16 наносят непрерывный слой 18 изоляторного материала (или стопу непрерывных слоев изоляторных материалов). Функция этого слоя из изоляторного материала состоит в предотвращении электрических замыканий между третьим проводящим слоем 16 и верхним проводящим слоем 20. Затем производят структурирование комбинации полупроводникового и изоляторных слоев 9, 10, 14 и 18, чтобы сформировать (i) сквозные отверстия, проходящие вниз до каждого проводника стока, (ii) сквозные отверстия, проходящие вниз до каждого продолжения проводника затвора, (iii) сквозные отверстия, проходящие вниз до каждого проводника истока, и (iv) сквозные отверстия, проходящие вниз до каждой из временных закорачивающих перемычек, сформированных структурированием первого и второго проводящих слоем 8, 12.

Затем поверх изоляторного слоя 18 наносят непрерывный четвертый слой 20 проводящего материала. Этот, непрерывный четвертый слой 20 проводящего материала заполняет вышеупомянутые сквозные отверстия (i), (ii), (iii) и (iv). Далее четвертый слой 20 проводящего материала структурируют, чтобы сформировать по меньшей мере (i) массив пиксельных проводников, каждый из которых соединен посредством одного или более соответствующих межслоевых проводящих перемычек (не изображены) с соответствующим проводником стока, (ii) контакты затвора, соединенные посредством одной или более межслоевых проводящих перемычек 28 с соответствующими продолжениями проводников затвора, образованными при структурировании первого проводящего слоя 8; (iii) контакты истока, соединенные посредством одной или более межслоевых проводящих перемычек 28 с соответствующими проводниками истока, образованными при структурировании первого проводящего слоя 8, и (iv) контакты закорачивающих перемычек, соединенные с соответствующими закорачивающими перемычками, образованными структурированными первым и вторым проводящими слоями 8, 12. Контакты затвора и истока, образованные при структурировании четвертого проводящего слоя 20, используются для обеспечения соединений с соответствующими выходными терминалами одного или более чипов драйвера, выполненных по технологии "чип-на-пластике" (chip-on-plastic, СОР) или с одним или более выходными терминалами одной или более тонкопленочных микросхем (chip-on-fiex, COF). Как будет показано далее, контакты закорачивающих перемычек используются для промежуточного электрического тестирования проводников истока и затвора.

Как уже было упомянуто, в этом примере первый структурированный проводящий слой задает массив проводников 32 истока (см. фиг. 4), каждый из которых образует электроды истока для соответствующей строки транзисторов.

Структурирование первого проводящего слоя 8 включает образование одной или более проводящих закорачивающих перемычек 34, которые связывают в структурированном первом проводящем слое 8 соответствующие группы проводников 32 истока. Эти временные закорачивающие перемычки 34 находятся снаружи зон локализации межслоевых проводящих перемычек 28, проходящих между проводниками 32 истока и структурированным четвертым проводящим слоем 20. Имеются также одна или более дополнительных межслоевых проводящих перемычек 36, 38, проходящих от каждой закорачивающей перемычки 34 к одному или более верхних уровней. В этом примере эти дополнительные межслоевые перемычки включают: (а) одну или более межслоевых перемычек 36 между каждой закорачивающей перемычкой 34 и одним или более соответствующими контактами, образованными при структурировании второго проводящего слоя 12 с целью облегчить тестирование на стадии, следующей за формированием проводников затвора, но до нанесения покрывающего их изоляторного слоя 14; (b) одно или более межслоевых перемычек 38 между каждой закорачивающей перемычкой 34 и одним или более соответствующими контактами, образованными при структурировании дополнительного проводящего слоя 20, с целью облегчить тестирование после формирования пиксельных проводников и контактов затвора/истока и др.

По завершении электрического тестирования проводящие связи между закорачивающими перемычками 34 и проводниками 32 истока в первом проводящем слое 8 разрушаются путем создания отверстий на одном или более участках 40 между закорачивающими перемычками и местоположениями межслоевых перемычек 28 между проводниками 32 истока и структурированным четвертым проводящим слоем 20. Эти отверстия проходят вниз сквозь все слои стопы до несущей подложки 6. Одним из примеров технологии для формирования подобных отверстий является лазерная абляция. В этом примере второй, третий и четвертый проводящие слои структурированы таким образом, что эти отверстия могут быть сформированы без прорезания какого-либо проводящего материала этих трех структурированных проводящих слоев 12, 16, 20, чтобы более надежно предотвратить нежелательное закорачивание между любыми из четырех проводящих слоев. На фиг. 4 показаны только 7 проводников истока, однако, устройство может содержать более тысячи таких проводников, каждый из которых формирует электроды истока для соответствующей одной строки из более чем тысячи строк транзисторов. В этом примере технологии формирования временных закорачивающих перемычек аналогичны технологиям, применяемым для проводников затвора. Между каждой закорачивающей перемычкой, образованной при структурировании второго проводящего слоя 12, и одним или более соответствующих контактов, заданных при структурировании дополнительного проводящего слоя 20, сформированы одна или более межслоевых перемычек.

После того как будет завершено окончательное электрическое тестирование через структурированный четвертый проводящий слой 20, а временные закорачивающие перемычки 34 будут изолированы, результирующую структуру разделяют на индивидуальные устройства путем разрезания стопы слоев и несущего листа 6. В этом примере каждое индивидуальное устройство затем ламинируют с получением соответствующего компонента оптической среды, в котором каждая пиксельная часть оптической среды 22 (например электрофоретической среды) может независимо переключаться между двумя или более состояниями посредством управления электрическим потенциалом на соответствующем пиксельном проводнике в составе массива пиксельных проводников, образованного структурированным четвертым проводящим слоем 20.

В этом примере процесс ламинирования включает формирование одной или более сжимаемых контактных площадок 26 между компонентом оптической среды и управляющим компонентом в одной или более областей, расположенных снаружи области 5, занятой транзисторной матрицей, чтобы создать электрическое соединение между одним или более СОМ контактов, образованных структурированным четвертым проводящим слоем 20, и общим электродным слоем 24 компонента оптической среды. В процессе ламинирования данного компонента происходит прижатие, с усилием, одной или более контактных площадок 26 к верхней поверхности стопы, что обеспечивает качественное, надежное соединение между общим электродным слоем 24 компонента оптической среды и одним или более СОМ контактами, образованными структурированным четвертым проводящим слоем 20.

В этом примере межслоевые проводящие перемычки 28 для контактов затвора и истока, заданные структурированным четвертым проводящим слоем 20, проходят вниз к проводникам истока и к продолжениям проводников затвора, заданным структурированным первым проводящим слоем 8; а межслоевые проводящие перемычки 30 между проводниками затвора и продолжениями проводников затвора сформированы на участках, внутренних по отношению к местоположениям контактных площадок (как это схематично показано на фиг. 3). Было установлено, что эта технология разводки соединений (перемычек) между структурированным четвертым проводящим слоем 20 и частями промежуточных проводящих слоев, внутренних по отношению к местоположениям контактных площадок, через структурированный четвертый проводящий слой 20, уменьшает количество отказов устройств. Такое уменьшение количества отказов рассматривается как следствие неиспользования поперечной разводки через области второго, третьего и четвертого структурированных проводящих слоев, которые могут быть чувствительны к деформированию в процессе сжатия контактных площадок 26 между компонентом оптической среды и верхней поверхностью стопы, содержащей второй, третий и четвертый проводящие слои, наложенные на один или более изоляторных/полупроводниковых слоев, содержащих относительно мягкий органический материал. Процесс изготовления может включать также дополнительные операции, например инкапсулирование.

Электронные устройства могут содержать один или более элементов, не проиллюстрированных на чертежах или не упомянутых выше. Так, можно предусмотреть один или более дополнительных функциональных слоев, например, между пластиковой пленкой-подложкой и выравнивающим слоем, используемым для планаризации верхней поверхности этой пленки, и/или между выравнивающим слоем и первым структурированным проводящим слоем, и/или на стороне пластиковой пленки-подложки, противоположной по отношению к выравнивающему слою.

В этом примере полупроводниковый слой 9 и все изоляторные/диэлектрические слои 10, 14, 18 содержат органические полимерные материалы и нанесены в виде непрерывных слоев с использованием жидкостной технологии (например флексографической печати и/или центрифугирования) или из паровой фазы, т.е. без какого-либо маскирования с целью предотвратить нанесение на любые зоны вокруг областей 5 размещения транзисторных матриц. Авторы настоящего изобретения обнаружили, что уменьшение использования масок уменьшает количество оптических неоднородностей в пределах области транзисторной матрицы, когда она используется для управления отображающей средой.

В данном примере описанное структурирование органических слоев осуществляется посредством лазерной абляции.

В рассмотренном примере нанесение всех четырех проводящих слоев производилось посредством распыления, а их структурирование - посредством фотолитографии. Примеры материалов для проводящих слоев включают металлы и сплавы. Проводящие слои могут иметь многослойную структуру. Например, было установлено, что применение для проводящих слоев двухслойной металлической структуры может улучшить адгезию между проводящим слоем и нижележащим органическим материалом. В частности, было обнаружено, что формирование каждого проводящего слоя путем нанесения сначала титана, а затем металла с более высокой электропроводностью (такого как золото) позволяет получить слой, обладающий как лучшей адгезией к нижележащему органическому материалу, так и хорошей электропроводностью. Было обнаружено также, что, подвергая органические слои воздействию аргоновой плазмой непосредственно перед нанесением на них металла, можно улучшить адгезию между органическим материалом и покрывающим его металлом. Было также обнаружено, что предварительная обработка слоев металла ультрафиолетовым излучением непосредственно перед нанесением органического изоляторного/диэлектрического материала может повысить адгезию слоев металла к соответствующему покрывающему органическому материалу.

Полупроводниковый слой 9 перед нанесением слоя 10, формирующего диэлектрический затвор, может быть дополнительно структурирован так, чтобы уменьшить токи утечки между смежными проводниками истока, в частности, в зонах вблизи вертикальных межслоевых перемычек 28, где плотность расположения проводников истока может быть наибольшей. Примером технологии для осуществления подобного дополнительного структурирования является лазерная абляция. Другой пример технологии для уменьшения токов утечки (если их требуется уменьшить) включает нанесение на структурированный первый проводящий слой непрерывного слоя изоляционного материала (например материала для изолирования фоторезиста) перед нанесением полупроводникового материала 9 и структурирование изоляторного слоя таким образом, чтобы сохранить его под теми областями полупроводникового слоя 9, для которых токи утечки составляют проблему. Другой пример альтернативной технологии состоит в существенном уменьшении проводимости полупроводникового материала в тех областях полупроводникового слоя 9, для которых токи утечки составляют проблему. Следующий пример альтернативной технологии состоит в том, чтобы задать в структурированном втором проводящем слое один или более дополнительных проводников, которые наложены на области полупроводникового слоя, токи утечки в которых составляют проблему, и в приложении к этим дополнительным проводникам напряжений, которые вызывают уменьшение проводимости нижележащего полупроводника в результате действия полевого эффекта.

Было установлено, что описанная технология с ограниченным применением масок при нанесении органических материалов облегчает также структурирование проводящих слоев с высоким разрешением.

Приведенное описание относится к примеру массива транзисторов с верхним расположением затвора. Однако описанная технология в равной степени применима к изготовлению электронных устройств, отличных от устройств с транзисторной матрицей, а также к изготовлению устройств, содержащих транзисторные матрицы других типов, таких как массивы транзисторов с нижним расположением затвора. В частности, описанная технология применима к устройствам другого типа, содержащим стопу слоев, включающую один или более органических материалов. Примером подобного устройства, не содержащего полупроводникового слоя, является устройство на базе ячейки с прямым управлением (direct drive cell device), в которой каждый пиксельный проводник связан с соответствующим выходным терминалом контроллера непосредственно, а не через транзистор. Еще одним примером устройства другого типа, содержащего полупроводниковый слой, является датчик, например датчик излучения.

Далее, приведенное описание относится к примеру, в котором проводники затвора и истока находятся на различных уровнях в пределах массива тонкопленочных транзисторов (ТПТ), причем проводники затвора или истока проходят к контактам чипа драйвера вокруг одного угла массива ТПТ. Однако описанная технология может использоваться также в комбинации с технологией, согласно которой проводники затвора или истока проходят к контактам чипа драйвера через участки между другими проводниками затвора и истока, находящимися в пределах данного массива на том же уровне.

Приведенное описание относится к примеру архитектуры устройства, в которой пиксельные проводники, заданные верхним проводящим слоем, соединены с соответствующими проводниками стока, заданными нижним проводящим слоем, через сквозные отверстия в проводниках затвора, а четвертый, экранирующий проводящий слой расположен между проводящим слоем, задающим проводники затвора, и проводящим слоем, задающим пиксельные проводники. Однако описанная технология применима и к другим архитектурам, в которых каждый проводник стока имеет контактную площадку, которая не находится под каким-либо проводником затвора и может быть соединена с соответствующим пиксельным проводником без необходимости в сквозном отверстии в проводнике затвора, и/или не требующим наличия четвертого, экранирующего проводящего слоя.

Специалисту в данной области будет очевидно, что, в дополнение к описанным модификациям, изобретение охватывает и другие модификации рассмотренного варианта.

Индивидуальные признаки изобретения раскрыты заявителем в представленном описании по отдельности и/или как комбинации двух или более признаков в достаточной степени для того, чтобы эти признаки или их комбинации могли быть практически осуществлены в целом с учетом знаний, которыми обладает любой специалист в соответствующей области, независимо от того, решают ли данные признаки или комбинации именно проблемы, рассмотренные в описании, и без внесения каких-либо ограничений в объем изобретения, определяемый формулой. При этом заявитель отмечает, что различные аспекты изобретения могут включать любые индивидуальные признаки или их комбинации.

Использование: для изготовления электронного устройства. Сущность изобретения заключается в том, что способ изготовления электронных устройств включает формирование на общей подложке одной или более серий многослойных электронных устройств с последующим разделением многослойных электронных устройств одно от другого; при этом каждое из указанных устройств содержит один или более слоев органического материала, при этом способ включает нанесение единственного или каждого из указанных слоев в виде слоя, имеющего протяженность по меньшей мере от одного конца одной или более серий устройств до противоположного конца одной или более серий устройств, причем указанные устройства содержат по меньшей мере три проводящих слоя, расположенных на соответствующих уровнях, и способ дополнительно включает создание одной или более проводящих перемычек между одной или более частями верхнего проводящего слоя в периферийной области и одной или более частями промежуточного проводящего слоя, смещенными внутрь относительно указанной периферийной области, через одну или более частей нижнего проводящего слоя, расположенных между указанной периферийной областью и областью, смещенной внутрь относительно периферийной области. Технический результат: обеспечение возможности снижения частоты появления дефектов в устройствах, содержащих органические материалы. 3 н. и 8 з.п. ф-лы, 4 ил.

1. Способ изготовления электронных устройств, включающий формирование на общей подложке одной или более серий многослойных электронных устройств с последующим разделением многослойных электронных устройств одно от другого; при этом каждое из указанных устройств содержит один или более слоев органического материала, при этом способ включает нанесение единственного или каждого из указанных слоев в виде слоя, имеющего протяженность по меньшей мере от одного конца одной или более серий устройств до противоположного конца одной или более серий устройств, причем указанные устройства содержат по меньшей мере три проводящих слоя, расположенных на соответствующих уровнях, и способ дополнительно включает создание одной или более проводящих перемычек между одной или более частями верхнего проводящего слоя в периферийной области и одной или более частями промежуточного проводящего слоя, смещенными внутрь относительно указанной периферийной области, через одну или более частей нижнего проводящего слоя, расположенных между указанной периферийной областью и областью, смещенной внутрь относительно периферийной области.

2. Способ по п. 1, в котором каждое электронное устройство содержит массив транзисторов, при этом один или более слоев органического материала, наносимых в виде одного или более непрерывных слоев, содержит один или более из следующих слоев: полупроводниковый слой, задающий полупроводниковые каналы транзисторов; диэлектрический слой, образующий диэлектрик затворов транзисторов, и один или более изоляторных слоев, нанесенных между проводящими слоями.

3. Способ по п. 1, в котором электронные устройства содержат по меньшей мере один проводящий слой, задающий массив проводников, активируемых через соответствующие выходные терминалы одного или более чипов драйвера, а способ включает формирование контактов для указанных одного или более чипов драйвера с локализацией указанных контактов поверх одного или более слоев органического материала, наносимых в виде непрерывных слоев, при этом указанные контакты связаны с соответствующими проводниками указанного массива через указанные один или более слоев органического материала.

4. Способ по п. 1, дополнительно включающий формирование в указанной периферийной области контактной площадки для обеспечения проводящего соединения между верхним проводящим слоем и компонентом оптической среды; и

зажатие указанной контактной площадки между указанным компонентом оптической среды и верхним проводящим слоем.

5. Способ по п. 1, в котором верхний проводящий слой задает контакты затвора и истока для массива транзисторов, а одна или более частей указанного промежуточного проводящего слоя содержат один или более проводников затвора, образующих электроды затвора для указанного массива транзисторов, и/или один или более проводников истока, образующих электроды истока для массива транзисторов.

6. Способ по любому из предыдущих пунктов, дополнительно включающий:

формирование по меньшей мере одного закорачивающего проводника, связывающего группу проводников, расположенных в проводящем слое под указанными одним или более слоями органического материала, нанесенными в виде непрерывных слоев;

формирование по меньшей мере одной межслоевой проводящей перемычки между указанным закорачивающим проводником и контактом, сформированным поверх указанных одного или более слоев органического материала, через указанные один или более слоев, нанесенных в виде непрерывных слоев, и

осуществление электрического тестирования через указанный контакт с последующим изолированием закорачивающего проводника от указанной группы проводников путем удаления одной или более частей указанного проводящего слоя и одной или более частей одного или более слоев органического материала, расположенных поверх указанных одной или более частей проводящего слоя.

7. Способ по п. 2, в котором указанные одна или более частей верхнего проводящего слоя в периферийной области содержат контакты затвора для указанного массива транзисторов, указанные одна или более частей промежуточного проводящего слоя, смещенные внутрь относительно периферийной области, содержат проводники затвора, образующие электроды затвора для указанного массива транзисторов, а указанные одна или более частей нижнего проводящего слоя, расположенных между указанной периферийной областью и областью, смещенной внутрь относительно периферийной области, содержат продолжения проводников затвора.

8. Способ по любому из пп. 1-5, в котором по меньшей мере три проводящих слоя и одно или более продолжение проводника состоят из металла или сплава.

9. Способ изготовления электронных устройств, включающий формирование на общей подложке одной или более серий многослойных электронных устройств с обеспечением областей между соседними устройствами в пределах серии и последующее разделение многослойных электронных устройств одно от другого и от указанных областей между соседними устройствами в пределах серии; при этом каждое из указанных устройств содержит один или более слоев органического материала, при этом способ включает нанесение единственного или каждого из указанных слоев в виде слоя, имеющего протяженность по меньшей мере от одного конца одной или более серий устройств до противоположного конца одной или более серий устройств, и покрытие указанных областей между соседними устройствами в пределах серии.

10. Способ по п. 9, в котором каждое электронное устройство содержит массив транзисторов, при этом один или более слоев органического материала, наносимых в виде одного или более непрерывных слоев, содержит один или более из следующих слоев: диэлектрический слой, образующий диэлектрик затворов транзисторов, и один или более изоляторных слоев, нанесенных между проводящими слоями.

11. Способ изготовления электронных устройств, включающий формирование на общей подложке одной или более серий многослойных электронных устройств с последующим разделением многослойных электронных устройств одно от другого; при этом каждое из указанных устройств содержит один или более слоев органического материала, при этом способ включает нанесение единственного или каждого из указанных слоев в виде слоя, имеющего протяженность по меньшей мере от одного конца одной или более серий устройств до противоположного конца одной или более серий устройств; формирование по меньшей мере одного закорачивающего проводника, связывающего группу проводников, расположенных в проводящем слое под указанными одним или более слоями органического материала, нанесенными в виде непрерывных слоев; формирование по меньшей мере одной межслоевой проводящей перемычки между указанным закорачивающим проводником и контактом, сформированным поверх указанных одного или более слоев органического материала, через указанные один или более слоев, нанесенных в виде непрерывных слоев; и осуществление электрического тестирования через указанный контакт с последующим изолированием закорачивающего проводника от указанной группы проводников путем удаления одной или более частей указанного проводящего слоя и одной или более частей одного или более слоев органического материала, расположенных поверх указанных одной или более частей проводящего слоя.

| US 20080266514 A1, 30.10.2008 | |||

| US 7612375 B2, 03.11.2009 | |||

| СПОСОБ ВЫРАБОТКИ КОНСЕРВОВ "КОТЛЕТЫ РУБЛЕНЫЕ ИЗ ТЕТЕРЕВА С ГАРНИРОМ И КРАСНЫМ ОСНОВНЫМ СОУСОМ" | 2012 |

|

RU2485828C1 |

| US 20090152532 A1, 18.06.2009 | |||

| US 7585697 B2, 08.09.2009. | |||

Авторы

Даты

2018-11-19—Публикация

2014-10-07—Подача