Устройство, содержащее множество ТПТ (тонкопленочных транзисторов), обычно имеет структурированный проводящий слой, образующий цепи электродов истока и цепи электродов стока для множества ТПТ, а также полупроводниковый слой, обеспечивающий соответствующие полупроводниковые каналы между соответствующей комбинацией электродов истока и стока для каждого ТПТ. Цепь электрода затвора, имеющая емкостную связь с полупроводниковым слоем, используется для переключения полупроводниковых каналов между двумя или более уровнями проводимости.

При этом может потребоваться уменьшение токов утечки между цепями электродов истока и стока в областях, лежащих за пределами области цепи электрода затвора.

Один из способов уменьшения таких токов утечки использует осаждение сплошного слоя полупроводникового материала на цепи электродов истока/стока для всего множества транзисторов с последующим удалением частей этого полупроводникового слоя, например, при помощи лазерной абляции на одном или более участках за пределами полупроводниковых каналов.

Другой способ уменьшения таких токов утечки использует осаждение полупроводникового слоя в виде множества островков, каждый из которых обеспечивает полупроводниковый канал для соответствующего ТПТ, однако, не соединяется в полупроводниковом слое с каким-либо из других островков.

Задачей изобретения является обеспечение нового способа уменьшения токов утечки.

Настоящее изобретение обеспечивает способ управления устройством, содержащим структурированный проводящий слой, образующий цепь электрода истока и цепь электрода стока для множества транзисторов, полупроводниковый слой, обеспечивающий соответствующий полупроводниковый канал для каждого транзистора между цепью электрода истока и цепью электрода стока, а также цепь электрода затвора, покрывающую полупроводниковые каналы множества транзисторных устройств для переключения полупроводниковых каналов между двумя или более уровнями проводимости, при этом указанный способ содержит применение одного или более дополнительных проводников, независимых от указанной цепи электрода затвора, чтобы обеспечить емкостное индуцирование уменьшения проводимости указанных одной или более областей указанного полупроводникового слоя за пределами указанных полупроводниковых каналов.

В одном варианте осуществления указанные одна или более областей полупроводникового слоя включают в себя одну или более областей за пределами области цепи электрода затвора.

В одном варианте осуществления указанные одна или более областей включают в себя одну или более областей, на которых цепи электродов истока и стока расположены наиболее близко друг к другу за пределами области цепи электрода затвора.

В одном варианте осуществления способ дополнительно содержит емкостное индуцирование уменьшения проводимости указанных одной или более областей указанного полупроводникового слоя при одновременном использовании указанной цепи электрода затвора для емкостного индуцирования изменения проводимости одного или более указанных полупроводниковых каналов.

В одном варианте осуществления указанные один или более дополнительных проводников расположены на противоположной стороне структурированного проводящего слоя относительно цепи электрода затвора.

В одном варианте осуществления указанные один или более дополнительных проводников содержат проводящий слой, проходящий, по существу, по всей области между цепями электрода стока и электрода истока для множества транзисторов за исключением полупроводниковых каналов.

Кроме того, обеспечено управляющее устройство, содержащее: первый структурированный проводящий слой, образующий цепь электрода истока и цепь электрода стока для множества транзисторных устройств, полупроводниковый слой, обеспечивающий соответствующий полупроводниковый канал для каждого транзисторного устройства между цепью электрода истока и цепью электрода стока одного транзисторного устройства, второй структурированный проводящий слой, образующий цепь электрода затвора для емкостной связи с полупроводниковыми каналами множества транзисторных устройств и переключения полупроводниковых каналов между двумя или более уровнями проводимости, при этом указанный полупроводниковый слой проходит за пределами указанных полупроводниковых каналов к другим участкам между указанной цепью электрода истока и цепью электрода стока, при этом устройство содержит также третий структурированный проводящий слой, расположенный на противоположной стороне полупроводникового слоя относительно второго структурированного проводящего слоя и проходящий, по существу, по всей области между цепями электрода истока и электрода стока для множества транзисторов за исключением полупроводниковых каналов.

Ниже раскрывается вариант осуществления настоящего изобретения, представленный только в качестве примера, со ссылками на прилагаемые чертежи, на которых показаны:

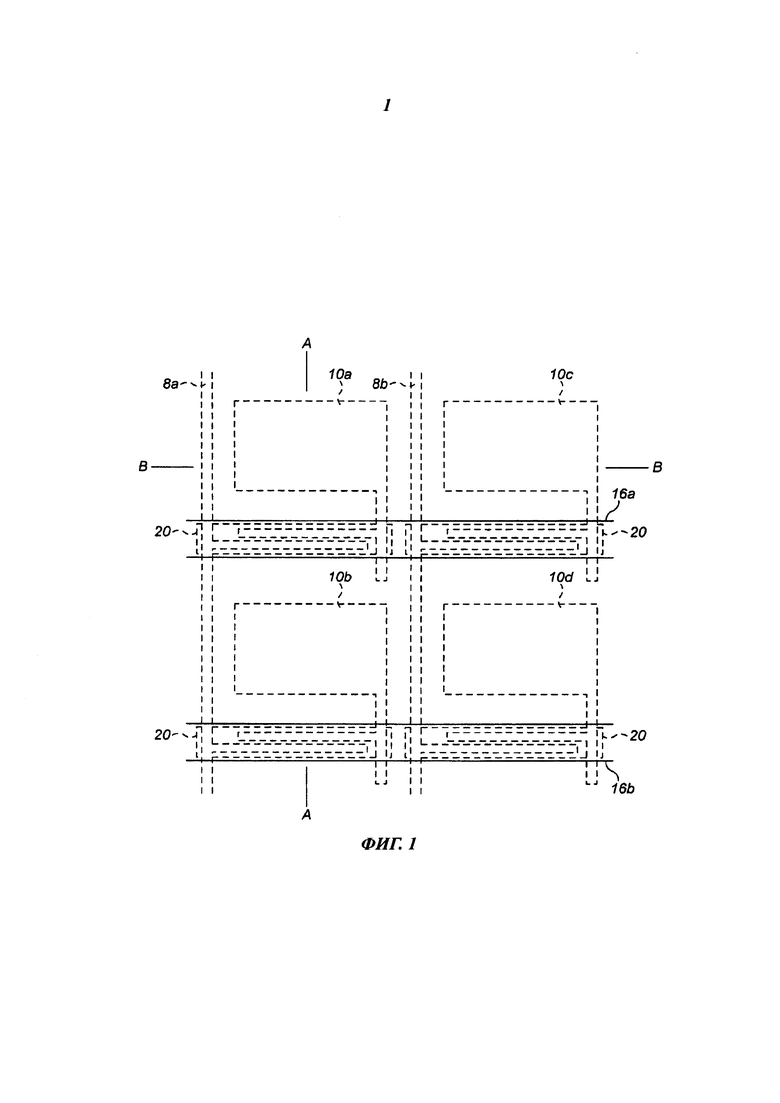

фиг. 1 - вид сверху устройства согласно первому варианту осуществления настоящего изобретения, и

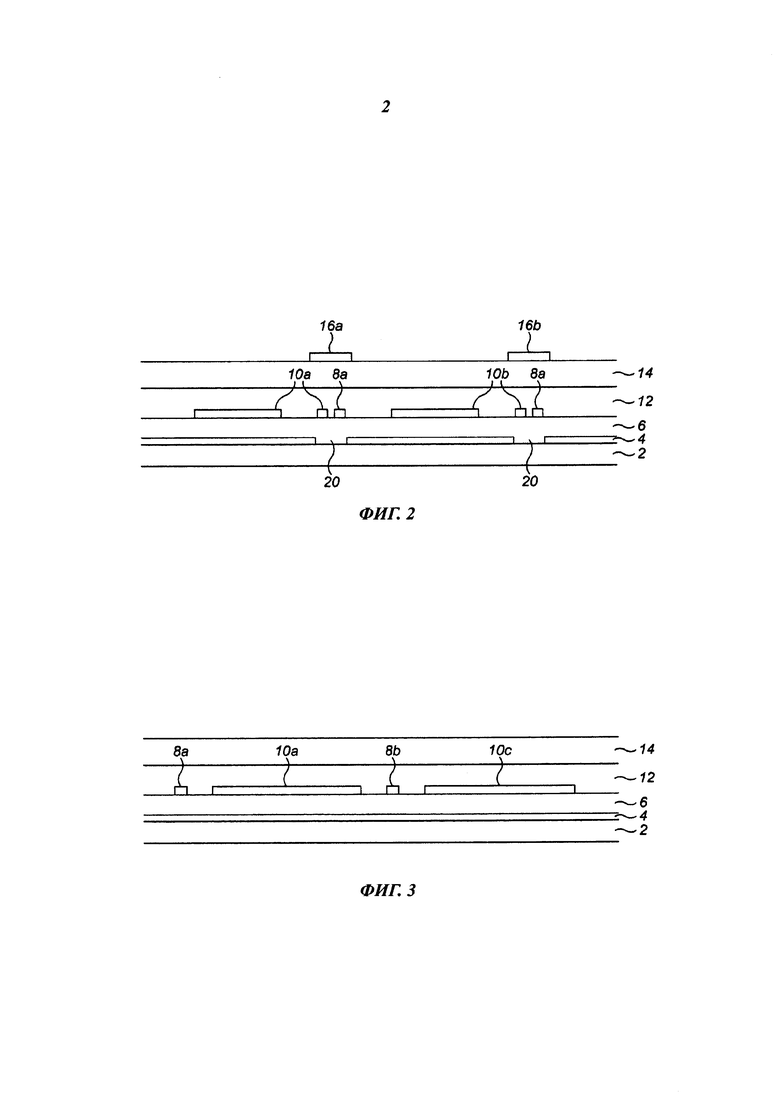

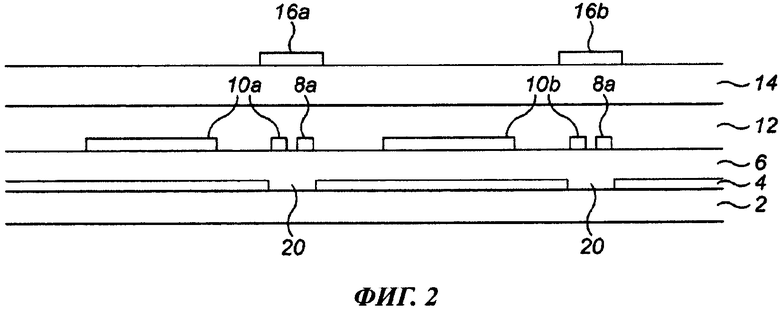

фиг. 2 и 3 - виды в поперечном сечении устройства с фиг. 1 по осям А и В, соответственно.

На фиг. 1 показан вид сверху части матрицы ТПТ согласно одному варианту осуществления настоящего изобретения. Для простоты на фиг. 1 показано только четыре ТПТ, однако, например, матрица ТПТ для управления оптическим дисплеем с большим количеством пикселей обычно содержит тысячи ТПТ.

Структурированный проводящий слой на промежуточном уровне образует цепи электродов истока и стока для матрицы ТПТ. Цепь электрода истока содержит множество независимых проводников 8а, 8b электродов истока, электрический потенциал которых можно регулировать независимо друг от друга. Каждый проводник 8а, 8b электрода истока образует электроды истока соответствующего ряда ТПТ и адресную шину для этого ряда ТПТ. Цепь электрода стока содержит множество независимых проводников 10а, 10b, 10 с, 10d электродов стока. Каждый из независимых проводников 10 электродов стока образует электрод стока соответствующего ТПТ и обеспечивает проводящий путь к другим элементам матрицы ТПТ, в частности, к соответствующему пиксельному электроду на более высоком уровне. Для большей ясности пиксельные электроды и межслойные соединения между пиксельными электродами и проводниками электродов стока на чертежах не показаны.

На цепи электродов истока и стока нанесен сплошной слой 12 полупроводникового материала, который образует полупроводниковые каналы между электродами истока и стока каждого ТПТ. Полупроводниковые каналы представляют собой части полупроводникового слоя, соединяющие участки цепей электродов истока и стока, которые специально расположены очень близко друг к другу (расстояние составляет, например, 20 микрон или менее), чтобы получить электроды истока и стока соответствующих ТПТ. Полупроводниковый слой 12 может быть нанесен, по существу, на всей области, занимаемой ТПТ, и более конкретно - на всех областях между цепями электродов истока и цепями электродов стока. Диэлектрический слой 14 затвора расположен поверх полупроводникового слоя 12. Еще один структурированный проводящий слой расположен на противоположной стороне диэлектрического слоя 14 затвора относительно полупроводникового слоя 12 и образует матрицу независимых затворных шин 16а, 16b, каждая из которых проходит над полупроводниковыми каналами соответствующего столбца ТПТ. Электрический потенциал каждой затворной шины 16 можно регулировать независимо от других, при этом затворные шины 16 используются для переключения полупроводниковых каналов соответствующего столбца ТПТ между двумя или более уровнями проводимости. Так, например, затворные шины 16 используются для переключения соответствующих столбцов ТПТ между состояниями включения и выключения.

На противоположной стороне структурированного проводящего слоя образующего цепи электродов истока и стока относительно полупроводникового слоя 12 нанесен дополнительный диэлектрический слой 6 и третий структурированный проводящий слой 4, имеющий емкостную связь с полупроводниковым слоем 12 через указанный дополнительный диэлектрический слой 6. Опорой для всех вышеуказанных слоев является подложка 2. Третий структурированный проводящий слой 4 является первым из вышеуказанных трех структурированных проводящих слоев, сформированных в примере, показанном на чертежах. Этот третий структурированный проводящий слой содержит окна 20, соответствующие местоположению каждого полупроводникового канала матрицы ТПТ. Указанный третий структурированный проводящий слой 4 проходит, по существу, по всей области полупроводникового слоя между цепями электродов истока и стока для множества транзисторов за исключением полупроводниковых каналов. В частности, третий структурированный проводящий слой проходит через все и каждую области, где цепи электродов истока и стока расположены наиболее близко друг к другу за пределами областей, покрываемых затворными шинами 16.

Функция матрицы ТПТ включает изменение электрического потенциала затворных шин 16 (и тем самым переключение полупроводниковых каналов ТПТ между двумя или более уровнями проводимости) при сохранении электрического потенциала третьего структурированного проводящего слоя на уровне, по существу, постоянной величины, что приводит к емкостному индуцированию уменьшения проводимости в частях полупроводникового слоя 12, покрываемых третьим структурированным проводящим слоем 4. Такое уменьшение проводимости этих частей служит подавлению токов утечки, которые могут вызывать нежелательные перекрестные помехи между ТПТ и нежелательную утечку заряда накопительных конденсаторов, между цепями 8, 10 электродов истока и стока через полупроводниковый слой 12, а также подавлению токов утечки между проводниками электродов истока (адресные шины истока) в особенности на периферии пиксельной матрицы, при этом указанное подавление является полезным для уменьшения потребления мощности.

Если указанный полупроводниковый материал представляет собой, например, полупроводник р-типа, то приложение высокого положительного напряжения смещения к третьему структурированному проводящему слою вызывает уменьшение проводимости полупроводникового материала. Высокое положительное напряжение, приложенное к третьему структурированному проводящему слою 4, полностью исключает наличие свободных носителей заряда в полупроводнике и, таким образом, уменьшает проводимость полупроводника 12. Отношение (i) этого положительного напряжения к (ii) толщине диэлектрического слоя 6, расположенного между третьим структурированным проводящим слоем 4 и полупроводниковым слоем 12, выбирается такого же порядка, как и отношение (iii) напряжения (Vgate_off), прилагаемого к затворным шинами 16 для переключения соответствующего ряда ТПТ в непроводящее состояние к (iv) толщине затворного диэлектрического слоя, расположенного между цепями 8, 10 электродов истока/стока и затворными шинами 16.

В отличие от проводников 8, 10, электродов истока и стока третий структурированный проводящий слой 4 является сплошным на всех ТПТ матрицы, при этом требуется только один контакт с третьим структурированным проводящим слоем 4 для приложения необходимого электрического потенциала, чтобы подавлять вышеуказанные токи утечки между проводниками на уровне исток-сток при помощи полупроводникового слоя, по существу, на всех участках за пределами области цепи 16 электрода затвора.

При этом электрическая мощность, потребляемая вследствие приложения вышеуказанного высокого положительного напряжения к третьему структурированному проводящему слою 4, является низкой в связи с отсутствием прямого тока, проходящего в третьем структурированном проводящем слое 4, и отсутствием переключения напряжения, приложенного к третьему структурированному проводящему слою 4 во время работы матрицы ТПТ.

Уровень, на котором нанесен третий структурированный проводящий слой 4, может также содержать один или более независимых проводников за пределами поверхности матрицы ТПТ, которые служат в качестве электродов нижнего затвора для дополнительных ТПТ с нижним затвором, образующих логические схемы для поддержки работы матрицы ТПТ.

В примере, раскрытом выше и показанном на чертежах, третий структурированный проводящий слой находится на той же стороне, что и проводящий слой, образующий проводники истока и стока. Согласно одному из измененных вариантов третий структурированный проводящий слой наносится на противоположную сторону подложки относительно проводников истока и стока, при этом опорная подложка 2 дополнительно функционирует в качестве диэлектрика между третьим структурированным проводящим слоем и полупроводниковым слоем.

В примере, раскрытом выше и показанном на чертежах, матрица ТПТ представляет собой матрицу ТПТ с верхним затвором. Однако такой же способ в равной степени может быть использован для матриц ТПТ с нижним затвором, в этом случае третий структурированный проводящий слой является последним из трех формируемых структурированных проводящих слоев и наносится поверх структурированного проводящего слоя, образующего проводники истока и стока.

Для специалистов в данной области техники очевидно, что кроме модификаций, в явном виде указанных выше, в пределах объема изобретения могут иметь место различные другие модификации описанного варианта осуществления.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ УМЕНЬШЕНИЯ НЕЖЕЛАТЕЛЬНОЙ ЕМКОСТНОЙ СВЯЗИ В ТРАНЗИСТОРНОМ УСТРОЙСТВЕ | 2014 |

|

RU2710905C1 |

| ВЫРАВНИВАЮЩИЙ СЛОЙ | 2014 |

|

RU2679270C2 |

| РАЗВОДКА МАТРИЦЫ ТРАНЗИСТОРОВ | 2014 |

|

RU2660318C2 |

| ЭЛЕКТРОННОЕ УСТРОЙСТВО, СОДЕРЖАЩЕЕ ОРГАНИЧЕСКИЕ МАТЕРИАЛЫ | 2014 |

|

RU2672778C2 |

| ПОЛУПРОВОДНИКОВОЕ УСТРОЙСТВО | 2010 |

|

RU2501117C2 |

| ПЕРЕКЛЮЧАЮЩИЙ ТПТ И СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ | 2013 |

|

RU2634088C2 |

| РЕКОНФИГУРИРУЕМЫЙ ЦВЕТНОЙ ЭКРАН | 2014 |

|

RU2671911C2 |

| ПОЛЕВОЙ ТРАНЗИСТОР | 2005 |

|

RU2358355C2 |

| ИНТЕГРАЛЬНАЯ СХЕМА С МАТРИЦЕЙ СЕНСОРНЫХ ТРАНЗИСТОРОВ, СЕНСОРНОЕ УСТРОЙСТВО И СПОСОБ ИЗМЕРЕНИЯ | 2013 |

|

RU2650087C2 |

| РЕГУЛИРОВАНИЕ ПОРОГОВОГО НАПРЯЖЕНИЯ ЗА СЧЕТ МОДИФИКАЦИИ ДИЭЛЕКТРИЧЕСКОЙ МНОГОСЛОЙНОЙ ЗАТВОРНОЙ СТРУКТУРЫ | 2010 |

|

RU2538356C2 |

Группа изобретений относится к области полупроводниковых устройств. Способ подавления токов утечки в устройстве, содержащем структурированный проводящий слой, образующий цепь электрода истока и цепь электрода стока для множества транзисторов, полупроводниковый слой, обеспечивающий соответствующий полупроводниковый канал для каждого транзистора между цепью электрода истока и цепью электрода стока, и цепь электрода затвора, покрывающую полупроводниковые каналы множества транзисторных устройств для переключения полупроводниковых каналов между двумя или более уровнями проводимости, при этом указанный способ содержит применение одного или более дополнительных проводников, независимых от указанной цепи электрода затвора, для емкостного индуцирования уменьшения проводимости указанных одной или более областей указанного полупроводникового слоя за пределами указанных полупроводниковых каналов. Технический результат – уменьшение токов утечки. 2 н. и 3 з.п. ф-лы, 3 ил.

1. Способ подавления токов утечки в устройстве, содержащем структурированный проводящий слой, образующий цепь электрода истока и цепь электрода стока для матрицы транзисторов, содержащей ряды и столбцы транзисторов; полупроводниковый слой, образующий соответствующий полупроводниковый канал для каждого транзистора между цепью электрода истока и цепью электрода стока; и цепь электрода затвора, покрывающую полупроводниковые каналы матрицы транзисторов, для переключения полупроводниковых каналов между двумя или более уровнями проводимости, при этом способ содержит применение дополнительного проводящего слоя для емкостного индуцирования уменьшения проводимости одной или более областей указанного полупроводникового слоя за пределами указанных полупроводниковых каналов, причем указанный дополнительный проводящий слой расположен на противоположной стороне структурированного проводящего слоя относительно цепи электрода затвора, является сплошным на всех транзисторах матрицы и содержит окна в местоположениях каждого полупроводникового канала матрицы транзисторов.

2. Способ по п. 1, в котором указанная одна или более область полупроводникового слоя содержат одну или более областей за пределами области цепи электрода затвора.

3. Способ по п. 2, в котором указанные одна или более областей включают в себя одну или более областей, где цепи электродов истока и стока расположены наиболее близко друг к другу за пределами области цепи электрода затвора.

4. Способ по любому из п.п. 1-3, содержащий: емкостное индуцирование уменьшения проводимости указанных одной или более областей указанного полупроводникового слоя при одновременном использовании указанной цепи электрода затвора для емкостного индуцирования изменения проводимости одного или более указанных полупроводниковых каналов.

5. Устройство на матрице из тонкопленочных транзисторов, содержащее первый структурированный проводящий слой, образующий цепь электрода истока и цепь электрода стока для матрицы транзисторов, содержащей ряды и столбцы транзисторов; полупроводниковый слой, образующий соответствующий полупроводниковый канал для каждого транзистора между цепью электрода истока и цепью электрода стока одного и того же транзистора; второй структурированный проводящий слой, образующий цепь электрода затвора для емкостной связи с полупроводниковыми каналами матрицы транзисторов и переключения полупроводниковых каналов между двумя или более уровнями проводимости, причем указанный полупроводниковый слой проходит за пределами указанных полупроводниковых каналов к другим участкам между указанной цепью электрода истока и цепью электрода стока, при этом устройство дополнительно содержит третий структурированный проводящий слой, расположенный на противоположной стороне полупроводникового слоя относительно второго структурированного проводящего слоя, причем этот третий структурированный проводящий слой является сплошным на всех транзисторах матрицы и содержит окна в местоположениях каждого полупроводникового канала матрицы транзисторов.

| СПОСОБ БЕЗРАЗБОРНОГО ВОССТАНОВЛЕНИЯ СОПРЯЖЕНИЙ ДЕТАЛЕЙ ЦИЛИНДРО-ПОРШНЕВОЙ ГРУППЫ ДВИГАТЕЛЯ ВНУТРЕННЕГО СГОРАНИЯ | 1990 |

|

RU2015379C1 |

| WO 0115233 A1, 01.03.2001 | |||

| US 4746961 A1, 24.05.1988 | |||

| ЭЛЕКТРОННОЕ ПЕРЕКЛЮЧАЮЩЕЕ УСТРОЙСТВО И СПОСОБ ИЗГОТОВЛЕНИЯ ЭТОГО УСТРОЙСТВА | 2008 |

|

RU2475893C2 |

Авторы

Даты

2018-08-29—Публикация

2014-07-01—Подача