Уровень техники

Матрица транзисторов (транзисторная матрица) в типичном варианте содержит массив проводников истока, формирующих электроды истока для транзисторов, массив проводников стока, формирующих электроды стока для транзисторов, и массив проводников затвора, формирующих электроды затвора для транзисторов.

Согласно одной технологии, для обеспечения соединений проводников истока и затвора с соответствующими выходными терминалами одного или более чипов драйвера, проводники истока заканчиваются на одном краю массива транзисторов, а проводники затвора - на другом его краю. При этом либо размещают отдельные чипы драйвера истока и затвора у соответствующих краев массива, либо размещают чипы драйвера истока и затвора у общего края массива и формируют проводящие треки, проходящие вокруг двух краев матрицы к проводникам затвора или истока, заканчивающихся у края, отличного от края, у которого расположен чип драйвера.

Раскрытие изобретения

Авторы настоящего изобретения идентифицировали существование проблемы улучшения разводки проводников истока/затвора с подведением к одному или более чипам драйвера.

Соответственно, предлагается устройство, содержащее массив транзисторов. Более конкретно, устройство по изобретению содержит: первый проводящий слой, находящийся на первом уровне и задающий множество первых проводников, образующих электроды затвора или истока для указанного массива транзисторов, и второй проводящий слой, находящийся на втором уровне и задающий множество вторых проводников, образующих другие электроды затвора или истока для указанного массива транзисторов. При этом второй проводящий слой дополнительно задает проводники разводки, расположенные в одной или более зонах между вторыми проводниками, а каждый проводник разводки соединен посредством одной или более межслоевых проводящих перемычек с соответствующим первым проводником.

Согласно одному варианту первые проводники образуют электроды истока для массива транзисторов, а вторые проводники образуют электроды затвора для массива транзисторов.

Согласно другому варианту каждый первый проводник ассоциирован с одним или более столбцами массива транзисторов, а каждый второй проводник ассоциирован с одной или более строками массива транзисторов.

Согласно еще одному варианту первые проводники образуют электроды затвора для массива транзисторов, а вторые проводники образуют электроды истока для массива транзисторов.

Согласно следующему варианту вторые проводники и проводники разводки заканчиваются у одного и того же края массива транзисторов.

Согласно одному варианту устройство дополнительно содержит чип драйвера, находящийся у указанного края массива транзисторов и содержащий выходные терминалы истока и затвора. При этом порядок следования выходных терминалов совпадает с порядком следования вторых проводников и проводников разводки на указанном крае массива транзисторов.

Согласно другому варианту первый уровень расположен ниже второго уровня.

Согласно следующему варианту межслоевые проводящие перемычки образуют часть однородного массива межслоевых соединений (перемычек), содержащего также межслоевые соединения, не соединенные ни с одним из первых проводников.

Краткое описание чертежей

Далее, со ссылками на прилагаемые чертежи, будет описан, только в качестве примера, вариант способа согласно изобретению.

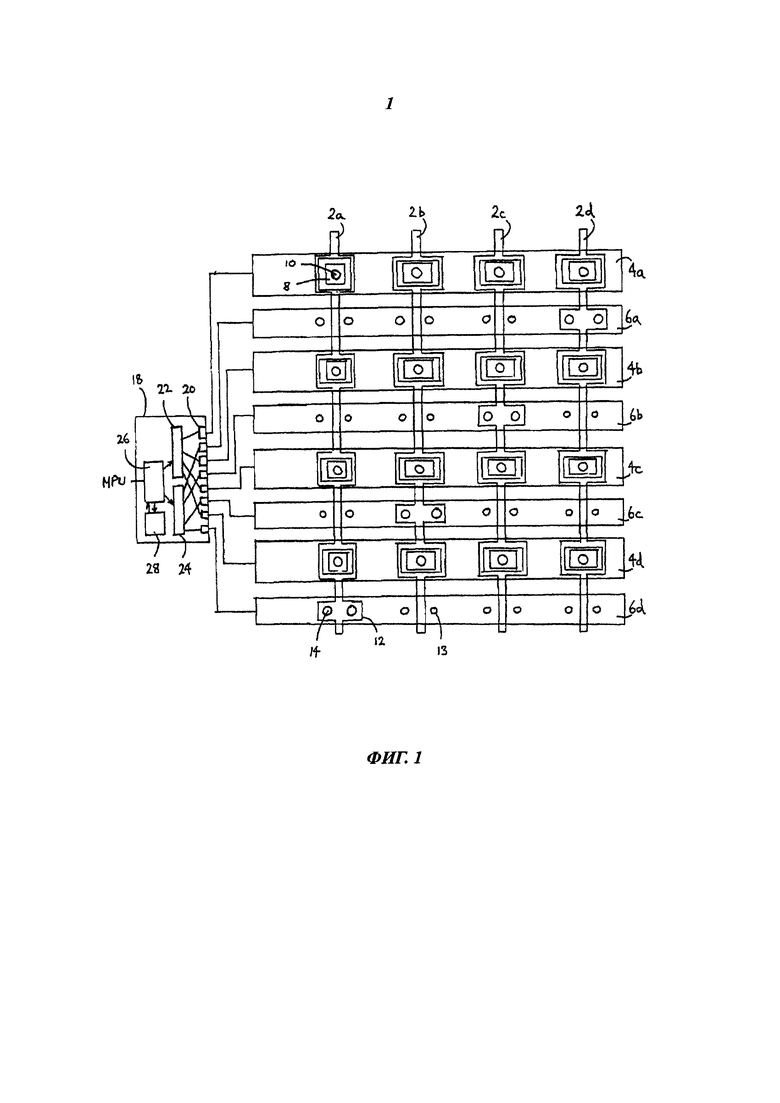

На фиг. 1 схематично, на виде в плане представлен пример конфигурации проводников затвора и истока для массива тонкопленочных транзисторов (ТПТ).

На фиг. 2 пример конфигурации проводников затвора и истока для массива ТПТ схематично изображен в сечении.

Фиг. 3 иллюстрирует вариант скрещивания проводников затвора и проводников разводки.

Осуществление изобретения

Для облегчения понимания изобретения на фиг. 1 и 2 проиллюстрирован пример конфигурации проводников затвора и истока для небольшого (4×4) массива ТПТ; однако тот же тип конфигурации применим и к намного более крупным транзисторным матрицам, в частности к транзисторным матрицам, содержащим более миллиона транзисторов. Примеры возможных модификаций (не выходящих за пределы изобретения) для устройств, проиллюстрированных на чертежах, будут рассмотрены в конце данного описания.

Первый структурированный проводящий слой сформирован на несущей подложке 30. Несущая подложка может, например, содержать пластиковую пленку и выравнивающий слой, сформированный между этой пленкой и первым проводящим слоем, а также один или более дополнительных функциональных слоев (например, проводящих и/или изоляторных) между пластиковой пленкой и выравнивающим слоем и/или между выравнивающим слоем и первым структурированным проводящим слоем, и/или на стороне пластиковой пленки-подложки, противоположной по отношению к выравнивающему слою.

Первый структурированный проводящий слой структурирован таким образом, чтобы задать (i) массив 2а, 2b, 2с, 2d проводников истока, каждый из которых в этом примере образует электроды истока для соответствующего столбца транзисторов, и (ii) массив проводников 8 стока, каждый из которых образует электрод стока для соответствующего транзистора. Такое структурирование первого структурированного проводящего слоя может быть проведено, например, посредством технологии фотолитографии.

Поверх структурированного первого проводящего слоя, задающего проводники истока и стока 2, 8, сформирован полупроводниковый слой 32, который задает соответствующий полупроводниковый канал для каждого транзистора. Полупроводниковый слой 32 может представлять собой, например, полупроводник из органического полимера, нанесенный по жидкостной технологии (посредством флексографической печати и/или центрифугирования).

Поверх полупроводникового слоя 32 сформирован диэлектрический слой 34, который образует соответствующий диэлектрический затвор для каждого транзистора. Диэлектрический слой может, например, включать в себя один или более диэлектрических слоев из органического полимера.

Затем полупроводниковый слой 32 и диэлектрический слой 34 структурируют, чтобы сформировать одно или более сквозных отверстий, проходящих вниз к каждому проводнику 2 истока. Такое структурирование может быть проведено, например, посредством лазерной абляции. Этот процесс структурирования может также включать формирование избыточных сквозных отверстий во всех других соответствующих местах, под которыми не находится проводник 2 истока (или опорная площадка 12). Избыточные сквозные отверстия также заполняют проводящим материалом (во время нанесения второго проводящего слоя, который образует проводники 4 затвора и проводники 6 разводки), чтобы создать избыточные межслоевые соединения (перемычки) 13. Эти избыточные межслоевые перемычки не подсоединены ни к одному из проводников 2 истока, однако формирование однородного массива межслоевых перемычек 13, 14 по всей площади массива ТПТ может быть полезным в плане создания дисплея, имеющего однородные характеристики по всей площади массива ТПТ в случае, когда этот массив используется, в качестве части дисплейного устройства, для управления оптической средой.

Поверх структурированных диэлектрического слоя 34 и полупроводникового слоя 32 наносят проводящий материал, который заполняет каждое сквозное отверстие, образованное на описанной операции структурирования, и формирует второй проводящий слой, покрывающий диэлектрический слой 34.

Затем второй проводящий слой структурируют, чтобы задать (i) массив проводников 4 затвора, каждый из которых образует электроды затвора для соответствующей строки транзисторов, и (ii) массив проводников 6 разводки, параллельных проводникам 4 затвора, причем каждый проводник 6 расположен между двумя проводниками 4 затвора. Структурирование второго проводящего слоя задает также сквозные отверстия в проводниках 4 затвора, в местах, расположенных над центрами проводников 8 стока. Как было упомянуто, эти сквозные отверстия позволяют сформировать межслоевые проводящие перемычки 10 между проводниками 8 стока и соответствующими пиксельными проводниками 42, находящимися в верхней части устройства. Проводники 6 разводки сформированы там, где второй проводящий слой образует межслоевые проводящие перемычки, доходящие до проводников 2 истока. Каждый проводник 6 разводки связан с соответствующим проводником истока, например, посредством соответствующей пары межслоевых проводящих перемычек 14, образованных вторым проводящим слоем. Проводники 4 затвора и проводники 6 разводки совместно завершаются у одного и того же края массива транзисторов.

Каждый из проводников 2 истока, заданных первым структурированным проводящим слоем, сконфигурирован так, что он формирует соответствующую опорную площадку 12, имеющую относительно большую ширину в направлении, по существу, параллельном проводникам 6 разводки. Эти опорные площадки 12 облегчают формирование межслоевых проводящих перемычек 14, проходящих вниз от проводников 6 разводки до проводников 2 истока.

На фиг. 2 показана часть устройства в сечении плоскостью, проходящей через центральную линию одного из проводников 2 истока. Чтобы облегчить понимание изобретения, на фиг. 2 межслоевые проводящие перемычки 14 показаны проходящими вниз до части соответствующего проводника 2 истока, расположенной на его центральной линии.

Поверх второго структурированного проводящего слоя сформирован изоляторный слой 36, а поверх изоляторного слоя 36 сформирован третий проводящий слой 38. Третий проводящий слой 38 структурирован так, чтобы задать, по существу, непрерывный проводящий слой, в котором образованы сквозные отверстия, формирующие межслоевые проводящие перемычки 10, проходящие через второй и третий проводящие слои и доходящие от проводников 8 стока до соответствующих пиксельных проводников 42. Этот, третий проводящий слой функционирует как слой, экранирующий расположенные сверху пиксельные проводники 42 от влияния электрических потенциалов, возникающих на всех нижележащих проводниках, включая проводники 4 затвора и проводник 6 разводки. Поверх третьего проводящего слоя сформирован еще один изоляторный слой 40. Изоляторные слои 36, 40 могут быть, например, слоями из органического полимера. После этого изоляторные слои 36, 40, диэлектрический слой 34 и полупроводниковый слой 32 структурируют так, чтобы задать сквозные отверстия, проходящие вниз до каждого проводника 8 стока через сквозные отверстия, сформированные в третьем проводящем слое, и через сквозные отверстия, сформированные в проводниках 4 затвора. Эти сквозные отверстия имеют диаметр, меньший, чем у сквозных отверстий в проводниках 4 затвора и в третьем проводящем слое, что позволяет избежать любого электрического замыкания между межслоевыми проводящими перемычками 10 и третьим проводящим слоем 38 и/или проводниками 4 затвора.

Поверх изоляторного слоя 40 наносят проводящий материал, который заполняет сквозные отверстия, сформированные в изоляторных слоях 36, 40, в диэлектрическом слое 34 и в полупроводниковом слое 32, и образует четвертый проводящий слой, расположенный над изоляторным слоем 40. Затем этот, четвертый проводящий слой структурируют, чтобы сформировать массив пиксельных проводников 42, каждый из которых ассоциирован с соответствующим проводником 8 стока. Пиксельные проводники 42 могут, например, использоваться для управления оптической средой (не изображена), находящейся над четвертым проводящим слоем.

Примеры материалов для первого, второго, третьего и четвертого проводящих слоев включают металлы и сплавы.

Чип 18 драйвера затвора/истока прикреплен к подложке 30 у того края транзисторной матрицы, где заканчиваются проводники 4 затвора и проводники 6 разводки. Каждый проводник затвора и проводник разводки подсоединены к соответствующему выходному терминалу 20 чипа драйвера. В этом примере чип 18 драйвера сконфигурирован так, что порядок расположения выходных терминалов 20 соответствует порядку проводников 4 затвора и проводников 6 разводки. Это позволяет избежать любых взаимных пересечений проводников 4 затвора и проводников 6 разводки и позволяет поместить чип 18 драйвера ближе к транзисторной матрице.

Единственная интегральная схема (ИС) чипа 18 драйвера содержит блок 22 драйвера затвора, блок 24 драйвера истока, логический блок 26 и память 28. В функции логического блока 26 входят: обеспечение связи между ИС чипа 18 драйвера и основным процессором MPU; передача данных в память 28 и из нее; координация сигналов, подаваемых блоками драйвера затвора и истока на проводники 4 затвора и проводники 6 разводки; управление переносом выходных данных в блок 24 драйвера истока. ИС чипа 18 может содержать и другие блоки.

В функции чипа 18 драйвера входят: (i) последовательное переключение строк транзисторов между выключенным и включенным состояниями путем приложения соответствующих напряжений к соответствующим проводникам 4 затвора и (ii) одновременная подача соответствующих входных напряжений на все проводники 2 истока (через проводники 6 разводки) для создания соответствующих электрических потенциалов на каждом пиксельном проводнике, ассоциированном со строкой транзисторов, находящихся во включенном состоянии.

В описанном примере между проводниками соответствующей пары проводников затвора находится один проводник 6 разводки, связанный с истоком. Примеры возможных модификаций включают: (а) формирование между парой проводников 4 затвора проводников 6 разводки для более чем одного проводника 2 истока/столбца транзисторов или формирование между парой проводников 6 разводки, связанных с истоком, проводников 4 затвора для более чем одной строки транзисторов. В более общем случае отношение количества проводников 4 затвора к количеству проводников 6 разводки может быть большим или меньшим 1. Согласно одному конкретному примеру между каждой парой проводников 4 затвора введены проводник 6 разводки для истока, соответствующего комплекту из двух столбцов транзисторов, чтобы обеспечить массиву ТПТ возможность иметь больше столбцов транзисторов, чем строк, и одновременно облегчить размещение чипа (чипов) драйвера для проводников истока и проводников затвора у одного и того же (более короткого) края массива ТПТ.

В описанном примере используется единственный комбинированный чип драйвера затвора/истока, у которого порядок следования выходных терминалов истока и затвора согласован с порядком следования проводников затвора и проводников разводки на краю массива ТПТ. Пример одной из модификаций предусматривает использование одного или более чипов драйвера, при этом выходные терминалы истока сгруппированы отдельно от выходных терминалов затвора. Фиг. 3 схематично иллюстрирует одну из технологий для обеспечения скрещивания проводников затвора и проводников разводки в такой модификации. Фиг. 3 относится к примеру проводников 6 разводки, соответствующих паре проводников 2 истока/столбцов транзисторов между парой проводников 4 затвора. Однако та же технология применима и к любому другому соотношению проводников 6 разводки истока (столбцов транзистора) и проводников 4 затвора (строк транзисторов). Первый проводящий слой, задающий проводники 2 истока (на фиг. 3 не изображен), задает также дополнительные проводники 7, отходящие наружу от края массива ТПТ и расположенные под формируемыми позднее частями проводников 4 затвора, ведущими наружу от того же края массива ТПТ. Диэлектрический слой 34, который выступает за этот край массива ТПТ, предотвращает электрическое закорачивание между дополнительными проводниками 7 и проводниками 4 затвора. Процесс формирования сквозных отверстий для межслоевых перемычек 14 включает формирование дополнительных сквозных отверстий в зонах над каждым дополнительным проводником 7; а процесс нанесения второго проводящего слоя включает также заполнение этих дополнительных сквозных отверстий, чтобы создать проводящие перемычки 9 между каждым проводником 6 разводки и соответствующим дополнительным проводником 7. На фиг. 3 показаны также межслоевые проводящие перемычки 11, которые соединяют каждый из дополнительных проводников 7 и проводников 4 затвора с уровнем, на котором расположены один или более чипов драйвера.

Приведенное описание относится к примеру массива транзисторов с верхним расположением затвора, но технология того же типа в равной степени применима и к массивам транзисторов с нижним расположением затвора, причем в этом случае порядок нанесения первого структурированного проводящего слоя, полупроводникового слоя 32, диэлектрического слоя 34 и второго структурированного проводящего слоя будет изменен на обратный, а в проводниках 4 затвора не будет выполняться никаких сквозных отверстий.

Приведенное описание относится к примеру кольцевой конструкции полупроводниковых каналов, в которой электрод стока для каждого транзистора окружен в проводящем слое истока-стока электродом истока для этого транзистора. Однако данная технология применима также к другим конструкциям полупроводникового канала, включая некольцевые конструкции таких каналов и другие типы кольцевых конструкций полупроводниковых каналов. Например, электроды истока и стока для каждого транзистора могут содержать гребенчатые структуры.

Далее, хотя приведенное описание относится к примеру использования единственного чипа драйвера для проводников затвора и истока, рассмотренная технология применима также, например, к устройствам, в которых для управления проводниками истока и затвора используются отдельные чипы драйвера. Приведенное описание относится также к примеру локализации проводников 6 разводки для истока между проводниками 4 затвора на одном уровне с проводниками затвора. Однако другой пример предусматривает локализацию проводников разводки для затвора между проводниками истока на том же уровне на одном уровне с проводниками истока и использование одной или более межслоевых проводящих перемычек между каждым проводником разводки для затвора и соответствующим проводником затвора.

Описанная технология устраняет необходимость в использовании (а) отдельных чипов драйвера для истока и затвора на различных краях транзисторной матрицы или (b) проводников разводки для истока или проводников затвора у двух краев транзисторной матрицы. Тем самым облегчается сокращение требуемой области подложки снаружи транзисторной матрицы. Кроме того, применительно к примеру использования комбинированного чипа драйвера, в котором порядок следования выходных терминалов истока и затвора совпадает с порядком следования проводников истока и затвора на краю массива ТПТ, дополнительным преимуществом является то, что все проводники, расположенные снаружи транзисторной матрицы, могут быть сформированы на одном уровне (т.е. в единственном проводящем слое).

Специалисту в данной области будет очевидно, что в дополнение к описанным модификациям изобретение охватывает и другие модификации описанного варианта.

Индивидуальные признаки изобретения раскрыты заявителем в представленном описании по отдельности и/или как комбинации двух или более признаков в достаточной степени для того, чтобы эти признаки или их комбинации могли быть практически осуществлены в целом с учетом знаний, которыми обладает любой специалист в соответствующей области, независимо от того, решают ли данные признаки или комбинации именно проблемы, рассмотренные в описании, и без внесения каких-либо ограничений в объем изобретения, определяемый формулой. При этом заявитель отмечает, что различные аспекты изобретения могут включать любые индивидуальные признаки или их комбинации.

Использование: для создания массива транзисторов. Сущность изобретения заключается в том, что устройство, представляющее собой массив транзисторов, содержит первый проводящий слой, находящийся на первом уровне и задающий множество первых проводников, образующих электроды затвора или истока для указанного массива транзисторов, и второй проводящий слой, находящийся на втором уровне и задающий множество вторых проводников, образующих другие электроды истока или затвора для указанного массива транзисторов, при этом второй проводящий слой дополнительно задает проводники разводки, расположенные в одной или более зонах между вторыми проводниками, а каждый проводник разводки соединен посредством одной или более межслоевых проводящих перемычек с соответствующим первым проводником. Технический результат обеспечение возможности создания дисплея с однородными характеристиками по всей площади массива. 7 з.п. ф-лы, 3 ил.

1. Устройство, представляющее собой массив транзисторов и содержащее

первый проводящий слой, находящийся на первом уровне и задающий множество первых проводников, образующих электроды затвора или истока для указанного массива транзисторов, и

второй проводящий слой, находящийся на втором уровне и задающий множество вторых проводников, образующих другие электроды истока или затвора для указанного массива транзисторов;

при этом второй проводящий слой дополнительно задает проводники разводки, расположенные в одной или более зонах между вторыми проводниками, а каждый проводник разводки соединен посредством одной или более межслоевых проводящих перемычек с соответствующим первым проводником.

2. Устройство по п. 1, в котором первые проводники образуют электроды истока для массива транзисторов, а вторые проводники образуют электроды затвора для массива транзисторов.

3. Устройство по п. 2, в котором каждый первый проводник ассоциирован с одним или более столбцами массива транзисторов, а каждый второй проводник ассоциирован с одной или более строками массива транзисторов.

4. Устройство по п. 1, в котором первые проводники образуют электроды затвора для массива транзисторов, а вторые проводники образуют электроды истока для массива транзисторов.

5. Устройство по п. 1, в котором вторые проводники и проводники разводки заканчиваются у одного и того же края массива транзисторов.

6. Устройство по п. 5, дополнительно содержащее чип драйвера, находящийся у указанного края массива транзисторов и содержащий выходные терминалы истока и затвора, причем порядок следования выходных терминалов совпадает с порядком следования вторых проводников и проводников разводки на указанном крае массива транзисторов.

7. Устройство по п. 1, в котором первый уровень расположен ниже второго уровня.

8. Устройство по любому из предыдущих пунктов, в котором межслоевые проводящие перемычки образуют часть однородного массива межслоевых перемычек, содержащего также межслоевые перемычки, не соединенные ни с одним из первых проводников.

| US 20100066967 A1, 18.03.2010 | |||

| US 20130093657 A1, 18.04.2013 | |||

| JP 11305681 A, 05.11.1999 | |||

| WO 2012069650 A1, 31.05.2012 | |||

| US 7291860 B2, 06.11.2007. |

Авторы

Даты

2018-07-05—Публикация

2014-10-07—Подача