ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

Изобретение относится к области технологии отображения, и, в частности, к матричной подложке и способу ее возбуждения, панели отображения и устройству отображения.

УРОВЕНЬ ТЕХНИКИ

С развитием технологии разрешение панели отображения становится выше и выше. То есть, количество пикселей на единице площади растет, что требует, чтобы размер каждого субпикселя становился меньше и меньше. Однако, вследствие ограничений процесса, размер каждого субпикселя не может быть уменьшен неограниченно.

Чтобы улучшить эффект отображения при заданном размере субпикселя, предложено устройство отображения в режиме Pentile. В устройстве отображения в режиме Pentile субпиксели некоторых цветов (такие как красные субпиксели и синие субпиксели) уменьшены в количестве, тогда как субпиксели других цветов в устройстве отображения фактически считаются находящимися в различных "слоях", и каждый слой разделен на множество областей выборки, области выборки в различных слоях разделены так, что они не перекрываются друг с другом, и затем контент, который должен быть отображен каждым субпикселем, вычисляется посредством соотношения площадей областей выборки. Часть субпикселей в устройстве отображения в режиме Pentile используются совместно, так что визуальное разрешение выше, чем фактическое физическое разрешение. То есть, по сравнению с традиционной панелью отображения панель отображения в режиме Pentile может иметь больше пиксельных блоков, сформированных на ней. Однако, как поймет специалист в данной области техники, каждый пиксельный блок требует возбуждения одной пиксельной схемой, и вследствие ограничения размера панели отображения, хотя больше пиксельных блоков может быть изготовлено, нет способа изготовить соответственно больше пиксельных схем, то есть все еще очень трудно изготовить панель отображения высокого разрешения.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Чтобы решить вышеупомянутые проблемы, существующие в современных панелях отображения, варианты осуществления изобретения предоставляют матричную подложку высокого разрешения и способ ее возбуждения, панель отображения и устройство отображения.

В соответствии с вариантом осуществления изобретения, матричная подложка выполнена с возможностью содержания множества циркуляционных блоков и множества пиксельных схем. Каждый циркуляционный блок состоит из четырех субпиксельных блоков, расположенных в четырех столбцах и двух строках, субпиксельные блоки в любых двух смежных столбцах расположены в различных строках и имеют различные цвета, и субпиксельные блоки по меньшей мере в одной строке имеют различные цвета. Каждый субпиксельный блок соединен с одной пиксельной схемой, каждый субпиксельный блок содержит первый субпиксель и второй субпиксель, расположенный в том же столбце и имеющий такой же цвет. Пиксельная схема выполнена с возможностью возбуждения первого субпикселя, когда отображается картинка первого кадра, и возбуждения второго субпикселя, когда отображается картинка второго кадра.

Циркуляционный блок содержит один красный субпиксельный блок, один синий субпиксельный блок и два зеленых субпиксельных блока.

Циркуляционный блок может содержать один красный субпиксельный блок, один зеленый субпиксельный блок, один синий субпиксельный блок и один белый субпиксельный блок.

Пиксельная схема может содержать первую субпиксельную схему, вторую субпиксельную схему и блок управления. Первая субпиксельная схема соединена с первым субпикселем, а вторая субпиксельная схема соединена со вторым субпикселем. Блок управления выполнен с возможностью управления первой субпиксельной схемой, чтобы возбуждать первый субпиксел, когда отображается картинка первого кадра, и управления второй субпиксельной схемой, чтобы возбуждать второй субпиксель, когда отображается картинка второго кадра.

Матричная подложка может дополнительно содержать множество линий передачи данных, и первая субпиксельная схема и второй субпиксель в каждой из пиксельных схем соединены с одной и той же линией передачи данных.

Пиксельная схема может дополнительно содержать компенсационную схему, первая субпиксельная схема может, по меньшей мере, содержать первый управляющий транзистор, а вторая субпиксельная схема может, по меньшей мере, содержать второй управляющий транзистор. Компенсационная схема выполнена с возможностью компенсации порогового напряжения первого возбуждающего транзистора в первой субпиксельной схеме, и с возможностью компенсации порогового напряжения второго возбуждающего транзистора во второй субпиксельной схеме.

В соответствии с вариантами осуществления изобретения, предоставлен способ возбуждения вышеупомянутой матричной подложки. Способ возбуждения состоит в том, что: возбуждают, посредством пиксельной схемы, первый субпиксель в субпиксельном блоке, соединенном с пиксельной схемой, когда отображается картинка первого кадра; и возбуждают, посредством пиксельной схемы, второй субпиксель в субпиксельном блоке, соединенном с пиксельной схемой, когда отображается картинка второго кадра.

В соответствии с вариантами осуществления изобретения, предоставлена панель отображения, чтобы содержать вышеупомянутую матричную подложку.

В соответствии с вариантами осуществления изобретения, предоставлено устройство отображения, чтобы содержать вышеупомянутую панель отображения.

В матричной подложке вариантов осуществления изобретения первый субпиксель и второй субпиксель в каждом субпиксельном блоке возбуждаются одной и той же пиксельной схемой, и по сравнению с предшествующим уровнем техники, в котором требуется возбуждать первый субпиксель и второй субпиксель в каждом субпиксельном блоке с использованием двух пиксельных схем, соответственно, количество пиксельных схем, требуемых во всей матричной подложке, уменьшено, тем самым уменьшая стоимость производства и рабочее давление. В то же время, поскольку количество пиксельных схем уменьшено, больше субпиксельных блоков может быть сформировано на единице площади на матричной подложке, таким образом эффективно увеличивая разрешения матричной подложки.

ОПИСАНИЕ ЧЕРТЕЖЕЙ

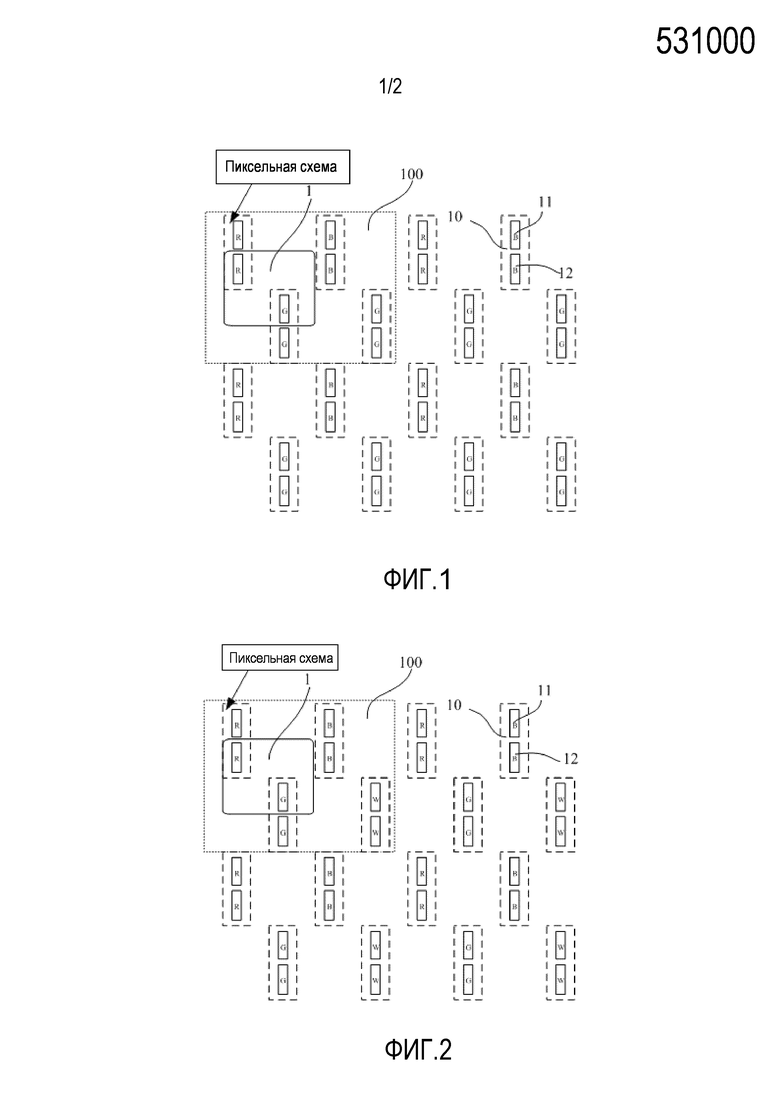

Фиг. 1 представляет собой схематическое изображение матричной подложки в соответствии с вариантом осуществления изобретения;

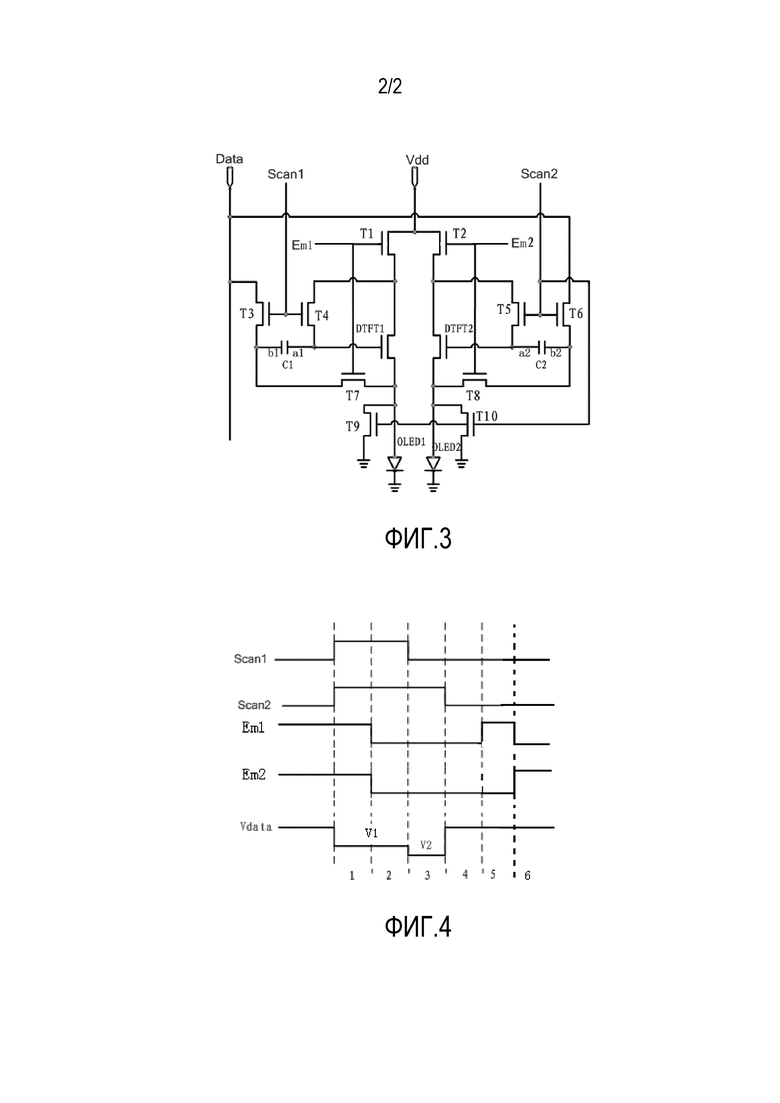

Фиг. 2 представляет собой схематическое изображение другой матричной подложки в соответствии с вариантом осуществления изобретения;

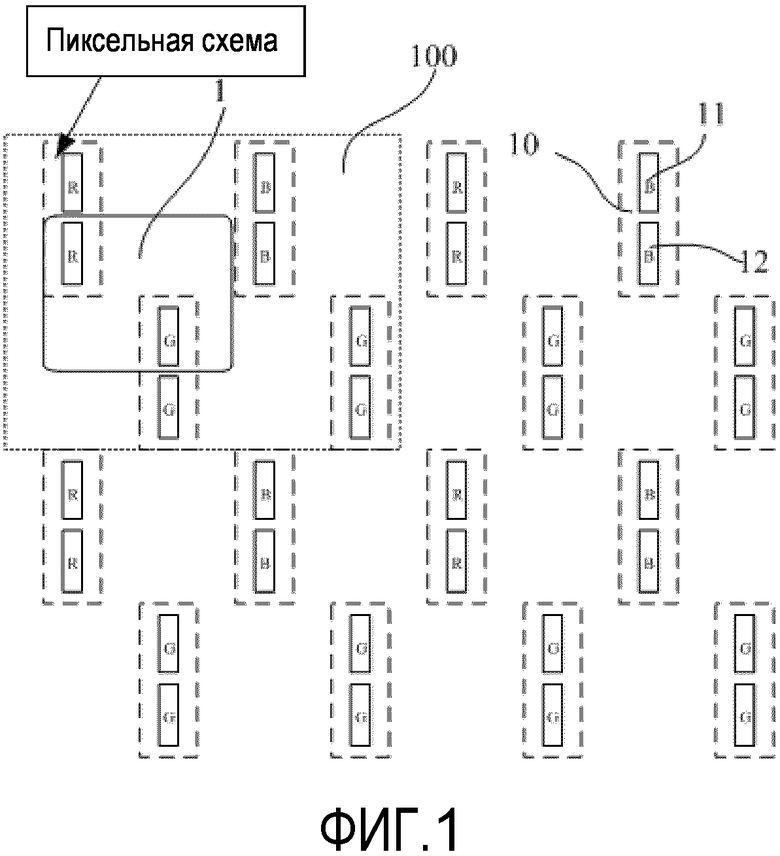

Фиг. 3 представляет собой принципиальную схему пиксельной схемы в соответствии с вариантом осуществления изобретения; и

Фиг. 4 представляет собой временную диаграмму работы пиксельной схемы на Фиг. 3.

Подробное описание вариантов осуществления

Для того, чтобы специалистам в данной области техники лучше понять технические решения изобретения, изобретение далее будет подробно описано в связи с чертежами и реализациями.

В связи с Фиг. 1 и 2, вариант осуществления изобретения предоставляет матричную подложку, которая содержит множество циркуляционных блоков 100, при этом каждый циркуляционный блок 100 состоит из четырех субпиксельных блоков 10, расположенных в четырех столбцах и двух строках, субпиксельные блоки 10 в каждых двух смежных столбцах расположены в различных строках и имеют различные цвета, и субпиксельные блоки 10 по меньшей мере в одной строке имеют различные цвета. Матричная подложка дополнительно содержит множество пиксельных схем, при этом каждый субпиксельный блок 10 соединен с одной пиксельной схемой, каждый субпиксельный блок 10 содержит первый субпиксель 11 и второй субпиксель 12, расположенный в том же столбце и имеющий такой же цвет. Каждая пиксельная схема выполнена с возможностью возбуждения первого субпикселя 11, когда отображается картинка первого кадра, и возбуждения второго субпикселя 12, когда отображается картинка второго кадра.

Кроме того, пиксельный блок 1 может содержать два субпикселя, которые происходят из двух субпиксельных блоков 10, расположенных в двух смежных столбцах, и два субпикселя расположены в двух смежных строках.

Следует отметить, что чтобы достичь отображения с высоким разрешением в предшествующем уровне техники, требуется делать размер каждого субпикселя меньше и меньше; однако, вследствие ограничений процесса, очевидно, размер субпикселя не может быть уменьшен неограниченно. Таким образом технология 2-в-1, то есть, два смежных субпикселя одного и того же цвета в панели отображения совместно используют отверстие в FMM (Теневая Маска Чистого Металла), представлена в изобретении, то есть, в варианте осуществления возбуждение первого субпикселя 11 и второго субпикселя 12 каждого субпиксельного блока 10, когда отображаются различные картинки кадров, достигается одним отверстием в FMM. В то же время, поскольку соответствующие пиксельные блоки 1 в матричной подложке варианта осуществления расположены вышеупомянутым способом, отображение с высоким разрешением достигается с меньшим количеством субпикселей в определенном порядке совместного использования пикселей. Например, один пиксельный блок 1 в варианте осуществления может быть снабжен только двумя субпикселами, красным субпикселом R и зеленым субпикселом G, а синий субпиксель B в смежном пиксельном блоке 1 может быть использован для выполнения нормального отображения, так что больше пиксельных блоков 1 может быть изготовлено на единице площади на матричной подложке, таким образом увеличивая разрешения матричной подложки.

В варианте осуществления, первый субпиксель 11 и второй субпиксель 12 каждого субпиксельного блока 10 возбуждаются одной и той же пиксельной схемой, и по сравнению с предшествующим уровнем техники, в котором требуется возбуждать первый субпиксел 11 и второй субпиксел 12 в каждом субпиксельном блоке 10 с использованием двух пиксельных схем, соответственно, количество пиксельных схем, требуемых во всей матричной подложке, уменьшено, тем самым уменьшая стоимость производства и рабочее давление. В то же время, поскольку количество пиксельных схем уменьшено, больше субпиксельных блоков 10 может быть сформировано на единице площади на матричной подложке, таким образом эффективно увеличивая разрешения матричной подложки.

Как показано на Фиг. 1, в качестве предпочтительной реализации варианта осуществления, один циркуляционный блок 100 матричной подложки содержит четыре субпиксельных блока 10, то есть, один красный субпиксельный блок, один синий субпиксельный блок и два зеленых субпиксельных блока.

В частности, красные субпиксельные блоки 10 и синие субпиксельные блоки 10 в нечетных строках расположены поочередно, и все субпиксельные блоки, расположенные в четных строках, являются зелеными. Альтернативно, все субпиксельные блоки 10, расположенные в нечетных строках, являются зелеными, а красные субпиксельные блоки 10 и синие субпиксельные блоки 10 расположены поочередно в четных строках. Красный субпиксельный блок 10 содержит первый красный субпиксель R и второй красный субпиксель R, синий субпиксельный блок 10 содержит первый синий субпиксель B и второй синий субпиксель B, а зеленый субпиксельный блок 10 содержит первый зеленый субпиксель G и второй зеленый субпиксель G. Когда отображается картинка первого кадра, каждая пиксельная схема возбуждает первый субпиксел 11 субпиксельного блока 10, соединенного с пиксельной схемой, когда отображается картинка второго кадра, пиксельная схема возбуждает второй субпиксел 12 субпиксельного блока 10, соединенного с пиксельной схемой, и этот способ возбуждения с разделением по времени может улучшить разрешение матричной подложки.

Как показано на Фиг. 2, в качестве другой предпочтительной реализации варианта осуществления, циркуляционный блок 100 содержит один красный субпиксельный блок 10, один зеленый субпиксельный блок 10, один синий субпиксельный блок 10 и один белый субпиксельный блок 10. В этой реализации только цвета субпикселей отличаются от цветов вышеупомянутой реализации, а способ возбуждения и принцип отображения являются такими же, как и в вышеупомянутой реализации, которая не будет подробно описана здесь.

Пиксельная схема в варианте осуществления может содержать первую субпиксельную схему, вторую субпиксельную схему и блок управления. Первая субпиксельная схема соединена с первым субпикселом 11, вторая субпиксельная схема соединена со вторым субпикселом, а блок управления выполнен с возможностью управления первой субпиксельной схемой, чтобы возбуждать первый субпиксель 11, когда отображается картинка первого кадра, и управления второй субпиксельной схемой, чтобы возбуждать второй субпиксель 12, когда отображается картинка второго кадра.

Кроме того, матричная подложка дополнительно содержит множество линий Data передачи данных, и первая субпиксельная схема и вторая субпиксельная схема каждой из пиксельных схем соединены с одной и той же линией Data передачи данных. Таким образом, структура матричной подложки может быть простой.

Кроме того, пиксельная схема варианта осуществления может дополнительно содержать компенсационную схему. Первая субпиксельная схема, по меньшей мере, содержит первый возбуждающий транзистор, а вторая субпиксельная схема, по меньшей мере, содержит второй возбуждающий транзистор. Компенсационная схема выполнена с возможностью компенсации порогового напряжения первого возбуждающего транзистора в первой субпиксельной схеме, и с возможностью компенсации порогового напряжения второго возбуждающего транзистора во второй субпиксельной схеме. Две субпиксельные схемы совместно используют один компенсационный блок, так что пороговые напряжения возбуждающих транзисторов компенсируются, чтобы улучшить эффект отображения, уменьшить площадь размещения пиксельных схем матричной подложки и уменьшить стоимость.

Соответственно, вариант осуществления дополнительно предоставляет способ возбуждения любой из вышеупомянутых матричных подложек, который состоит в том, что: возбуждают, посредством пиксельной схемы, первый субпиксель 11 в субпиксельном блоке 10, соединенном с пиксельной схемой, когда отображается картинка первого кадра; и возбуждают, посредством пиксельной схемы, второй субпиксель 12 в субпиксельном блоке 10, соединенном с пиксельной схемой, когда отображается картинка второго кадра.

В качестве структуры пиксельной схемы в варианте осуществления, как показано на Фиг. 3, каждая пиксельная схема содержит первую субпиксельную схему и вторую субпиксельную схему, при этом первая субпиксельная схема содержит первый возбуждающий транзистор DTFT1, а вторая субпиксельная схема содержит второй возбуждающий транзистор DTFT2. На Фиг. 3 первое устройство OLED1 отображения эквивалентно первому субпикселю, а второе устройство OLED2 отображения эквивалентно второму субпикселю. Первая субпиксельная схема и вторая субпиксельная схема используют совместно компенсационный блок, и управляются одной и той же линией Data передачи данных, которая соединена с блоком управления. Компенсационный блок выполнен с возможностью регулировки напряжения затвора первого возбуждающего транзистора DTFT1 в первой субпиксельной схеме, чтобы устранить влияние порогового напряжения первого возбуждающего транзистора DTFT1 на возбуждающий ток первого устройства OLED1 отображения, и регулировки напряжения затвора второго возбуждающего транзистора DTFT2 во второй субпиксельной схеме, чтобы устранить влияние порогового напряжения второго возбуждающего транзистора DTFT2 на возбуждающий ток второго устройства OLED2 отображения. Компенсационный блок может, в частности, содержать первый переключающий транзистор T1, второй переключающий транзистор T2, третий переключающий транзистор T3, четвертый переключающий транзистор T4, пятый переключающий транзистор T5, шестой переключающий транзистор T6, седьмой переключающий транзистор T7, восьмой переключающий транзистор T8, девятый переключающий транзистор T9, десятый переключающий транзистор T10, первый запоминающий конденсатор C1 и второй запоминающий конденсатор C2. Затвор первого переключающего транзистора T1 и затвор седьмого переключающего транзистора T7 соединены с первой линией Em1 управления светоизлучением, исток первого переключающего транзистора T1 соединен с истоком второго переключающего транзистора T2 и первым источником VDD опорного напряжения, а сток первого переключающего транзистора T1 соединен с истоком четвертого переключающего транзистора T4 и истоком первого возбуждающего транзистора DTFT1. Затвор второго переключающего транзистора T2 соединен с затвором восьмого переключающего транзистора T8 и второй линией Em2 управления светоизлучением, а сток второго переключающего транзистора T2 соединен с истоком пятого переключающего транзистора T5 и истоком второго возбуждающего транзистора DTFT2. Затвор третьего переключающего транзистора T3 соединен с затвором четвертого переключающего транзистора T4 и первой сканирующей линией Scan1, исток третьего переключающего транзистора T3 соединен с линией Data передачи данных, сток третьего переключающего транзистора T3 соединен со вторым выводом b1 первого запоминающего конденсатора C1 и истоком седьмого переключающего транзистора T7. Сток четвертого переключающего транзистора T4 соединен с первым терминалом a1 первого запоминающего конденсатора C1 и стоком первого возбуждающего транзистора DTFT1. Затвор пятого переключающего транзистора T5 соединен с затвором шестого переключающего транзистора T6 и второй сканирующей линией Scan2, а сток пятого переключающего транзистора T5 соединен с первым выводом a2 второго запоминающего конденсатора C2 и затвором второго возбуждающего транзистора DTFT2. Исток шестого переключающего транзистора T6 соединен с линией Data передачи данных, сток шестого переключающего транзистора T6 соединен со вторым выводом b2 второго запоминающего конденсатора C2 и истоком восьмого переключающего транзистора T8. Сток седьмого переключающего транзистора T7 соединен с истоком девятого переключающего транзистора T9, стоком первого возбуждающего транзистора DTFT1 и первым выводом первого устройства отображения, а второй вывод первого устройства отображения заземлен. Сток восьмого переключающего транзистора T8 соединен с истоком десятого переключающего транзистора T10, стоком второго возбуждающего транзистора DTFT2 и первым выводом второго устройства отображения, а второй вывод второго устройства отображения заземлен. Затвор девятого переключающего транзистора T9 соединен с затвором десятого переключающего транзистора T10 и второй сканирующей линией Scan2, а сток девятого переключающего транзистора T9 заземлен. Сток десятого переключающего транзистора T10 заземлен.

Чтобы сделать так, чтобы пиксельная схема имела более высокую производительность, так что каждый пиксельный блок мог хорошо управляться, первый переключающий транзистор T1, второй переключающий транзистор T2, третий переключающий транзистор T3, четвертый переключающий транзистор T4, пятый переключающий транзистор T5, шестой переключающий транзистор T6, седьмой переключающий транзистор T7, восьмой переключающий транзистор T8, девятый переключающий транзистор T9, десятый переключающий транзистор T10, первый возбуждающий транзистор DTFT1 и второй возбуждающий транзистор DTFT2 являются тонкопленочными транзисторами N-типа.

В связи с Фиг. 3 и 4, в настоящем варианте осуществления дополнительно предоставлен способ возбуждения пиксельной схемы, причем способ возбуждения, в частности, содержит следующие шесть временных периодов от первого временного периода до шестого временного периода.

Стадия установки в исходное состояние (первый временной период): высокоуровневый сигнал вводится в первую линию Scan1 сканирования, вторую линию Scan2 сканирования, первую линию Em1 управления светоизлучением и вторую линию Em2 управления светоизлучением. Первый переключающий транзистор T1, второй переключающий транзистор T2, третий переключающий транзистор T3, четвертый переключающий транзистор T4, пятый переключающий транзистор T5, шестой переключающий транзистор T6, седьмой переключающий транзистор T7, восьмой переключающий транзистор T8, девятый переключающий транзистор T9 и десятый переключающий транзистор T10 все включены, и первый источник опорного напряжения устанавливает потенциал на первом выводе a1 первого запоминающего конденсатора C1 и потенциал на первом выводе a2 второго запоминающего конденсатора C2 в напряжение Vdd первого источника опорного напряжения и подает первое напряжение V1 на линию Data передачи данных. В это время, поскольку третий переключающий транзистор T3, четвертый переключающий транзистор T4, пятый переключающий транзистор T5 и шестой переключающий транзистор T6 все включены, как потенциал на втором выводе b1 первого запоминающего конденсатора C1, так и потенциал на втором выводе b2 второго запоминающего конденсатора C2 установлены в первое напряжение V1, то есть a1=Vdd, b1=V1, a2=Vdd, и b2=V1.

Стадия разряда (второй временной период): высокоуровневый сигнал вводится в первую линию Scan1 сканирования, вторую линию Scan2 сканирования, и низкоуровневый сигнал вводится в первую линию Em1 управления светоизлучением и вторую линию Em2 управления светоизлучением. Третий переключающий транзистор T3, четвертый переключающий транзистор T4, пятый переключающий транзистор T5, шестой переключающий транзистор T6, девятый переключающий транзистор T9 и десятый переключающий транзистор T10 все включены, как первый запоминающий конденсатор C1, так и второй запоминающий конденсатор C2 разряжаются, и потенциал на первом выводе a1 первого запоминающего конденсатора C1 и потенциал на первом выводе a2 второго запоминающего конденсатора C2 разряжаются, чтобы стать пороговым напряжением Vth1 первого возбуждающего транзистора DTFT1 и пороговым напряжением Vth2 второго возбуждающего транзистора DTFT2. Кроме того, поскольку девятый переключающий транзистор T9 и десятый переключающий транзистор T10 включены, ток в схеме не будет течь через первое устройство OLED1 отображения и второе устройство OLED2 отображения, неявно уменьшая энергопотребление первого устройства OLED1 отображения и второго устройства OLED2 отображения.

Стадия непрерывного разряда (третий временной период): низкоуровневый сигнал вводится в первую линию Scan1 сканирования, первую линию Em1 управления светоизлучением и вторую линию Em2 управления светоизлучением, высокоуровневый сигнал вводится во вторую линию Scan2 сканирования, и второе напряжение V2 подается на линию Data передачи данных. В это время потенциал на втором выводе b2 второго запоминающего конденсатора C2 соответственно становится V2, и потенциал на первом выводе a2 второго запоминающего конденсатора C2 поддерживается на Vth2, так что разность напряжений между двумя выводами первого запоминающего конденсатора C1 составляет Vth1-V1, а разность напряжений между двумя терминалами второго запоминающего конденсатора C2 составляет Vth2-V2, где V1>V2.

Стадия стабилизации напряжения (четвертый временной период): низкоуровневый сигнал вводится в первую линию Scan1 сканирования, вторую линию Scan2 сканирования, первую линию Em1 управления светоизлучением и вторую линию Em2 управления светоизлучением. Первый переключающий транзистор T1, второй переключающий транзистор T2, третий переключающий транзистор T3, четвертый переключающий транзистор T4, пятый переключающий транзистор T5, шестой переключающий транзистор T6, седьмой переключающий транзистор T7, восьмой переключающий транзистор T8, девятый переключающий транзистор T9 и десятый переключающий транзистор T10 все включены, и разности напряжений между двумя выводами первого запоминающего конденсатора C1 и второго запоминающего конденсатора C2 стабилизированы, оба из которых готовятся к стадии светоизлучения.

Первая стадия светоизлучения (пятый временной период): низкоуровневый сигнал вводится в первую линию Scan1 сканирования и вторую линию Scan2 сканирования, и высокоуровневый сигнал вводится в первую линию Em1 управления светоизлучением, и низкоуровневый сигнал вводится во вторую линию Em2 управления светоизлучением. Первый переключающий транзистор T1 и седьмой переключающий транзистор T7 включены, потенциал V1 на втором выводе b1 первого запоминающего конденсатора C1 становится анодным потенциалом Voled1 первого устройства OLED1 отображения, потенциал на первом выводе a1 первого запоминающего конденсатора C1 составляет Vth1-V1+Voled1, и первый возбуждающий транзистор DTFT1 возбуждает первое устройство OLED1 отображения, чтобы испускать свет. В это время ток, текущий через первое устройство OLED1 отображения, может быть получен на основе тока насыщения тонкопленочного транзистора:

Ioled1 = K(VGS-Vth1)2

= K[(Vth1-V1+Voled1) - Voled1 – Vth1]2

= K·(V1)2

Вторая стадия светоизлучения (шестой временной период): низкоуровневый сигнал вводится в первую линию Scan1 сканирования и вторую линию Scan2 сканирования, низкоуровневый сигнал вводится в первую линию Em1 управления светоизлучением, и высокоуровневый сигнал вводится во вторую линию Em2 управления светоизлучением. В это время второй переключающий транзистор T2 и восьмой переключающий транзистор T8 включены, потенциал V2 на втором выводе b2 второго запоминающего конденсатора C2 становится анодным потенциалом Voled2 второго устройства OLED2 отображения, потенциал на первом выводе a2 второго запоминающего конденсатора C2 составляет Vth2-V2+Voled2, и второй возбуждающий транзистор DTFT2 возбуждает второе устройство OLED2 отображения, чтобы испускать свет. С помощью того же принципа, ток, протекающий через второе устройство OLED2 отображения, составляет Ioled2=K·(V2)2.

На основе полученных выше токов первого устройства OLED1 отображения и второго устройства OLED2 отображения, пиксельная схема не только достигает отображения с высоким разрешением, но также избегает влияния порогового напряжения возбуждающего транзистора на пиксельную схему, так что матричная подложка варианта осуществления получает более однородное отображение.

Следует отметить, что способ для возбуждения соответствующих субпикселей на матричной подложке в варианте осуществления описан, принимая вышеупомянутую пиксельную схему лишь в качестве примера. Однако, пиксельная схема в варианте осуществления не ограничена вышеупомянутой пиксельной схемой. Любая пиксельная схема, которая достигает способа управления с временным разделением, может быть применена к матричной подложке варианта осуществления, и подпадает под объем защиты варианта осуществления.

Соответственно, вариант осуществления дополнительно предоставляет панель отображения, которая содержит вышеупомянутую матричную подложку, и, таким образом, может достигать отображения с высоким разрешением.

Соответственно, вариант осуществления дополнительно предоставляет устройство отображения, которое содержит вышеупомянутую панель отображения, и может быть любым продуктом или компонентом, имеющим функцию отображения, таким как жидкокристаллическая панель, OLED панель, мобильный телефон, планшетный компьютер, телевизор, дисплей, ноутбук, цифровая фоторамка и навигатор.

Из-за того, что устройство отображения в варианте осуществления содержит вышеупомянутую панель отображения, его разрешение выше, и производительность лучше.

Конечно, устройство отображения в варианте осуществления также может содержать другие традиционные структуры, такие как блок возбуждения отображения, и т.д.

Должно быть понятно, что приведенные выше варианты осуществления представляют собой лишь примерные варианты осуществления, используемые для иллюстрирования принципа изобретения, и изобретение ими не ограничено. Для обычных специалистов в данной области техники различные варианты и улучшения могут быть сделаны, не выходя за пределы духа и сущности изобретения, и эти варианты и улучшения также расцениваются как объем защиты изобретения.

Изобретение относится к области отображения данных. Технический результат – обеспечение возбуждения матричной подложки высокого разрешения посредством одной пиксельной схемы. Матричная подложка содержит множество циркуляционных блоков и множество пиксельных блоков, причем: каждый циркуляционный блок состоит из четырех субпиксельных блоков, расположенных в четырех столбцах и двух строках, субпиксельные блоки в любых двух смежных столбцах расположены в различных строках и имеют различные цвета, и субпиксельные блоки по меньшей мере в одной строке имеют различные цвета; каждый субпиксельный блок соединен с одной пиксельной схемой, и каждый субпиксельный блок содержит первый субпиксель и второй субпиксель, расположенный в том же столбце и имеющий такой же цвет; при этом пиксельная схема выполнена с возможностью возбуждения первого субпикселя, когда отображается картинка первого кадра, и возбуждения второго субпикселя, когда отображается картинка второго кадра. 4 н. и 5 з.п. ф-лы, 4 ил.

1. Матричная подложка, содержащая множество циркуляционных блоков и множество пиксельных блоков, в которой:

каждый циркуляционный блок состоит из четырех субпиксельных блоков, расположенных в четырех столбцах и двух строках, субпиксельные блоки в любых двух смежных столбцах расположены в различных строках и имеют различные цвета, и субпиксельные блоки по меньшей мере в одной строке имеют различные цвета;

каждый субпиксельный блок соединен с одной пиксельной схемой, и каждый субпиксельный блок содержит первый субпиксель и второй субпиксель, расположенный в том же столбце и имеющий такой же цвет; и

пиксельная схема выполнена с возможностью возбуждения первого субпикселя, когда отображается картинка первого кадра, и возбуждения второго субпикселя, когда отображается картинка второго кадра.

2. Матричная подложка по п. 1, в которой циркуляционный блок содержит один красный субпиксельный блок, один синий субпиксельный блок и два зеленых субпиксельных блока.

3. Матричная подложка по п. 1, в которой циркуляционный блок содержит один красный субпиксельный блок, один зеленый субпиксельный блок, один синий субпиксельный блок и один белый субпиксельный блок.

4. Матричная подложка по любому из пп. 1-3, в которой пиксельная схема содержит первую субпиксельную схему, вторую субпиксельную схему и блок управления;

первая субпиксельная схема соединена с первым субпикселем, а вторая субпиксельная схема соединена со вторым субпикселем; и

блок управления выполнен с возможностью управления первой субпиксельной схемой, чтобы возбуждать первый субпиксель, когда отображается картинка первого кадра, и управления второй субпиксельной схемой, чтобы возбуждать второй субпиксель, когда отображается картинка второго кадра.

5. Матричная подложка по п. 4, дополнительно содержащая множество линий передачи данных, причем первая субпиксельная схема и вторая субпиксельная схема в каждой пиксельной схеме соединены с одной и той же линией передачи данных.

6. Матричная подложка по п. 4, в которой пиксельная схема дополнительно содержит компенсационную схему, причем первая субпиксельная схема по меньшей мере содержит первый возбуждающий транзистор и вторая субпиксельная схема по меньшей мере содержит второй возбуждающий транзистор; и

компенсационная схема выполнена с возможностью компенсации порогового напряжения первого возбуждающего транзистора в первой субпиксельной схеме и с возможностью компенсации порогового напряжения второго возбуждающего транзистора во второй субпиксельной схеме.

7. Способ возбуждения матричной подложки по любому из пп. 1-6, содержащий этапы, на которых:

возбуждают посредством пиксельной схемы первый субпиксель в субпиксельном блоке, соединенном с пиксельной схемой, когда отображается картинка первого кадра; и

возбуждают посредством пиксельной схемы второй субпиксель в субпиксельном блоке, соединенном с пиксельной схемой, когда отображается картинка второго кадра.

8. Панель отображения, содержащая матричную подложку по любому из пп. 1-6.

9. Устройство отображения, содержащее панель отображения по п. 8.

| CN 103745684 A, 23.04.2014 | |||

| Способ защиты переносных электрических установок от опасностей, связанных с заземлением одной из фаз | 1924 |

|

SU2014A1 |

| Способ защиты переносных электрических установок от опасностей, связанных с заземлением одной из фаз | 1924 |

|

SU2014A1 |

| Изложница с суживающимся книзу сечением и с вертикально перемещающимся днищем | 1924 |

|

SU2012A1 |

| Колосоуборка | 1923 |

|

SU2009A1 |

| ЖИДКОКРИСТАЛЛИЧЕСКОЕ УСТРОЙСТВО ОТОБРАЖЕНИЯ | 2010 |

|

RU2512680C1 |

Авторы

Даты

2018-12-25—Публикация

2015-04-20—Подача