Предлагаемое устройство относится к области радиосвязи, использующей широкополосные фазоманипулированные сигналы на основе псевдослучайных последовательностей (ПСП). Устройство может найти применение в широкополосных помехозащищенных системах радиосвязи.

В настоящее время выросли требования к рабочим характеристикам приемопередающих устройств радиосвязи военного и специального назначения, построенных на основе методов расширения спектра. Одновременно существенно увеличились возможности специализированной элементной базы, осуществляющей быстродействующую цифровую обработку сигналов (ЦОС). Это обусловило перевод систем передачи и обработки информации на цифровую основу, потому что обеспечивается устойчивость и эффективность работы систем связи совместно с повышением быстродействия при наличии значительных уровней априорной неопределенности сигнально-информационных воздействий.

Известно устройство поиска псевдослучайной последовательности, описанное в [1], содержащее фильтр нижних частот, генератор тактовых импульсов, аналого-цифровой преобразователь, делитель частоты, коммутаторы, адресный счетчик, элементы «ИЛИ», счетчик циклов, формирователи управляющих сигналов, регистры, генератор ПСП, элементы «И», триггер накопления, АЛУ, триггер обнаружения, ОЗУ, пороговый блок, ключи, регистр сдвига с обратными связями, позволяющее уменьшить время поиска сигнала. Устройство [1] по функциональности и алгоритму работы аналогично заявляемому устройству. Недостатком устройства [1] является возможность работы только с М-последовательностями.

Наиболее близким по технической сущности к заявляемому является устройство, описанное в [2], принятое за прототип.

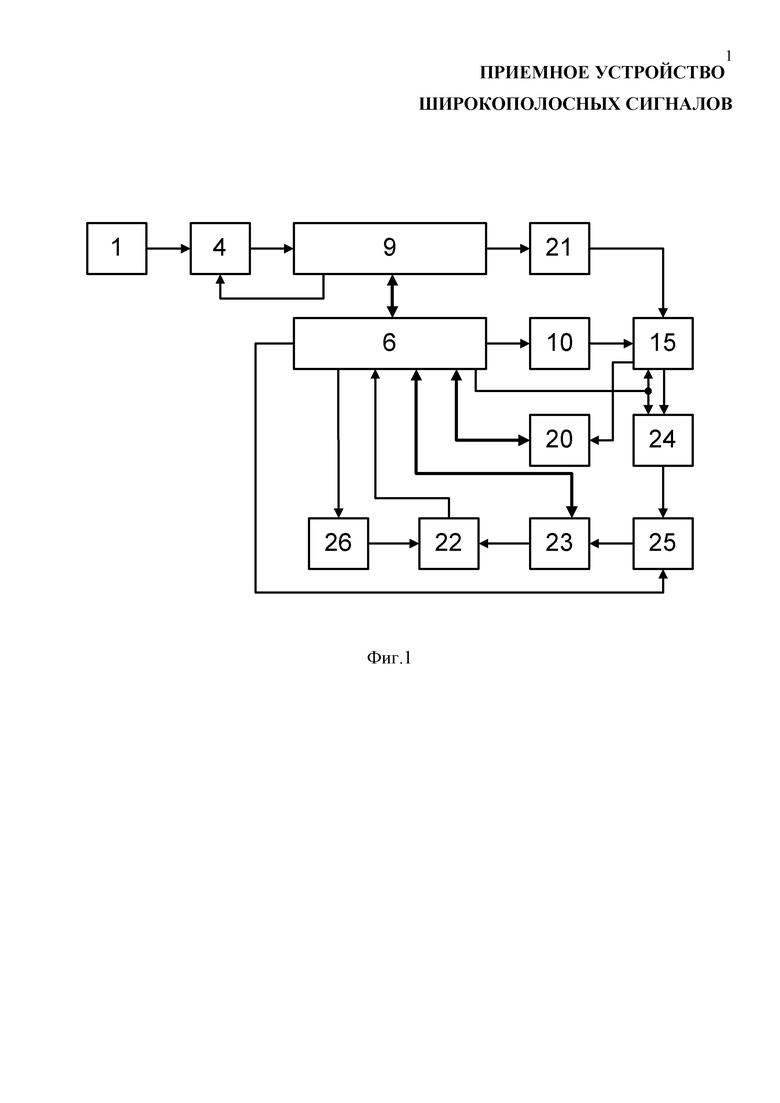

Функциональная схема устройства-прототипа приведена на фиг. 1, где приняты следующие обозначения:

1 – приемный блок (ПБ);

4 – аналого-цифровой преобразователь (АЦП);

6 – блок управления (БУ);

9 – блок накопления сигнала (БНС);

10 – формирователь опорных сигналов (ФОС) - ПСП;

15 – блок корреляторов (БК);

20 – блок выделения информации (БВИ);

21 – цифроаналоговый преобразователь (ЦАП);

22 – блок сравнения (БС);

23 – блок выбора максимального кода (БВМК);

24 – блок преобразования напряжение-код (БПНК);

25 – блок наполнения корреляционных сверток (БНК);

26 – постоянное запоминающее устройство (ПЗУ).

Устройство-прототип содержит последовательно соединенные приемный блок (ПБ) 1, аналого-цифровой преобразователь (АЦП) 4, блок накопления сигнала (БНС) 9, цифроаналоговый преобразователь (ЦАП) 21, блок корреляторов (БК) 15, блок преобразования напряжение-код (БПНК) 24, блок наполнения корреляционных сверток (БНК) 25, блок выбора максимального кода (БВМК) 23, блок сравнения (БС) 22, выход которого подключен к входу блока управления (БУ) 6; кроме того, устройство-прототип содержит формирователь опорных сигналов (ФОС) 10, блок выделения информации (БВИ) 20, постоянное запоминающее устройство (ПЗУ) 26.

При этом второй выход БНС 9 соединен со вторым входом АЦП 4, выход ФОС 10 соединен со вторым входом БК 15, второй выход БК 15 соединен с входом БВИ 20, выход ПЗУ 26 соединен со вторым входом БС 22.

Первый вход-выход БУ 6 соединен с входом-выходом БНС 9, второй вход-выход соединен с входом-выходом БВИ 20, а третий вход-выход соединен с входом-выходом БВМК 23; первый выход БУ 6 соединен со вторым входом БНК 25, второй выход соединен с входом ПЗУ 26, третий выход соединен с третьим входом БК 15 и вторым входом БПНК 24, четвертый выход соединен с входом ФОС 10.

Работа устройства–прототипа заключается в следующем.

Входная смесь полезного сигнала, шумов и помех поступает в ПБ 1, в котором происходит предварительная селекция, перенос на промежуточную частоту, режекция участков спектра, пораженных узкополосными помехами, бланкирование импульсных помех и усиление до фиксированного среднего уровня.

С выхода ПБ 1 смесь полезного сигнала, флуктуационных шумов и широкополосных помех поступает на АЦП 4.

В АЦП 4 осуществляется дискретизация поступающего сигнала с частотой 4Ft, где Ft – тактовая частота модулирующих псевдослучайных последовательностей, и квантуется по уровням, при этом выборки преобразуются в 4-разрядный двоичный код. Полученный поток цифровых данных непрерывно записывается в БНС 9.

Сжатые потоки данных с выхода БНС 9 поступают на входы ЦАП 21. Далее с выхода ЦАП 21 аналоговый сигнал поступает на БК 15, где в каждом корреляторе входной сигнал перемножается с опорной видеопоследовательностью, предварительно фильтруется, переносится на вторую промежуточную частоту, затем детектируется.

Далее выходные сигналы с БК 15 поступают на БПНК 24, где напряжения цифровых сверток нормируются по шуму и преобразуются в цифровую форму, затем поступают на БНК 25, где осуществляется последетекторное накопление и запоминание сверток.

Затем значения сверток поступают на БВМК 23, где осуществляется выбор максимального из N значений корреляционных сумм и определение его номера. Значение максимального кода поступает на БС 22, где происходит его сравнение с пороговым значением, которое выдается ПЗУ 26.

В конце каждого такта накопления БУ 6 выбирает из ПЗУ 26 два значения порогов и поочередно выдает их на БС 22.

Если значение максимального кода не превышает меньший из порогов, поиск прекращается. Если превышает больший из порогов, сигнал считается обнаруженным.

Далее БУ 6 формирует сигнал фазирования, который поступает на БНС 9 и синхронизирует момент начала записи приемной информации, а приемник, соответственно, переходит в режим слежения и выделения информации.

БВИ 20 осуществляет выделение информации. ФОС 10 формирует опорные псевдослучайные последовательности и осуществляет их фазирование с началом считывания информации из БНС 9 по команде управления, поступающей от БУ 6.

Исходя из описания работы устройства-прототипа, можно сделать вывод о том, что он выполнен на схемах и элементах жесткой логики, что приводит к избыточному количеству аппаратных ресурсов. В устройстве-прототипе введены блоки, реализующие преобразование сигнала из аналоговой формы в цифровую и обратно, имеется блок аналоговых корреляторов. Это значительно ограничивает функциональные возможности, не позволяя реализовать адаптивные алгоритмы ЦОС.

Также, недостатком устройства-прототипа является отсутствие возможности приема сигналов с переменной тактовой частотой, что ограничивает возможность адаптации устройства [2] к изменениям частоты принимаемого сигнала.

В заявляемом изобретении решается задача разработки приемного устройства широкополосных сигналов на основе быстродействующих устройств цифровой обработки сигналов с одновременным улучшением характеристик устройства. Кроме того, все блоки, входящие в приемное устройство, должны централизованно управляться и динамически менять параметры поиска и обнаружения при различных соотношениях сигнал/шум, что позволяет реализовать алгоритмы адаптивной обработки сигнала.

Достигаемый при использовании изобретения технический результат –уменьшение времени обнаружения сигнала и повышение точности синхронизации приемных устройств широкополосных сигналов, обнаруживающих сложные сигналы с известной несущей частотой и случайной начальной фазой, с одновременным упрощением аппаратной реализации и уменьшением габаритных характеристик, причем характеристики улучшаются за счет добавления блоков, выполняющих цифровую обработку, что позволяет в процессе приема оптимизировать алгоритмы синхронизации.

Для решения поставленной задачи в устройство, содержащее приемный блок (ПБ 1), вход которого является входом устройства, аналого-цифровой преобразователь (АЦП 4), блок управления (БУ 6), выход которого является выходом устройства, причем ПБ последовательно соединен с АЦП, согласно изобретению, введены цифровое приемное устройство (ЦПУ 2), синтезатор тактовой частоты (СТЧ 5), опорный генератор (ОГ 7) и корреляционное приемное устройство (КПУ 3),

содержащее блок управления корреляционной обработкой (БУКО 8), первый выход которого является выходом КПУ 3, блок накопления сигнала (БНС 9), первый вход которого является первым входом КПУ 3, формирователь опорных сигналов (ФОС 10), первый вход которого является вторым входом КПУ 3, последовательно соединенные блок вычисления корреляционной функции (БВКФ 11) и блок обнаружения синхропоследовательности (БОС 12), последовательно соединенные блок оценки задержки сигнала (БОЗС 13) и первый фильтр-экстраполятор (ФЭ1 14), блок корреляторов (БК 15), последовательно соединенные блок обнаружения (БО 16), блок оценки фазы сигнала (БОФС 17) и второй фильтр-экстраполятор (ФЭ2 18), схему приема информации (СПИ 19), причем группы входов-выходов БУКО 8, ФОС 10, СПИ 19 являются группой входов-выходов КПУ 3;

при этом первый вход ЦПУ 2 соединен с выходом АЦП 4, а выход соединен с первым входом КПУ 3, группа входов-выходов которого соединена с группой входов-выходов БУ 6; выход СТЧ 5 соединен соответственно со вторыми входами ЦПУ 2, КПУ 3, АЦП 4; первый выход БУ 6 соединен с первым входом ПБ 1, второй выход соединен с первым входом СТЧ 5, а третий выход соединен с третьим входом ЦПУ 2; первый выход ОГ 7 соединен со вторым входом СТЧ 5, а второй выход соединен со вторым входом ПБ 1; выход КПУ 3 соединен с четвертым входом ЦПУ 2;

кроме того,

первый вход БВКФ 11 соединен с первым выходом ФОС 10, выход БОС 12 соединен с первым входом БУКО 8; первый выход ФЭ1 14 соединен со вторым входом БНС 9; первый вход БК 15 соединен со вторым выходом ФОС 10, а первый выход соединен соответственно с входом БОЗС 13 и первым входом СПИ 19; второй выход БО 16 соединен со вторым входом БУКО 8, а первый вход соединен со вторым выходом БК 15; выход БНС 9 соединен соответственно со вторыми входами БВКФ 11 и БК 15, второй выход ФЭ1 14 соединен соответственно со вторыми входами БО 16, БОФС 17 и СПИ 19, выход ФЭ2 18 соединен с третьим входом СПИ 19, второй выход БУКО 8 соединен соответственно с третьими входами БНС 9, БК 15 и со вторым входом ФОС 10.

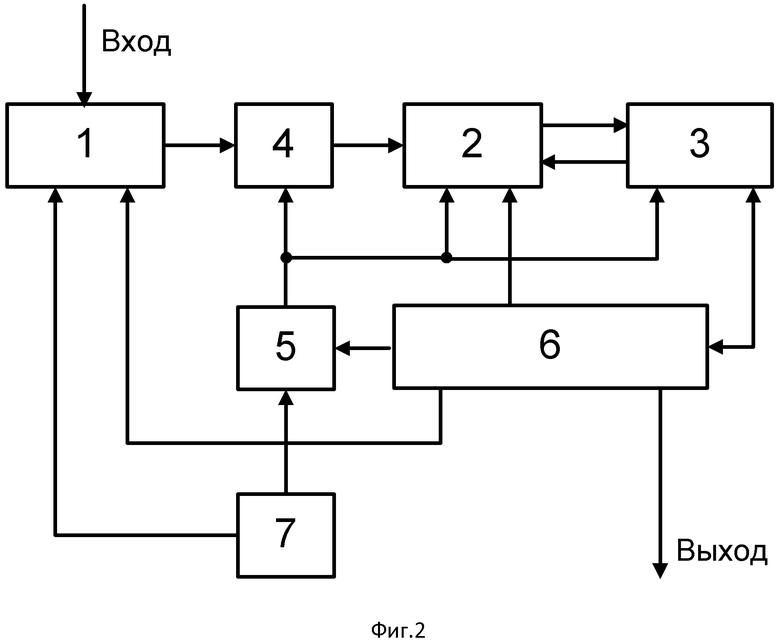

Функциональная схема заявляемого устройства приведена на фиг. 2, где приняты следующие обозначения:

1 – приемный блок (ПБ);

2 – цифровое приемное устройство (ЦПУ);

3 – корреляционное приемное устройство (КПУ);

4 – аналого-цифровой преобразователь (АЦП);

5 – синтезатор тактовой частоты (СТЧ);

6 – блок управления (БУ);

7 – опорный генератор (ОГ).

Заявляемое устройство содержит последовательно соединенные приемный блок (ПБ) 1, аналого-цифровой преобразователь (АЦП) 4 и цифровое приемное устройство (ЦПУ) 2, корреляционное приемное устройство (КПУ) 3, соединенное двумя группами входов-выходов с ЦПУ 2; синтезатор тактовой частоты (СТЧ) 5, выход которого соединен соответственно со вторыми входами ЦПУ 2 и АЦП 4.

Дополнительно, устройство содержит блок управления (БУ) 6, первый выход которого соединен с первым входом ПБ 1, второй выход соединен с первым входом СТЧ 5, а третий выход является выходом устройства; опорный генератор (ОГ) 7, первый выход которого соединен со вторым входом СТЧ 5, а второй выход соединен со вторым входом ПБ 1.

Кроме того, БУ 6 соединен группой входов-выходов с КПУ 3.

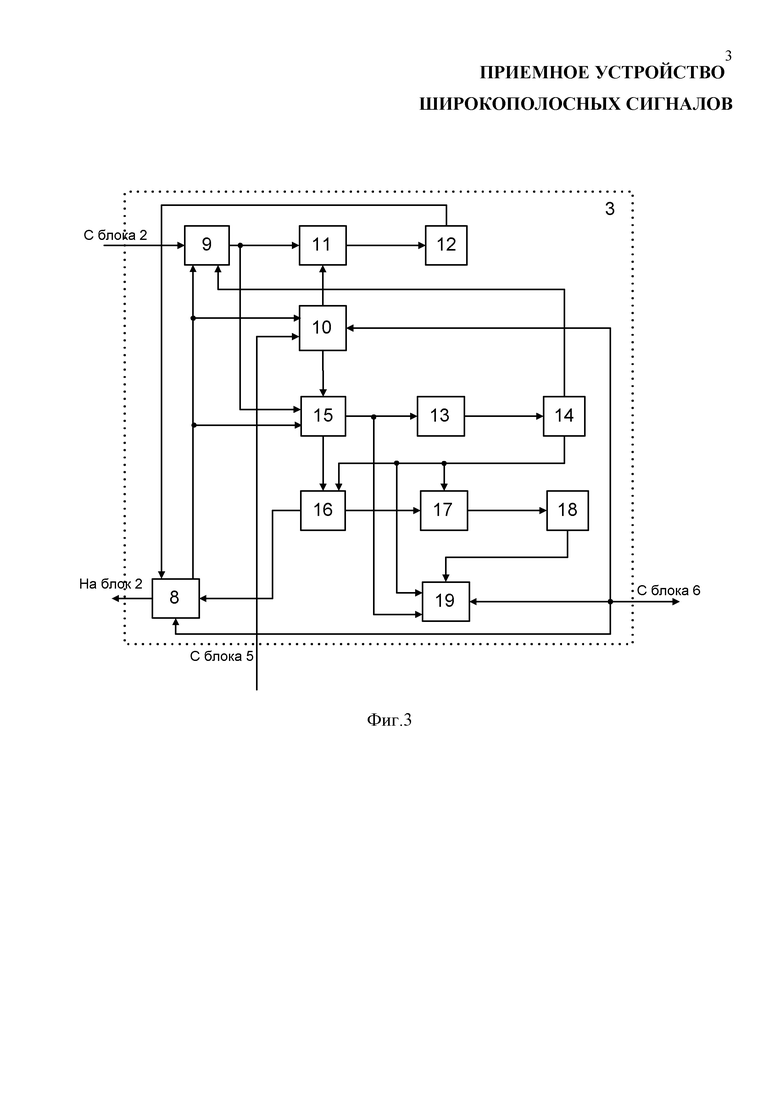

Функциональная схема КПУ 3 приведена на фиг. 3, где приняты следующие обозначения:

8 – блок управления корреляционной обработкой (БУКО);

9 – блок накопления сигнала (БНС);

10 – формирователь опорных сигналов (ФОС);

11 – блок вычисления корреляционной функции (БВКФ);

12 – блок обнаружения синхропоследовательности (БОС);

13 – блок оценки задержки сигнала (БОЗС);

14 – первый фильтр-экстраполятор (ФЭ1);

15 – блок корреляторов (БК);

16 – блок обнаружения (БО);

17 – блок оценки фазы сигнала (БОФС);

18 – второй фильтр-экстраполятор (ФЭ2);

19 – схема приема информации (СПИ).

КПУ 3 содержит блок накопления сигнала (БНС) 9, группа входов-выходов которого является первой группой входов-выходов КПУ 3, блок управления корреляционной обработкой (БУКО) 8, первая группа входов-выходов которого является второй группой входов-выходов КПУ 3, а вторая группа входов-выходов является третьей группой входов-выходов КПУ 3.

Кроме того, КПУ 3 дополнительно содержит формирователь опорных сигналов (ФОС) 10, первый вход которого является первым выходом БНС 9, последовательно соединенные блок вычисления корреляционной функции (БВКФ) 11, первый вход которого соединен с первым выходом ФОС 10, и блок обнаружения синхропоследовательности (БОС) 12, первый выход которого соединен с первым входом БУКО 8, а второй выход соединен с первым входом БНС 9; последовательно соединенные блок оценки задержки сигнала (БОЗС) 13 и первый фильтр-экстраполятор (ФЭ1) 14, первый выход которого соединен со вторым входом БНС 9; блок корреляторов (БК) 15, первый вход которого соединен со вторым выходом ФОС 10, а первый выход соединен соответственно с входом БОЗС 13 и первым входом схемы приема информации (СПИ) 19; последовательно соединенные блок обнаружения (БО) 16, блок оценки фазы сигнала (БОФС) 17 и второй фильтр-экстраполятор (ФЭ2) 18, причем второй выход БО 16 соединен со вторым входом БУКО 8, а первый вход соединен со вторым выходом БК 15; (СПИ) 19,.

Кроме того, выход БНС 9 соединен соответственно со вторыми входами БВКФ 11 и БК 15, второй выход БУКО 8 соединен соответственно с третьими входами БНС 9, БК 15 и вторым входом ФОС 10, второй выход ФЭ1 14 соединен соответственно со вторыми входами БО 16, БОФС 17 и СПИ 19, выход ФЭ2 18 соединен с третьим входом СПИ 19.

Устройство работает следующим образом.

Перед началом цикла поиска сигнала БУ 6 устанавливает параметры поиска путем передачи управляющей информации на БУКО 8 и ФОС 10.

ОГ 7 выдает сигнал стабильной частоты FОГ, который поступает на входы ПБ 1 и СТЧ 5. Сигнал с выхода СТЧ 5 поступает на входы АЦП 4, ЦПУ 3 и ФОС 10.

ПБ 1 и АЦП 4 по функциональному назначению аналогичны блокам устройства-прототипа. Входная смесь полезного сигнала, шумов и широкополосных помех поступает в ПБ 1, в котором происходит предварительная селекция, перемножение на сигнал стабильной частоты, синтезируемый из сигнала ОГ 7, режекция участков спектра, пораженных узкополосными помехами, бланкирование импульсных помех и усиление до фиксированного среднего уровня.

Полученный сигнал с выхода ПБ 1 поступает на АЦП 4. В АЦП 4 осуществляется дискретизация сигнала с частотой синтезатора тактовой частоты, и преобразование в параллельный двоичный код.

Преобразованный сигнал поступает на вход ЦПУ 2, где осуществляется выделение комплексных огибающих сигналов соответствующих каналов приема, затем осуществляется предварительная децимация, последующая децимация до минимально необходимой частоты дискретизации, равной удвоенной тактовой частоте модулирующих последовательностей, коррекция искажений амплитудно-частотной характеристики и канальная фильтрация. ЦПУ 2 также осуществляет управление фазой выходного сигнала на основании управляющих кодов, выдаваемых БУКО 8.

Далее оцифрованный сигнал с выхода ЦПУ 2 поступает на вход БНС 9, где происходит накопление и сложение нескольких периодов повторения синхросигнала. Затем поток цифровых данных поступает на входы БВКФ 11 и БК 15, где сигнал перемножается с опорным сигналом. Опорный сигнал вырабатывается в ФОС 10 под управлением БУКО 8 и тактируется сигналом, поступающим от СТЧ 5.

В БВКФ 11 вычисляется функция взаимной корреляции входного и опорного синхросигналов при помощи двойного преобразования Фурье (ДПФ), определяется максимальное значение квадрата модуля функции взаимной корреляции Rmax(k), среднее значение квадрата модуля функции взаимной корреляции Rср(k), вычисляется отношение сигнал/шум q2(k)= R2max(k)/ R2ср(k). Операция повторяется для каждого значения расстройки по частоте k*Δf, где Δf – шаг поиска сигнала по несущей частоте, k=0, ±1, ±2... ±m.

Затем с выхода БВКФ 11 значения q2(k) поступают на БОС 12, где происходит сравнение с порогом и принимается решение об обнаружении или отсутствии сигнала в радиоканале.

При отсутствии сигнала БОС 12 выдает донесение на БУКО 8. БУКО 8 выдает донесение об отсутствии сигнала на БУ 6, а БУ 6 устанавливает новые параметры поиска путем передачи управляющей информации на БУКО 8 и ФОС 10.

При обнаружении сигнала БОС 12 выдает донесение на БУКО 8. БУКО 8 выдает донесение на БНС 9 и БК 15.

В БК 15 вычисляется функция взаимной корреляции входного и опорного сигналов при расстройке по частоте kО*Δf, определяется максимальное значение модуля функции взаимной корреляции. Вычисления повторяются для каждого периода сигнала в окрестности найденного максимального значения с шагом, равным половине элементарной посылки сигнала. По найденным значениям определяется максимальное значение функции взаимной корреляции и его местоположение.

Полученное значение временного сдвига относительно моментов дискретизации сигнала БК 15 передает в БОЗС 13, который формирует оценку временного сдвига. БОЗС 13 выдает полученные значения на ФЭ1 14, который осуществляет автоподстройку тактовой частоты для БНС 9, БО 16, БОФС 17 и СПИ 19.

После обнаружения информационного сигнала БО 16 осуществляет проверку достоверности обнаружения, путем вычисления на каждом периоде сигнала соотношения модулей функций взаимной корреляции входного сигнала и опорных синхронизирующего и информационного сигналов, усреднении этих оценок на определенном количестве периодов и сравнении результатов с пороговыми значениями.

После получения подтверждения обнаружения сигнала БО 16 выдает донесение в БУКО 8, который выдает донесение в СПИ 19.

На основе значений, полученных от ФЭ1 14 и БО 16, БОФС 17 определяет фазовый угол сигнала, затем передает вычисленные значения в ФЭ2 18.

ФЭ2 18 осуществляет автоподстройку несущей частоты и передает полученные значения на СПИ 19.

СПИ 19 на основании данных, полученных от БК 15, принимает решение о приеме бита «1», если разность фазовых углов находится в пределах от 0 до 180 градусов, в противном случае принимается решение о приеме бита «0». Затем СПИ 19 по шине ввода-вывода передает данные на БУ 6.

Прекращение выдачи информации и переход в режим поиска осуществляется по команде от БУ 6.

РЕАЛИЗАЦИЯ.

Блок АЦП 4 может быть реализован на базе микросхемы 1273ПВ5У (ОАО «СКТБ ЭС» г. Воронеж) или аналогичных ей по функциональности [3].

СТЧ 5 может быть реализован как устройство, описанное в [4, 5].

БУ 6 может быть реализован как устройство управления для помехозащищенной радиотехнической системы [6], включающее микропроцессор семейства 51х, например, на базе микропроцессоров [7, 8].

Блок КПУ 3 может быть реализован, например, на базе сигнальных процессоров из серии однокристальных программируемых многопроцессорных "систем на кристалле" на основе IP-ядерной (IP-intellectual property) платформы "МУЛЬТИКОР", которые содержат процессорные RISC-ядра с архитектурой MIPS32, выполняющие функции центрального процессора системы CPU (Central Processing Unit) и высокопроизводительные ядра процессоров-акселераторов для ЦОС с плавающей/фиксированной точкой [9] или аналогичных им по функциональности.

Блок ЦПУ 2 может быть реализован, например, на базе микросхемы 1288ХК1 [10] или аналогичных ей по функциональности.

АЛГОРИТМЫ.

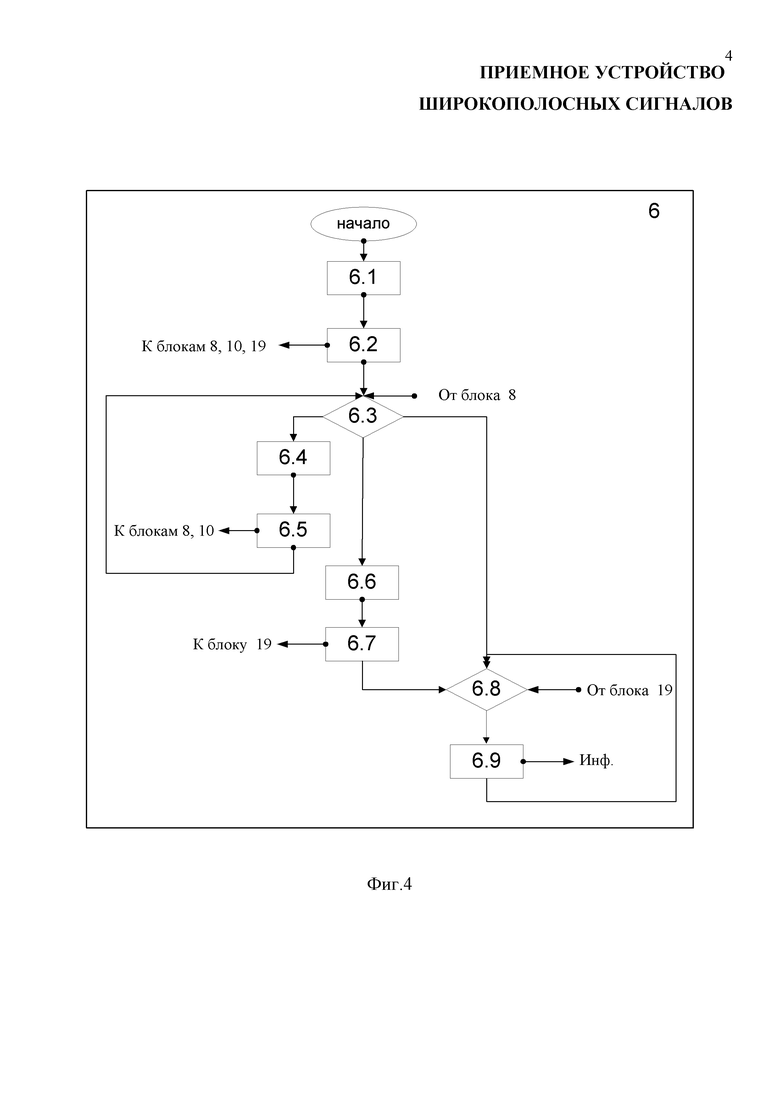

Укрупненный алгоритм функционирования БУ 6 приведен на фиг. 4.

При включении в блоке 6.1 происходит инициализация значений параметров управления.

Далее в блоке 6.2 происходит выдача начальных установок БУКО 8 и ФОС 10, активируется СПИ 19 сообщением об ожидании приема информации.

Далее в блоках 6.3 и 6.8 БУ 6 переходит в режим ожидания сообщений от БУКО 8 либо от СПИ 19. Если пришло сообщение от БУКО 8, что сигнал в радиоканале не найден, то происходит переход к блоку 6.4, где производится пересчет параметров для БУКО 8 и ФОС 10.

Далее в блоке 6.5 происходит выдача новых параметров БУКО 8 и ФОС 10 и возврат к блоку 6.3.

Если от БУКО 8 пришло сообщение, что сигнал в радиоканале обнаружен, то происходит переход к блоку 6.6, где производится инициализация данных для режима приема информации.

Далее в блоке 6.7 происходит выдача запроса на СПИ 19 о готовности приема очередного пакета данных, и переход к блоку 6.8 в режим ожидания сообщений от СПИ 19.

Далее в блоке 6.9 происходит прием очередного пакета данных от СПИ 19, обработка очередного пакета данных (проверка корректности пакета данных), декодирование и выдача информации, после чего происходит возвращение к блоку 6.8.

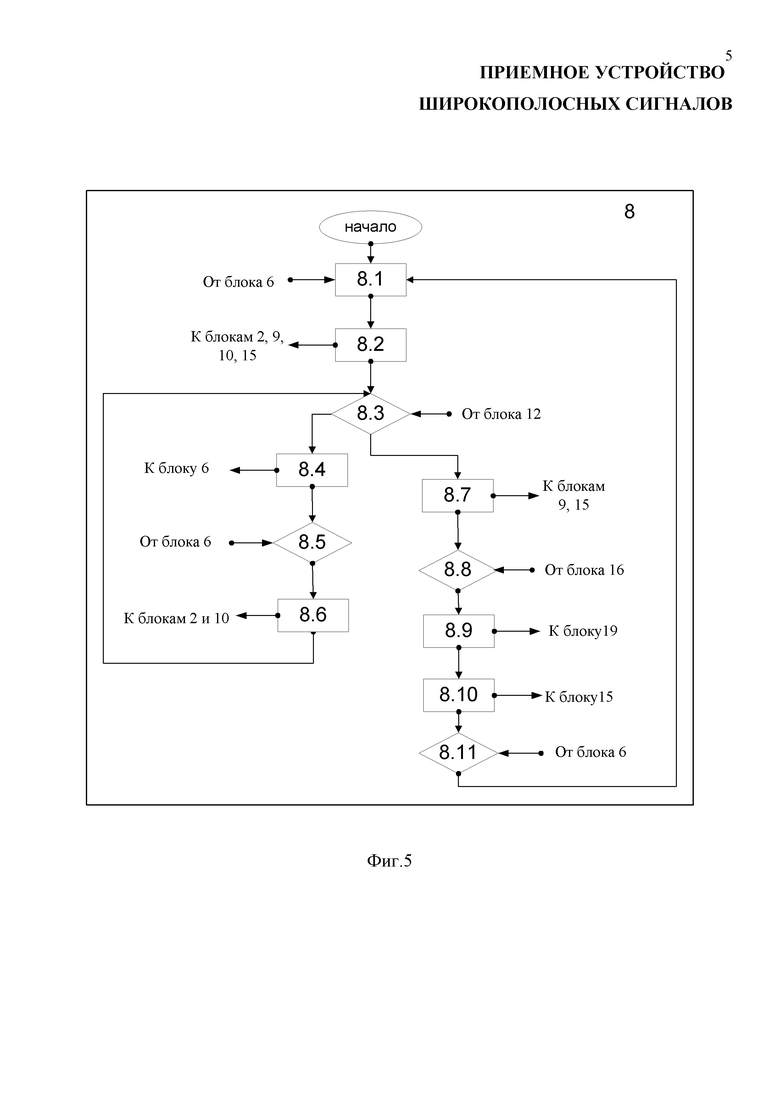

Укрупненный алгоритм функционирования БУКО 8 приведен на фиг. 5.

При включении в блоке 8.1 происходит прием начальных установок управления от БУ 6 и инициализация значений параметров управления блоками ЦПУ 2, БНС 9, ФОС 10 и БК 15.

Далее в блоке 8.2 происходит расчет текущих значений и выдача параметров управления на блоки ЦПУ 2, БНС 9, ФОС 10 и БК 15.

БУКО 8 переходит в режим ожидания сообщений от БОС 12.

В случае, если в блоке 8.3 пришло сообщение от БОС 12 об отсутствии сигнала, то происходит переход к блоку 8.4.

В блоке 8.4 БУКО 8 посылает сообщение на БУ 6 о необходимости перейти на следующий цикл поиска радиосигнала и установить новые параметры поиска.

Далее в блоке 8.5 БУКО 8 переходит в режим ожидания сообщений от БУ 6.

Далее в блоке 8.6 БУКО 8 принимает от БУ 6 очередные параметры управления значения и производит их выдачу на блоки ЦПУ 2 и ФОС 10, в результате определяются параметры режима для очередного поиска радиосигнала. Далее происходит возврат к блоку 8.3.

Если в блоке 8.3 пришло сообщение от БОС 12, который сообщает об обнаружении сигнала, то происходит переход к блоку 8.7, где выдается донесение об обнаружении сигнала на БНС 9 и БК 15.

Далее в блоке 8.8 БУКО 8 переходит в режим ожидания сообщений об обнаружении информационного сигнала от БО 16.

В случае, если пришло сообщение от БО 16, происходит переход к блоку 8.9, где происходит выдача донесения на СПИ 19 о начале приема информации.

Далее в блоке 8.10 БУКО 8 выдает сообщение об обнаружении информационного сигнала на БК 15, в результате чего начинают работать блоки подстройки частоты и фазы в режиме слежения за радиосигналом.

Далее в блоке 8.11 БУКО 8 переходит в режим ожидания сообщений о прекращении выдачи информации и переходе в режим поиска от БУ 6.

После приема сообщения происходит возврат к блоку 8.1.

Таким образом, совокупность введенных в предлагаемом устройстве новых блоков и их связей позволяет уменьшить время обнаружения сигнала и повысить точность синхронизации приемного устройства широкополосных сигналов, что в итоге позволяет осуществить адаптивную цифровую обработку принимаемого сигнала, оптимизировать алгоритмы синхронизации. Кроме того, использование современных аппаратных средств позволяет значительно уменьшить габаритные размеры с одновременным упрощением аппаратной реализации.

Источники информации:

1. Патент РФ №1788592. Устройство поиска псевдослучайной последовательности: МПК H04L 7/02, H04L 7/04 / Н.И. Козленко, Ю.В. Левченко, В.И. Сапрыкин, И. Г. Павлов; заявитель и патентообладатель Воронежский научно-исследовательский институт связи (RU). – №4921630/09, заявл. 26.03.1991, опубл. 15.01.1993, Бюл. №2.

2. Патент РФ №1840292. Приемное устройство широкополосных сигналов: МПК H04B 7/00 / А.П. Биленко, Н.И. Козленко, Р.Н. Рыжкова, Н.И. Пополитов, Ю.В. Левченко; заявитель и патентообладатель Воронежский научно-исследовательский институт связи (RU). – №3060708/09, заявл. 28.02.1983, опубл. 27.08.2006, Бюл. №24.

3.http://www.analog.com/ru/analog-to-digital-converters/ad-converters/ products/index.html - радиоэлектронные компоненты компании "Analog Device".

4. Патент РФ №2419201. Адаптивный синтезатор частот с коммутацией элементов кольца фазовой автоподстройки: МПК H03L 7/16 / Н.М. Тихомиров, А.В. Леньшин; заявитель и патентообладатель Открытое акционерное общество "Концерн "Созвездие" (RU). – №2010106933/09, заявл. 24.02.2010, опубл.: 20.05.2011, Бюл. № 14.

5. Патент РФ №2416158. Цифровой синтезатор частот: МПК H03L 7/18 / И.П.Усачев, Е.И. Стецура, В.В. Стецура; заявитель и патентообладатель Открытое акционерное общество "Концерн "Созвездие" (RU). – №2009134759/09, заявл. 16.09.2009, опубл.: 10.04.2011, Бюл. № 10.

6. Патент РФ №127957. Устройство управления для помехозащищенной радиотехнической системы: МПК G05B 19/05 / А.Н. Асосков, Ю.В. Левченко, И.Н. Малышева, Ю.А. Плахотнюк (RU); заявитель и патентообладатель ОАО «Концерн «Созвездие». № 2012149703/08; заявл. 21.11.2012, опубл.10.05.2013, Бюл. № 13. 3 с.

7. http://www.atmel.com/products/ - радиоэлектронные компоненты компании "ATMEL".

8. http://www.silabs.com/products/pages/default.aspx - радиоэлектронные компоненты компании "Silicon Labs".

9. http://www.multicore.ru - радиоэлектронные компоненты компании ГУП «НПЦ «Элвис» (г. Зеленоград).

10. http://www.transistor.by - радиоэлектронные компоненты компании УП "Завод ТРАНЗИСТОР" (г. Минск).

| название | год | авторы | номер документа |

|---|---|---|---|

| Приемное устройство широкополосных сигналов | 2021 |

|

RU2768249C1 |

| КОМБИНИРОВАННЫЙ ПОДВИЖНЫЙ РАДИОУЗЕЛ СВЯЗИ | 2005 |

|

RU2287898C1 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИОННЫХ СООБЩЕНИЙ ПО РАДИОНАВИГАЦИОННОМУ КАНАЛУ ИМПУЛЬСНО-ФАЗОВОЙ РАДИОНАВИГАЦИОННОЙ СИСТЕМЫ | 1999 |

|

RU2158933C1 |

| СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИОННЫХ СООБЩЕНИЙ ПО РАДИОНАВИГАЦИОННОМУ КАНАЛУ ИМПУЛЬСНО-ФАЗОВОЙ РАДИОНАВИГАЦИОННОЙ СИСТЕМЫ | 2006 |

|

RU2318220C1 |

| АДАПТИВНАЯ АНТЕННАЯ СИСТЕМА | 1995 |

|

RU2099837C1 |

| Многоканальное устройство измерения и регистрации рН | 1987 |

|

SU1518757A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ПОЛЯРИЗАЦИОННОЙ МАТРИЦЫ РАССЕЯНИЯ ОБЪЕКТА | 2001 |

|

RU2190239C1 |

| Устройство для обнаружения места дефекта оптического кабеля | 1989 |

|

SU1684750A1 |

| ИНФОРМАЦИОННО-АНАЛИТИЧЕСКАЯ СИСТЕМА МОНИТОРИНГА ОБСТАНОВКИ, ПРЕДУПРЕЖДЕНИЯ И ЛИКВИДАЦИИ ЧРЕЗВЫЧАЙНЫХ СИТУАЦИЙ | 2014 |

|

RU2558658C1 |

Изобретение относится к области радиотехники, в частности к системам обработки информации, использующим сложные широкополосные сигналы, и может найти применение в широкополосных помехозащищенных устройствах радиосвязи. Изобретение предназначено для уменьшения времени обнаружения сигнала и повышения точности синхронизации приемного устройства широкополосных сигналов. Устройство содержит приемный блок (ПБ), цифровое приемное устройство (ЦПУ), аналого-цифровой преобразователь (АЦП), синтезатор тактовой частоты (СТЧ), блок управления (БУ), опорный генератор (ОГ), корреляционное приемное устройство (КПУ), содержащее блок управления корреляционной обработкой (БУКО), блок накопления сигнала (БНС), формирователь опорных сигналов (ФОС), блок вычисления корреляционной функции (БВКФ), блок обнаружения синхропоследовательности (БОС), блок оценки задержки сигнала (БОЗС), первый фильтр-экстраполятор (ФЭ1), блок корреляторов (БК), блок обнаружения (БО), блок оценки фазы сигнала (БОФС), второй фильтр-экстраполятор (ФЭ2), схему приема информации (СПИ). 5 ил.

Приемное устройство широкополосных сигналов, содержащее приемный блок (ПБ), вход которого является входом устройства, аналого-цифровой преобразователь (АЦП), блок управления (БУ), выход которого является выходом устройства, причем ПБ последовательно соединен с АЦП, отличающееся тем, что введены цифровое приемное устройство (ЦПУ), синтезатор тактовой частоты (СТЧ), опорный генератор (ОГ) и корреляционное приемное устройство (КПУ), содержащее блок управления корреляционной обработкой (БУКО), первый выход которого является выходом КПУ, блок накопления сигнала (БНС), первый вход которого является первым входом КПУ, формирователь опорных сигналов (ФОС), первый вход которого является вторым входом КПУ, последовательно соединенные блок вычисления корреляционной функции (БВКФ) и блок обнаружения синхропоследовательности (БОС), последовательно соединенные блок оценки задержки сигнала (БОЗС) и первый фильтр-экстраполятор (ФЭ1), блок корреляторов (БК), последовательно соединенные блок обнаружения (БО), блок оценки фазы сигнала (БОФС) и второй фильтр-экстраполятор (ФЭ2), схему приема информации (СПИ), причем группы входов-выходов БУКО, ФОС, СПИ являются группой входов-выходов КПУ; при этом первый вход ЦПУ соединен с выходом АЦП, а выход соединен с первым входом КПУ, группа входов-выходов которого соединена с группой входов-выходов БУ; выход СТЧ соединен соответственно со вторыми входами ЦПУ, КПУ, АЦП; первый выход БУ соединен с первым входом ПБ, второй выход соединен с первым входом СТЧ, а третий выход соединен с третьим входом ЦПУ; первый выход ОГ соединен со вторым входом СТЧ, а второй выход соединен со вторым входом ПБ; выход КПУ соединен с четвертым входом ЦПУ;

кроме того, первый вход БВКФ соединен с первым выходом ФОС, выход БОС соединен с первым входом БУКО; первый выход ФЭ1 соединен со вторым входом БНС; первый вход БК соединен со вторым выходом ФОС, а первый выход соединен соответственно с входом БОЗС и первым входом СПИ; второй выход БО соединен со вторым входом БУКО, а первый вход соединен со вторым выходом БК; выход БНС соединен соответственно со вторыми входами БВКФ и БК, второй выход ФЭ1 соединен соответственно со вторыми входами БО, БОФС и СПИ, выход ФЭ2 соединен с третьим входом СПИ, второй выход БУКО соединен соответственно с третьими входами БНС, БК и со вторым входом ФОС.

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| РАДИОПРИЕМНОЕ УСТРОЙСТВО С НЕПРЕРЫВНОЙ АВТОМАТИЧЕСКОЙ РЕГУЛИРОВКОЙ ВОСПРИИМЧИВОСТИ | 2014 |

|

RU2562796C1 |

| Трубчатое перо | 1958 |

|

SU118142A1 |

| УСТРОЙСТВО СВЕРХШИРОКОПОЛОСНОЙ РАДИОСВЯЗИ С ПОВЫШЕННОЙ ПОМЕХОЗАЩИЩЕННОСТЬЮ | 2012 |

|

RU2527487C2 |

| РАДИОПРИЁМНОЕ УСТРОЙСТВО С КЛЮЧЕВЫМ УПРАВЛЕНИЕМ АМПЛИТУДОЙ РАЗМЫВАЮЩЕГО СИГНАЛА | 2016 |

|

RU2660660C2 |

| US 6967993 B1, 22.11.2005. | |||

Авторы

Даты

2019-06-18—Публикация

2018-07-23—Подача