Предлагаемое изобретение относится к области широкополосной радиосвязи и преимущественно может быть использовано для обеспечения помехозащищенной передачи сигналов в СДВ, ДВ и СВ диапазонах.

Известны приемные устройства широкополосных сигналов на основе согласованных фильтров (авт.св. №547773) или же корреляторов.

Недостатком устройств с согласованными фильтрами является сложность их практической реализации для сигналов с большими базами и большой длительности, значительный объем аппаратуры и нестабильность параметров.

Устройства, использующие обычные корреляторы, обладают, как правило, большим временем поиска сигнала, так как сама процедура поиска носит последовательный характер с перебором всех значений области неопределенности сигнала.

Этими недостатками не обладают устройства с цифроаналоговой обработкой сигналов (авт.св. 1840322), при которой входной сигнал сжимается во времени и обрабатывается корреляторами.

Однако помехозащищенность поиска сигнала в этих устройствах ограничена стабильностью частоты принимаемого сигнала.

Наиболее близким к заявляемому является устройство, описанное в авт.св. №1840131 (Устройство передачи и приема для широкополосной радиосвязи, 17.03.1980 г.).

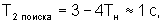

Блок-схема устройства-прототипа изображена на фиг.1, для которой введены следующие обозначения:

1 - приемный блок;

2- блок выделения информации;

3 - регулируемый усилитель;

4 - аналого-цифровой преобразователь (ДЦП);

5, 15 - блок корреляторов;

6 - блок выделения сигналов рассогласования;

7, 13 - регистр сдвига;

8 - сумматор;

9 - блок памяти;

10 - формирователь опорных сигналов;

11 - блок управления;

12 - цифроаналоговый преобразователь (ЦАП);

14 - пороговый блок;

16 - блок сравнения.

Устройство содержит последовательно соединенные приемный блок 1, АЦП 4, сумматор 8, блок памяти 9, ЦАП 12, блок корреляторов 15, пороговый блок 14 и блок управления 11, один выход которого соединен с блоком памяти 9, второй выход которого соединен со входом сумматора 8, второй выход блока управления 11 соединен со вторым входом блока корреляторов 15 через формирователь опорных сигналов 10 и регистр сдвига 13, второй вход блока управления 11 подключен к блоку корреляторов 15 через блок сравнения 16, а третий вход соединен с блоком корреляторов 5 через блок выделения сигналов рассогласования 6, второй выход формирователя опорных сигналов 10 соединен с регистром сдвига 7, выходы которого соединены с блоком выделения информации 2 и блоком корреляторов 5, другие входы которых соединены с выходом регулируемого усилителя 3, управляющий вход которого соединен с блоком корреляторов 5.

Входной сигнал поступает в приемный блок 1, в котором происходит предварительная селекция, перенос на промежуточную частоту обработки, режекция участков спектра, пораженных узкополосными помехами, бланкирование импульсных помех и усиление до фиксированного среднего уровня сигнала.

С выхода приемного блока 1 сигнал поступает на регулируемый усилитель 3 и АЦП 4.

В аналого-цифровом преобразователе 4 осуществляется дискретизация сигнала с частотой 4Fm, где Fm - тактовая частота модуляции принимаемого сигнала, и квантование выборок по уровням.

Формируемые массивы чисел через сумматор 8 подаются на блок памяти 9, емкость которого рассчитана на 4N чисел, где N - длина модулирующей псевдослучайной последовательности.

В первоначальный момент числа, поступающие с АЦП, непосредственно записываются в память, а по окончании записи 4N чисел они суммируются с ранее записанными в память. После записи всех чисел на интервале накопления сигнала происходит восстановление аналогового сигнала со сжатием его во времени. Для этого записанные числа периодически считываются из блока памяти 9 с частотой, гораздо большей частоты дискретизации, и подаются на цифроаналоговый преобразователь 12, восстанавливающий аналоговый сигнал.

Полученный сигнал, представляющий собой периодически повторяющийся сжатый во времени отрезок входного сигнала, поступает на блок корреляторов 15, в котором сворачивается с опорными последовательностями. Процедура поиска сигнала построена таким образом, что вычисляется вся функция взаимной корреляции записанного сигнала и опорной последовательности и выбирается максимальное значение, которое сравнивается с порогом.

При превышении порога устройство переходит в режим слежения и выделения информации в реальном масштабе времени.

Преимуществом устройства-прототипа является то, что за счет сжатия входного сигнала сокращается время обработки сигнала корреляторами.

К недостаткам следует отнести наличие дополнительных узлов, работающих в реальном масштабе времени. Основным недостатком устройства-прототипа является то, что помехозащищенность поиска сигнала сильно зависит от нестабильности его несущей частоты.

Это связано с тем, что при поиске осуществляется когерентное сложение (накопление) элементов сигнала. Если несущая частота сигнала отличается от ожидаемой на величину Δf, то при времени накопления, большем 1/Δf, наблюдаются значительные потери при когерентном накоплении.

Например, если несущая частота равна 500 кГц, а суммарная нестабильность опорных генераторов передатчика и приемника составляет 5.10-6, то расстройка частоты может составлять 2,5 Гц. Если время накопления равно 1/2,5 Гц=400 мс, то свертка сигнала будет равна нулю. При времени накопления 130 мс потери составят 1 дБ.

Таким образом, при такой расстройке делать время накопления больше 200 мс нельзя. Соответственно и помехозащищенность поиска сигнала ограничена этой цифрой.

Реальное макетирование показало, что при тактовой частоте последовательности 50 кГц и времени накопления 200 мс помехозащитенность поиска составлявт 24-25 дБ.

Цель предлагаемого изобретения - повышение помехозащищенности.

Увеличение помехозащищенности поиска достигается за счет последетекторного накопления корреляционных сверток. Для снижения времени поиска используется последовательная процедура обнаружения.

Кроме того, выделение информации и слежение за сигналом проводится с использованием тех же поисковых корреляторов, устраняются тем самым все узлы обработки, работающие в реальном масштабе времени (блоки 2, 3, 5, 6, 7).

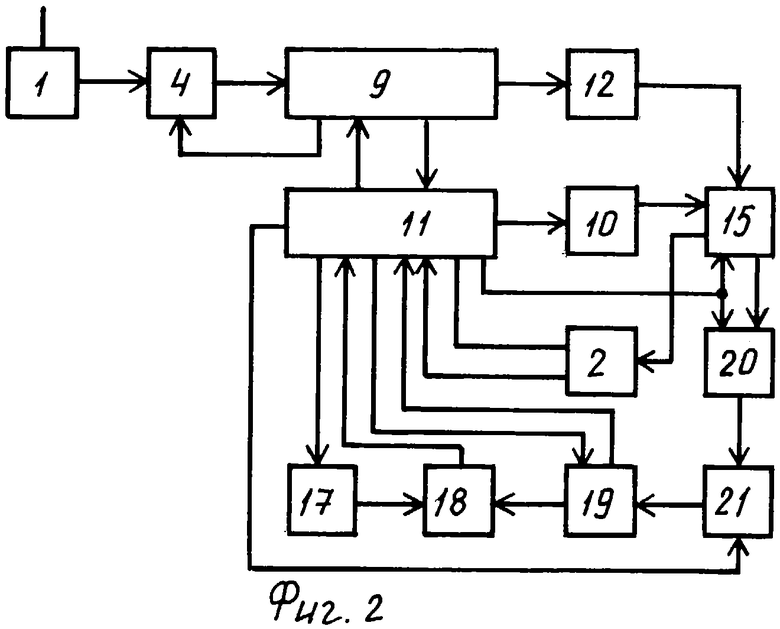

На основании этих выводов было разработано предлагаемое приемное устройство широкополосной радиосвязи. Его блок-схема изображена на фиг.2, для которой введены следующие обозначения:

1 - приемный блок;

2 - блок выделения информации (БВИ);

4 - аналого-цифровой преобразователь (АЦП);

9 - блок накопления и сжатия сигнала (БНС);

10 - формирователь опорных сигналов;

11 - блок управления;

12 - цифроаналоговый преобразователь;

15 - блок корреляторов;

17 - постоянное запоминающее устройство (ПЗУ);

18 - блок сравнения;

19 - блок выбора максимального кода;

20 - блок преобразования напряжение-код (БПНК);

21 - блок накопления корреляционных сверток (БНК).

Авторы объединили блоки 8 и 9 устройства-прототипа в один блок по выполняемой ими функции - блок накопления и сжатия сигнала 9.

Предлагаемое устройство содержит последовательно соединенные приемный блок 1, аналого-цифровой преобразователь 4, блок накопления и сжатия сигнала 9, цифроаналоговый преобразователь 12, блок корреляторов 15, блок преобразования напряжение-код 20, блок накопления корреляционных сверток 21, блок выбора максимального кода 19, блок сравнения 18, второй вход которого соединен с ПЗУ 17, а выход подключен к блоку управления 11, входы и выходы которого соединены с БНС 9, блоком выделения информации 2 и блоком выбора максимального кода 19, выходы блока управления 11 соединены с БНК 21, ПЗУ 17, блоком корреляторов 15, блоком преобразования напряжение-код 20 и формирователем опорных сигналов 10, выход которого соединен с блоком корреляторов 15, выход которого соединен с блоком выделения информации 2, выход БНС 9 соединен с АЦП 4.

Предлагаемое устройство работает следующим образом.

Входная смесь полезного сигнала, шумов и помех поступает в приемный блок 1, в котором происходит предварительная селекция, перенос на промежуточную частоту, режекция участков спектра, пораженных узкополосными помехами, бланкирование импульсных помех и усиление до фиксированного среднего уровня.

С выхода приемного блока 1 смесь полезного сигнала, флуктуационных шумов и широкополосных помех поступает на аналого-цифровой преобразователь 4.

В АЦП 4 осуществляется дискретизация сигнала с частотой 4Fm, где Fm - тактовая частота модулирующих псевдослучайных последовательностей, и квантуется по уровням. Количество уровней квантования можно выбрать равным 16. При этом выборки преобразуются в 4-разрядный двоичный код. Полученный поток цифровых данных непрерывно записывается в блок накопления и сжатия сигнала 9.

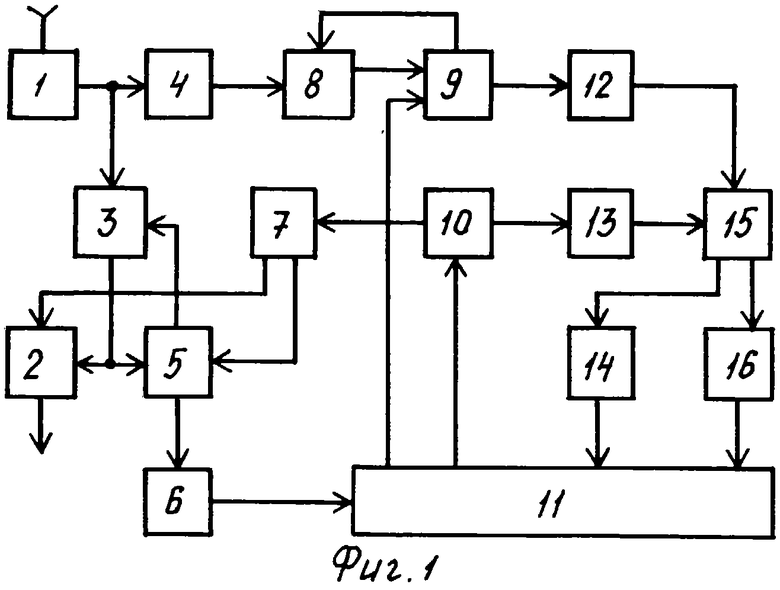

Схема БНС 9 приведена на фиг.3, на которой приняты следующие обозначения:

91 - сумматор;

92 - формирователь импульсов управления;

93 - оперативное запоминающее устройство;

94 - адресный счетчик;

96 - регистр;

95, 97 - коммутатор.

Непрерывный режим работы БВС достигается за счет поочередной записи чисел в два ОЗУ 93 и считывания из них.

Входная информация поступает на сумматор 91, где суммируется с содержимым регистра 96.

В начальный момент регистр 96 обнулен и входные числа непосредственно проходят на входы ОЗУ 93, представляющего собой матрицу стандартных быстродействующих микросхем оперативной памяти. Объем памяти рассчитан на 4Nр - разрядных двоичных чисел, где N определяется максимальной длиной принимаемых псевдослучайных последовательностей, а число p - количеством накапливаемых периодов сигнала.

Первые 4N выборок записываются в ОЗУ непосредственно. Номера ячеек ОЗУ задаются адресным счетчиком. При записи следующих чисел информация из соответствующей ячейки ОЗУ 93 считывается, записывается в регистр 96, суммируется с приходящим числом и записывается в ту же ячейку ОЗУ. Если на длине отрезка накопления укладывается К периодов сигнала, то к окончанию записи в каждой ячейке ОЗУ хранится сумма К чисел, соответствующих выборкам сигнала, отстоящим на период ПСП.

Разрядность такой суммы определяется разрядностью чисел и числом слагаемых К. Если, например, К=16, а числа четырехразрядные, то сумма может быть 8-разрядной, поэтому ОЗУ 93 должно быть рассчитано на хранение 8-разрядных чисел.

По окончанию записи 4NK чисел очередные выборки начинают записываться во второе ОЗУ 93, а ранее записанная информация периодически считывается из ОЗУ с высокой частотой, стробируется в регистре 96 и выдается на ЦАП 12 через открытый коммутатор 97. После записи следующих 4NK чисел это ОЗУ опять переходит в режим накопления, а информация выдается со второго ОЗУ и т.д. Управление режимами осуществляется за счет переключения установочных и тактовых импульсов адресных счетчиков 94, импульсов запись/считывания и выбора кристаллов ОЗУ, а также тактовых импульсов и установочных импульсов регистров 96 в коммутаторе 95.

В блоке БНС 9 предусмотрена внешняя принудительная синхронизация момента начала записи выборок и считывания за счет установки адресных счетчиков в исходное состояние.

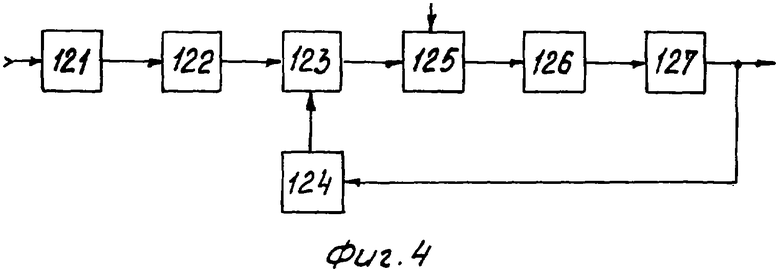

Сжатые потоки данных с выхода БНС 9 поступают на входы цифроаналогового преобразователя 12, функциональная схема которого изображена на фиг.4.

Входные числа преобразуются в ступенчатое напряжение в преобразователе код-напряжение 121, которое фильтруется в корректирующем фильтре нижних частот 122, усиливается в регулируемом усилителе 123, переносится на промежуточную частоту в смесителе 125, фильтруется в полосовом фильтре 126 и усиливается в блоке 127.

Выходной сигнал усилителя 127 одновременно подается на детектор АРУ 124, формирующий управляющее напряжение для усилителя 123. За счет работы кольца АРУ средний уровень выходного напряжения поддерживается постоянным.

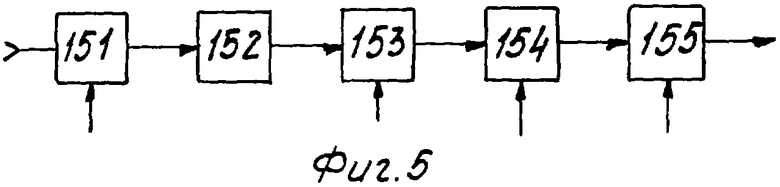

С выхода ЦАП 12 аналоговый сигнал поступает на блок корреляторов, состоящий из идентичных каналов, функциональная схема которых изображена на фиг.5.

В каждом корреляторе входной сигнал перемножается с опорной видеопоследовательностью в перемножителе 151, предварительно фильтруется в полосовом фильтре 152, переносится на вторую промежуточную частоту в смесителе 153 и поступает на радиоинтегратор со сбросом 154, представляющий собой узкополосный контур со сбросом.

Сигнал с выхода радиоинтегратора 154 детектируется пиковым детектором со сбросом 155 и поступает на выход блока.

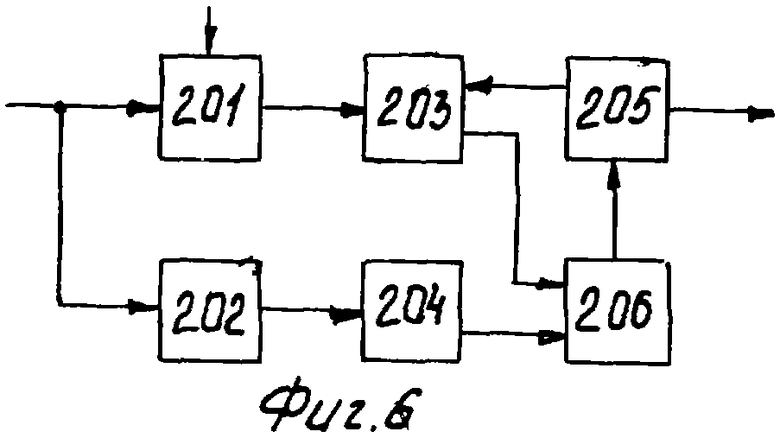

Блок преобразования напряжение-код 20 (фиг.6) состоит из следующего:

201 - коммутатор каналов;

202 - сумматор;

203 - ступенчатый делитель напряжения;

204 - фильтр нижних частот;

205 - счетчик кода;

206 - компаратор.

В блоке БПНК (20) напряжения корреляционных сверток преобразуются в цифровую форму. Характеристика преобразования выбрана таким образом, что коды сверток пропорциональны квадратам отношений напряжений сверток и оценки дисперсии шума.

Это достигается следующим образом.

Напряжения корреляционных сверток с выходов блока корреляторов 15 суммируются в блоке 202 и усредняются в фильтре нижних частот 204. На выходе ФНЧ 204 формируется оценка среднего значения сверток, которая пропорциональна дисперсии шумов.

Входные сигналы с блока корреляторов 15 поочередно коммутируются на вход ступенчатого делителя напряжения 203 коммутатором 201. Коэффициенты деления блока 203 выбраны по закону корня квадратного. Выходное напряжение делителя сравнивается с сигналом фильтра 204 в компараторе 206.

Делитель управляется счетчиком 205, который последовательно перебирает все коэффициенты деления. Как только напряжение на выходе делителя станет меньше напряжения фильтра, фиксируется код деления и выдается в качестве кода напряжение свертки. Таким образом, напряжения корреляционных сверток нормируются по шуму и преобразуются в цифровую форму.

Коды корреляционных сверток поступают на блок накопления корреляционных сверток 21.

Алгоритм поиска сигнала построен таким образом, что за время считывания информации из каждого ОЗУ 93 вычисляется вся функция взаимной корреляции считываемого отрезка сигнала и опорной последовательности и записывается в БНК 21.

Рассмотрим этот процесс более подробно. Для этого вернемся к описанию работы БНС 9 еще раз. Частота записи выборок в ОЗУ 93 4Fm. Если частота считывания из ОЗУ 93 равна fсч, а число накапливаемых периодов сигнала равно К, то за время записи информации в одно из ОЗУ 93 второе ОЗУ 93 успеет  раз считать записанный сигнал.

раз считать записанный сигнал.

Например, если Fm=50 кГц, fсч=8 МГц, К=16, то каждый записанный отрезок сигнала считывается 640 раз. При каждом считывании на блок корреляторов 15 подаются опорные последовательности с новыми временными сдвигами относительно считываемого сигнала. Частота следования импульсов последовательностей равна fсч/4=2 МГц. Задержка между последовательностями равна длительности одного импульса. Если число корреляторов равно n, то за один период считываемой информации вычисляется n значений функции взаимной корреляции. За все время считывания вычисляется 640n значений. Таким образом, если длина последовательностей равна, например, 1023, то для того чтобы вычислить все ее 1023 значения функции взаимной корреляции необходимо всего два коррелятора (n=2).

Вычисленные значения сверток записываются в БНК 21 не сразу. Первые 50-100 циклов считывания информации из ОЗУ 93 уходят на формирование оценки дисперсии шума в БПНК 20. После этого цифровые коды сверток записываются в БНК 21.

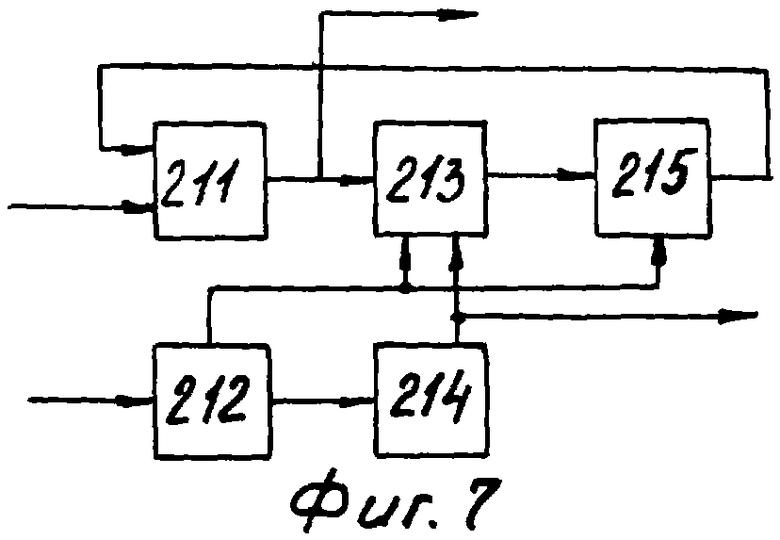

Блок накопления корреляционных сверток 21 (фиг.7) содержит следующее:

211 - сумматор;

212 - формирователь импульсов управления;

213 - оперативное запоминающее устройство;

214 - адресный счетчик;

215 - регистр.

В первом такте накопления коды сверток записываются в ОЗУ 213 по адресам, соответствующим их временным задержкам. В последующих тактах они суммируются с предыдущими значениями и записываются в ОЗУ 213. Для этого информация из ОЗУ 213 предварительно записывается в регистр 215, складывается с новым значением кода свертки и записывается в ОЗУ 213. Таким образом осуществляется последетекторное накопление корреляционных сверток. В силу того что каждый код пропорционален квадрату отношения напряжения свертки и дисперсии шума, накопление является оптимальным в условиях меняющейся помеховой обстановки.

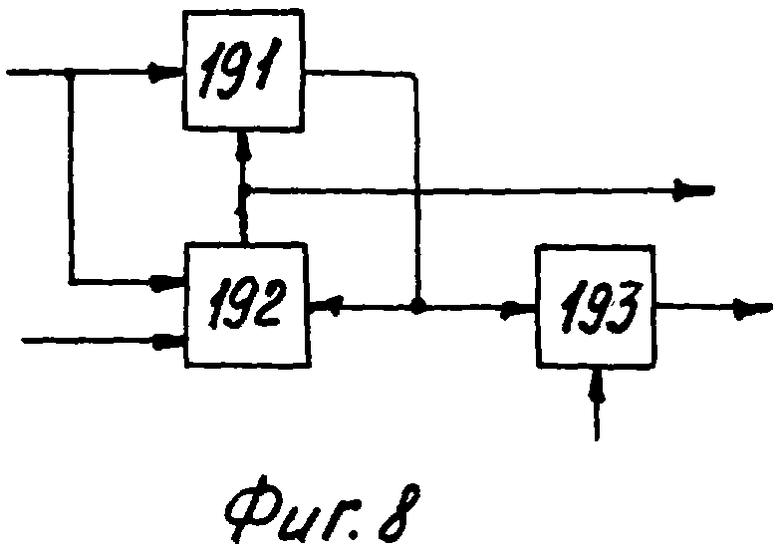

Суммарные значения кодов с выхода сумматора 211 вместе со своими номерами, задаваемыми адресным счетчиком 214, выдаются на блок выбора максимального кода 19 (фиг.8), содержащий следующее:

191 - схема сравнения;

192 - регистр;

193 - реверсивный счетчик.

В блоке 19 на каждом такте накопления сигнала осуществляется выбор максимального из N значений корреляционных сумм и определение его номера. Для этого каждое значение кодов сумм сравнивается с содержимым регистра 192 и в случае превышения его записывается в регистр 192, а его номер записывается в реверсивный счетчик, работающий в режиме параллельного регистра. После перебора всех N значений кодов в регистр 192 устанавливается максимальный код, а в счетчике 193 - его номер.

Значение максимального кода поступает на блок сравнения 18, где сравнивается с кодами порогов, выдаваемых постоянным запоминающим устройством 17.

В конце каждого такта накопления сигнала блок управления 11 выбирает из ПЗУ 17 два значения порогов и поочередно выдает их на блок сравнения 18.

Если значение максимального кода не превышает меньший из порогов, поиск прекращается. Если превышает больший из порогов, сигнал считается обнаруженным. В остальных случаях поиск продолжается.

Благодаря такой последовательной процедуре поиска удается значительно сократить среднее время поиска. Для того чтобы в блоке 21 не наступило переполнение ОЗУ 21, количество тактов суммирования корреляционных сверток ограничивается некоторым числом, после которого автоматически принимается решение об отсутствии сигнала.

В случае решения об отсутствии сигнала приемник либо возобновляет поиск сигнала, либо переходит на поиск следующего сигнала, если система связи многоканальная. При обнаружении сигнала приемник синхронизирует момент начала записи информации в БНС 9 с началом принимаемого сигнала. Для этого блок управления 11 в момент переключения ОЗУ 93, соответствующий началу записи очередного отрезка сигнала, начинает выдавать на реверсивный счетчик 193 импульсы с частотой принимаемой последовательности. Счетчик 193 работает на вычитание до тех пор, пока не перейдет в нулевое состояние. При этом он выдает импульс "заема". Количество тактов, пришедших на счетчик до появления этого импульса, равно ранее записанному в него номеру свертки с максимальным значением, т.е. найденной фазе сигнала. Из импульса "заема" блок управления 11 формирует сигнал фазирования момента начала записи информации в блок БНС 9.

Блок 9 переводится в режим записи одного периода последовательностей, а приемник в режим слежения и выделения информации.

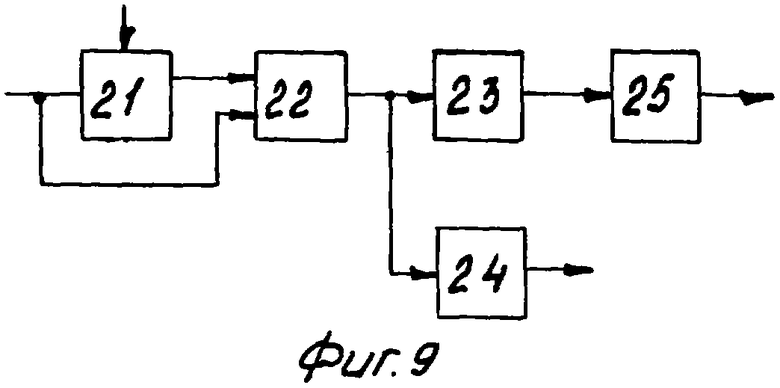

Выделение информации и сигнала рассогласования по фазе последовательностей происходит в БВИ 2. Для этого при каждом цикле считывания информации из БНС 9 одним из корреляторов блока 15 вычисляется свертка с последовательностями информационных "1" и "0", а также последовательностями, сдвинутыми относительно них на половину длительности элементарного импульса. Блок выделения информации 2 (фиг.9) состоит из следующего:

21 - аналоговое запоминающее устройство;

22 - компаратор;

23, 24 - триггер;

25 - декодер.

Напряжение сверток о коррелятора поступает на аналоговое запоминающее устройство 21 и компаратор 22. Свертка с последовательностью информационного "0" запоминается в АЗУ 21 и сравнивается со сверткой последовательности информационной "1". Результат сравнения фиксируется триггером 23 и поступает на декодер 25. После этого в АЗУ 21 запоминается напряжение свертки с последовательностью, задержанной на половину такта, и сравнивается с напряжением свертки с последовательностью, опережающей сигнал на половину такта. Результат сравнения фиксируется триггером 24 и выдается в качестве сигнала рассогласования по фазе. По этому сигналу блок управления 11 сдвигает импульсы дискретизации сигнала на определенное время в сторону задерживания или опережения. Тем самым осуществляется слежение по задержке (фазе) за принимаемыми последовательностями.

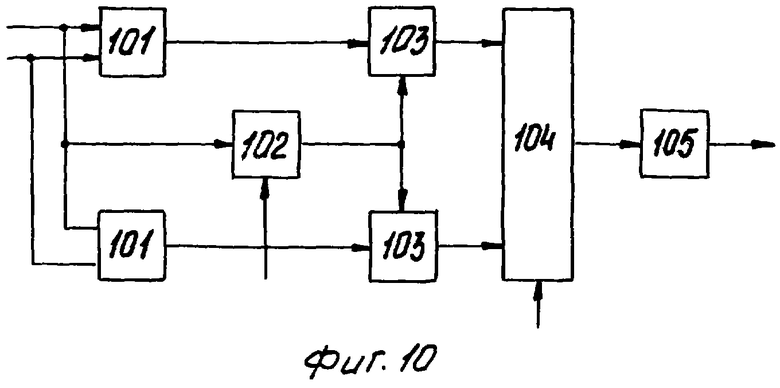

Формирователь опорных сигналов 10 (фиг.10) содержит следующие блоки:

101 - генератор псевдослучайной последовательности;

102 - сумматор по модулю два;

103 - регистр сдвига;

104 - мультиплексор;

105 - преобразователь код-напряжение;

Блок 10 формирует опорные псевдослучайные последовательности с частотой fсч/4.

Генераторы 101 вырабатывают последовательности, соответствующие "1" и "0" информации, которые сдвигаются в регистрах 103. Количество разрядов регистров равно числу корреляторов. Сигналы с выходов регистров через мультиплексор 104 подаются на преобразователь код-напряжение 105.

В режиме поиска на выходах ПКН 105 формируются трехуровневые сигналы, пропорциональные сумме последовательностей "0" и "1". В режиме приема информации в ПКН формируются поочередно последовательности "1" и "0", а также сдвинутые относительно них на половину такта в сторону опережения или задерживания. В последнем случае тактовые импульсы регистров 103 инвертируются. Требуемая коммутация обеспечивается мультиплексором 104 и сумматором по модулю два 102.

Генераторы ПСП 101 выполнены с внешней установкой, что позволяет фазироватъ их с моментом начала считывания информации из БНС 9, а также принимать последовательности переменной длительности. Сканирование в режиме поиска осуществляется за счет "выкусывания" тактовых импульсов генераторов в блоке управления 11.

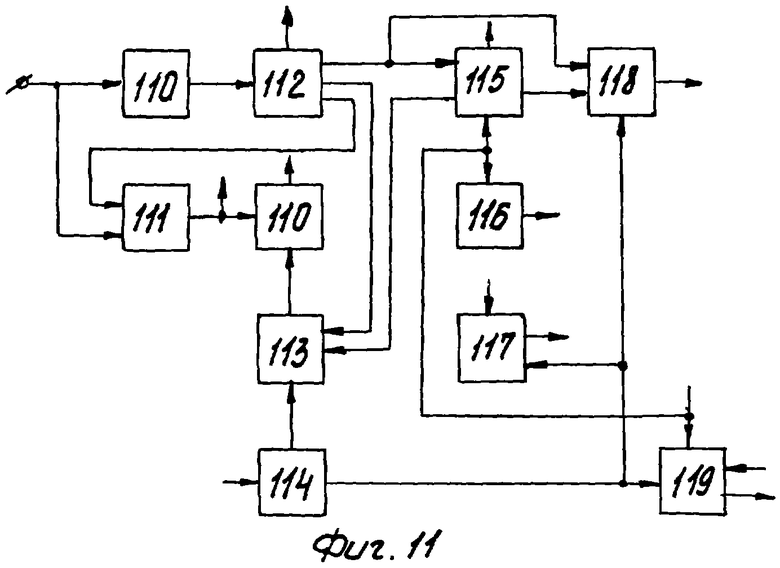

Структурная схема блока управления 11 (фиг.11) содержит следующее:

110 - счетчик;

111 - схема И;

112 - дешифратор;

113 - коммутатор;

114 - схема принятия решения;

115 - формирователь защитного интервала;

116 - счетчик циклов накопления;

117 - схема слежения за задержкой;

118 - схема управления опорными последовательностями;

119 - схема фазирования.

С блока БНС 9 поступает сигнал частоты fсч/4 на один счетчик 110 непосредственно, а на второй через схему И.

Первый счетчик 110 выполняет функцию таймера для процесса интегрирования сигнала в блоке корреляторов 15. Необходимые сигналы управления блоком 15 вырабатывает дешифратор 112 состояний счетчика 110. Он же вырабатывает сигнал разрешения тактовых импульсов второго счетчика 110, поступающий на второй вход схемы И. За один такт интегрирования в блоке 15 на второй счетчик 110 поступает (N-n) импульсов, где N - длина последовательностей, а n - число корреляторов в блоке 15.

Второй счетчик 110 играет роль эквивалента генераторов ПСП. Его тактовые импульсы поступают одновременно на блок 10 и являются тактовыми импульсами генераторов ПСП, а выход пересчета служит для фазирования генераторов ПСП. За один такт интегрирования фаза второго счетчика 110 и генераторов ПСП сдвигается на n тактов частоты fсч/4 относительно фазы первого счетчика 110.

Дешифратор 112 вырабатывает сигнал фазирования информации, считываемой из БНС 9, благодаря чему фаза считываемой информации жестко связана с состоянием счетчика 110, а фаза опорных последовательностей изменяется на n тактов относительно считываемого сигнала в каждом такте интегрирования.

Так происходит процесс сканирования сигнала.

Формирователь защитного интервала 115 в каждом такте накопления отсчитывает первые 50-100 циклов считывания информации из БНС 9, необходимые для формирования оценки дисперсии шума, после чего выдает сигнал разрешения записи кодов сверток в блок 21. Одновременно он выдает импульс, который, проходя через коммутатор 113, фазирует счетчики 110.

При этом генераторы опорных последовательностей оказываются сфазированы с началом считывания информации из БНС 9.

Счетчик 116 подсчитывает число циклов накоплений сигнала и формирует сигналы управления ПЗУ 17.

Схема принятия решения 114 на основе анализа сигналов превышения порогов принимает решение об обнаружении либо отсутствии сигнала в радиоканале. При обнаружении она меняет потенциалы на своих выходах.

При этом сканирование сигналов прекращается, так как коммутатор 113 подключает к установочному входу счетчика 110 один из выходов дешифратора 112 и оба счетчика 110 все время сфазированы.

Схема 119 осуществляет фазирование момента начала записи информации в БНС 9 с обнаруженным сигналом. Для этого после обнаружения сигнала в момент прихода очередного импульса начала записи схема 119 начинает выдавать на реверсивный счетчик 193 импульсы с частотой принимаемой последовательности, до тех пор пока со счетчика 193 не придет сигнал заема.

Из этого сигнала схема 119 вырабатывает один импульс, фазирующий начало записи информации в БНС и прекращает работу.

Схема слежения за задержкой 117 из сигналов рассогласования по фазе, поступающих с триггера 24, вырабатывает импульсы управления БНС 9, по которым изменяется фаза импульсов дискретизации, выдаваемых БНС 9 на АЦП 4.

Таким образом, в предлагаемом устройстве вся обработка сигнала осуществляется в сжатом масштабе времени с использованием всего одного блока корреляторов. Это значительно снижает габариты и стоимость устройства. Благодаря последетекторному накоплению корреляционных сверток повышается помехозащищенность поиска сигнала при незначительном увеличении времени поиска.

На основе предлагаемого устройства и устройства-прототипа были изготовлены два макета приемников. При этом оказалось, что габариты и потребляемая мощность предлагаемого устройства примерно в два раза меньше, чем устройства-прототипа, а помехозащищенность поиска сигнала на 5-6 дБ выше.

В качестве базового образца может выбрана аппаратура Кулон-III, построенная на принципах многоканальной корреляционной обработки.

При базе сигналов N=1023, числе корреляторов n=10 и времени накопления сигнала Тн=0,2 с время поиска сигнала в приемниках подобного типа составит

Время поиска в предлагаемом устройстве составляет

т.е. в двадцать раз меньше.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1983 |

|

SU1840196A1 |

| УСТРОЙСТВО ПОИСКА И СЛЕЖЕНИЯ ЗА ШИРОКОПОЛОСНЫМ СИГНАЛОМ | 1983 |

|

SU1840276A1 |

| Приёмное устройство широкополосных сигналов | 2018 |

|

RU2691731C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1985 |

|

SU1840079A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1984 |

|

SU1840075A1 |

| УСТРОЙСТВО ПЕРЕДАЧИ И ПРИЕМА ДЛЯ ШИРОКОПОЛОСНОЙ РАДИОСВЯЗИ | 1980 |

|

SU1840131A1 |

| Устройство для поиска шумоподобного сигнала | 1984 |

|

SU1277415A1 |

| УСТРОЙСТВО ДЛЯ ОДНОВРЕМЕННОГО ПРИЕМА СИГНАЛОВ РАЗЛИЧНЫХ СИСТЕМ СПУТНИКОВОЙ НАВИГАЦИИ | 2015 |

|

RU2611069C1 |

| УСТРОЙСТВО ПОИСКА ШУМОПОДОБНОГО СИГНАЛА | 1985 |

|

SU1840083A1 |

| УСТРОЙСТВО ПОИСКА ШИРОКОПОЛОСНОГО СИГНАЛА | 1986 |

|

SU1840221A1 |

Изобретение относится к области широкополосной радиосвязи и может быть использовано для обеспечения помехозащищенной передачи сигналов в СДВ, ДВ и СВ диапазонах. Технический результат - повышение помехозащищенности устройства. Сущность изобретения состоит в том, что предлагаемое устройство содержит последовательно соединенные приемный блок 1, аналого-цифровой преобразователь (АЦП) 4, блок накопления и сжатия сигнала (БНС) 9, цифроаналоговый преобразователь 12, блок корреляторов (15), блок преобразования напряжение-код 20, блок накопления корреляционных сверток (БНК) 21, блок выбора максимального кода 19, блок сравнения 18, второй вход которого соединен с постоянным запоминающим устройством (ПЗУ) 17, а выход подключен к блоку управления 11, входы и выходы которого соединены с (БНС) 9, блоком выделения информации 2 и блоком выбора максимального кода 19, выходы блока управления 11 соединены с БНК 21, ПЗУ 17, блоком корреляторов 15, блоком 20 и формирователем опорных сигналов 10, выход которого соединен с блоком 15, вход которого соединен с блоком выделения информации 2, а выход БНС 9 соединен с АЦП 4. Увеличение помехозащищенности поиска достигается за счет последетекторного накопления корреляционных сверток. Для снижения времени поиска используется последовательная процедура обнаружения. Кроме того, выделение информации и слежение за сигналом проводится с использованием поисковых корреляторов, при этом устраняются все узлы обработки, работающие в реальном масштабе времени. 4 з.п. ф-лы, 11 ил.

| Авт | |||

| св | |||

| Устройство поиска псевдослучайного сигнала по задержке | 1975 |

|

SU547773A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Авт | |||

| св | |||

| УСТРОЙСТВО ПЕРЕДАЧИ И ПРИЕМА ДЛЯ ШИРОКОПОЛОСНОЙ РАДИОСВЯЗИ | 1980 |

|

SU1840131A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

2006-08-27—Публикация

1983-02-28—Подача