Изобретение относится к импульсной технике, к устройствам для манипулирования импульсами, в частности к устройствам для формирования импульсов с использованием линий задержки, и может быть использовано в аппаратуре для прецизионного генерирования, запуска и синхронизации электрических сигналов.

Известна регулируемая схема задержки электрических сигналов, содержащая цепочку последовательно включенных ступеней задержки электрических сигналов с одинаковым временем задержки, выход каждой из которых соединен с селектором и с входом последовательно включенного с ним управляющего элемента (патент US 5668491 «Variable delay circuit)), публикация от 16.09.1997).

Чем больше ступеней задержки, соединенных друг с другом последовательно в схеме, тем ниже точность выдачи сигнала при осуществлении регулировки временной задержки в широком диапазоне значений. В известной схеме для реализации регулировки времени задержки в широком диапазоне, ступени должны иметь одинаковое время распространения сигнала, чтобы обеспечить линейность и детерминированность регулировки времени задержки. В реальности, каждая ступень задержки имеет погрешность времени распространения. При последовательном соединении ступеней погрешности складываются, вследствие чего погрешность на выходе увеличивается и ее величина зависит от количества ступеней, используемых для обеспечения заданного диапазона задержки.

В известной схеме учтены времена распространения сигналов через ступени задержки и времена распространения сигналов по межсоединениям между ступенями. Значения времени распространения по межсоединениям между ступенями можно подобрать, чтобы скомпенсировать погрешность суммарной задержки, однако, при необходимости регулирования времени задержки в широком диапазоне значений, этих мер недостаточно из-за разброса параметров соединенных последовательно ступеней задержки.

Наиболее близкой к предлагаемому изобретению по совокупности известных признаков является регулируемая схема задержки электрических сигналов, содержащая каскад из множества последовательно включенных ступеней задержки электрических сигналов с различным временем задержки, выход каждой из которых соединен с селектором (патент US 6459319 «Variable delay circuit and semiconductor integrated circuit having the same», публикация от 01.10.2002). Данная схема выбрана в качестве прототипа. В данной схеме предусмотрена подача командных сигналов на ступени задержки и получение на выходе ступеней задержанных сигналов с различным временем задержки, в зависимости от полученного командного сигнала. Селектор получает задержанные сигналы для выбора и вывода одного из них в ответ на командные сигналы.

Так. же, как и рассмотренная выше., данная схема не позволяет обеспечить точность выдачи задержанного сигнала при необходимости регулирования временной задержки в широком диапазоне значений. В частности, при необходимости регулирования временной задержки в диапазоне порядка нескольких миллисекунд с пикосекундным разрешением и точностью, требуется использовать большое количество ступеней задержки, при этом отдельные ступени должны обеспечивать достаточно длительную задержку с высокой точностью. Схема задержки, обеспечивающая такие требования, является достаточно сложной, включает много компонентов с различными характеристиками, использование которых приводит к суммарной погрешности, не позволяющей обеспечить получение необходимых выходных параметров схемы.

Техническая проблема, которая решается за счет создания изобретения -разработка регулируемой схемы задержки электрических сигналов, позволяющей осуществлять регулирование временной задержки в широком диапазоне значений с высоким временным разрешением и высокой точностью срабатывания.

Техническая проблема решается за счет того, что регулируемая схема задержки, содержащая каскад соединенных последовательно ступеней задержки электрических сигналов с различным временем задержки, выход каждой из которых соединен с селектором, содержит дополнительный блок задержки, включающий преобразователь входного сигнала, соединенный с источником. входного сигнала, тактовый генератор, контроллер и двоичный счетчик, последний соединен с входом каскада, тактовым генератором, преобразователем и контроллером, который в свою очередь соединен с преобразователем и селектором, при этом период подачи импульсов тактового генератора на двоичный счетчик не превышает суммарное время задержки, обеспечиваемое всеми ступенями каскада.

При этом тактовый генератор может быть соединен с преобразователем. Схема может содержать параллельно включенный с каскадом, по крайней мере, еще один каскад соединенных последовательно ступеней задержки электрических сигналов с различным временем задержки, выход каждой из которых соединен с селектором этого каскада, а вход каскада соединен со своим дополнительным блоком задержки, двоичный счетчик которого соединен со своим преобразователем входного сигнала, связанным с общим источником входного сигнала.

Включение в регулируемую схему дополнительного блока задержки сигналов позволяет расширить диапазон работы схемы, т.к. обеспечивает задержку распространения сигнала с высокой дискретностью, а именно, с периодом подачи импульсов тактового генератора на двоичный счетчик, не превышающим суммарное время задержки, обеспечиваемое всеми ступенями каскада.

Основным элементом дополнительного блока задержки является двоичный счетчик, на который подается сигнал тактового генератора, входной сигнал от источника и сигналы уставки задержки от контроллера. В двоичном счетчике предусмотрена схема сравнения с сигналом уставки, благодаря наличию которой выходной сигнал дополнительного блока задержки генерируется при равенстве значения счетчика сигналам уставки.

Чтобы сигнал уставки подавался на дополнительный блок задержки и последовательно включенные ступени каскада, в схеме предусмотрен контроллер.

При условии, что двоичный счетчик подключен к источнику входного сигнала, соединенному с тактовым генератором, предлагаемая регулируемая схема задержки позволит осуществить управление системами с большим количеством каналов на большой площади.

В регулируемой схеме задержки, выполненной в соответствии с изобретением, общая задержка выходного сигнала складывается из суммарного времени задержки ступеней каскада и времени задержки дополнительного блока, при этом одновременно обеспечивается возможность реализации времени задержки с интервалом, не превышающим суммарное время задержки, обеспечиваемое всеми ступенями каскада. При выполнении этого условия обеспечивается возможность регулирования временной задержки в широком диапазоне с высоким временным разрешением и обеспечивается высокая точность срабатывания в диапазоне, превышающем период подачи импульсов тактового генератора на двоичный счетчик, с точностью, обеспечиваемой каскадом последовательно соединенных ступеней задержки. Регулируемая схема задержки может включать два и более параллельно включенных каскадов последовательно соединенных ступеней задержки для обеспечения одновременной синхронной работы нескольких функциональных схем автоматизации технологических процессов. Изобретение поясняется графическими материалами.

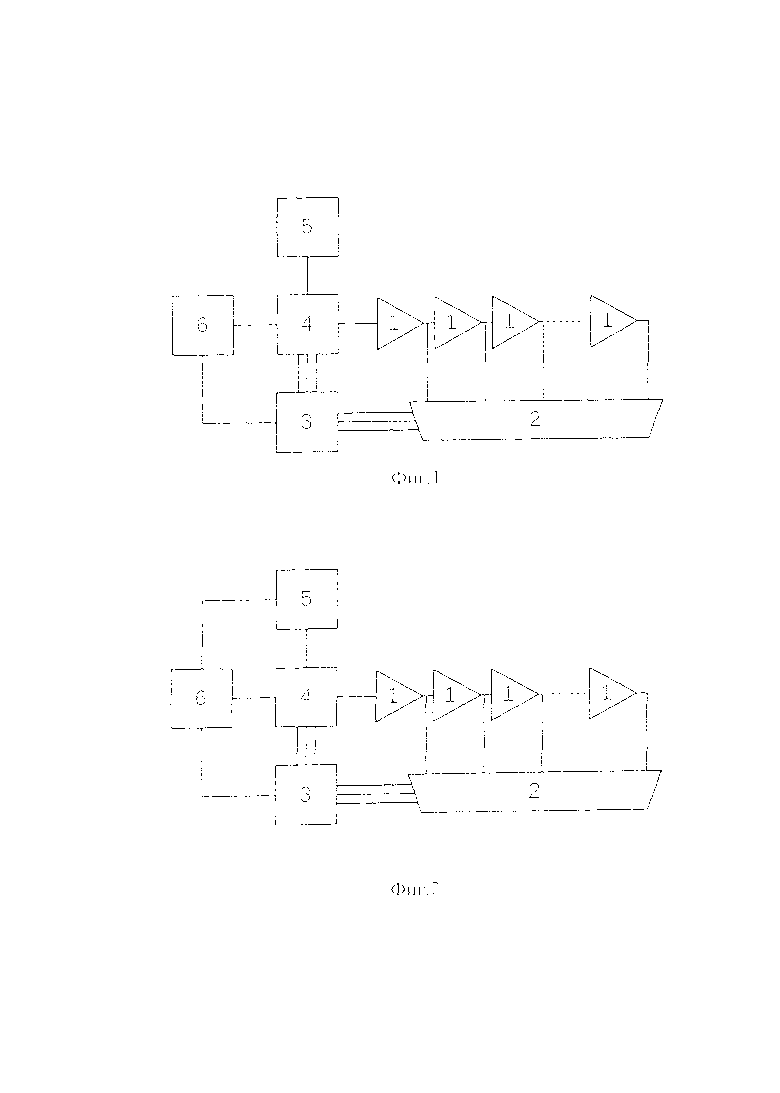

На фиг. 1 изображена заявляемая регулируемая схема задержки.

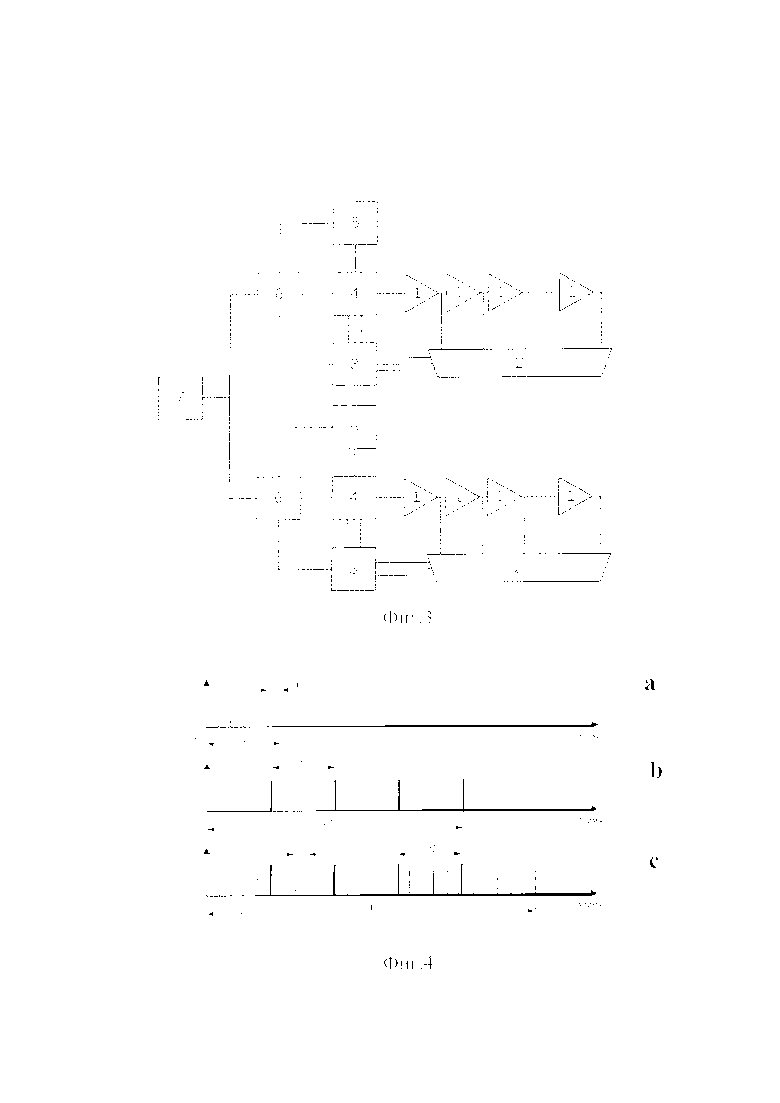

На фиг. 2 - то же, но с соединением тактового генератора с преобразователем входного сигнала.

На фиг. 3 - регулируемая схема задержки, содержащая два параллельно включенных каскада последовательно соединенных ступеней задержки.

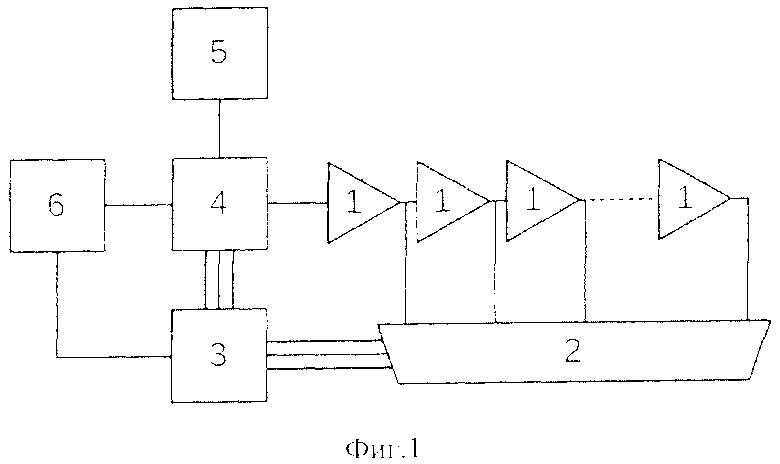

На фиг. 4 - временные диаграммы, иллюстрирующие работу заявляемой регулируемой схемы задержки.

Пояснения к фиг.: 1 - ступени задержки электрических сигналов; 2 - селектор; 3 - контроллер; 4 - двоичный счетчик; 5 - тактовый генератор; 6 - преобразователь входного сигнала; 7 - источник входного сигнала; Т1 - суммарное время задержки всех ступеней каскада; Т2 - время задержки дополнительного блока: t1 - минимальное время задержки одной из ступеней каскада; t2 - период подачи импульсов тактового генератора на двоичный счетчик.

Примером конкретного выполнения заявляемого изобретения могут служить схемы, представленные на фиг. 1, на фиг. 2 и на фиг. 3. Регулируемая схема задержки, представленная на фиг. 1, содержит один каскад соединенных последовательно, например, восьми ступеней задержки электрических сигналов, обеспечивающих различное время задержки, например, от 5 пс до 2,5 нс. Выход каждой ступени соединен с селектором. Регулируемая схема также содержит дополнительный блок задержки, включающий преобразователь входного сигнала, соединенный с источником входного сигнала, тактовый генератор, контроллер и двоичный счетчик, последний соединен с входом каскада, тактовым генератором, преобразователем и контроллером, который в свою очередь соединен с преобразователем и селектором.

Отличие регулируемой схемы задержки, представленной на фиг. 2 от схемы, представленной на фиг. 1, заключается в том, что тактовый генератор соединен с преобразователем.

Регулируемая схема задержки, представленная на фиг. 3, содержит два параллельно включенных каскада. Оба каскада состоят из соединенных последовательно ступеней задержки электрических сигналов с различным временем задержки, выход каждой из которых соединен с селектором этого каскада, а вход каждого каскада соединен со своим дополнительным блоком задержки, двоичный счетчик которого соединен со своим преобразователем входного сигнала, связанным с общим источником входного сигнала.

При этом для всех примеров конкретного выполнения период подачи импульсов тактового генератора на двоичный счетчик не превышает суммарное время задержки, обеспечиваемое всеми ступенями каскада, которое составляет 4 нс.

В процессе работы на двоичный счетчик 4 подается входной сигнал от источника входного сигнала 7 через преобразователь входного сигнала 6 и сигнал уставки от контроллера 3. При поступлении сигнала двоичный счетчик 4 начинает счет импульсов тактового генератора 5. Когда значение двоичного счетчика 4 становится равным значению сигналов уставки, приходящих с контроллера 3, на выходе двоичного счетчика 4 генерируется задержанный выходной сигнал. Дополнительный блок задержки позволяет варьировать задержку распространения сигнала с низким временным разрешением, равным периоду t2, обеспечиваемому тактовым генератором 5. Период подачи импульсов тактового генератора 5 на двоичный счетчик 4 не превышает суммарное время задержки Т1, обеспечиваемое всеми ступенями 1 каскада.

В известных схемах расширение диапазона работы достигается путем увеличения количества последовательно включенных ступеней задержки, что приводит к увеличению суммарной погрешности работы схемы на выходе. В заявляемой схеме для расширения диапазона работы предлагается использовать минимальное количество последовательно включенных ступеней задержки совместно с дополнительным блоком задержки.

На фиг. 4 (позиция а) показаны возможные значения выходного задержанного регулируемой схемой импульса при условии, что на первую ступень задержки из последовательно включенных ступеней каскада поступил входной сигнал в момент времени, равный 0.

При различных значениях сигналов уставки, поступающих на селектор 2, с помощью каскада соединенных последовательно ступеней задержки 1, возможно реализовать различные времена задержек, отстоящие друг от друга на временной оси на время t1 - минимальное время задержки одной из ступеней каскада, входящее в суммарное время Т1 - суммарное время задержки всех ступеней каскада.

На фиг. 4 (позиция b) в том же масштабе показаны возможные значения выходного задержанного электрического сигнала дополнительного блока задержки при условии, что входной сигнал на двоичный счетчик 4 поступил в момент равный 0 синхронно с сигналом тактового генератора 5. При различных значениях сигналов уставки, поступающих на двоичный счетчик 4, можно реализовать различные времена задержек, отстоящие друг от друга на временной оси на период t2 за время, соответствующее время задержки Т2.

На фиг. 4 (позиция с) в том же масштабе показаны возможные значения выходного задержанного электрического сигнала регулируемой схемы задержки при условии, что входной сигнал поступил в момент, равный 0, синхронно с сигналом тактового генератора 5. Дополнительный блок задержки и каскад из набора ступеней 1 включены последовательно, поэтому общая задержка Т выходного электрического сигнала регулируемой схемы складывается из T1 - суммарное время задержки всех ступеней каскада и Т2 - время задержки дополнительного блока. Т.о. общая задержка составляет Т=Т1+Т2 За все время Т возможно реализовать времена задержек с интервалом t1 - минимальное время задержки одной из ступеней каскада.

Таким образом, предлагаемая регулируемая схема задержки электрических сигналов позволяет регулировать задержку прихода сигналов в широком диапазоне величин с высоким временным разрешением и высокой точностью срабатывания.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1971 |

|

SU297071A1 |

| Устройство для измерения средней скорости изменения частоты и линейности модуляционных характеристик частотно-модулированных генераторов | 1987 |

|

SU1499259A1 |

| ИЗМЕРИТЕЛЬ УРОВНЯ | 1992 |

|

RU2029248C1 |

| Устройство для измерения средней скорости изменения частоты и линейности модуляционных характеристик частотно-модулированных генераторов | 1991 |

|

SU1807422A1 |

| ПРЕОБРАЗОВАТЕЛЬ ВРЕМЯ-КОД | 2005 |

|

RU2303803C2 |

| АНАЛИЗАТОР СПЕКТРА | 1992 |

|

RU2054682C1 |

| ЦИФРОВОЙ ТЕЛЕВИЗОР | 2003 |

|

RU2246796C1 |

| ПРИЕМНИК ИМПУЛЬСНЫХ РАДИОСИГНАЛОВ И ИЗМЕРИТЕЛЬ УРОВНЯ ДЛЯ НЕГО | 1996 |

|

RU2097922C1 |

| СПОСОБ СДВИГА ФАЗЫ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1993 |

|

RU2141165C1 |

| АДАПТИВНЫЙ ЛАЗЕРНЫЙ ДОПЛЕРОВСКИЙ ЛОКАТОР | 1990 |

|

RU2012013C1 |

Изобретение относится к импульсной технике. Технический результат - разработка регулируемой схемы задержки электрических сигналов, позволяющей осуществлять регулирование временной задержки в широком диапазоне значений с высоким временным разрешением и высокой точностью срабатывания. Для этого предложена регулируемая схема задержки, содержащая каскад соединенных последовательно ступеней задержки электрических сигналов с различным временем задержки, выход каждой из которых соединен с селектором, содержит дополнительный блок задержки, включающий преобразователь входного сигнала, соединенный с источником входного сигнала, тактовый генератор, контроллер и двоичный счетчик, последний соединен с входом каскада, тактовым генератором, преобразователем и контроллером, который, в свою очередь, соединен с преобразователем и селектором, при этом период подачи импульсов тактового генератора на двоичный счетчик не превышает суммарное время задержки, обеспечиваемое всеми ступенями каскада. 2 з.п. ф-лы, 4 ил.

1. Регулируемая схема задержки, содержащая каскад соединенных последовательно ступеней задержки электрических сигналов с различным временем задержки, выход каждой из которых соединен с селектором, отличающаяся тем, что содержит дополнительный блок задержки, включающий преобразователь входного сигнала, соединенный с источником входного сигнала, тактовый генератор, контроллер и двоичный счетчик, содержащий схему сравнения с сигналом уставки задержки от контроллера, за счет чего выходной сигнал дополнительного блока задержки генерируется при равенстве значения двоичного счетчика с сигналом уставки, и соединенный с входом каскада, тактовым генератором, преобразователем и контроллером, который, в свою очередь, соединен с преобразователем и селектором, при этом период подачи импульсов тактового генератора на двоичный счетчик не превышает суммарное время задержки, обеспечиваемое всеми ступенями каскада.

2. Схема по п. 1, отличающаяся тем, что тактовый генератор соединен с преобразователем.

3. Схема по п. 1 или 2, отличающаяся тем, что содержит параллельно включенный с каскадом по крайней мере еще один каскад соединенных последовательно ступеней задержки электрических сигналов с различным временем задержки, выход каждой из которых соединен с селектором этого каскада, а вход каскада соединен со своим дополнительным блоком задержки, двоичный счетчик которого соединен со своим преобразователем входного сигнала, связанным с общим источником входного сигнала.

| US 6459319 B2, 01.10.2002 | |||

| US 5668491 A1, 16.09.1997 | |||

| Регулируемая линия задержки | 1980 |

|

SU884080A1 |

| Способ обработки целлюлозных материалов, с целью тонкого измельчения или переведения в коллоидальный раствор | 1923 |

|

SU2005A1 |

Авторы

Даты

2019-08-01—Публикация

2018-05-21—Подача