(54) РЕГУЛИРУЕМАЯ ЛИНИЯ ЗАДЕРЖКИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения вероятностных характеристик фазы случайного сигнала | 1982 |

|

SU1112377A1 |

| ПЛКЙТНО-ИХШЕСЙА*ЬИБ;1ИО'^ЕКАГ. Л. Биланов | 1972 |

|

SU342297A1 |

| Устройство синхронизации фаз сигналов двух генераторов | 1978 |

|

SU771886A1 |

| Цифровая система измерения глубинного положения морской пьезосейсмографной косы | 1976 |

|

SU894640A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ СИНХРОНИЗАЦИЕЙ ТЕЛЕВИЗИОННОГО ИЗОБРАЖЕНИЯ | 2006 |

|

RU2324300C1 |

| Устройство для определения прочности бетона | 1981 |

|

SU1029071A2 |

| ИНФОРМАЦИОННАЯ СИСТЕМА СВЯЗИ | 1991 |

|

RU2019851C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ПЕРЕХОДНОЙ И ЧАСТОТНЫХ ХАРАКТЕРИСТИК ЭЛЕКТРИЧЕСКИХ ПРИБОРОВ | 1991 |

|

RU2028635C1 |

| Программное задающее устройство | 1986 |

|

SU1334107A1 |

I

Изобретение относится к электротехнике, конкретно к линиям задержки с непрерывным регулированием времени задержки, и может быть использовано в устройствах автоматики, вычислительной техники, преимущественно в тех случаях, когда предъявляются высокие требования по точности измерения времени задержки импульсного сигнала.

Известны линии задержки, вьшолненные на катушках индуктивности и содержащие цепь управления, п которых плавная регулировка времени задержки осуществляется измене шем индуктивности или емкостилинии с помощью управ- ляющего напряжения 1.

Недостатком таких устройств является зависимость параметров линии задержки от процесса регулирования.

Известно устройство, содержащее линию с постоянным временем зя,держки, например, выполненную на постоянных . катзшках индуктивности и конденсаторах, и цепь управления, выполненную

В виде усилителя с регулируемым коэффициентом усиления, соединенного параллельно с линией с постоянным временем задержки 2.

Недостатком известного устройства является зависимость параметров линии задержки от процесса регулирования, что снижает точность измерения и изменяет частотную характеристику линии задержки.

to

Цель изобретения - првьшение точности и расширение функциональных возможностей.

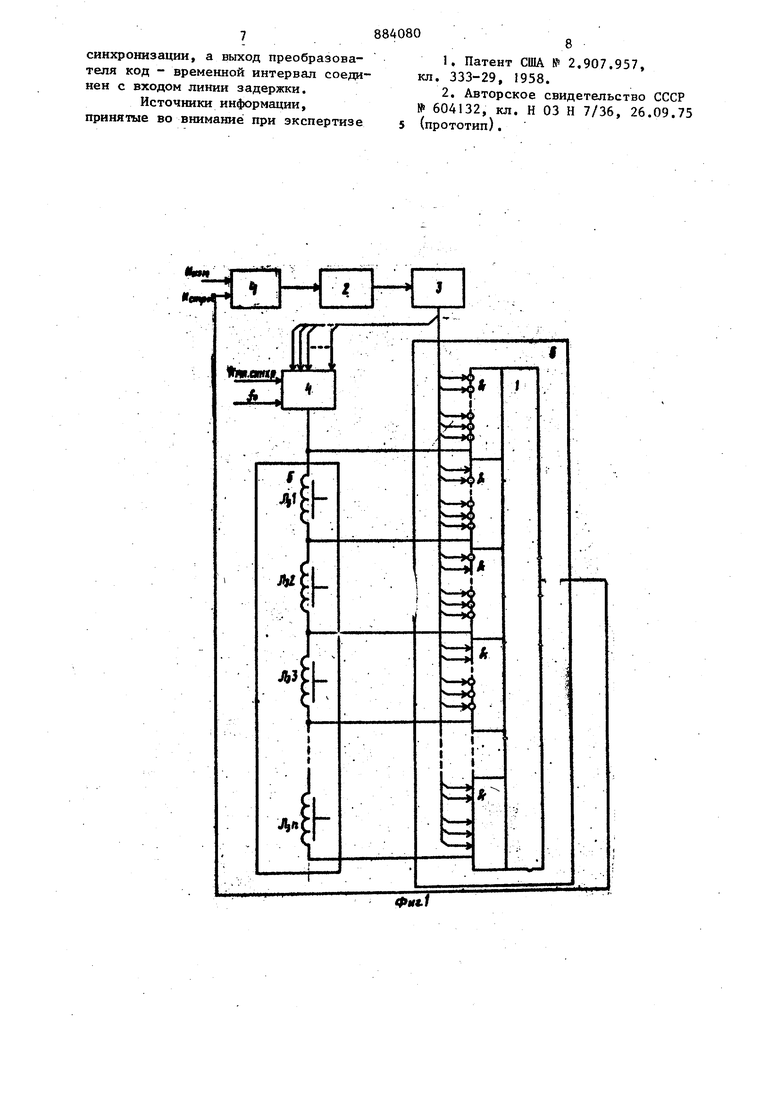

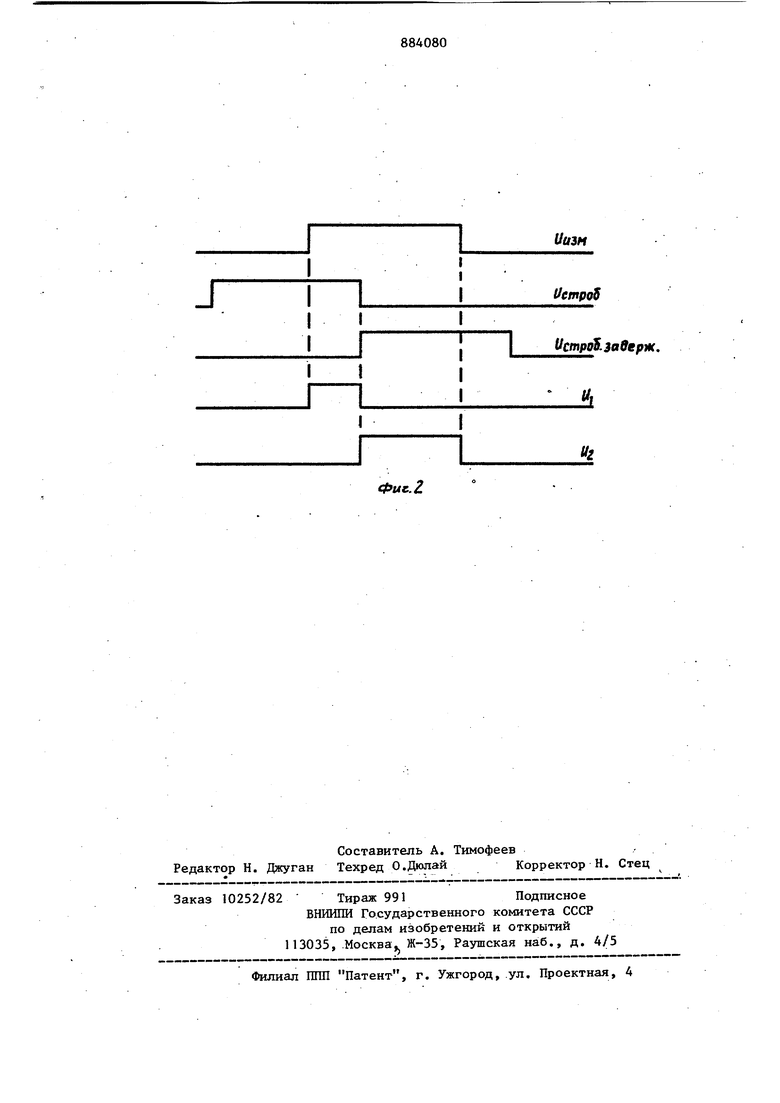

Для достижения указанной цели в регулируемой линии задержки, содержащей ли15нию с постоянным временем задержки и цепь упрйбления, линия задержки выполнена в виде набора п-числа последовательно соединенных секций, а цепь управления состоит из временного дискрими20натора, преобразователя напряжениечастота, реверсивного счетчика, преобразователя код - временной интервал и селектора-мультиплексора, при этом входы селектора-ьгультиплексора соединены с выходами разрядов реверсивного счетчика и соответствующими выходами линии задержки, а выход подключен к одному из входов временного дискриминатора, второй вход которого подклю4eiivK источнику импульсов, для измере ния времени задержки, причем выход временного, дискриминатора через преобразователь напряжение - частота соединен с входом реверсивного счетчика, выходы разрядов которого соединены дополнительно с входами преобразователя код-временной интервал, управляющие входы которого подключены к источнику опорной частоты и источнику импульсов синхронизации, а выход преобразователя код - временной интер вал соединен с входом линии задерж1си. Предлагаемое техническое решение служит для измерения текущего времени задержки импульсного сигнала с наперед заданной точностью. На фиг. 1 представлена функциональ ная схема устройства; на фиг. 2 - вре менные диаграммы, поясняющие принцип его работьь Регулируемая линия задержки содержит временной дискриминатор ), преобразователь 2 напряжение - частота, реверсивный счетчик 3, преобразователь 4 код - временной HHTepBajij, линию задержки 5 из п-числа секций, селектор-мультиплексор 6. Работа устройства происходит следующим образом. Импульс Ицам. задержку которого требуется измерить, поступает на вход временного дискриминатора 1, Туда же подается стробирующий импульс Herpod. который формируется в устройстве и следит за Ииьм.. Во временном дискриминаторе вырабатывается напряжение сигнала ощибки, величина и полярность которого определяются величи ной и знаком временного рассогласования между положениями центра И изм. и Истпроб, Далее это напряжение подается на преобразователь 2 напряжение - частота, который вырабатывает последовательность импульсов с частотой, пропорциональной величине входного напряжения. Этот же преобразователь Фо мирует сигнал Реверс Реверсв зависимости от полярности входного напряжения. Число импульсов, вьфабаты ваемое преобразователем напряжение частота, непрерывно подсчитывается 8 04 реверсивным счетчиком 3, который работает на сложение или вычитание в зависимости от знака сигнала Реверс. Текущие состояния выходных разрядов реверсивного счетчика 3 являются управляющими воздействиями для преобразователя 4 код - временный интервал. Преобразователь код - временной интервал представляет собой счетчик прямого счета, имеющий параллельную запись кода и счетный вход. Количество разрядов этого преобразователя выбирается таким, что бы время заполнеНИН счетчика равнялось бы максимальному значению величины задержки измеряемого импульса. Для преобразова1шя кода во временную задержку на него по сигналу синхронизации записываются текущие значения выхддных разрядов реверсивного счетчика 3 в параллельном обратном коде и по этому же сигналу синхронизации на счетный вход пропускаются импульсы опорной частоты f, , которые от значения записанного параллельного кода до единичного состояния всех разрядов. При достижении этого состояния на выходе старшего разряда появляется импульс переноса, отстающий от импульса синхронизации на время, равное разности максимальной задержки и числа импульсов (числа периодов) опорной частоты, дополнякицих счетчик преобразователя 4 код - временной интервал до единичного состояния всех разрядов, то есть преобразованного во временную задержку прямого кода реверсивного счетчика. Если нулевой код реверсивного счетчика записать в обратном коде в преобразователь 4, то все его разряды оказьшаются в единичном состоянии и первый же импульс опорной частоты появляются на выходе старшего разряда. Таким образом, при записи в преобразователь 4 нулевого кода получаем задержку, равную периоду опорной частоты; при увеличении же кода реверсивного счетчика, выработанная в ПКВИ, задержка увеличивается, так как вычитается уменьшающее (для обратного кода)- число. Полученный с преобразователя 4 импульс переполнения поступает на вход первой секции линии задержки. Дешифрованные текущие состояния разрядов реверсивного счетчика 3 выбирают дополнительную задержку импуль5са, сформированного в преобразовател 4, которая может .изменяться в предел длительности периода опорной частоты ffl. Дополнительная задержка вырабаты вается с помощью линии задержки 5, состоящей из п-числа последовательно соединенных секций. Полное время задержки всей линии выбирается равным периоду опорной ча тоты fo . Выбранные посредством дешифрирова ния значения выходов линий задержек затем логически складываются, и этот выбранньш сигнал поступает на один из входов временного дискримина тора 1, Указанная функция дешифрирова шя состояния разрядов реверсивного счет чика и логического сложения вьшолнена на устройстве, называемом селектор ом-муль типлек сер ом. Характеристика временного дискриминатора 1 близка в синусоиде ,с линейной частью ± 30° и крутизной сигнала на участке от 0° до максимума вдвое большей, чем на остальных участках. Это достигается взаимным расп ложением импульсов Ииьм И строб, и Истроб.зддер- гдеистроб.5адер. представляет собой импульс H(.jpo(j. задержанн на время его длительности, причем во временном дискриминаторе вырабатываю ся импульсы И, и И (фиг. 2 . Импульсы И,, H;i во временном дискриминаторе преобразуются в постоянные напряжения того или другого знака, величины которых пропорциональны длительности выделенных импульсов. Результирующее этих напряже ний подается на преобразователь напряжение-частота. При смещении импульса относительно центра измеряемого импульса, на выходе временного дискриминатора появляется такой сигнал ошибки, под де ствием которого И троб- перемещается по оси времени до тех пор, пока цент измеряемого, импульса И м. займет положения, симметричного относительн И строб, и Истроб.ъадеря. , и при этом на выходах схем логического умножения появляются импульсы И, и Hj равной дпительности, что сводит к нулю выхо ное напряжение временного дискриминатора. Полученная таким обрятом цифроаналоговая следящая система в дальнейшем вырабатывает также возмущающие воздействия, которые сводят вы0ходное напряжение временного дискриминатора до нуля, производя измерение текущего значения задержки Ицзм, представленного кодом выходных раз- рядов реверсивного счетчика. В качестве базового образца использована линия задержки, набранная из последовательно соединенных секций, каждая из которых имеет свой выход, подключаемый с помощью цепи управления. Причем количество секций линии задержки базового образца прямо пропорционально величине временной задерж - ки импульсного сигнала и заданной точности отсчета. В предлагаемом изобретении выбор величины временной задержки одной секции определяется заданной точностью измерения, аколичество секций - длительностью периода опорной частоты f,,, практически величина которой не превышает IMI.C 1° приводит к снижению габаритов и веса регулируемой лиНИИ задержки. Формула изобретения Регулируемая линия задержки, содержащая линию с постоянным временем задержки и цепь управления, о т л и- чающаяся тем, что, с целью повышения точности и расширения функциональных возможностей, линия задержки выполнена в виде набора п-числа последовательно соединенных секций, а цепь управления вьшолнена в виде временного дискриминатора, преобразователя напряжение-частота, реверсивного счетичика, преобразователя код временной интервал и селектора-мультиплексора, при этом входы селекторамультиплексора соединены с выходами разрядов реверсивного счетчика и соответствуюшлми выходами линий задержки, а выход подключен к одному из входов временного дискриминатора, к второму входу которого подключен источник импульсов, дпя измерения времени задержки, причем выход временного дискриминатора через преобразователь напряжение-частота соединен с входом реверсивного счетчика, выходы разрядов которого соединены дополнительно с входами преобразователя код - временной интервал, управляющие входы которого подключены к источнику опорной частоты и источнику импульсов синхронизации, а выход преобразователя код - временной интервал соединен с входом линии задержки. Источники информации, - -. -..ч i., принятые ВО внимание при экспертизе 84080 1.Патент США № 2,907.957, кл. 333-29, J958. 2.Авторское свидетельство СССР № 604132, кл. Н 03 Н 7/36, 26.09.75 Р 504132, К / - 5 (прототип).

Фиг.2

Авторы

Даты

1981-11-23—Публикация

1980-03-14—Подача