Изобретение относится к радиотехнике и может найти применение в средствах связи.

Известно устройство синхронизации, описанное в патенте РФ №141688 H04L 7/02 «Устройство установления тактовой синхронизации по информационному составному последовательному сигналу», недостатком которого является значительная сложность и недостаточно высокая точность синхронизации.

Известно устройство синхронизации, описанное в патенте РФ №2232479 H04L 27/22 «Система и способ устранения ошибки синхронизации символа и ошибки по частоте несущей в системе цифрового радиовещания ОЧУ», недостатком которого является недостаточно высокая точность синхронизации.

Известен способ синхронизации, описанный в патенте РФ №2538281 G08C 19/28 «Способ синхронизации передаваемых сообщений», у которого недостаточно высокая точность синхронизации и большое время синхронизации.

Известны способ и устройство синхронизации, описанные в патенте РФ №2591565 H04J3/06 «Способ синхронизации передаваемых сообщений и устройство для его реализации», недостатком которых является значительная сложность и невысокая точность синхронизации.

В учебном пособии «Основы теории радиотехнических систем. Учебное пособие. // В.И. Борисов, В.М. Зинчук, А.Е. Лимарев, Н.П. Мухин. Под ред. В.И. Борисова. Воронежский научно-исследовательский институт связи, 2004», стр. 206 - 207» рассматривается две типовые структурные схемы синхронных систем радиосвязи: с передачей опорного сигнала по отдельному каналу связи (рис.7.1а), и с формированием опорного сигнала на приемной стороне (рис.7.1б). Первый обладает очевидными недостатками – повышенными массогабаритными и стоимостными характеристиками приемного устройства, а также необходимостью организации отдельного канала для передачи опорного сигнала, что в современных условиях зачастую затруднено. В настоящее время наибольшее применение находят синхронные системы радиосвязи с формированием опорного сигнала вследствие их большей эффективности.

При этом под полной синхронизацией понимается, что действующий на входе приемника системы радиосвязи кодированный сигнал точно синхронизирован по началу кодовой последовательности и частоте следования ее двоичных символов.

Известно множество устройств, реализующих поисковый и беспоисковый методы синхронизации в системах с формированием опорного сигнала. Устройства, реализующие поисковый метод фазовой и тактовой синхронизации построены на основе системы фазовой автоподстройки частоты (ФАПЧ). Например, петля Костаса используется для восстановления фазированной несущей для двухполосной системы с подавлением несущей, а также для демодуляции фазоманипулированных сигналов (BPSK, QPSK) (Прокис Джон. Цифровая связь. Пер. с англ. / Под ред. Д.Д. Кловского - М.: Радио и связь. 2000. стр. 302-303). Устройства, основанные на петле Костаса, имеют недостатки, связанные с неоднозначностью фазы на 180º, а также с инерционностью петлевого фильтра.

Наиболее близким аналогом по технической сущности к предлагаемому является устройство синхронизации символов, описанное в учебном пособии «Основы теории радиотехнических систем. Учебное пособие. // В. И. Борисов, В. М. Зинчук, А. Е. Лимарев, Н. П. Мухин. Под ред. В. И. Борисова. Воронежский научно-исследовательский институт связи, 2004», стр. 222 - 223», принятое за прототип.

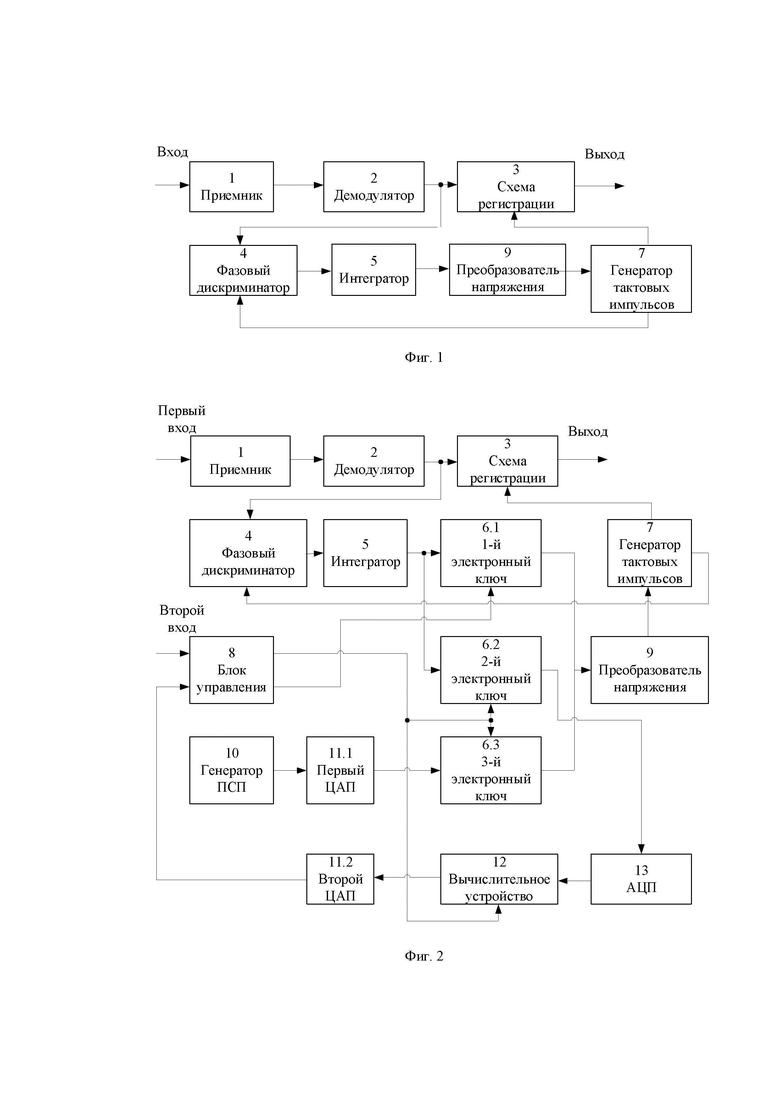

Структурная схема устройства-прототипа приведена на фиг. 1, где обозначено:

1 – приемник;

2 – демодулятор;

3 – схема регистрации;

4 – фазовый дискриминатор (ФД);

5 – интегратор;

7 – генератор тактовых импульсов (ГТИ);

9 – преобразователь напряжения (блок управления).

Устройство содержит последовательно соединенные приемник 1, демодулятор 2, схему регистрации 3, выход которой является

выходом устройства, а также последовательно соединенные фазовый дискриминатор 4, интегратор 5, преобразователь напряжения 9 и генератор тактовых импульсов 7, первый выход которого соединен с вторым входом схемы регистрации 3. Второй выход генератора тактовых импульсов 7 соединен со вторым входом фазового дискриминатора 4, первый вход которого подсоединен к выходу демодулятора 2. Вход приемника 1 является входом устройства.

Устройство-прототип работает следующим образом.

Сигнал с выхода приемника 1 подается в демодулятор 2. После демодуляции сигнал поступает в фазовый дискриминатор 4, на второй вход которого подаются сигналы с ГТИ 7, управляемого напряжением. Фазовый дискриминатор 4 вырабатывает напряжение (напряжение ошибки) знак и амплитуда которого пропорциональна знаку и величине рассогласования фаз (времени) между тактовыми импульсами ГТИ 7 и принимаемыми символами. Символ, в данном случае, представляет собой сигнал установленной заранее длительности с полностью известными параметрами, кроме его времени появления (фазы).

Напряжение, поступающее с выхода фазового дискриминатора 4, усредняют в интеграторе 5 и формируют с его использованием управляющее напряжение в преобразователе напряжения 9 таким образом, чтобы рассогласование фаз уменьшилось до минимума. На выход схемы регистрации 3 поступают символы после того, как процесс синхронизации завершают. Схема регистрации 3 может быть выполнена, например, в виде электронного ключа, который открывают напряжением, поступающим с ГТИ 7. В данном случае преобразователь напряжения (блок управления) 9, преобразует напряжение, которое изменяется в пределах от U1 до U2, в напряжение, которое изменяется соответственно в пределах от U3 до U4 по определенной функциональной зависимости.

Недостатком данного устройства является невысокая точность синхронизации, что обусловлено тем, что устройство-прототип реализовано по принципу аналогового замкнутого контура. При этом для повышения точности необходимо значительно увеличивать время усреднения напряжения ошибки.

Задача предлагаемого устройства – повышение точности синхронизации.

Для решения поставленной задачи в устройство стохастической синхронизации символов, содержащее последовательно соединенные приемник, демодулятор и схему регистрации, выход которой является выходом устройства, последовательно соединенные фазовый дискриминатор и интегратор, последовательно соединенные преобразователь напряжения и генератор тактовых импульсов (ГТИ), первый выход которого соединен со вторым входом схемы регистрации, а второй выход ГТИ подключен ко второму входу фазового дискриминатора, первый вход которого подсоединен к выходу демодулятора, при этом вход приемника является первым входом устройства, согласно изобретению, введены первый, второй и третий электронные ключи, причем выходы первого и третьего ключей соединены с входом преобразователя напряжения; выход интегратора соединен с входами первого и второго электронных ключей, при этом выход второго электронного ключа через последовательно соединенные аналого-цифровой преобразователь (АЦП), вычислительное устройство и второй цифро-аналоговый преобразователь (ЦАП) соединен с соответствующим входом блока управления, первый выход которого соединен со вторыми входами второго и третьего электронных ключей и вторым входом вычислительного устройства; второй выход блока управления соединен со вторым входом первого электронного ключа, кроме того, последовательно соединенные генератор псевдослучайной последовательности и первый ЦАП, выход которого соединен с входом третьего электронного ключа; соответствующий вход блока управления является вторым входом устройства.

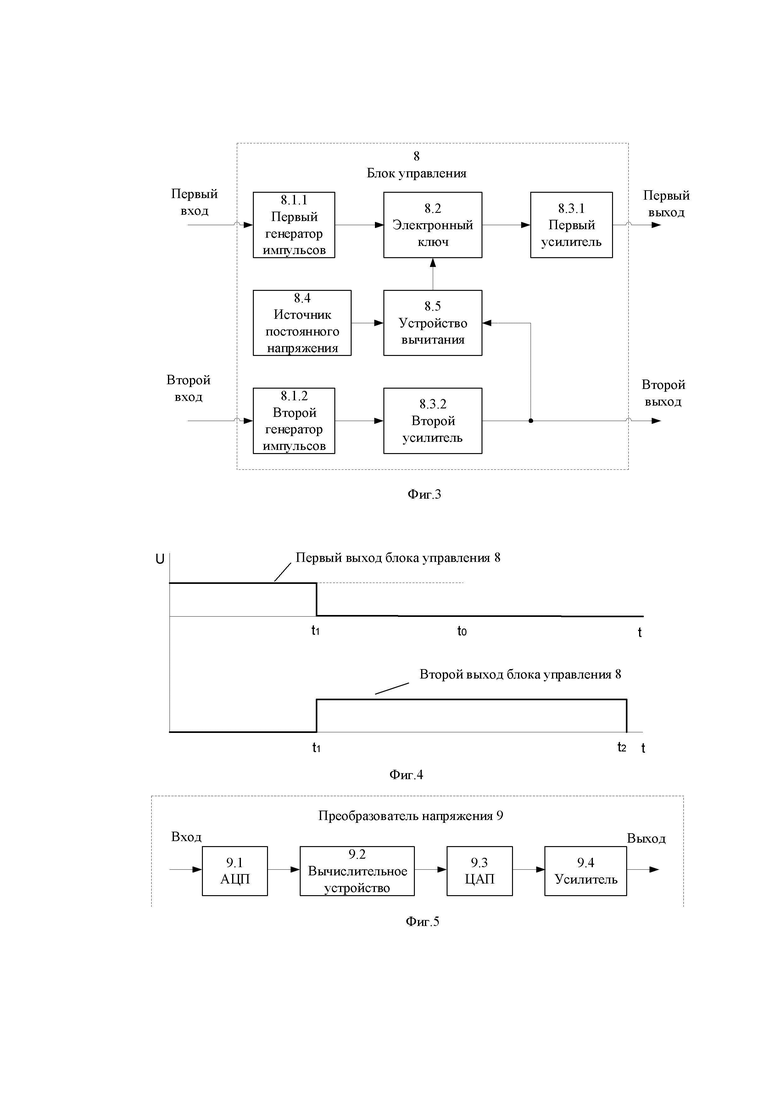

Структурная схема заявляемого устройства приведена на фиг. 2, где обозначено:

1 – приемник;

2 – демодулятор;

3 – схема регистрации;

4 – фазовый дискриминатор (ФД);

5 – интегратор;

6.1, 6.2, 6.3 – с первого по третий электронные ключи;

7 – генератор тактовых импульсов (ГТИ);

8 – блок управления (БУ);

9 – преобразователь напряжения;

10 – генератор псевдослучайной последовательности (ПСП) чисел;

11.1, 11.2 – первый и второй цифро-аналоговые преобразователи (ЦАП);

12 – вычислительное устройство (ВУ);

13 – аналого-цифровой преобразователь (АЦП).

Предлагаемое устройство содержит последовательно соединенные приемник 1, демодулятор 2, схему регистрации 3, выход которой является выходом устройства, а также последовательно соединенные фазовый дискриминатор 4, интегратор 5, первый электронный ключ 6.1, преобразователь напряжения 9 и ГТИ 7, первый выход которого соединен со вторым входом схемы регистрации 3, второй выход ГТИ 7 соединен со вторым входом фазового дискриминатора 4, первый вход которого подсоединен к выходу демодулятора 2. Кроме того, последовательно соединенные второй электронный ключ 6.2, АЦП 13, вычислительное устройство 12, второй ЦАП 11.2 и блок управления 8, второй выход которого соединен со вторым входом первого электронного ключа 6.1. Последовательно соединенные генератор ПСП 10, первый ЦАП 11.1, третий электронный ключ 6.3, выход которого соединен с входом преобразователя напряжения 9. Первый выход блока управления 8 соединен со вторым входом вычислительного устройства 12 и объединенными вторыми входами второго 6.2 и третьего 6.3 электронных ключей. Выход интегратора 5 соединен с первым входом второго электронного ключа 6.2. Вход приемника 1 является первым входом устройства, а его вторым входом – соответствующий вход блока управления 8.

Предлагаемое устройство работает следующим образом.

Синхронизация осуществляется в два этапа:

– первый этап – вход в синхронизм;

– второй этап – слежение за фазой принимаемых символов.

На первом этапе сигнал с приемника 1 подается в демодулятор 2. После демодуляции сигнал подают на первый вход фазового дискриминатора 4. На вход блока управления 8, соответствующий второму входу устройства, поступает сигнал управления от устройства управления средства связи (на фиг. 2 не показан). Под воздействием этого сигнала в блоке управления 8 формируется импульс установленной заранее длительности (t0) (см. фиг. 4), который подают на его первый выход, с которого напряжение поступает на вторые входы второго 6.2 и третьего 6.3 электронных ключей и открывает их. Это напряжение подают и на второй вход вычислительного устройства 12, под воздействием которого вычислительное устройство 12 устанавливают в исходное состояние.

Длительность импульса (t0), подаваемого на соответствующий выход блока управления 8, выбирают из условия обеспечения обработки N чисел, которые формируют в генераторе ПСП 10 за это время. Данное значение чисел (N) определяют на этапе разработки экспериментальным путем или методом математического моделирования как значение, обеспечивающее заданный уровень точности синхронизации при условии, что вероятность того, что за время t0 хотя бы одно значение напряжения ошибки окажется меньше заданного значения, превышает заданный уровень.

В генераторе ПСП 10 формируют псевдослучайную последовательность чисел, которую преобразуют в соответствующие напряжения

различного уровня в первом ЦАП 11.1, и затем подают это напряжение через открытый третий электронный ключ 6.3 на вход преобразователя напряжения 9. Напряжение с выхода преобразователя напряжения 9 подают на вход ГТИ 7. С выхода ГТИ 7 напряжение подают на второй вход фазового дискриминатора 4. Фазовый дискриминатор 4 вырабатывает напряжение (напряжение ошибки), знак и амплитуда которого пропорциональна знаку и величине рассогласования фаз (времени) между тактовыми импульсами

ГТИ 7 и принимаемыми символами. Это напряжение усредняют в интеграторе 5 и через открытый второй электронный ключ 6.2 подают его в АЦП 13.

Преобразованное в цифровую форму напряжение ошибки в АЦП 13 подают в вычислительное устройство 12, где сравнивают его с определенным заранее пороговым значением.

Данное пороговое значение определяют на этапе разработки изделия, как значение, определяющее заданный уровень ошибки синхронизации.

В случае если напряжение ошибки превышает пороговое значение, то описанную процедуру повторяют для очередного случайного числа, которое вырабатывает генератор ПСП 10.

В противном случае в ВУ 12 формируют сигнал, который подают на второй ЦАП 11.2, где преобразуют его в аналоговый вид. Напряжение с

выхода второго ЦАП 11.2 подают на соответствующий вход блока управления 8. Под воздействием данного напряжения на его первом выходе в момент времени t1 формируют напряжение нулевого уровня, которое поступает на вторые входы второго 6.2 и третьего 6.3 электронных ключей и закрывает их (см. фиг. 4).

На втором выходе блока управления 8 в момент времени t1 формируют напряжение, которое подают на второй вход первого электронного ключа 6.1 и которое открывает его.

В этом случае устройство начинает работать по алгоритму устройства-прототипа в режиме слежения за фазой принимаемых символов.

А именно – напряжение со второго выхода блока управления 8 подают на второй вход первого электронного ключа 6.1 и открывают его. Напряжение ошибки усредняют в интеграторе 5 и через открытый первый электронный ключ 6.1 подают на вход преобразователя напряжения 9. Напряжение с выхода преобразователя напряжения 9 подают на ГТИ 7, в котором соответствующим образом изменяется фаза тактовых импульсов. Тактовые импульсы, синфазные с сигналом, с выхода ГТИ 7 подают на второй вход схемы регистрации 3, и на ее выход поступают принимаемые символы.

В случае если за первый цикл вхождения в синхронизм напряжение ошибки ни разу не стало меньше порогового значения, то описанную процедуру повторяют.

Процесс повторяют до тех пор, пока на очередном шаге напряжение ошибки не станет меньше порогового значения, или не истечет время, отведенное на синхронизацию.

Генератор ПСП 10 является датчиком равномерно распределенных случайных величин (чисел) в интервале от 0 до 1.

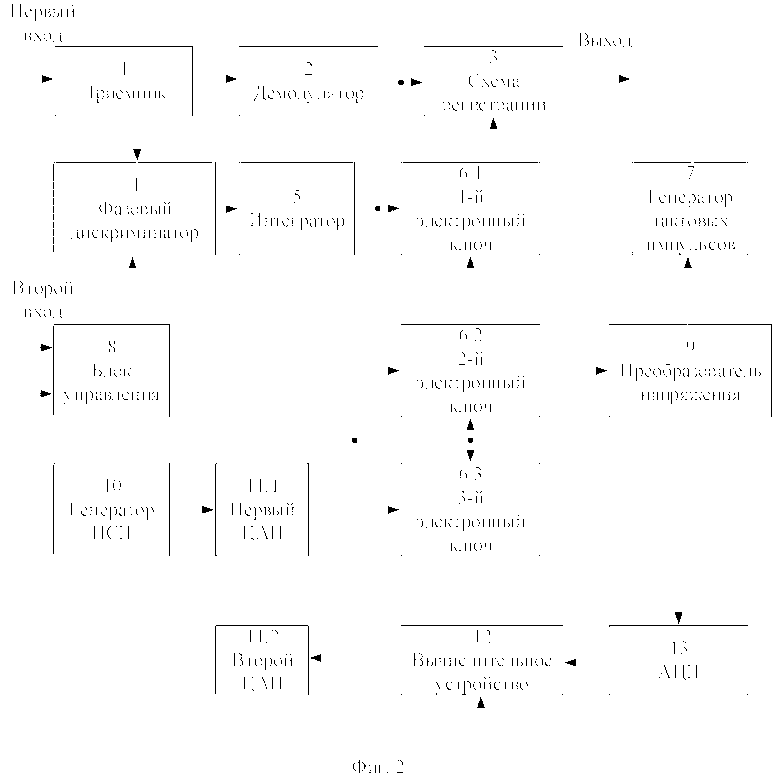

Блок управления 8 может быть выполнен, например, в виде устройства, структурная схема которого приведена на фиг. 3, где обозначено:

8.1.1, 8.1.2 – первый и второй генераторы импульсов;

8.2 – электронный ключ;

8.3.1, 8.3.2 – первый и второй усилители;

8.4 – источник постоянного напряжения;

8.5 – устройство вычитания.

Блок управления 8 содержит последовательно соединенные первый генератор импульсов 8.1.1, электронный ключ 8.2 и первый усилитель 8.3.1, выход которого является первым выходом блока управления 8; последовательно соединенные источник постоянного напряжения 8.4 и устройство вычитания 8.5, выход которого соединен со вторым входом электронного ключа 8.2; последовательно соединенные второй генератор импульсов 8.1.2 и второй усилитель 8.3.2, выход которого соединен со вторым входом устройства вычитания 8.5 и является вторым выходом блока управления 8. При этом входы первого 8.1.1 и второго 8.1.2 генераторов импульсов являются соответственно первым и вторым входами блока управления 8.

Эпюры напряжений, поступающих с выходов блока управления 8, приведены на фиг. 4.

Под воздействием сигнала управления, поступающего от устройства управления средства связи через первый вход блока управления 8 на первый генератор импульсов 8.1.1, на его выходе формируется положительное напряжение, которое поступает на первый вход электронного ключа 8.2. В это время на второй вход блока управления 8 подают напряжение нулевого уровня со второго ЦАП 11.2, пока на вход второго ЦАП 11.2 не поступит напряжение в цифровом виде с ВУ 12. Соответственно на выходе второго генератора импульсов 8.1.2 сохраняется напряжение нулевого уровня, и поэтому на выходе устройства вычитания 8.5 значение напряжения равно значению напряжения, поступающего на первый вход устройства вычитания 8.5 от источника постоянного напряжения 8.4. Данное напряжение подают на второй вход электронного ключа 8.2 и поддерживают его в открытом состоянии. Напряжение, поступающее с выхода электронного ключа 8.2, усиливают в первом усилителе 8.3.1 и подают его на первый выход блока управления 8.

После того, как на вход второго генератора импульсов 8.1.2 поступит напряжение со второго ЦАП 11.2, на выходе второго генератора импульсов 8.1.2 формируется импульс длительностью (t2- t1). Данное напряжение после усиления во втором усилителе 8.3.2 подают на второй выход блока управления 8, а также на второй вход устройства вычитания 8.5. Коэффициент усиления второго усилителя 8.3.2 выбирают так, что напряжение на его выходе равно или немного больше напряжения источника постоянного напряжения 8.4. При этом на выходе устройства вычитания 8.5 появляется напряжение нулевого уровня или небольшое отрицательное напряжение, которое подают на второй вход электронного ключа 8.2 и закрывают его. При этом на первом выходе блока управления 8 появляется напряжение нулевого уровня.

Длительность импульса (t2- t1), который формируют на выходе второго генератора импульсов 8.1.2, выбирают из условия обеспечения работы устройства в режиме слежения за фазой принимаемых символов в течение заданного времени.

Преобразователь напряжения 9 выполнен в виде устройства преобразования напряжения, которое изменяется в пределах от U1 до U2, в напряжение, которое изменяется соответственно в пределах от U3 до U4 по некоторой функциональной зависимости. Преобразователь напряжения 9 может быть выполнен, например, в виде устройства, структурная схема которого приведена на фиг. 5, где обозначено:

9.1 – аналого-цифровой преобразователь (АЦП);

9.2 – вычислительное устройство;

9.3 – цифро-аналоговый преобразователь (ЦАП);

9.4 – усилитель.

Преобразователь напряжения 9 содержит последовательно соединенные АЦП 9.1, вычислительное устройство 9.2, ЦАП 9.3 и усилитель 9.4, выход которого является выходом преобразователя напряжения 9. Вход АЦП 9.1 является входом преобразователя напряжения 9.

Поступающее на вход преобразователя напряжения 9 напряжение ошибки преобразуют в цифровую форму в АЦП 9.1 и подают его в вычислительное устройство 9.2, где входное напряжение пересчитывается следующим способом

y(n)= kn x(n), (1)

т.е.: y(1)=k1 x(1), y(2)=k2 x(2), … , y(n)=kn x(n),

где n – номер шага процесса.

Полученное напряжение преобразуют в ЦАП 9.3 в аналоговую форму и усиливают до необходимого уровня в усилителе 9.4.

Вычислительное устройство 9.2 может быть выполнено, например, в виде программируемой логической интегральной схемы (ПЛИС).

Ниже приведены результаты моделирования процесса стохастической синхронизации символов, когда в качестве входного сигнала используют гармонический сигнал Sin x.

Результаты оценки эффективности предлагаемого устройства получены методом математического моделирования на ЭВМ с использованием системы MATLAB.

В таблице представлены результаты моделирования процесса стохастической синхронизации символов.

При моделировании были использованы следующие исходные данные:

– амплитуда сигнала – 1;

– число реализаций – 106.

В таблице использованы следующие обозначения:

N – количество используемых чисел псевдослучайной последовательности.

На основе анализа данных, приведенных в таблице, может быть сделан вывод о том, что при использовании предлагаемого устройства, при числе шагов алгоритма 40, может быть обеспечено (число используемых чисел ПСП равно 40):

– значение средней ошибки синхронизации, % – 0,24;

– значение максимальной ошибки синхронизации, % – 14.

По результатам моделирования получено, что при числе шагов алгоритма равном 40 вероятность того, что напряжение ошибки ни разу не превысит порог (вероятность того, что синхронизации за один цикл поиска не будет осуществлена) составляет около 10-5.

Первый 11.1, второй 11.2 ЦАП и ЦАП 9.3 могут быть выполнены, например, на микросхеме AD9957BSVZ Analog Devices.

Вычислительные устройства 12 и 9.2 могут быть выполнены, например, на микросхеме TMS320VC5416 фирмы Texas Instruments (США).

АЦП 13 и 9.1 могут быть выполнены, например, на микросхеме AD7495BR фирмы Analog Devices.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство адаптивной синхронизации символов | 2020 |

|

RU2735494C1 |

| Способ адаптивной синхронизации символов | 2020 |

|

RU2738253C1 |

| Радиостанция, обеспечивающая противодействие системам извлечения информации | 2021 |

|

RU2758499C1 |

| Способ противодействия системам извлечения информации, осуществляющим распознавание индивидуальной структуры сигналов, путем искажения формы сигнала | 2021 |

|

RU2774743C1 |

| Способ противодействия системам извлечения информации, передаваемой средствами радиосвязи | 2021 |

|

RU2760978C1 |

| Способ снижения эффективности систем извлечения информации, использующих индивидуальную структуру излучаемых сигналов | 2021 |

|

RU2768255C1 |

| Способ передачи информации с использованием модуляции частотным сдвигом при наличии помех с неравномерной спектральной плотностью | 2022 |

|

RU2799089C1 |

| Способ энергетического обнаружения сигнала с компенсацией комбинационных составляющих в условиях воздействия нестационарных помех | 2023 |

|

RU2811900C1 |

| ЦИФРОВОЙ МОДЕМ КОМАНДНОЙ РАДИОЛИНИИ ЦМ КРЛ | 2013 |

|

RU2548173C2 |

| РУБИДИЕВЫЙ СТАНДАРТ ЧАСТОТЫ | 2001 |

|

RU2213364C2 |

Изобретение относится к области вычислительной техники. Технический результат заключается в повышении точности синхронизации символов. Устройство содержит: последовательно соединенные приемник, демодулятор и схему регистрации, выход которой является выходом устройства, последовательно соединенные фазовый дискриминатор и интегратор, последовательно соединенные преобразователь напряжения и генератор тактовых импульсов (ГТИ), причем, введены первый, второй и третий электронные ключи, выходы первого и третьего ключей соединены с входом преобразователя напряжения. 2 з.п. ф-лы, 5 ил.

1. Устройство стохастической синхронизации символов, содержащее последовательно соединенные приемник, демодулятор и схему регистрации, выход которой является выходом устройства, последовательно соединенные фазовый дискриминатор и интегратор, последовательно соединенные преобразователь напряжения и генератор тактовых импульсов (ГТИ), первый выход которого соединен со вторым входом схемы регистрации, а второй выход ГТИ подключен ко второму входу фазового дискриминатора, первый вход которого подсоединен к выходу демодулятора, при этом вход приемника является первым входом устройства, отличающееся тем, что введены первый, второй и третий электронные ключи, причем выходы первого и третьего ключей соединены с входом преобразователя напряжения; выход интегратора соединен с входами первого и второго электронных ключей, при этом выход второго электронного ключа через последовательно соединенные аналого-цифровой преобразователь (АЦП), вычислительное устройство и второй цифро-аналоговый преобразователь (ЦАП) соединен с соответствующим входом блока управления, первый выход которого соединен со вторыми входами второго и третьего электронных ключей и вторым входом вычислительного устройства; второй выход блока управления соединен со вторым входом первого электронного ключа, кроме того, последовательно соединенные генератор псевдослучайной последовательности и первый ЦАП, выход которого соединен с входом третьего электронного ключа; соответствующий вход блока управления является вторым входом устройства.

2. Устройство по п. 1, отличающееся тем, что блок управления содержит последовательно соединенные первый генератор импульсов, электронный ключ и первый усилитель, выход которого является первым выходом блока управления; последовательно соединенные источник постоянного напряжения и устройство вычитания, выход которого соединен со вторым входом электронного ключа; последовательно соединенные второй генератор импульсов и второй усилитель, выход которого соединен со вторым входом устройства вычитания и является вторым выходом блока управления, при этом входы первого и второго генераторов импульсов являются соответственно первым и вторым входами блока управления.

3. Устройство по п. 1, отличающееся тем, что преобразователь напряжения содержит последовательно соединенные аналого-цифровой преобразователь (АЦП), вычислительное устройство, цифро-аналоговый преобразователь и усилитель, выход которого является выходом преобразователя, при этом вход АЦП является входом преобразователя напряжения.

| Термостатический парожидкостный бескапиллярный регулятор | 1961 |

|

SU141688A1 |

| RU 2012122943 A, 10.12.2013 | |||

| СПОСОБ СИНХРОНИЗАЦИИ ПЕРЕДАВАЕМЫХ СООБЩЕНИЙ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2015 |

|

RU2591565C1 |

| US 6539063 B1, 25.03.2003. | |||

Авторы

Даты

2019-08-02—Публикация

2018-11-13—Подача