Изобретение относится к системам связи и может быть использовано врадиоприемных устройствах, а именно - в детекторах сигналов с двухпозиционной фазовой манипуляцией (ФМС).

Известен демодулятор по схеме Костаса ([1] Проакис Дж. «Цифровая связь» / Под ред. Д.Д. Кловского. - М.: Радио и Связь, 2000, стр. 303), обеспечивающий квазикогерентную обработку ФМС с априорно неизвестными частотой и начальной фазой. Данный демодулятор состоит из двух перемножителей, двух фильтров нижних частот, управляемого по частоте гетеродина, фазовращателя на 90°, которые обеспечивают формирование квадратурных составляющих ФМС с последующим их перемножением в третьем перемножителе и выделении сигнала рассогласования в петлевом фильтре, с выхода которого он подается на управляемый гетеродин.

К недостаткам такого демодулятора следует отнести его сложность цифровой реализации, а также склонность к так называемой «обратной работе». Данное явление заключается в том, что в присутствии произвольного изменения фазы, введенного каналом связи, демодулятор не способен определить, какая точка сигнального созвездия соответствует 1, а какая - 0. Поэтому наиболее широкое применение данная схема нашла в системах с предварительной битовой синхронизацией, обеспечиваемой путем использования дифференциальной фазовой манипуляции, помехоустойчивого кодирования, дополнения данных корреляционным словом или преамбулой.

Известен демодулятор по схеме Костаса, совмещенный с устройством вычисления фазы и ошибки ([2] Вестник Нижегородского университета им. Н.И. Лобачевского, 2010, №5 (2), с. 389-392). Данное устройство состоит из цифрового квадратурного демодулятора по схеме Костаса, блока вычисления фазы, блока нормализации и демпфера. Для функционирования цифрового демодулятора на его вход подается предварительно оцифрованный радиочастотный сигнал, квадратурный сигнал с выхода демодулятора подается на блок вычисления фазы, выход блока вычисления фазы подключен к устройству прямого цифрового синтеза, заменяющему управляемый гетеродин, через последовательно подключенные блок нормализации и демпфер.

Недостатком такого решения является низкая устойчивость системы управления синтезатором к фазовым шумам и как следствие слабая помехоустойчивость

Известен демодулятор системы связи с двукратной фазовой модуляцией ([3]патент РФ №2427969, МПК H04L 27/22, от 15.12. 2009), содержащий первый и второй перемножители, квадратурный фазовращатель, генератор, управляемый по частоте, первый и второй фильтры низкой частоты, сумматор и фильтр петли, третий и четвертый перемножители, первый и второй ограничители, вычитающее устройство, аналого-цифровой преобразователь (АЦП), N-канальный вычислитель-анализатор обобщенного спектра сигнала биений, вычислитель номера канала, в котором находится максимальная спектральная составляющая, и преобразователь номера канала в напряжение (ЦАП), при этом выход первого перемножителя соединен с входом первого фильтра низкой частоты, выход которого соединен с первым входом третьего перемножителя и входом второго ограничителя, выход второго ограничителя соединен со вторым входом четвертого перемножителя, выход второго перемножителя соединен с входом второго фильтра низкой частоты, выход которого соединен с первым входом четвертого перемножителя и с входом первого ограничителя, выход первого ограничителя соединен со вторым входом третьего перемножителя, выход которого соединен с первым входом вычитающего устройства, второй вход которого соединен с выходом четвертого перемножителя, выход вычитающего устройства соединен со вторым входом сумматора, выход сумматора соединен с входом фильтра петли, выход которого соединен с входом генератора, управляемого по частоте, выход которого соединен с входом квадратурного фазовращателя, выходы которого соединены соответственно со вторыми входами первого и второго перемножителей, первые входы которых соединены между собой и являются входом демодулятора, первый вход сумматора соединен с выходом преобразователя номера канала в напряжение (ЦАП), входы которого соединены с выходами вычислителя номера канала, в котором находится максимальная спектральная составляющая, входы которого соединены с выходами N-канального вычислителя-анализатора обобщенного спектра сигнала биений, входы которого соединены с выходами аналого-цифрового преобразователя (АЦП), вход которого соединен с выходом вычитающего устройства, выходы третьего и четвертого перемножителей являются информационными выходами демодулятора.

Недостатком известного устройства является сложность технической реализации, обусловленная большим количеством оборудования.

Наиболее близким по технической сущности к предлагаемому техническому решению является известный адаптивный демодулятор ([4]патент РФ №139043, МПК H04L 27/22 от 15.08.2013), содержащий демодулятор по схеме Костаса, который включает в себя первый, второй и третий перемножители, первый и второй фильтры нижних частот, управляемый гетеродин, петлевой фильтр, фазовращатель, и имеющий два параллельно соединенных входа, причем первый вход демодулятора по схеме Костаса является первым входом первого перемножителя, а второй вход демодулятора по схеме Костаса является первым входом второго перемножителя, второй вход первого перемножителя подключен к выходу управляемого гетеродина, второй вход второго перемножителя подключен к выходу управляемого гетеродина через фазовращатель, выход первого перемножителя соединен через первый фильтр нижних частот с первым входом третьего перемножителя, выход второго перемножителя соединен через второй фильтр нижних частот со вторым входом третьего перемножителя, выход которого соединен с первым входом петлевого фильтра, линию задержки, параллельный спектроанализатор, решающее устройство и сумматор, вход линии задержки и вход параллельного спектроанализатора являются входом адаптивного демодулятора, выход линии задержки подключен к первым входам первого и второго перемножителей, а выход параллельного спектроанализатора подключен ко входу решающего устройства, первый выход которого подключен к управляющим входам первого и второго фильтров нижних частот, второй выход к первому входу сумматора, третий выход - к управляющему входу петлевого фильтра, выход которого подключен ко второму входу сумматора, выход которого подключен к управляющему входу управляемого гетеродина.

Недостатком этого устройства является низкая помехоустойчивость и недостаточная надежность в работе, обусловленные зависимостью от фазовой неопределенностипри приеме информационных сигналов и высокая вероятность срыва в работе в условиях помех.

Техническим результатом, достигаемым в предлагаемом демодуляторе, является снижение вероятности «обратной работы», обеспечениестабильностивне зависимости от начальной фазовой неопределенности, обеспечение детектирования принимаемого сигнала без какой-либо информации о характере передаваемых данных, повышение помехоустойчивости иуменьшение вероятности срыва слежения за фазой при наличии значительных помех при приеме информационного сигнала.

Указанный технический результат достигается в демодуляторе двухпозиционных фазоманипулированных сигналов, содержащем первый и второй перемножители, первый, второй и третий фильтры нижних частот и анализатор фазы, тем, что он содержит аналого-цифровой преобразователь, вход которого является входом демодулятора, полосовой фильтр, пропорционально-интегрально-дифференциальный регулятор, модуль прямого цифрового синтеза и компаратор, выход которого является выходом демодулятора, при этом выход аналого-цифрового преобразователя подключен ко входу полосового фильтра, выход которого соединен с первыми входами первого и второго перемножителей, вторые входы которых подключены к соответствующим выходам модуля прямого цифрового синтеза, управляющий вход которого соединен с выходом пропорционально-интегрально-дифференциального регулятора, причем выход первого фильтра нижних частот подключен к первому входу анализатора фазы и входу компаратора, а выход второго фильтра нижних частот соединен со вторым входом анализатора фазы, выход которого подключен ко входу третьего фильтра нижних частот, выход которого соединен со входом пропорционально-интегрально-дифференциального регулятора.

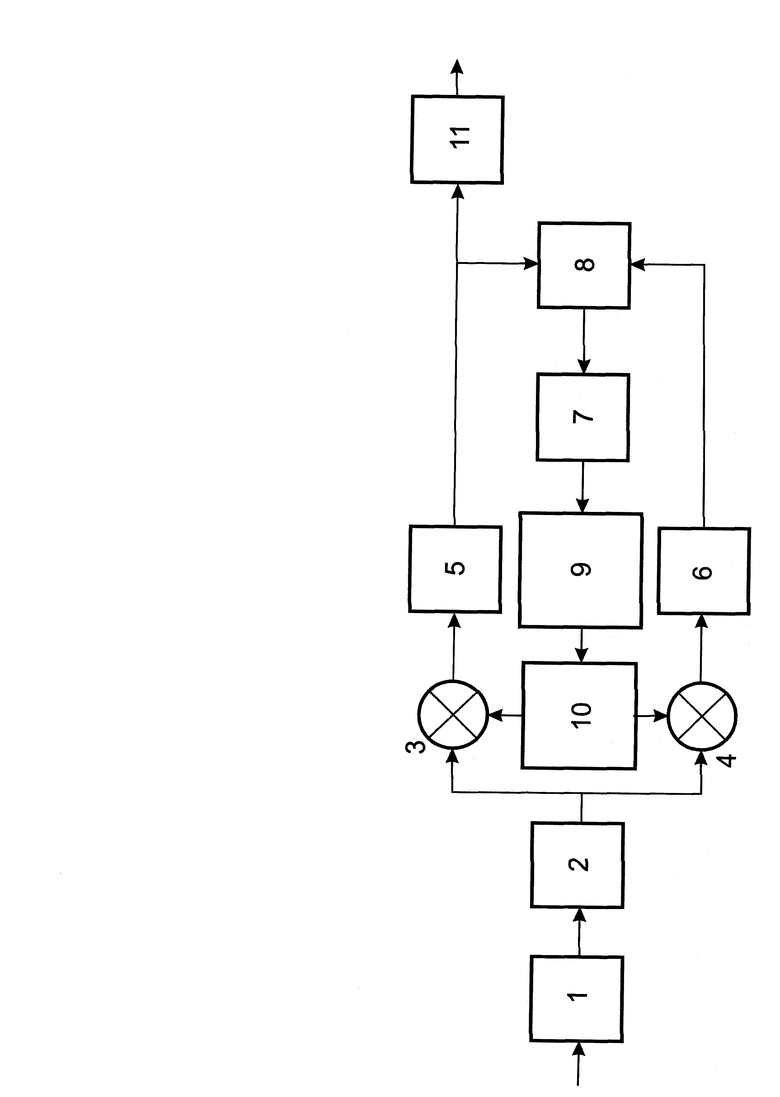

Сущность изобретения поясняется чертежом, на котором представлена функциональная схема устройства.

Устройство содержит содержит аналого-цифровой преобразователь 1, вход которого является входом цифрового демодулятора, полосовой фильтр 2, первый 3 и второй 4 перемножители, первый 5, второй 6 и третий 7 фильтры нижних частот, анализатор фазы 8, пропорционально-интегрально-дифференциальный регулятор 9, модуль 10 прямого цифрового синтеза, пропорционально-интегрально-дифференциального регулятора 9 и компаратор 11, выход которого является выходом цифрового демодулятора.

Выход аналого-цифрового преобразователя 1 подключен ко входу полосового фильтра 2, выход которого соединен с первыми входами первого и второго перемножителей 3 и 4, вторые входы которых подключены к соответствующим выходам модуля 10 прямого цифрового синтеза, вход которого соединен с выходом пропорционально-интегрально-дифференциального регулятора 9. При этом выход первого фильтра 5 нижних частот подключен к первому входу анализатора фазы 8 и входу компаратора 10, а выход второго фильтра 6 нижних частот соединен со вторым входом анализатора фазы 8, выход которого подключен ко входу третьего фильтра 7 нижних частот, выход которого соединен со входом пропорционально-интегрально-дифференциального регулятора 9..

Предлагаемый демодулятор работает следующим образом.

На вход устройства поступает аналоговый сигнал на промежуточной частоте. Аналогово-цифровой преобразователь (АЦП) 1 осуществляет дискретизацию сигнала. Дальнейшая обработка сигналов осуществляется в цифровом виде.

С помощью полосового фильтра 2 выделяется рабочая полоса частот и предотвращаются наложения спектра, вызванные дискретизацией сигнала. Оцифрованный сигнал с АЦП 1 подается на перемножители 3 и 4, которые осуществляют выделение квадратур сигналов путем умножения входного сигнала на синусоиду и косинусоиду опорной частоты, формируемые модулем прямого цифрового синтеза 10. Фильтры нижних частот 5 и 6 согласованы с частотой следования информационных сигналов и предназначены для подавления компоненты удвоенной частоты, возникающей в результате операции умножения частот.

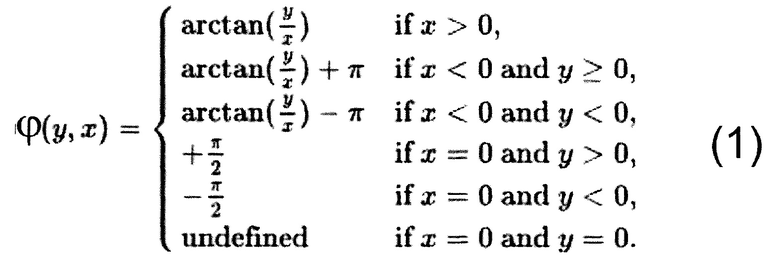

Синфазная и квадратурная составляющие являются входными сигналами для анализатора фазы 8, который по входным значениям вычисляет величину фазового угла согласно выражению 1 и нормализует полученную величину фазового угла согласно выражению 2.

При вычислении фазового угла по выражению (1) в качестве аргумента х выступает значение синфазной составляющей, а в качестве аргументау - значение квадратурной составляющей сигнала.

В выражении (2) ϕ - значение фазового угла, вычисленное по выражению (1),  - искомое значение нормализованного фазового угла. Основным назначением операции нормализации является устранение влияния фазовой модуляции информационным потоком абсолютной фазы сигнала. Известно, что непосредственное использование схем фазовой автоподстройки частоты (ФАПЧ) как систем восстановления когерентной несущей для ФМС затруднено. Причина в том, что схема ФАПЧ, на вход которой подан ФМС, будет постоянно перестраиваться, пытаясь синхронизироваться с каждым символом входного сигнала. Необходимо тем или иным способом исключить информационную составляющую из входного сигнала, что и реализуется применением операции, описываемой выражением (2).

- искомое значение нормализованного фазового угла. Основным назначением операции нормализации является устранение влияния фазовой модуляции информационным потоком абсолютной фазы сигнала. Известно, что непосредственное использование схем фазовой автоподстройки частоты (ФАПЧ) как систем восстановления когерентной несущей для ФМС затруднено. Причина в том, что схема ФАПЧ, на вход которой подан ФМС, будет постоянно перестраиваться, пытаясь синхронизироваться с каждым символом входного сигнала. Необходимо тем или иным способом исключить информационную составляющую из входного сигнала, что и реализуется применением операции, описываемой выражением (2).

При этом скачки фазы устраняются благодаря двукратно примененной операции взятия модуля, а динамический диапазон изменения значения фазы сужается до интервала [0, π/2]. В результате чего результирующий сигнал отражает разность фаз, возникающую из-за рассогласования частот тактовых генераторов приемника и передатчика.

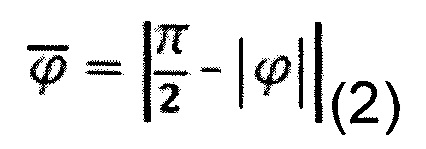

Далее нормализованный сигнал фазы сглаживается ФНЧ 7, полоса пропускания которого ограничена величиной максимального допустимого частотного рассогласования между опорными частотами модулятора и демодулятора. Ширина полосы пропускания данного фильтра напрямую обуславливает полосу захвата ФАПЧ, однако, попадающие в полосу шумы негативно влияют на устойчивость системы управления. В результате частотного анализа устойчивости системы было получено выражение 3, обуславливающее выбор оптимальной полосы для ФНЧ 7.

В выражении (3) В - оптимальная ширина полосы пропускания ФНЧ 7, Fs - частота следования информационных символов, Δƒ - максимальное ожидаемое доплеровское смещение частоты принимаемого радиосигнала.

Пропорционально-интегрально-дифференцирующий регулятор (ПИД-регулятор 9 предназначен для формирования управляющего сигнала с целью получения необходимой точности регулирования.

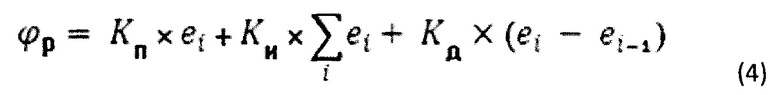

ПИД-регулятор 9 формирует управляющий сигнал, являющийся суммой трех слагаемых, первое из которых пропорционально разности входного сигнала и сигнала обратной связи (сигнал рассогласования), второе - интеграл сигнала рассогласования, третье - производная сигнала рассогласования.

ПИД-регулятор 6 по входному сигналу  с выхода ФНЧ 7 рассчитывает ошибку регулирования фазы и на основании ее вычисляет значение фазы, передаваемую на модуль прямого цифрового синтеза 10, который реализуется по известной схеме и с помощью известных технических средств (см. например [5] https.//yandex.ru/images/search?text=модуль прямого цифрового синтеза&stype=image&Ir=213&source=wiz).

с выхода ФНЧ 7 рассчитывает ошибку регулирования фазы и на основании ее вычисляет значение фазы, передаваемую на модуль прямого цифрового синтеза 10, который реализуется по известной схеме и с помощью известных технических средств (см. например [5] https.//yandex.ru/images/search?text=модуль прямого цифрового синтеза&stype=image&Ir=213&source=wiz).

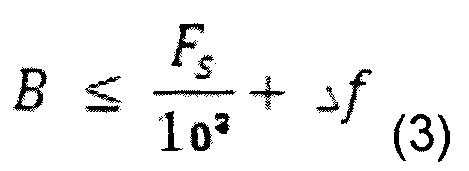

Ошибка регулирования вычисляется как разность между оптимальной величиной фазового угла  и входным сигналом регулятора. Так как величина фазового угла однозначно определяет амплитуду квадратурных сигналов, оптимальное значение фазового угла рассчитывается исходя из желаемого соотношения сигнал-шум (ОСШ). Так, если желаемое ОСШ установлено равным 6 дБ, средняя амплитуда квадратурной составляющей, поступающей на компаратор 9, должна быть в 4 раза больше среднего уровня помехи в канале. В ([6] Ким Д.П. «Теория автоматического управления. Т. 1. Линейные системы». - М.: Физматлит, 2003) описан метод синтеза ПИД-регулятора для линейных дискретных систем. Выходной сигнал ПИД-регулятора описывается выражением 4.

и входным сигналом регулятора. Так как величина фазового угла однозначно определяет амплитуду квадратурных сигналов, оптимальное значение фазового угла рассчитывается исходя из желаемого соотношения сигнал-шум (ОСШ). Так, если желаемое ОСШ установлено равным 6 дБ, средняя амплитуда квадратурной составляющей, поступающей на компаратор 9, должна быть в 4 раза больше среднего уровня помехи в канале. В ([6] Ким Д.П. «Теория автоматического управления. Т. 1. Линейные системы». - М.: Физматлит, 2003) описан метод синтеза ПИД-регулятора для линейных дискретных систем. Выходной сигнал ПИД-регулятора описывается выражением 4.

В выражении (4)  - выходной сигнал ПИД-регулятора 6,

- выходной сигнал ПИД-регулятора 6,  - ошибка регулирования, определяемая как разность между оптимальной величиной фазового угла

- ошибка регулирования, определяемая как разность между оптимальной величиной фазового угла  и входным сигналом регулятора

и входным сигналом регулятора  , Кп, Ки, Кд - коэффициенты регулятора, i - шаг расчета.

, Кп, Ки, Кд - коэффициенты регулятора, i - шаг расчета.

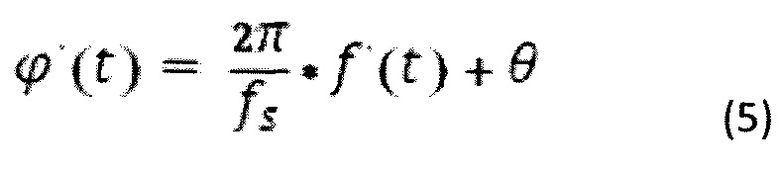

При аппроксимации шума в канале радиосвязи функцией распределения плотности вероятности аддитивного белого гауссова шума приращение абсолютного значения фазового угла во времени можно выразить уравнением 5:

где  - приращение фазы во времени, ƒs - частота дискретизации демодулятора,

- приращение фазы во времени, ƒs - частота дискретизации демодулятора,  - рассогласование несущих частот модулятора (передатчика) и демодулятора (приемника), θ - аддитивный белый гауссов шум. Из выражения 5 следует, что при ненулевом частотном рассогласовании величина абсолютного фазового угла накапливается во времени, поэтому при синтезе дискретной системы управления непрерывная часть описывается передаточной функцией интегратора:

- рассогласование несущих частот модулятора (передатчика) и демодулятора (приемника), θ - аддитивный белый гауссов шум. Из выражения 5 следует, что при ненулевом частотном рассогласовании величина абсолютного фазового угла накапливается во времени, поэтому при синтезе дискретной системы управления непрерывная часть описывается передаточной функцией интегратора:

В выражении (6) WНЧ(s) - передаточная функция непрерывной части системы, s - комплексная переменная преобразования Лапласа.

Аналогово-цифровой преобразователь 1 с периодом дискретизации Т может быть математически описан с помощью передаточной функции фиксатора нулевого порядка:

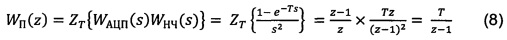

Так как предлагаемая система дискретна, для оценки ее устойчивости и качества требуется провести Z-преобразование для передаточных функций в изображениях Лапласа, выраженных в(6) и (7). Дискретная приведенная передаточная функция непрерывной части имеет вид:

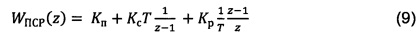

Пропорционально-суммарно-разностный (ПСР) регулятор является аналогом ПИД-регулятора для дискретных систем, его передаточная функция в Z-изображениях представлена выражением (9):

ПИД-регулятор 6 для управления обеспечивает порядок астатизма системы равный 2, так как суммарно система содержит два интегратора - один в структуре регулятора, второй - в структуре объекта управления. Второй порядок астатизма обеспечивает нулевую ошибку регулирования  при постоянном или линейно возрастающем управляющем воздействии (

при постоянном или линейно возрастающем управляющем воздействии ( или

или  ) и возмущении (

) и возмущении ( или

или  ).

).

После обработки сигналов описанным выше образом синфазная составляющая сигнала с выхода фильтра 5 поступает на вход компаратора 11, который осуществляет сравнение амплитуды сигнала с нулевым уровнем и формирует выходную последовательность бит.

Испытания показали, что амплитудно-фазовые частотные характеристики предлагаемого демодулятора удовлетворяют критерию Найквиста, и система управления, реализованная в демодуляторе, устойчива как по управляющему воздействию, так и по возмущению.

Таким образом, предлагаемый цифровой демодулятор позволяет обеспечить:

Возможность поддерживать амплитудное соотношение между квадратурными сигналами и однозначно детектировать переданные данные, в результате чего достигается повышение помехоустойчивости, увеличение полосы допустимого частотного рассогласования между частотами ФМС и управляемого синтезатора; уменьшение вероятности срыва слежения за фазой в сложной помеховой обстановке.

- Детектирование неравномерно распределенных данных, что позволяет передавать информационные сообщения с преобладающим количеством нулей или единиц без дополнительной битовой синхронизации через преамбулы или синхрослова, что в свою очередь снимает ограничения с алгоритма передающего устройства.

- Реализуемость в программируемой логике ввиду отсутствия сложных математических операций, что позволяет минимизировать количество используемых ресурсов и увеличить скорость обработки.

Предлагаемый демодулятор двухпозиционных фазоманипулированных сигналов с управлением по фазе обладает новизной, реализован на ПЛИС Cyclon-4 фирмы Intel, имеющих достаточные аппаратные ресурсы для работы на частоте до 200 МГц. и может быть неоднократно воспроизведен, т.е. соответствует критерию промышленной применимости.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДЕМОДУЛЯТОР СИСТЕМЫ СВЯЗИ С ДВУХКРАТНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2009 |

|

RU2427969C1 |

| Квазикогерентный демодулятор фазоманипулированных сигналов | 1990 |

|

SU1758897A1 |

| ДЕМОДУЛЯТОР СИСТЕМЫ СВЯЗИ С ДВУКРАТНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2008 |

|

RU2376718C1 |

| Квазикогерентный демодулятор фазоманипулированных сигналов | 1990 |

|

SU1758898A1 |

| СПОСОБ ДЛЯ ОПРЕДЕЛЕНИЯ РАБОЧИХ ПАРАМЕТРОВ СИСТЕМЫ ЦИФРОВОЙ СВЯЗИ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2012 |

|

RU2523219C2 |

| ДЕМОДУЛЯТОР СИГНАЛОВ ЧЕТЫРЕХПОЗИЦИОННОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 1990 |

|

RU2019050C1 |

| ЦИФРОВОЕ КВАДРАТУРНОЕ УСТРОЙСТВО ФАЗОВОЙ СИНХРОНИЗАЦИИ И ДЕМОДУЛЯЦИИ | 2015 |

|

RU2591032C1 |

| СПОСОБ ОБНАРУЖЕНИЯ ЖИВЫХ ОБЪЕКТОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2010 |

|

RU2442186C1 |

| ДЕМОДУЛЯТОР ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2008 |

|

RU2393641C1 |

| ИЗМЕРИТЕЛЬ ФАЗ ОСЦИЛЛОГРАФИЧЕСКИЙ | 2005 |

|

RU2314543C2 |

Изобретение относится к радиотехнике и может быть использовано в радиоприемных устройствах, а именно - в детекторах сигналов с двухпозиционной фазовой манипуляцией. Демодулятор содержит первый и второй перемножители, первый, второй и третий фильтры нижних частот и анализатор фазы, аналого-цифровой преобразователь, вход которого является входом демодулятора, полосовой фильтр, пропорционально-интегрально-дифференциальный регулятор, модуль прямого цифрового синтеза, и компаратор, выход которого является выходом демодулятора, при этом выход аналого-цифрового преобразователя подключен ко входу полосового фильтра, выход которого соединен с первыми входами первого и второго перемножителей, вторые входы которых подключены к соответствующим выходам модуля прямого цифрового синтеза, управляющий вход которого соединен с выходом пропорционально-интегрально-дифференциального регулятора, причем выход первого фильтра нижних частот подключен к первому входу анализатора фазы и входу компаратора, а выход второго фильтра нижних частот соединен со вторым входом анализатора фазы, выход которого подключен ко входу третьего фильтра нижних частот, выход которого соединен со входом пропорционально-интегрально-дифференциального регулятора. Техническим результатом является снижение вероятности «обратной работы», обеспечение стабильности вне зависимости от начальной фазовой неопределенности, обеспечение детектирования принимаемого сигнала без какой-либо информации о характере передаваемых данных, повышение помехоустойчивости и уменьшение вероятности срыва слежения за фазой при наличии значительных помех при приеме информационного сигнала. 1 ил.

Демодулятор двухпозиционных фазоманипулированных сигналов, содержащий первый и второй перемножители, первый, второй и третий фильтры нижних частот и анализатор фазы, отличающийся тем, что он содержит аналого-цифровой преобразователь, вход которого является входом демодулятора, полосовой фильтр, пропорционально-интегрально-дифференциальный регулятор, модуль прямого цифрового синтеза и компаратор, выход которого является выходом демодулятора, при этом выход аналого-цифрового преобразователя подключен ко входу полосового фильтра, выход которого соединен с первыми входами первого и второго перемножителей, вторые входы которых подключены к соответствующим выходам модуля прямого цифрового синтеза, управляющий вход которого соединен с выходом пропорционально-интегрально-дифференциального регулятора, причем выход первого фильтра нижних частот подключен к первому входу анализатора фазы и входу компаратора, а выход второго фильтра нижних частот соединен со вторым входом анализатора фазы, выход которого подключен ко входу третьего фильтра нижних частот, выход которого соединен со входом пропорционально-интегрально-дифференциального регулятора.

| Горелка для сжигания порошкообразных материалов в струе кислорода | 1960 |

|

SU139043A1 |

| ДЕМОДУЛЯТОР СИСТЕМЫ СВЯЗИ С ДВУХКРАТНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2009 |

|

RU2427969C1 |

| US 4833416 A1, 23.05.1989 | |||

| US 9553748 B2, 24.01.2017 | |||

| Способ гальванического снятия позолоты с серебряных изделий без заметного изменения их формы | 1923 |

|

SU12A1 |

| NICOLOSO STEVEN P | |||

| An Investigation Of Carrier Recovery Techniques For Psk Modulated Signals In Cdma And Multipath Mobile Environments Virginia Blacksburg, June 1997[Электронный ресурс] URL: http:// vtechworks.lib.vt.edu›handle/10919/35869 Дата создания: 09.09.2015, рис.4.3,4.5 | |||

| СОРОХТИН Е.М | |||

| и др Алгоритм цифровой демодуляции многопозиционных фазоманипулированных сигналов для реализации в программируемой логике, Вестник Нижегородского университета им | |||

| Н.И | |||

| Лобачевского, 2010, # 5(2), рис.1,3. | |||

Авторы

Даты

2019-09-03—Публикация

2018-09-11—Подача