Изобретение относится к радиотехнике и предназначено для использования при когерентной демодуляции сигналов с многопозиционной фазовой манипуляцией (ФМн).

Известен демодулятор сигналов четырехпозиционной ФМн [1], содержащий два фазовых детектора (ФД), два фильтра нижних частот, вычитатель, петлевой фильтр, управляемый генератор, фазовращатель, блок измерения отношения сигнал/шум, два двойных балансных смесителя, два регулируемых усилителя.

Недостатком этого устройства являются его энергетические потери, которые показывают, на сколько нужно увеличить отношение сигнал/шум (SNR), то есть увеличить мощность передатчика, чтобы получить потенциально возможную вероятность битовой ошибки.

Из структуры демодулятора [1] видно, что восстановление несущей выполнено с помощью контура фазовой автоподстройки частоты (ФАПЧ), от качества работы которого зависят энергетические потери. В контуре ФАПЧ устройства применена синфазно-квадратурная схема (эквивалент схемы Костаса), увеличивающая дисперсию фазы  восстановленного колебания. Производительность такой схемы эквивалентна схеме возведения сигнала в квадрат (см., например, [2] абзац 10.2.1.5, стр.637).

восстановленного колебания. Производительность такой схемы эквивалентна схеме возведения сигнала в квадрат (см., например, [2] абзац 10.2.1.5, стр.637).

Снижение дисперсии фазы возможно за счет уменьшения шумовой полосы ФАПЧ, что в некоторой степени уменьшает энергетические потери, если это не приводит к противоположному результату, когда возрастает дисперсия фазы, вызванная нескомпенсированной паразитной фазовой модуляцией (ПФМ). Уровень ее определяется фазовым шумом гетеродинов передатчика и приемника, а также паразитными гармоническими составляющими, находящимися в их спектре. Большой уровень ПФМ может внести значительный вклад в общие энергетические потери, которые становятся невосполнимыми (см., например, [2] абзац, 10.2.1.8, стр.641, 642).

Энергетические потери также связаны с применением в устройстве [1] управляемого генератора, который входит в контур ФАПЧ и, как правило, обладает низкой стабильностью и повышенной ПФМ по сравнению со стабилизированным генератором, работающим на фиксированной частоте.

Наиболее близким к заявляемому демодулятору, принятым за прототип, является устройство компенсации нестабильности несущей частоты фазоманипулированных сигналов [3], содержащее два перемножителя, первые входы которых объединены и являются входом устройства, фазовращатель, синтезатор частоты, опорный генератор, два аналого-цифровых преобразователя (АЦП), два интегратора со сбросом, вычислитель двойного арктангенса, два умножителя-делителя, петлевой фильтр, синтезатор фазы, два блока вычитания, выход второго блока вычитания является выходом устройства.

Устройство компенсации нестабильности несущей частоты [3] является основной составной частью демодуляторов ФМн сигналов, от которой зависят их энергетические потери. Устройство [3] имеет меньшие энергетические потери по сравнению с устройством [1] только при высоких скоростях передачи информации, превышающих нестабильность несущей частоты в десятки раз. При более низких скоростях передачи информации в устройстве [3] возникают энергетические потери. При скоростях передачи информации, менее или соизмеримых с нестабильностью несущей частоты, устройство [3] становится неработоспособным.

Предлагаемое изобретение направлено на решение задачи снижения энергетических потерь при когерентной демодуляции сигналов с многопозиционной ФМн при низких скоростях передачи информации.

Достижение технического результата демодулятора фазоманипулированных сигналов определяется совокупностью следующих существенных признаков:

- наличием, так же как и в прототипе, первого и второго перемножителей, фазовращателя, первого и второго АЦП, опорного генератора, синтезатора частоты, вычислителя двойного арктангенса, умножителя-делителя, блока вычитания, синтезатора фазы, причем первые входы первого и второго перемножителей объединены и являются входом устройства, выход фазовращателя соединен со вторым входом первого перемножителя, а второй вход второго перемножителя объединен с входом фазовращателя, выход опорного генератора соединен с входом синтезатора частоты, выход которого соединен с объединенными вторым входом второго перемножителя и входом фазовращателя, выходы первого и второго перемножителей соединены с входами соответственно первого и второго АЦП, выход вычислителя двойного арктангенса соединен с первым входом блока вычитания,

- наличием, в отличие от прототипа, комплексного перемножителя, синусно-косинусного функционального преобразователя, первого и второго согласованных фильтров (СФ), элемента задержки, первого, второго и третьего сумматоров элементов, вычислителя арктангенса, первого и второго сумматоров, вычислителя дисперсии фазы, интегратора, компаратора, причем выходы первого и второго АЦП соединены соответственно с первым и вторым входами комплексного перемножителя, первый и второй выходы синусно-косинусного функционального преобразователя соединены соответственно с третьим и четвертым входами комплексного перемножителя, первый и второй выходы комплексного перемножителя соединены соответственно с входом первого СФ и с входом второго СФ, выход первого СФ соединен с первым входом вычислителя двойного арктангенса и с входом первого сумматора элементов, выход второго СФ соединен со вторым входом вычислителя двойного арктангенса и с входом второго сумматора элементов, выход вычислителя двойного арктангенса также соединен с входом элемента задержки, выход элемента задержки соединен со вторым входом блока вычитания, выход блока вычитания соединен с входом третьего сумматора элементов, выходы первого и второго сумматоров элементов являются выходами демодулятора и соединены, соответственно, с первым и вторым входами вычислителя арктангенса, при этом выход вычислителя арктангенса соединен с первым входом умножителя-делителя, выход которого соединен с первыми входами первого и второго сумматоров и входом вычислителя дисперсии фазы, выход третьего сумматора элементов соединен со вторым входом первого сумматора, выход которого соединен с входом интегратора, выход интегратора соединен со вторым входом второго сумматора, выход которого соединен с входом синтезатора фазы, выход синтезатора фазы соединен со входом синусно-косинусного функционального преобразователя, выход вычислителя дисперсии фазы соединен с первым входом компаратора, выход которого соединен с входом управления третьего сумматора элементов, вторые входы умножителя-делителя и компаратора объединены и являются управляющим входом демодулятора,

- наличием дополнительного блока поиска, вход которого соединен с выходом компаратора, а выход блока поиска соединен с входом данных интегратора.

Первый и второй перемножители, фазовращатель, так же как и в прототипе, образуют квадратурный преобразователь, который переносит спектр сигнала St с промежуточной или несущей частоты вниз, на сигнальную плоскость, на которой вектор сигнала вращается с разностной частотой. Разностная частота, как положительная, так и отрицательная, определяется нестабильностью несущих частот приемника и передатчика, в том числе и доплеровским сдвигом частоты.

Опорный генератор и синтезатор частоты, так же как и в прототипе, образуют стабилизированный генератор, работающий на фиксированной, номинальной частоте приема, который является гетеродином для квадратурного преобразователя.

Первый и второй АЦП, так же как и в прототипе, квантуют сигнал по амплитуде и времени.

Синтезатор фазы совместно с синусно-косинусным функциональным преобразователем образуют цифровой синтезатор отсчетов, выход которого соединен с комплексным перемножителем. Синусно-косинусный функциональный преобразователь выполняется на основе постоянного запоминающего устройства (ПЗУ), адресом которого является выходное значение сигнала синтезатора фазы. Комплексный перемножитель перемножает входной сигнал с опорным сигналом синтезатора отсчетов и переносит центр спектра входного сигнала, в режиме синхронизации несущей, в область частоты, равной нулю. Таким образом, на выходе комплексного перемножителя образуется новая сигнальная плоскость, на которой вектор сигнала становится невращаемым. Комплексный перемножитель выполняется на основе четырех перемножителей, сумматора и вычитателя.

Первый и второй СФ выполняются на основе регистра сдвига длиной, равной расширяющей псевдослучайной последовательности (ПСП), которая накладывается передающей стороной на каждую информационную посылку временной длительностью T, перемножителя, нескольких многовходовых "пирамидальных" сумматоров элементарных участков информационной посылки. Информационная посылка временной длительностью T делится на несколько элементов длительностью T/w, на интервале которых СФ производят свертку, перемножение с расширяющей ПСП и накопление сигнала.

Вычислитель двойного арктангенса, по оцененным согласованными фильтрами элементам квадратурных составляющих сигнала, последовательно оценивает фазу вектора сигнала на всей сигнальной плоскости от -π до π.

Вычислитель двойного арктангенса выполняется на основе ПЗУ, адресом которого являются цифровые синфазный и квадратурный отсчеты элементов информационной посылки сигнала.

Элемент задержки задерживает оцененные вычислителем двойного арктангенса значения фазы сигнала на время, равное длительности элемента T/w. Блок вычитания вычисляет разницу фаз сигнала между текущим и задержанным их значениями. Третий сумматор элементов вычисляет сумму разностей фаз сигнала в пределах длительности T информационной посылки. Вычислитель двойного арктангенса, элемент задержки, блок вычитания и третий сумматор элементов образуют частотный детектор (ЧД).

Первый и второй сумматоры элементов по оцененным первым и вторым СФ элементам квадратурных составляющих сигнала производят дальнейшее накопление сигнала на длительности Т информационной посылки. Выходы первого и второго сумматоров элементов являются выходами демодулятора, а также поступают на вычислитель арктангенса.

Вычислитель арктангенса по оцененным первым и вторым сумматорами элементов квадратурных составляющих сигнала оценивает фазу вектора сигнала на сигнальной плоскости от -π/2 до π/2.

Вычислитель двойного арктангенса выполняется на основе ПЗУ, адресом которого являются цифровые синфазный и квадратурный оцененные значения сигнала.

Умножитель-делитель снимает фазовую манипуляцию сигнала на выходе вычислителя арктангенса при индексе манипуляции M, равном двум и более. Вычислитель арктангенса и умножитель-делитель образуют линейный ФД.

Первый сумматор производит суммирование выходов частотного и фазового детекторов, результат суммирования поступает на интегратор, представляющий собой накапливающий сумматор.

Второй сумматор и интегратор образуют петлевой пропорционально- интегрирующий фильтр (ПИФ), выход которого поступает на синтезатор фазы, в общем случае на синтезатор отсчетов.

Синтезатор отсчетов, комплексный перемножитель, частотный и фазовый детекторы, сумматоры, ПИФ образуют контур частотно-фазовой автоподстройки частоты, отслеживающий вращение фазы вектора сигнала, вызванное нестабильностью несущей частоты, а также ПФМ гетеродинов.

Вычислитель дисперсии фазы содержит квадратор и накапливающий сумматор со сбросом, то есть производит квадрирование выхода ФД и усреднение результата квадрирования на некотором участке времени. Компаратор сравнивает результат усреднения с установленным порогом, который определяется индексом манипуляции М. Вычислитель дисперсии фазы совместно с компаратором образуют детектор синхронизма. В режиме синхронизма выход компаратора блокирует (обнуляет) третий сумматор элементов, тем самым отключает ЧД.

Демодулятор дополнительно содержит блок поиска, который представляет собой накапливающий сумматор (интегратор) с верхним и нижним ограничителями. Выходные данные блока поиска записываются в интегратор ПИФ. В режиме синхронизации запись выходных данных блока поиска в интегратор ПИФ блокируется детектором синхронизма.

Таким образом, технический результат - снижение энергетических потерь, достигается путем компенсации на элементарных участках информационных посылок вращения фазы вектора сигнала, вызванного нестабильностью несущей частоты.

Для пояснения работы демодулятора ФМн сигналов приводятся следующие чертежи:

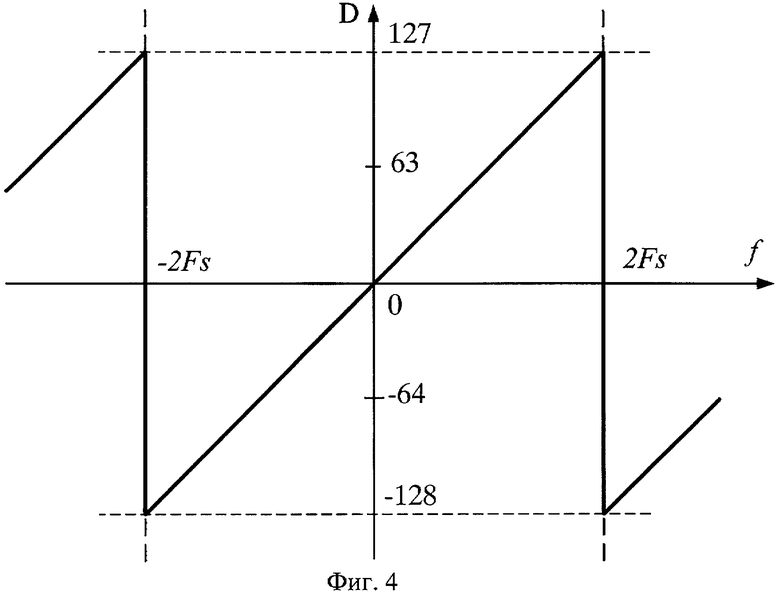

- фиг.1. Структурная схема демодулятора ФМн сигналов;

- фиг.2. Алгоритм функционирования СФ;

- фиг.3. График функции двойного арктангенса и дискриминационные характеристики ФД;

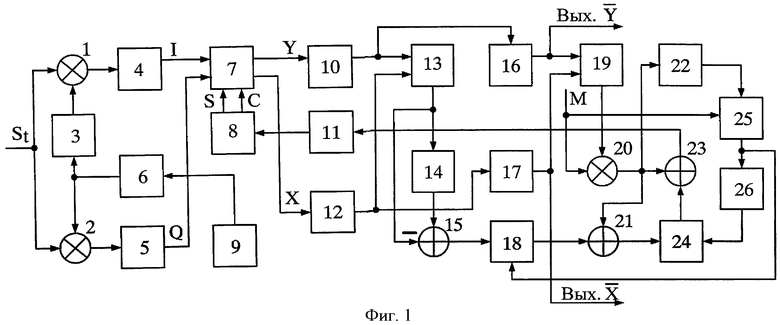

- фиг.4. Дискриминационная характеристика ЧД.

По п.1 формулы структурная схема демодулятора ФМн сигналов (фиг.1) содержит первый и второй перемножители 1 и 2, фазовращатель 3, первый и второй АЦП 4 и 5, синтезатор частоты 6, опорный генератор 9, комплексный перемножитель 7, синусно-косинусный функциональный преобразователь 8, первый и второй СФ 10 и 12, синтезатор фазы 11, вычислитель двойного арктангенса 13, элемент задержки 14, блок вычитания 15, первый, второй и третий сумматоры элементов 16, 17 и 18, вычислитель арктангенса 19, умножитель-делитель 20, первый и второй сумматоры 21 и 23, вычислитель дисперсии фазы 22, интегратор 24, компаратор 25.

По п.2 формулы структурная схема демодулятора ФМн сигналов дополнительно содержит блок поиска 26.

По п.1 формулы первые входы первого и второго перемножителей 1 и 2 объединены и являются входом демодулятора, выход фазовращателя 3 соединен со вторым входом первого перемножителя 1, а второй вход второго перемножителя 2 объединен с входом фазовращателя 3, выход опорного генератора 9 соединен с входом синтезатора частоты 6, выход которого соединен с объединенными вторым входом второго перемножителя 2 и входом фазовращателя 3, выходы первого и второго перемножителей 1 и 2 соединены с входами соответственно первого и второго АЦП 4 и 5, выходы первого и второго АЦП 4 и 5 соединены, соответственно, с первым и вторым входами комплексного перемножителя 7, первый и второй выходы синусно-косинусного функционального преобразователя 8 соединены соответственно с третьим и четвертым входами комплексного перемножителя 7, первый и второй выходы комплексного перемножителя 7 соединены соответственно с входом первого СФ 10 и с входом второго СФ 12, выход первого СФ 10 соединен с первым входом вычислителя двойного арктангенса 13 и с входом первого сумматора элементов 16, выход второго СФ 12 соединен со вторым входом вычислителя двойного арктангенса 13 и с входом второго сумматора элементов 17, выход вычислителя двойного арктангенса 13 соединен с входом элемента задержки 14 и с первым входом блока вычитания 15, выход элемента задержки 14 соединен со вторым входом блока вычитания 15, выход блока вычитания 15 соединен с входом третьего сумматора элементов 18, выходы первого и второго сумматоров элементов 16 и 17 являются выходами демодулятора и соединены, соответственно, с первым и вторым входами вычислителя арктангенса 19, при этом выход вычислителя арктангенса 19 соединен с первым входом умножителя-делителя 20, выход которого соединен с первыми входами первого и второго сумматоров 21 и 23 и входом вычислителя дисперсии фазы 22, выход третьего сумматора элементов 18 соединен со вторым входом первого сумматора 21, выход которого соединен с входом интегратора 24, выход интегратора 24 соединен со вторым входом второго сумматора 23, выход которого соединен с входом синтезатора фазы 11, выход синтезатора фазы соединен со входом синусно-косинусного функционального преобразователя 8, выход вычислителя дисперсии фазы 22 соединен с первым входом компаратора 25, выход которого соединен с входом управления третьего сумматора элементов 18, вторые входы умножителя-делителя 20 и компаратора 25 объединены и являются управляющим входом демодулятора.

По п.2 формулы вход блока поиска 26 соединен с выходом компаратора 25, а выход блока поиска 26 соединен с входом данных интегратора 24.

Устройство работает следующим образом.

Первый и второй перемножители 1 и 2 совместно с фазовращателем 3 на 90° образуют квадратурный преобразователь, который переносит спектр входного сигнала St c промежуточной частоты или несущей вниз, на сигнальную плоскость I, Q. Опорным сигналом для квадратурного преобразователя является выходной сигнал синтезатора частоты 6, который работает на фиксированной, номинальной частоте принимаемого сигнала. В свою очередь, синтезатор частоты 6 работает от высокостабильного, спектрально чистого опорного генератора 9.

Первый и второй АЦП 4 и 5 квантуют сигнал по амплитуде и времени и работают на повышенной частоте kFs, кратной тактовой частоте Fs. Сигнал на выходе аналого-цифровых преобразователей представляется вектором, имеющим комплексную форму записи:

где А(nτ) - текущее, суммарное значение амплитуды сигнала и шума;

φ(nτ) - текущее, суммарное значение фазы сигнала и шума;

- период квантования сигнала.

- период квантования сигнала.

Текущее, суммарное значение амплитуды сигнала и шума представляется следующим выражением:

где I(nτ) и Q(nτ) - квадратурные составляющие сигнала и шума на выходах АЦП 4 и 5.

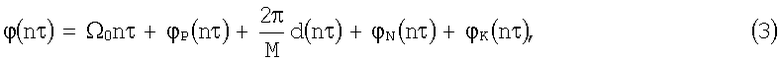

Текущее, суммарное значение фазы сигнала и шума представляется следующим выражением:

где Ω0 - угловая частота расстройки несущей приемника и передатчика (с учетом доплеровского сдвига), подлежащая компенсации;

φP(nτ) - динамическая составляющая отклонения фазы несущих частот приемника и передатчика, вызванная ПФМ и подлежащая компенсации;

- составляющая, обусловленная манипуляцией фазы сигнала передатчика информационными символами, d может принимать значения от 0 до М-1;

- составляющая, обусловленная манипуляцией фазы сигнала передатчика информационными символами, d может принимать значения от 0 до М-1;

φN(nτ) - динамическая составляющая отклонения фазы сигнала, вызванная аддитивным, белым, гауссовским шумом (АБГШ);

φK(nτ) - динамическая составляющая отклонения фазы сигнала, вызванная ошибкой (шумом) квантования.

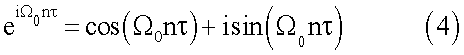

Синтезатор фазы 11 совместно с синусно-косинусным функциональным преобразователем 8 образуют цифровой синтезатор отсчетов, который формирует в режиме синхронизации синусную и косинусную составляющие единичного вектора, имеющим комплексную форму записи:

В качестве синтезатора фазы 11 используется цифровой интегратор (накапливающий сумматор). Синтезатор фазы 11, а следовательно, и синтезатор отсчетов имеют возможность получения на его выходе как нарастающей (положительная производная), так и убывающей (отрицательная производная) фазы, зависящей от знака на его входе. Периодичность или мгновенная частота повторения фазы на выходе синтезатора отсчетов определяется формулой:

где φC(nτ) - текущее значение фазы;

φC(nτ-τ) - задержанное значение фазы;

τ - период квантования сигнала.

На входе синтезатора фазы 11 задается производная фазы или частота. При отрицательной входной производной на выходе синтезатора его фаза будет убывающей. При ограниченной разрядности периодичность или частота повторения фазы определяется формулой:

где DC - децимальное значение цифрового входного сигнала (как положительное, так и отрицательное);

N - разрядность синтезатора фазы 11.

Из формулы (6) видно, что синтезатор отсчетов может формировать только дискретные значения частот с шагом, равным наименьшему значению частоты при DC=1(-1). При входном сигнале, равном нулю, фаза на выходе синтезатора отсчетов не меняется и имеет случайное (последнее) значение. Указанный синтезатор используется в контуре ФАПЧ для отслеживания вращения вектора сигнала, вызванного расстройкой несущей частоты приемника и передатчика с учетом доплеровского сдвига.

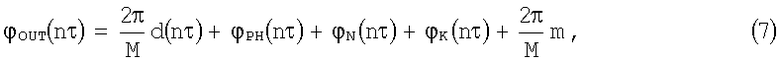

Комплексный перемножитель 7 перемножает входной сигнал S(nτ) с отрицательным единичным вектором  синтезатора отсчетов. Алгоритм комплексного перемножения определяется следующими выражениями: X=I·S+Q·C; Y=I·C-Q·S. Знак единичного вектора учтен комплексным перемножителем 7, который переносит центр спектра входного сигнала, в режиме синхронизации несущей, в область частоты, равной нулю. Таким образом, на выходе комплексного перемножителя 7 образуется новая сигнальная плоскость X, Y, на которой вектор сигнала становится невращаемым, фаза которого определяется формулой:

синтезатора отсчетов. Алгоритм комплексного перемножения определяется следующими выражениями: X=I·S+Q·C; Y=I·C-Q·S. Знак единичного вектора учтен комплексным перемножителем 7, который переносит центр спектра входного сигнала, в режиме синхронизации несущей, в область частоты, равной нулю. Таким образом, на выходе комплексного перемножителя 7 образуется новая сигнальная плоскость X, Y, на которой вектор сигнала становится невращаемым, фаза которого определяется формулой:

где  - составляющая, обусловленная манипуляцией фазы сигнала передатчика информационными символами, где d может принимать значения от 0 до М-1;

- составляющая, обусловленная манипуляцией фазы сигнала передатчика информационными символами, где d может принимать значения от 0 до М-1;

- нескомпенсированная, динамическая составляющая отклонения фазы несущих частот приемника и передатчика, вызванная ПФМ;

- нескомпенсированная, динамическая составляющая отклонения фазы несущих частот приемника и передатчика, вызванная ПФМ;

- динамическая составляющая отклонения фазы сигнала, вызванная АБГШ;

- динамическая составляющая отклонения фазы сигнала, вызванная АБГШ;

- динамическая составляющая отклонения фазы сигнала, вызванная ошибкой (шумом) квантования;

- динамическая составляющая отклонения фазы сигнала, вызванная ошибкой (шумом) квантования;

- фазовая неоднозначность, где m может принимать значения от 0 до М-1.

- фазовая неоднозначность, где m может принимать значения от 0 до М-1.

Первый и второй СФ 10 и 12 выполняются на основе регистра сдвига длиной, равной расширяющей ПСП, которая накладывается передающей стороной на каждую информационную посылку временной длительностью Т, перемножителя, нескольких многовходовых "пирамидальных" сумматоров элементарных участков информационной посылки. Информационная посылка временной длительностью Т делится на несколько элементов длительностью T/w, на интервале которых согласованные фильтры производят свертку, то есть перемножение с расширяющей ПСП, и накопление сигнала. Для примера, на фиг.2 приведен алгоритм функционирования СФ одного из квадратурных каналов при длине расширяющей ПСП, равной шестидесяти четырем b[0 … 63], и при делении информационной посылки на четыре элемента. Наложение расширяющей ПСП на информационные посылки позволяет по максимальным сверткам согласованных фильтров определять их границы. При скоростях передачи информации, превышающих в несколько раз нестабильность несущей частоты, когда границы информационных посылок могут быть определены, наложение расширяющей ПСП на них необязательно. В этом случае СФ производят только накопление сигнала на элементах информационных посылок.

Вычислитель двойного арктангенса 13, функции  , по оцененным согласованными фильтрами 10 и 12 элементам квадратурных составляющих сигнала

, по оцененным согласованными фильтрами 10 и 12 элементам квадратурных составляющих сигнала  ,

,  в пределах длительности информационной посылки Т последовательно оценивает фазу вектора сигнала на всей сигнальной плоскости от -π до π. Например, при делении информационной посылки на четыре элемента образуются четыре оцененных значения фазы

в пределах длительности информационной посылки Т последовательно оценивает фазу вектора сигнала на всей сигнальной плоскости от -π до π. Например, при делении информационной посылки на четыре элемента образуются четыре оцененных значения фазы  . В пределах информационной посылки, в режиме вхождения в синхронизм, оцененная фаза сигнала не зависит от индекса манипуляции, а зависит только от разности частот входного сигнала и синтезатора отсчетов. График функции двойного арктангенса D(φ), при восьмиразрядном выходе, приведен на фиг.3.

. В пределах информационной посылки, в режиме вхождения в синхронизм, оцененная фаза сигнала не зависит от индекса манипуляции, а зависит только от разности частот входного сигнала и синтезатора отсчетов. График функции двойного арктангенса D(φ), при восьмиразрядном выходе, приведен на фиг.3.

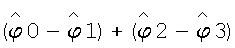

Элемент задержки 14 задерживает оцененные вычислителем двойного арктангенса 13 значения фазы сигнала  на время, равное длительности элемента T/w. Блок вычитания 15 вычисляет разницу фаз сигнала между текущим и задержанным их значениями, например:

на время, равное длительности элемента T/w. Блок вычитания 15 вычисляет разницу фаз сигнала между текущим и задержанным их значениями, например:  и

и  . Третий сумматор элементов 18 вычисляет сумму разностей фаз сигнала

. Третий сумматор элементов 18 вычисляет сумму разностей фаз сигнала  в пределах T информационной посылки. Вычислитель двойного арктангенса 13, элемент задержки 14, блок вычитания 15 и третий сумматор элементов 18 образуют частотный детектор. При таком построении ЧД обеспечивается раскрыв его дискриминационной характеристики, превышающий тактовую частоту информационных символов. Для примера: на фиг.4. приведена дискриминационная характеристика ЧД при делении информационной посылки на четыре элемента.

в пределах T информационной посылки. Вычислитель двойного арктангенса 13, элемент задержки 14, блок вычитания 15 и третий сумматор элементов 18 образуют частотный детектор. При таком построении ЧД обеспечивается раскрыв его дискриминационной характеристики, превышающий тактовую частоту информационных символов. Для примера: на фиг.4. приведена дискриминационная характеристика ЧД при делении информационной посылки на четыре элемента.

Первый и второй сумматоры элементов 16 и 17, работающие на повышенной частоте wFs, кратной тактовой частоте Fs, по оцененным согласованными фильтрами элементам квадратурных составляющих сигнала  ,

,  производят дальнейшее накопление сигнала на длительности Т информационной посылки. Для примера: при делении информационной посылки на четыре элемента

производят дальнейшее накопление сигнала на длительности Т информационной посылки. Для примера: при делении информационной посылки на четыре элемента  (см. фиг.2). Выходы первого и второго сумматоров элементов 16 и 17 являются выходами демодулятора, а также поступают на вычислитель арктангенса 19.

(см. фиг.2). Выходы первого и второго сумматоров элементов 16 и 17 являются выходами демодулятора, а также поступают на вычислитель арктангенса 19.

Вычислитель арктангенса 19 по оцененным первым и вторым сумматорами элементам 16 и 17 квадратурных составляющих сигнала  оценивает фазу вектора сигнала

оценивает фазу вектора сигнала  на сигнальной плоскости от -π/2 до π/2.

на сигнальной плоскости от -π/2 до π/2.

Умножитель-делитель 20 снимает фазовую манипуляцию сигнала на выходе вычислителя арктангенса 19 при индексах манипуляции М более двух. Операция умножения фазы сигнала на М/2, без учета переполнения, снимает фазовую манипуляцию, а операция деления на М/2 приводит к одной и той же фазовой крутизне сигнала, которая не зависит от индекса модуляции. Для цифрового сигнала в двоичной форме операция умножения-деления заменяется обнулением (исключением) старших разрядов на выходе вычислителя двойного арктангенса 19. Количество обнуляемых разрядов определяется двоичным логарифмом М/2 - индекса ФМн. Например: для модуляции ФМн-2 старший разряд не обнуляется, на выходе умножителя-делителя 20 остается функция арктангенса, а для ФМн-4 обнуляется один старший разряд, после чего на выходе умножителя-делителя 20 образуется функция арктангенса двойного угла. Графики этих функций D(Δφ) для М=2 и М=4 приведены на фиг.3. При этом фазовая неоднозначность демодулятора аналогична аналогу и прототипу.

Вычислитель арктангенса 19 и умножитель-делитель 20 образуют линейный фазовый детектор.

Первый сумматор 21 производит суммирование выходов частотного и фазового детекторов, результат суммирования поступает на интегратор 24.

Второй сумматор 23 и интегратор 24 образуют петлевой ПИФ, сигнал которого поступает на синтезатор фазы 11, в общем случае на синтезатор отсчетов.

В режиме вхождения в синхронизм синтезатор отсчетов комплексный перемножитель 7, частотный и фазовый детекторы, сумматоры 21 и 23, ПИФ образуют контур частотно-фазовой автоподстройки частоты, который первоначально стремится свести разность частот до полосы захвата системы ФАПЧ, которая в свою очередь будет стремиться свести разность фаз  и поддерживать это состояние. В режиме слежения за частотой работает только контур ФАПЧ. Таким образом осуществляется отслеживание вращения фазы вектора сигнала, вызванное нестабильностью несущей частоты, а также ПФМ гетеродинов.

и поддерживать это состояние. В режиме слежения за частотой работает только контур ФАПЧ. Таким образом осуществляется отслеживание вращения фазы вектора сигнала, вызванное нестабильностью несущей частоты, а также ПФМ гетеродинов.

Вычислитель дисперсии фазы 22 содержит квадратор и накапливающий сумматор со сбросом, то есть производит квадрирование выхода ФД и усреднение результата квадрирования на некотором участке времени. Дисперсия фазы  на выходе ФД однозначно связана с SNR на входе демодулятора. Дисперсия фазы

на выходе ФД однозначно связана с SNR на входе демодулятора. Дисперсия фазы  максимальна при отсутствии сигнала, в том числе и при отсутствии синхронизма. Максимальное

максимальна при отсутствии сигнала, в том числе и при отсутствии синхронизма. Максимальное

значение  зависит от раскрыва дискриминационной характеристики ФД, то есть от индекса манипуляции М. Компаратор 25 сравнивает результат усреднения с установленным порогом, который определяется индексом манипуляции М. Вычислитель дисперсии фазы 22 совместно с компаратором 25 образуют детектор синхронизма. В режиме фазового синхронизма выход компаратора 25 блокирует (обнуляет) третий сумматор элементов 18, тем самым отключая ЧД и исключая вносимый им дополнительный шум в петлю ФАПЧ.

зависит от раскрыва дискриминационной характеристики ФД, то есть от индекса манипуляции М. Компаратор 25 сравнивает результат усреднения с установленным порогом, который определяется индексом манипуляции М. Вычислитель дисперсии фазы 22 совместно с компаратором 25 образуют детектор синхронизма. В режиме фазового синхронизма выход компаратора 25 блокирует (обнуляет) третий сумматор элементов 18, тем самым отключая ЧД и исключая вносимый им дополнительный шум в петлю ФАПЧ.

По п.2 формулы демодулятор ФМн сигналов дополнительно содержит блок поиска 26, который представляет собой накапливающий сумматор с верхним и нижним ограничителями. Шаг накопления определяется полосой захвата петли частотной автоподстройки, а период накопления определяется временем переходного процесса частотно-фазовой автоподстройки и временем усреднения вычислителя дисперсии фазы 22. Выходные данные блока поиска 26 записываются в интегратор ПИФ с периодом его накопления. В режиме синхронизации запись выходных данных блока поиска в интегратор 24 ПИФ блокируется компаратором 25 детектора синхронизма.

Демодулятор по п.1 формулы используется при нестабильности несущих частот, менее или соизмеримых с тактовой частотой информационных посылок. Демодулятор по п.2 формулы используется при нестабильности несущих частот, превышающих полосу захвата по частоте системы компенсации несущей.

Для исключения дополнительных энергетических потерь демодулятора, возникающих за счет квантования по времени, частота дискретизации сигнала АЦП должна быть в десятки раз больше, чем нестабильность несущих частот.

Квадратурный преобразователь, синтезатор частоты, опорный генератор, АЦП выпускаются серийно промышленностью. Цифровая часть демодулятора фазоманипулированных сигналов может, например, являться составной частью устройств цифровой обработки сигналов, выполненных на основе программируемых логических интегральных схем, базовых матричных кристаллах или сигнальных процессоров.

Реально достижимые экспериментальные результаты, а именно энергетические потери, вносимые предложенным демодулятором, оценивались путем сравнения его помехоустойчивости с потенциально возможной. Для этого на его входе (по промежуточной частоте) задавалось SNR и снимались графики зависимости вероятности битовой ошибки от отношения энергии бита к спектральной плотности мощности шума Eb/No в интервале от минус 3 дБ до плюс 12 дБ в режимах ФМн-2 и ФМн-4. В этом случае скорость передачи информации и расстройка по частоте между гетеродинами (синтезаторами) приемника и передатчика были соизмеримыми и составляли 10 кГц, а частота дискретизации сигнала составляла 640 кГц. В результате проведения эксперимента энергетические потери в диапазоне SNR от 0 дБ до плюс 10 дБ имели малое значение, которое трудно оценимо измерительными приборами из-за их предельной точности. Энергетические потери в крайних точках отношения Eb/No составили не более 0,5 дБ. При низком отношении Eb/No это объясняется влиянием аддитивного шума на контур ФАПЧ, а при высоком - влиянием ПФМ и шумами квантования. Энергетические потери аналогичного демодулятора, выполненного по типовому решению и проверенного при той же скорости передачи информации и расстройке по частоте, составляли больше на 0,5 децибел при SNR, равном 0 дБ, и больше на 1,0 децибел при SNR, равном 10 дБ.

Таким образом, демодулятор фазоманипулированных сигналов позволяет получить снижение энергетических потерь при когерентной демодуляции ФМн сигналов путем компенсации на элементарных участках информационных посылок вращения фазы вектора сигнала, вызванного нестабильностью несущей частоты.

Литература

1. Патент RU №2019050, опубл. 30.08.1994 г.

2. Скляр Б. Цифровая связь, Москва · Санкт-Петербург · Киев, 2003, - 1104 с.

3. Патент RU №2336650, опубл. 20.10.2008 г.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО КОМПЕНСАЦИИ НЕСТАБИЛЬНОСТИ НЕСУЩЕЙ ЧАСТОТЫ ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2006 |

|

RU2336650C2 |

| ДЕМОДУЛЯТОР ДВУХПОЗИЦИОННЫХ ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2018 |

|

RU2699066C1 |

| УСТРОЙСТВО ВОССТАНОВЛЕНИЯ НЕСУЩЕЙ ЧАСТОТЫ ДЕМОДУЛЯТОРА СИГНАЛОВ КВАДРАТУРНОЙ АМПЛИТУДНОЙ МАНИПУЛЯЦИИ ВЫСОКИХ ПОРЯДКОВ | 2018 |

|

RU2693272C1 |

| ПОМЕХОЗАЩИЩЕННАЯ СИСТЕМА СВЯЗИ | 2004 |

|

RU2285344C2 |

| КОРРЕЛЯЦИОННЫЙ ПРИЕМНИК ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МОДУЛЯЦИЕЙ | 2014 |

|

RU2548010C1 |

| СПОСОБ ПРИЕМА ШУМОПОДОБНЫХ ЧАСТОТНО-МАНИПУЛИРОВАННЫХ СИГНАЛОВ С НЕПРЕРЫВНОЙ ФАЗОЙ | 2006 |

|

RU2323536C1 |

| Демодулятор псевдослучайных сигналов с относительной фазовой модуляцией | 2014 |

|

RU2625529C2 |

| УСТРОЙСТВО ДЛЯ ВОССТАНОВЛЕНИЯ НЕСУЩЕЙ ЧАСТОТЫ СИГНАЛОВ С АМПЛИТУДНО-ФАЗОВОЙ МАНИПУЛЯЦИЕЙ | 2004 |

|

RU2276838C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ ПРИЕМНИКА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2007 |

|

RU2357359C2 |

| УСТРОЙСТВО КОМПЕНСАЦИИ СТРУКТУРНЫХ ПОМЕХ | 2013 |

|

RU2534221C1 |

Изобретение относится к радиотехнике и предназначено для использования при когерентной демодуляции сигналов с многопозиционной фазовой манипуляцией. Технический результат заключается в снижении энергетических потерь при когерентной демодуляции фазоманипулированных сигналов, который достигается путем компенсации вращения фазы вектора сигнала, вызванного нестабильностью несущей частоты, на элементарных участках информационных посылок в цифровой форме линейными элементами. Устройство содержит два перемножителя (1, 2), первые входы которых объединены и являются входом устройства, фазовращатель (3), синтезатор частоты (6), опорный генератор (9), два аналого-цифровых преобразователя (4, 5), комплексный перемножитель (7), синусно-косинусный функциональный преобразователь (8), синтезатор фазы (11), первый и второй согласованные фильтры (10, 12), вычислитель двойного арктангенса (13), элемент задержки (14), блок вычитания (15), первый, второй и третий сумматоры элементов (16, 17, 18), вычислитель арктангенса (19), умножитель-делитель (20), первый и второй сумматоры (21, 23), интегратор (24), вычислитель дисперсии фазы (22), компаратор (25), блок поиска (26), выходы первого и второго сумматоров элементов (16, 17) являются выходами демодулятора. 1 з.п. ф-лы, 4 ил.

1. Демодулятор фазоманипулированных сигналов, содержащий первый и второй перемножители, фазовращатель, первый и второй аналого-цифровые преобразователи, опорный генератор, синтезатор частоты, вычислитель двойного арктангенса, умножитель-делитель, блок вычитания, синтезатор фазы, причем первые входы первого и второго перемножителей объединены и являются входом устройства, выход фазовращателя соединен со вторым входом первого перемножителя, а второй вход второго перемножителя объединен с входом фазовращателя, выход опорного генератора соединен с входом синтезатора частоты, выход которого соединен с объединенными вторым входом второго перемножителя и входом фазовращателя, выходы первого и второго перемножителей соединены с входами соответственно первого и второго аналого-цифровых преобразователей, выход вычислителя двойного арктангенса соединен с первым входом блока вычитания, отличающийся тем, что дополнительно содержит комплексный перемножитель, синусно-косинусный функциональный преобразователь, первый и второй согласованные фильтры, элемент задержки, первый, второй и третий сумматоры элементов, вычислитель арктангенса, первый и второй сумматоры, вычислитель дисперсии фазы, интегратор, компаратор, причем выходы первого и второго аналого-цифровых преобразователей соединены соответственно с первым и вторым входами комплексного перемножителя, первый и второй выходы синусно-косинусного функционального преобразователя соединены соответственно с третьим и четвертым входами комплексного перемножителя, первый и второй выходы комплексного перемножителя соединены соответственно с входом первого согласованного фильтра и с входом второго согласованного фильтра, выход первого согласованного фильтра соединен с первым входом вычислителя двойного арктангенса и с входом первого сумматора элементов, выход второго согласованного фильтра соединен со вторым входом вычислителя двойного арктангенса и с входом второго сумматора элементов, выход вычислителя двойного арктангенса также соединен с входом элемента задержки, выход элемента задержки соединен со вторым входом блока вычитания, выход блока вычитания соединен с входом третьего сумматора элементов, выходы первого и второго сумматоров элементов являются выходами демодулятора и соединены соответственно с первым и вторым входами вычислителя арктангенса, при этом выход вычислителя арктангенса соединен с первым входом умножителя-делителя, выход которого соединен с первыми входами первого и второго сумматоров и входом вычислителя дисперсии фазы, выход третьего сумматора элементов соединен со вторым входом первого сумматора, выход которого соединен с входом интегратора, выход интегратора соединен со вторым входом второго сумматора, выход которого соединен с входом синтезатора фазы, выход синтезатора фазы соединен со входом синусно-косинусного функционального преобразователя, выход вычислителя дисперсии фазы соединен с первым входом компаратора, выход которого соединен с входом управления третьего сумматора элементов, вторые входы умножителя-делителя и компаратора объединены и являются управляющим входом демодулятора.

2. Демодулятор фазоманипулированных сигналов по п.1, отличающийся тем, что дополнительно содержит блок поиска, вход которого соединен с выходом компаратора, а выход блока поиска соединен с входом данных интегратора.

| УСТРОЙСТВО КОМПЕНСАЦИИ НЕСТАБИЛЬНОСТИ НЕСУЩЕЙ ЧАСТОТЫ ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2006 |

|

RU2336650C2 |

| ДЕМОДУЛЯТОР СИГНАЛОВ ЧЕТЫРЕХПОЗИЦИОННОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 1990 |

|

RU2019050C1 |

| ЕР 1107531 А2, 13.06.2001 | |||

| US 5940451 А, 17.08.1999. | |||

Авторы

Даты

2010-06-27—Публикация

2008-12-23—Подача