Изобретение относится к архитектуре модуля центрального процессора (далее по тексту модуль ЦП) промышленного контроллера с программируемой логикой (далее по тексту ПЛК). ПЛК является вычислительной и управляющей единицей в автоматизированных системах управления технологическими процессами (АСУ ТП).

Быстрый рост систем управления, используемых в областях (промышленность, медицина, автомобильный и железнодорожный транспорт), где их выход из строя может привести к опасным ситуациям, которые приводят к травмированию или смерти людей и причинению вреда окружающей среде привел к развитию серии международных стандартов IEC 61508 (Functional safety of electrical /electronic /programmable electronic safety related systems) и идентичных им национальных стандартов ГОСТ Р МЭК 61508 «Функциональная безопасность систем электрических, электронных, программируемых электронных (далее Э/Э/ПЭ систем), связанных с безопасностью». В международном стандарте IEC 61508 вводятся понятия о четырех уровнях безопасного выполнения функции безопасности, которые должны быть реализованы Э/Э/ПЭ системой. Данные уровни именуются как уровни полноты безопасности (SIL), где самый низкий - 1, а самый высокий - 4.

Для того чтобы обеспечить функциональную безопасность Э/Э/ПЭ систем применяют микропроцессорные системы. Идея этих микропроцессорных систем основывается на аппаратной избыточности. Так, известны микропроцессорные системы, в которых два параллельно работающих вычислительных устройства (например, процессора) осуществляют взаимный контроль, заключающийся в сравнении их результатов обработки данных. Решения, где избыточный процессор взаимодействует с основным процессором, известны из следующих патентных источников:

- US 9,244,454 В2 под названием "Система управления для контроля критически безопасных и критически небезопасных процессов", компания ABB AG;

- US 7,715,932 В2 под названием "Способ и устройство для управления критичным для безопасности процессом", компания Pilz GmbH&Co;

- US 6,832,343 В2 под названием "Устройство для контроля критично важного процесса", компания Pilz GmbH&Co;

- WO 2015/113994 А1 под названием "Способ и устройство для безопасного отключения электрической нагрузки", компания Pilz GmbH&Co. KG;

- US 9,098,074 B2 под названием "Система управления, связанная с безопасностью, и способ для управления автоматизированной системой", компания Pilz GmbH&Co. KG.

Известны микропроцессорные системы, в которых результаты двух параллельно работающих вычислительных устройств сравнивает третье вычислительное устройство. Так, известно решение, в котором для обеспечения функциональной безопасности микропроцессорная система содержит центральный процессор, избыточный процессор и третий процессор, предназначенный для сравнения и выявления несоответствия в результатах первых двух процессоров (заявка на изобретение RU 94013455 А1, «Микропроцессорная система обеспечения безопасности, применимая, в частности, в области железнодорожного транспорта»). Известная микропроцессорная система содержит по меньшей мере два работающих параллельно процессора, выполняющих одну и ту же прикладную программу. Одни и те же входные данные подаются на входы этих процессоров. Результаты обработки каждый из процессоров направляет в третий процессор сравнения. Процессор сравнения сравнивает эти результаты. Если это сравнение корректно, процессор сравнения формирует сигнатуру, которую подает на динамический контроллер. При получении сигнатуры, являющейся признаком нормальной работы процессора сравнения, динамический контроллер санкционирует общую передачу выходных данных процессорами. Реально используются только выходные данные одного из процессоров. Кроме этого каждый из процессоров выполняет самодиагностику, результаты которой направляет в процессор сравнения. Возможны разные варианты исполнения микропроцессорной системы, например, от использования одинаковых программных средств, размещенных на двух одинаковых аппаратных средствах, до использования двух разных программных средств, размещенных на двух разных аппаратных средствах.

Аналогичное решение в области промышленной автоматизации известно из патента US 9,696,692 В2. В этом патенте описана система управления в ПЛК, предназначенном для управления промышленным оборудованием. Промышленное оборудование может представлять опасность для людей в случае возникновения отказа в системе управления. Поэтому необходимо обеспечить быстрое обнаружения ошибки в системе управления и исправление данной ошибки. Система управления включает в себя «первичный процесс управления», «вторичный процесс управления» и «процесс вывода». «Первичный процесс управления» и «вторичный процесс управления» сконфигурированы для обработки одних и тех же входных данных в одной или нескольких программах управления. Программы в «первичном процессе управления» и «вторичном процессе управления» запускаются одновременно. Во время нормальной работы «процесс вывода» сконфигурирован для управления промышленным оборудованием посредством использования сигналов управления и данных, принятых из «первичного процесса управления», которые затем передаются в сеть и далее к промышленному оборудованию. «Вторичный процесс управления» периодически генерирует вторичное значение контроля данных, в то время как «первичный процесс управления» периодически генерирует первичное значение контроля данных. Это могут быть значения циклического избыточного кода (CRC). Главное, чтобы эти значения проверки данных были компактны (с точки зрения количества бит и байтов), которые можно быстро сравнить, чтобы определить состояние процессов управления. «Процесс вывода» сравнивает эти два значения для обнаружения отказа в «первичном процессе управления». Если значения CRC не совпадают, вероятно, произошел отказ в «первичном процессе управления», и «процесс вывода» может переключить управление промышленным оборудованием на «вторичный процесс управления» или предпринять меры, направленные на аварийное выключение промышленного оборудования.

Решения аппаратной избыточности, описанные выше, используются для обеспечения функциональной безопасности так же и в микропроцессорных технологиях, поскольку современные микропроцессоры или микроконтроллеры могут включать в себя множество ядер на одном кристалле (многоядерные варианты исполнения). Такие решения описаны в следующих патентах:

- ЕР 1,973,017 А2 под названием «Программируемый логический контроллер, ориентированный на безопасность», компания ABB AG;

ЕР 2,237,118 А1 «Система безопасности для обеспечения безошибочного управления электрическими устройствами и предохранительным устройством», группа компаний

Robert Bosch GMBH.

В последнее время появились микроконтроллеры серии Hercules™ - микроконтроллеры реального времени для решения задач обеспечения функциональной безопасности. Микроконтроллеры серии Hercules™ описаны в следующих источниках информации [1],[2],[3],[4],[5]. Микроконтроллеры серии Hercules™ соответствуют уровню полноты безопасности SIL-3. Кардинальное отличие такого микроконтроллера с высоким уровнем функциональной безопасности от ранее известных микроконтроллеров заключается в том, что для диагностирования отказов помимо программной самодиагностики в нем реализованы еще и аппаратные механизмы самодиагностики, реализованные на кристалле микроконтроллера. В микроконтроллере используется концепция архитектуры безопасности, которая называется «островок безопасности». Она заключается в том, что для ряда ключевых элементов выделяются непрерывно работающие аппаратно реализованные механизмы обеспечения безопасности. Этот набор ключевых элементов включает в себя устройство питания / тактирования / сброса, ядро, flash-память, ОЗУ и соответствующие цепи взаимосвязи. Реализация аппаратного тестирования этих элементов дает уверенность в том, что эти элементы работают правильно. В этом случае можно использовать программное обеспечение, исполняемое на этих элементах, для обеспечения программно-реализованной диагностики других элементов, таких как периферийные устройства. Аппаратная диагностика ключевых элементов в микроконтроллерах Hercules™ позволила сократить объем программного обеспечения, связанного с диагностикой на 30%.

Микроконтроллер серии Hercules™ имеет два ядра и модуль сравнения, который сравнивает результаты вычислений ядер. Первое ядро функциональное. Второе ядро и модуль сравнения предназначены для контроля работы функционального ядра. Одни и те же входные данные подаются на ядра одинаковой архитектуры. Ядра работают параллельно со сдвигом во времени и с одним и тем же встроенным программным обеспечением. Ядра, с одной и той же логикой, должны генерировать одинаковые результаты вычислений. Если результаты вычислений ядер не равны, модуль сравнения информирует об этом модуль сигнализации об ошибках, который классифицирует данную ситуацию как отказ. В этом случае модуль прерывания микроконтроллера генерирует аппаратное прерывание, и выполнение программного обеспечения останавливается. Кристалл контролирующего ядра физически расположен зеркально и развернут относительно функционального ядра. Реализована встроенная самопроверка логики, которая обеспечивает охват диагностикой ядер на уровне транзисторов при включении питания или в ходе периодических интервалов проверки во время штатной работы. Использование такого микроконтроллера в устройствах для целей обеспечения высокого уровня их функциональной безопасности позволяет уйти от аппаратной избыточности (использования двух или трех вычислительных устройств). Изготовитель такого микроконтроллера заявляет о возможности использования такого микроконтроллера в ПЛК.

Однако, при разработке нами нового ПЛК МФК5000, мы столкнулись с проблемой, что на сегодняшний день микроконтроллеры, имеющие уровень полноты безопасности SIL-3, имеют малую производительность. К тому же из-за постоянно проводимых ими мер самодиагностики такой микроконтроллер имеет низкую скорость работы. Разрабатываемый нами ПЛК должен обеспечивать управление объектом, где количество сигналов может достигать пяти тысяч. При этом необходимо обеспечить быстродействие и высокий уровень функциональной безопасности. Следовательно, таким же требованиям должен отвечать и модуль ЦП.

При разработке ПЛК некоторые производители отделяют модуль ЦП (так называемый модуль ЦП безопасности), управляющий важными для безопасного состояния объекта управления процессами, от модуля ЦП, управляющего так называемыми некритически важными для безопасного состояния объекта управления процессами. Однако, часто оказывается трудным четко разделить критически важные для безопасности функции и некритические важные для безопасности функции. Поэтому, при разработке ПЛК нами разрабатывался единый модуль ЦП, в котором происходит обработка сигналов со всех датчиков объекта управления. Для обеспечения функциональной безопасности модуля ЦП предложена микропроцессорная система из двух микропроцессоров, микроконтроллера с высоким уровнем функциональной безопасности (назовем его далее по тексту микроконтроллер безопасности) и ПЛИС с контроллером шины. В нашем случае микроконтроллер безопасности используется только для целей контроля работы других высокопроизводительных и высокоскоростных вычислительных устройств микропроцессорной системы модуля ЦП и для регулирования (т.е. запрета или разрешения) выдачи выходных данных из модуля ЦП.

Уровень полноты безопасности (SIL) для Э/Э/ПЭ системы зависит от частоты (интенсивности) отказов различных категорий. В основном для уровня полноты безопасности Э/Э/ПЭ системы имеет значение (мера отказов) интенсивности необнаруженных опасных отказов (смотри Таблицу 3 в ГОСТ Р МЭК 61508-1-2012, Функциональная безопасность систем электрических, электронных, программируемых электронных, связанных с безопасностью. Часть 1. Общие требования). Это означает, что чем ниже интенсивность опасных необнаруженных отказов, тем более высокий уровень полноты безопасности (SIL) может быть достигнут для данного устройства. Применительно к системам, находящимся в нормальном режиме во включенном состоянии (например, системам противоаварийной защиты), безопасными считаются отказы, которые приводят к ошибочному отключению выхода и остановке контролируемого технологического процесса (ложное срабатывание). Опасными отказами, наоборот, являются отказы, препятствующие отключению выхода и остановке процесса при возникновении аварийной ситуации. «Обнаруженный опасный отказ считают фактически безопасным, что позволяет определить отношение между фактически безопасными отказами (т.е. любыми обнаруженными безопасными, необнаруженными безопасными или обнаруженными опасными отказами) и необнаруженными опасными отказами» (ГОСТ Р МЭК 61508-6-2012, Функциональная безопасность систем электрических, электронных, программируемых электронных, связанных с безопасностью. Часть 6. Руководство по применению ГОСТР МЭК 61508-2 и ГОСТ Р МЭК 61508-3, Приложение С (справочное). Расчет охвата диагностикой и доли безопасных отказов, пункт d). Следовательно, диагностические тесты, позволяющие обнаружить опасный отказ, могут обеспечить значительные преимущества в достижении функциональной безопасности Э/Э/ПЭ системы, связанной с безопасностью. При этом, при оценке достигаемой меры отказов для функции безопасности должен учитываться охват диагностикой каждого элемента в Э/Э/ПЭ системе, связанной с безопасностью (ГОСТ Р МЭК 61508-2-2012 Функциональная безопасность систем электрических, электронных, программируемых электронных, связанных с безопасностью. Часть 2. Требования к системам. Приложение С (обязательное). Охват диагностикой и доля безопасных отказов).

Из сказанного выше следует, что чем выше охват диагностикой элемента программируемой электронной системы, тем выше вероятность обнаружить опасный отказ, который при обнаружении становится безопасным отказом. Это приводит к уменьшению меры необнаруженных опасных отказов и, следовательно, к увеличению уровня полноты безопасности (SIL) как самого элемента программируемой электронной системы, так и самой программируемой электронной системы в целом.

В нашем случае, введение в микропроцессорную систему модуля ЦП микроконтроллера безопасности, в котором помимо программной самодиагностики обеспечивается высокий уровень аппаратной самодиагностики, приводит к тому, что увеличивается уровень полноты безопасности микропроцессорной системы в целом. Это и является отличием от аналогов (RU 94013455 А1 и US 9,696,692 В2).

В качестве прототипа принят известный модуль ЦП промышленного контроллера (Руководство на ПЛК безопасности Quantum №33003879 от 06/2007, стр. 33-38 раздел «Модуль ЦП безопасности», компания Schneider Electric, http://schneider.nt-rt.ru/images/manuals/33003879RU.pdf), как совпадающий по назначению и имеющий признаки, совпадающие с существенными признаками изобретения. В состав известного модуля ЦП входят два различных процессора - модель Intel Pentium и- прикладной процессор. Каждый из этих процессоров независимо друг от друга выполняет расчеты, и по завершению каждого цикла каждый из процессоров сравнивает свой результат с результатом другого процессора. При обнаружении ошибки или при несоответствии результатов любой из процессоров может «отключить систему, т.е. перевести ее в безопасное состояние». Работа такой микропроцессорной системы, состоящей из двух разных процессоров, для которых независимо друг от друга разрабатывается два исполняемых кода, позволяет выявить систематические отказы из-за ошибок в исходных текстах программ и случайные отказы, возникающие при работе модуля ЦП. Следует упомянуть о том, что модуль ЦП ПЛК безопасности серии Quantum имеет сертификат соответствия уровню полноты безопасности SIL-2 и может применяться в областях, где обесточенное состояние считается безопасным состоянием, например в системах аварийной остановки.

Целью изобретения является обеспечение высокого уровня функциональной безопасности модуля центрального процессора промышленного контроллера.

Технический результат в предлагаемом изобретении достигается тем, что модуль ЦП промышленного контроллера содержит:

- центральный микропроцессор, предназначенный для выполнения задачи прикладной программы, в результате которой обрабатываются входные данные от датчиков и результатом обработки которых являются выходные данные, предназначенные для управления исполнительными механизмами;

- дополнительный микропроцессор с архитектурой ядра отличной от архитектуры ядра центрального микропроцессора и предназначенный для выполнения точно такой же задачи с точно такими же входными данными от датчиков, что и в центральном микропроцессоре;

- программируемую логическую интегральную схему с контроллером шины, предназначенным для обмена данными по шине между модулем центрального процессора и модулями ввода и/или вывода промышленного контроллера;

- микроконтроллер безопасности, имеющий два ядра, одно из которых функциональное, а другое предназначено для контроля работы функционального ядра, и модуль сравнения, который предназначен для сравнения результатов вычислений с работающих параллельно с одним и тем же программным обеспечением и одними и теми же данными двух ядер, и предназначенный для сравнения результатов обработки из центрального микропроцессора и из дополнительного микропроцессора, и предназначенный для контроля времени выполнения задачи каждым из микропроцессоров, которое должно находиться в заданном интервале времени, который определяется исходя из объема обрабатываемых в задаче данных, и имеющий возможность разрешать контроллеру шины передачу выходных данных в шину, в случае если соблюдено равенство результатов вычислений ядер микроконтроллера безопасности, и соблюдено равенство результатов обработки из центрального и из дополнительного микропроцессоров, и время выполнения задачи каждым из микропроцессоров находится в заданном интервале времени.

Для последующего описания возможности осуществления заявленного изобретения приведены следующие фигуры:

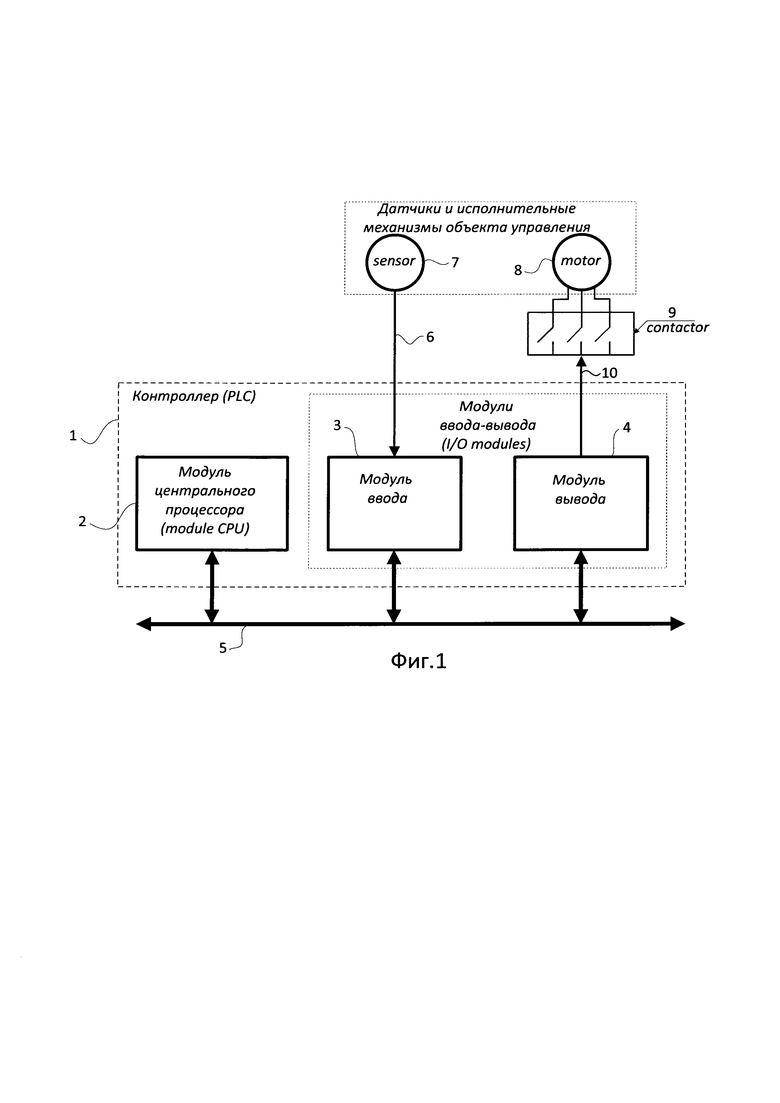

фиг. 1 - структурная схема ПЛК, датчика, контактора и двигателя;

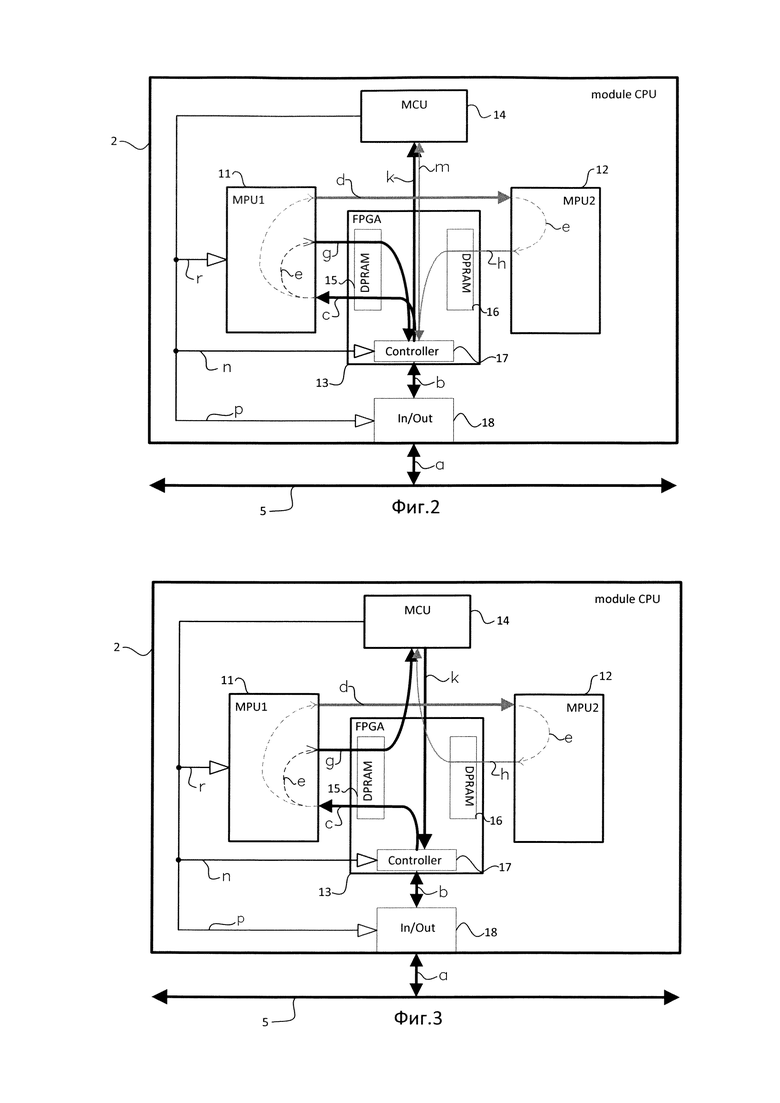

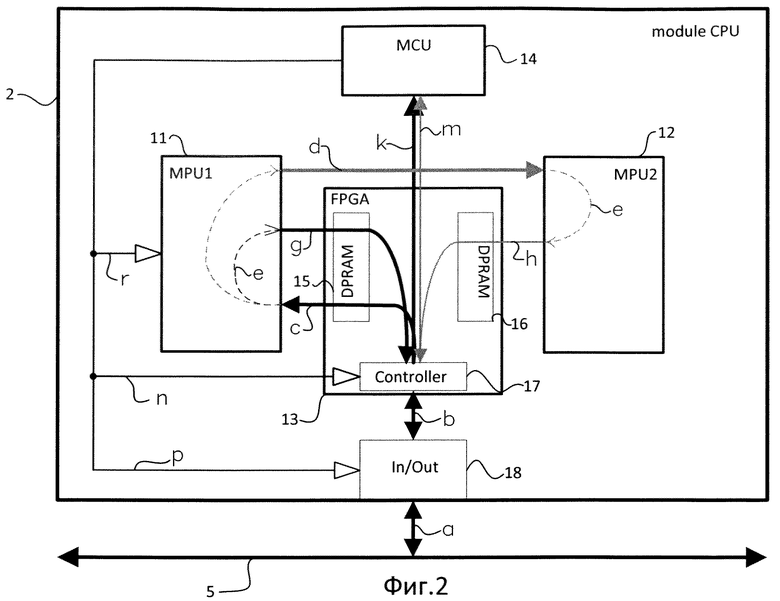

фиг. 2 и фиг. 3 - структурная схема модуля ЦП.

Прилагаемые фигуры, показывающие предпочтительное решение для осуществления настоящего изобретения, приведены в качестве иллюстрации, а не для ограничения раскрытия информации, и могут быть изменены в объеме прилагаемой формулы изобретения вместе с ее полным объемом эквивалентов.

При описании работы модуля ЦП следует оговорить следующие понятия и условия, используемые в данной заявке:

- Под функциональной безопасностью устройства (модуля ЦП) в данной заявке понимается безопасность, которая зависит от правильности функционирования устройства, основанного на электрической и/или электронной, и/или программируемой электронной технологии.

В АСУ ТП под «безопасным состоянием» понимается такое состояние выходов ПЛК, при котором подключенные к ним исполнительные механизмы находятся в состоянии наиболее безопасном для объекта управления, а именно состоянии, не приводящем к поломке объекта управления.

- В данной заявке описана работа нерезервированного модуля ЦП, неисправность в работе которого приведет к исчезновению (отключению) сигналов на выходе ПЛК. Это приведет к тому, что контакты контактора будут приведены в «безопасное состояние», т.е. контакты будут разомкнуты, при этом регулирующие и отсечные клапаны займут безопасное для технологического процесса положение в соответствии с требованиями технологического регламента, а двигатели будут остановлены.

- Модуль ЦП предназначен для обработки входных данных, получаемых от контрольно-измерительных приборов (датчиков), включая прием информации от других подсистем автоматизированного управления, для выработки управляющих воздействий (выходных данных) согласно запрограммированным алгоритмам прикладной (технологической) программы и для передачи этих воздействий на исполнительные механизмы. Работа ПЛК состоит из постоянного повторения последовательности действий, входящих в рабочий цикл. Следовательно, в модуле ЦП происходит циклически повторяющееся выполнение прикладной программы. Блоки алгоритмов прикладной программы включают в себя блоки обработки аналоговых, дискретных и цифровых сигналов, блоки управления арматурой и механизмами,. блоки автоматического регулирования, блоки автоматического логического управления, блоки технологической защиты и защитных блокировок. Поэтому прикладная программа реализована в виде ряда независимых задач. Работа модуля ЦП в данной заявке описана в рамках выполнения одной из ряда задач прикладной программы, например задачи, в которой выполняется алгоритм технологических защит и защитных блокировок.

Следует учитывать, что прикладная программа модуля ЦП может включать в себя и задачу, в которой обрабатываются входные данные с так называемого некритически важного для безопасного состояния объекта управления процесса. Такая задача выполняется в центральном микропроцессоре, но не выполняются в дополнительном микропроцессоре, так как не требуется проверка достоверности результатов обработки. Поступление входных данных для такой задачи и выдача выходных данных осуществляется через интерфейсные устройства, не расположенные на ПЛИС. Но такая задача не являются предметом рассмотрения данной заявки.

Промышленный контроллер 1 (PLC) (фиг. 1) содержит нерезервированный модуль ЦП 2 (module CPU). Модули ввода 3 и вывода 4 (I/O modules) осуществляют общение с модулем ЦП 2 по последовательной шине 5. Модуль 3 ввода получает по измерительной шине 6 сигналы с датчика 7. Для функций защит и блокировок датчик 7 контролирует важный для безопасного состояния объекта управления параметр. Включение или отключение исполнительного механизма, например двигателя 8, осуществляется через контактор 9. Замыкание или размыкание контактных групп контактора 9 зависит от сигнала в шине управления 10 модуля 4 вывода. При диагностировании отказа в любом из вычислительных устройств модуля ЦП 2 выходы модуля 4 вывода примут состояние как при отключенном питании. Это приведет к размыканию контактов контактора 9, прекращению подачи питания на двигатель 8 и остановке двигателя.

Модуль ЦП 2 (module CPU) (фиг. 2 и фиг. 3) состоит из центрального микропроцессора 11 (MPU1), дополнительного микропроцессора 12 (MPU2), ПЛИС 13 (FPGA) и микроконтроллера 14 безопасности (MCU). Внутри ПЛИС организованы области двухпортовой оперативной памяти 15 и 16 (DPRAM) и контроллер 17 шины (controller). Контроллер 17 шины поддерживает обмен данными по шине 5 между модулем ЦП и модулями ввода и/или вывода. На границе модуля ЦП 2 и шины 5 показан физический уровень 18 (In/Out) интерфейса.

Центральный микропроцессор 11 предназначен для выполнения прикладной (технологической) программы модуля ЦП. Для описания работы модуля ЦП работа центрального микропроцессора 11 определена в рамках решения им одной независимой задачи. В рамках этой задачи обрабатываются входные данные от датчика (датчиков), а результатом обработки являются выходные данные для управления исполнительным механизмом (механизмами).

Дополнительный микропроцессор 12 предназначен для выполнения прикладной (технологической) программы модуля ЦП с целью проверки правильности работы центрального микропроцессора 11. Дополнительный микропроцессор 12 выполнен с архитектурой ядра (ядер), отличной от архитектуры ядра (ядер) центрального микропроцессора 11. Для описания работы модуля ЦП 2 работа дополнительного микропроцессора определена как решение им точно такой же задачи, какую решает и центральный микропроцессор 11 с точно такими же входными данными.

В центральном микропроцессоре и дополнительном микропроцессоре для решения одинаковых задач могут быть использованы разные алгоритмы, разные исходные тексты прикладной программы (разные машинные коды). Прикладная программа в центральном микропроцессоре и прикладная программа в дополнительном микропроцессоре могут работать под управлением одинаковых или разных операционных систем, или вообще без операционных систем.

Микроконтроллер 14 безопасности предназначен для регулирования передачи; данных из модуля ЦП 2 в шину 5. Микроконтроллер 14 безопасности либо разрешает контроллеру 17 шины передачу данных из модуля ЦП 2, либо не дает этого разрешения. Это зависит от результатов осуществляемых им контрольных проверок и диагностик.

К таким контрольным проверкам и диагностикам следует отнести:

1. Микроконтроллер 14 безопасности сравнивает результаты обработки, полученные в результате решения задачи в центральном микропроцессоре 11 и в дополнительном микропроцессоре 12. Следует отметить, что результатами обработки могут быть, как выходные данные, так и значения проверки выходных данных, например циклические избыточные коды CRC, так и то и другое. В предпочтительном варианте микроконтроллер безопасности сравнивает значения проверки выходных данных (CRC).

2. Микроконтроллер 14 безопасности контролирует время выполнения задачи как центральным, так и дополнительным микропроцессорами. Время выполнения задачи должно находиться в заданном интервале времени, который определяют исходя из объема обрабатываемых в задаче данных.

3. Микроконтроллер 14 безопасности для увеличения уровня функциональной безопасности проводит периодически исполняемый аппаратный контроль (диагностику) работы своего функционального ядра. Для этого микроконтроллер 14 безопасности имеет второе контролирующее ядро и модуль сравнения, предназначенный для сравнения результатов вычислений функционального и контролирующего ядер. Одни и те же входные данные подаются на ядра одинаковой архитектуры. Ядра работают параллельно со сдвигом во времени и с одним и тем же встроенным программным обеспечением. Ядра с одной и той же логикой должны генерировать одинаковые результаты вычислений. Так же микроконтроллер 14 безопасности имеет модуль сигнализации об ошибках, который сам по себе не влияет на общую функцию устройства и служит ограниченным целям классификации ошибок по критичности. Так же микроконтроллер 14 безопасности имеет контроллер прерываний, который реализует возможность последовательной обработки запросов на прерывание от разных устройств, с учетом приоритетов.

Микроконтроллер 14 безопасности дает разрешение контроллеру 17 шины на передачу выходных данных в шину 5 при одновременном выполнении следующих условий:

- если результаты обработки в центральном и в дополнительном микропроцессорах равны;

- если время выполнения задачи каждым из микропроцессоров находится в заданном интервале времени (т.е. в заданном для них обоих интервале времени или в заданном для каждого из них интервале времени);

- если результаты вычислений функционального и контролирующего ядер равны.

Микроконтроллер 14 безопасности не дает разрешения на передачу выходных данных из модуля ЦП 2 в шину 5 при невыполнении любого из выше перечисленных условий.

Невыполнение первых двух условий считается отказом в работе центрального или дополнительного микропроцессоров.

Невыполнение третьего условия модуль сигнализации об ошибках классифицирует как отказ в работе микроконтроллера 14 безопасности. В этом случае контроллер прерывания генерирует аппаратное прерывание, и выполнение программного обеспечения микроконтроллера 14 безопасности останавливается.

Дополнительно микроконтроллер 14 безопасности проводит программную самодиагностику и принимает результаты периодически исполняемых программных диагностик из центрального микропроцессора 11 и дополнительного микропроцессора 12. Микроконтроллер 14 безопасности дает разрешение контроллеру 17 шины на передачу выходных данных в шину 5, если результаты программных самодиагностик всех вычислительных устройств положительные.

Вместо микроконтроллера 14 безопасности может быть использован микропроцессор, конструктивные и программные возможности которого позволяют ему выполнить перечисленные далее функции.

Контроллер 17 шины, сформированный на отдельном устройстве, например в ПЛИС 13, а не в микропроцессорах и не в микроконтроллере безопасности является граничным элементом который не осуществляет передачу выходных данных в шину 5 до тех пор, пока не получит разрешения от микроконтроллера 14 безопасности, работа которого устроена так, чтобы обеспечивать собственную функциональную безопасность. К тому же при выявлении микроконтроллером 14 безопасности неравенства результатов обработки из двух микропроцессоров не ясно, в каком из них произошел отказ. Следовательно, направление в микропроцессоры сигнала сброса RESET может и не привести к прекращению выполнения инструкций в одном из них, а именно в отказавшем микропроцессоре. В этом случае наличие отдельного устройства ПЛИС с контроллером шины обеспечивает дополнительную защиту для того, чтобы не допустить выдачи выходных данных в шину.

На фиг. 2 стрелками показана передача данных в модуле ЦП для того, чтобы осуществить проверку равенства результатов обработки из центрального и из дополнительного микропроцессоров (для обозначения последовательности действий по передаче данных использованы буквы от "а" до "m"). Управляющие сигналы показаны стрелками, обозначенными

буквами r, n, р.

Контроллер 17 шины рассылает по шине 5 в модули ввода пакеты заданий на чтение сигналов с датчиков. Модули ввода отвечают пакетами статуса и пакетами данных, которые передаются (действие а и действие b) с шины через физический уровень 18 (In/Out) интерфейса в контроллер 17 шины, которые всегда открыты на вход данных с шины 5. Далее центральный микропроцессор 11 забирает (действие с) входные данные из контроллера 17 шины и передает (действие d) точно такой же массив входных данных в дополнительный микропроцессор 12. После поступления массива входных данных в дополнительный микропроцессор 12 в обоих микропроцессорах начинается выполнение (действия е) одной и той же задачи прикладной программы, в которой обрабатываются входные данные, и результатом обработки которых являются в центральном микропроцессоре 11 (выходные данные 1 и их CRC 1), а в дополнительном микропроцессоре 12 (выходные данные 2 и их CRC 2). Результаты обработки из микропроцессоров передаются в контроллер 17 шины. В рассматриваемом варианте предлагается из центрального микропроцессора 11 в контроллер 17 шины передавать (действие g) данные (данные 1) и их циклические избыточные коды (CRC 1), а из дополнительного микропроцессора 12 в контроллер 17 шины передавать (действие h) только циклические избыточные коды (CRC 2).

Микроконтроллер 14 безопасности держит контроллер 17 шины в состоянии запрета передачи выходных данных из модуля ЦП 2 в шину 5. Каждый из микропроцессоров 11 и 12 сигнализирует микроконтроллеру 14 безопасности, что выходные данные записаны в контроллер 17 шины. Получив сигналы о завершении записи выходных данных, микроконтроллер 14 безопасности читает (действие k) из контроллера 17 шины данные 1, записанные центральным микропроцессором 11, и читает (действие m) значения циклических избыточных кодов CRC 2, записанные дополнительным микропроцессором 12. Затем микроконтроллер 14 безопасности заново вычисляет значения циклических избыточных кодов (CRC 3) для данных 1, обработкой которых занимался центральный микропроцессор 11, и сравнивает их со значением циклических избыточных кодов (CRC 2) для данных 2, обработкой которых занимался дополнительный микропроцессор 12. Предпочтительно, если микроконтроллер 14 безопасности будет сравнивать циклические избыточные коды CRC, а не выходные данные, так как эти значения компактны (с точки зрения количества бит и байтов) и их можно сравнить быстро. Если значения проверки циклических избыточных кодов (CRC 3) и (CRC 2) равны, микроконтроллер 14 безопасности санкционирует (разрешает) (действие n) передачу выходных данных контроллеру 17 шины и тот передает в шину 5 уже имеющиеся у него выходные данные 1 с циклическими избыточными кодами (CRC 1). Затем контроллер 17 шины извещает микроконтроллер 14 безопасности об окончании передачи данных в шину 5, и микроконтроллер 14 безопасности снова переводит контроллер 17 шины в состояние запрета передачи данных из модуля ЦП 2 в шину 5. Если значения циклических избыточных кодов (CRC 3) и (CRC 2) не равны, значит, произошел отказ в одном из микропроцессоров (центральном или дополнительном). В этом случае микроконтроллер 14 не даст разрешения на передачу данных контроллеру 17 шины. К тому же микроконтроллер 14 безопасности может сформировать сигнал RESET, который направит (действие r) в центральный микропроцессор 11 для того, чтобы центральный микропроцессор 11 прекратил выполнение инструкций. К тому же микроконтроллер 14 безопасности может отправить запрещающий сигнал на физический уровень интерфейса 18 (действие р), где разомкнется канал передачи выходных данных в шину 5.

Представленная на фиг. 2 последовательность действий для проверки равенства результатов обработки в центральном и в дополнительном микропроцессорах является предпочтительной, но не обязательной. Так, на фиг. 3 показана другая последовательность действий. Данная последовательность действий отличается от представленной на фиг. 2 тем, что после выполнения (действия е) одной и той же задачи прикладной программы центральным и дополнительным микропроцессорами, центральный микропроцессор 11 направляет (действие g) в микроконтроллер 14 безопасности свои выходные данные 1, а дополнительный микропроцессор 12 направляет (действие h) в микроконтроллер 14 безопасности только значения циклических избыточных кодов (CRC 2) своих выходных данных 2. Затем микроконтроллер 14 безопасности вычисляет значения циклических избыточных кодов (CRC 3) выходных данных 1 и сравнивает значения циклических избыточных кодов (CRC 3) для данных 1 со значением циклических избыточных кодов (CRC 2) для данных 2. Если значения проверки циклических избыточных кодов (CRC 3) и (CRC 2) равны, микроконтроллер 14 безопасности направляет (действие k) полученные им из центрального микропроцессора 11 выходные данные 1 и значения их циклических избыточных кодов (CRC 3) в контроллер 17 шины и разрешает (действие n) контроллеру 17 шины передачу данных в шину 5.

Дополнительно микроконтроллер 14 безопасности программно контролирует время выполнения задачи каждым из микропроцессоров. Для этого центральный микропроцессор 11 и дополнительный микропроцессор 12 сигнализируют в микроконтроллер 14 безопасности об окончании выполнения задачи прикладной программы. Время выполнения задачи должно находиться в заданном интервале времени (временном окне), определяемом для каждой задачи исходя из объема обрабатываемых/пересылаемых в ней данных. Может быть задан как единый интервал времени для двух микропроцессоров, так и два интервала, каждый из которых соответствует своему микропроцессору. Если время выполнения задачи одним из микропроцессоров находится вне заданного для него интервала, это воспринимается как отказ. В этом случае микроконтроллер 14 безопасности не даст разрешения контроллеру 17 шины на передачу выходных данных в шину 5. К тому же микроконтроллер 14 безопасности может сформировать (действие r) сигнал RESET, который направит в центральный микропроцессор 11, который прекратит выполнение инструкций. К тому же микроконтроллер 14 безопасности может отправить (действие р) запрещающий сигнал на физический уровень интерфейса 18, где разомкнется канал передачи выходных данных в шину 5.

Дополнительно микроконтроллер 14 безопасности принимает результаты периодически исполняемых программных диагностик (диагностика работоспособности сервисов, сетевых интерфейсов и т.п.) из центрального микропроцессора 11 и дополнительного микропроцессора 12. При отказе любого из микропроцессоров микроконтроллер 14 безопасности не даст разрешения контроллеру 17 шины на передачу выходных данных в шину 5. К тому же микроконтроллер 14 безопасности может сформировать (действие r) сигнал RESET, который направит в центральный микропроцессор 11, который прекратит выполнение инструкций. К тому же он может отправить (действие р) запрещающий сигнал на физический уровень интерфейса 18, где разомкнется канал передачи выходных данных в шину 5.

Использование в модуле ЦП микроконтроллера 14 безопасности, который с помощью программного обеспечения контролирует микропроцессоры, в отличие от использования для контрольных проверок простых логических элементов, позволяет предусмотреть различные варианты поведения микропроцессоров. Так, действия микроконтроллера 14 безопасности, направленные на прекращение передачи выходных данных из модуля ЦП 2, не всегда должны приводить к остановке работы микропроцессоров. Можно предусмотреть любые другие дальнейшие действия, например, перезагрузку микропроцессоров, их дальнейшую диагностику, выдачу данных диагностики на монитор оператора, и принятие решения оператором о прекращении работы модуля ЦП.

Для реализации модуля ЦП могут быть использованы следующие устройства:

В качестве центрального микропроцессора может быть использован четырехъядерный процессор Т1040 серии QorIQ®, производимый NXP SEMICONDUCTORS, с архитектурой ядра Power Architecture е5500, с тактовой частотой 1200 МГц и DMIPS 3600 на одно ядро.

В качестве дополнительного микропроцессора может быть использован двухъядерный процессор LS1020 серии QorIQ®, производимый NXP SEMICONDUCTORS, с архитектурой ядра ARM Cortex™-A7, с тактовой частотой 1000 МГц и DMIPS 2500 на одно ядро.

В качестве микроконтроллера безопасности может быть использован микроконтроллер Hercules™, TMS570 с архитектурой ядра ARM® Cortex-R5F™. К такому микроконтроллеру не предъявляются требования высокой производительности и быстродействия, которые необходимы для работы ПЛК в больших АСУ ТП, но зато такой микроконтроллер обладает высоким уровнем аппаратной и программной самодиагностики, что делает его высоконадежным устройством. Так, микроконтроллер Hercules™, TMS570 ARM® Cortex-R5F™, имеет тактовую частоту до 300 МГц и DMIPS 500.

Список литературы

1 Карл Глеб, Дев Прадхан, Микроконтроллеры Hercules™: микроконтроллеры реального времени для техники с особыми требованиями к обеспечению безопасности // Бюллетень научно-технической информации «Компоненты. Полный спектр применений», выпуск 3(35) 2012. - С. 1-8,

(https://www.ti.com/graphics/reserved/eugraphics/35_ALL.pdf);

2 Safety Manual for RM42x and RM41xHercules™ ARM® - Based Safety Critical Microcontrollers,  Guide, Literature Number: SPNU553B, November 2014-Revised October 2015, Texas Instruments Incorporated, (http://www.ti.com/lit/ug/spnu553b/spnu553b.pdf):

Guide, Literature Number: SPNU553B, November 2014-Revised October 2015, Texas Instruments Incorporated, (http://www.ti.com/lit/ug/spnu553b/spnu553b.pdf):

3 RM42x 16/32-Bit RISC Flash Microcontroller, Technical Reference Manual, Literature Number: SPNU516C March 2018, Texas Instruments Incorporated, (http://www.ti.com/lit/ug/spnu516c/spnu516c.pdf):

4 Safety Manual for RM57x Hercules™ ARM  Safety MCUs,

Safety MCUs,  Guide, Literature Number: SPNU575A, May 2014 - Revised September 2016, Texas Instruments Incorporated, (http://www.ti.com/lit/ug/spnu575a/spnu575a.pdf):

Guide, Literature Number: SPNU575A, May 2014 - Revised September 2016, Texas Instruments Incorporated, (http://www.ti.com/lit/ug/spnu575a/spnu575a.pdf):

5 TMS570LC43x 16/32-Bit RISC Flash Microcontroller, Technical Reference Manual, Literature Number: SPNU563A March 2018, Texas Instruments Incorporated, (http://www.ti.com/lit/ug/spnu563a/spnu563a.pdf).

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ передачи данных по шине, система связи для осуществления данного способа и устройство автоматической защиты для предотвращения аварийной ситуации на объекте управления | 2018 |

|

RU2705421C1 |

| Микропроцессорная система централизации МПЦ-ЭЛ | 2018 |

|

RU2692739C1 |

| СПОСОБ ФОРМИРОВАНИЯ ОТКАЗОУСТОЙЧИВОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ И ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2010 |

|

RU2439674C1 |

| Сложно-функциональный блок для СБИС типа система на кристалле | 2018 |

|

RU2691886C1 |

| Микропроцессорное устройство релейной защиты и автоматики с модулем управления вакуумным выключателем | 2022 |

|

RU2800658C1 |

| МИКРОПРОЦЕССОРНАЯ СИСТЕМА ЦЕНТРАЛИЗАЦИИ МПЦ-ЭЛ | 2017 |

|

RU2709068C1 |

| Программируемый логический контроллер для управления устройствами реального времени | 2024 |

|

RU2825561C1 |

| ГИБРИДНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2014 |

|

RU2627100C2 |

| СИСТЕМА ЛОГИЧЕСКОГО УПРАВЛЕНИЯ (ВАРИАНТЫ) | 2012 |

|

RU2574837C2 |

| Программно-аппаратная платформа и способ ее реализации для беспроводных средств связи | 2016 |

|

RU2626550C1 |

Изобретение относится к архитектуре модуля центрального процессора промышленного контроллера с программируемой логикой. Технический результат заключается в расширении арсенала средств. Центральный микропроцессор (ЦМ) предназначен для выполнения задачи прикладной программы, дополнительный микропроцессор (ДМ) предназначен для выполнения точно такой же задачи с теми же входными данными от датчиков, что и ЦМ, контроллер шины (КШ), сформированный в ПЛИС, предназначен для обмена данными по шине, микроконтроллер безопасности (МБ) для контроля работы своего функционального ядра содержит контролирующее ядро и модуль сравнения, который предназначен для сравнения результатов вычислений с параллельно работающих функционального и контролирующего ядер, МБ разрешает КШ передачу выходных данных в шину в случае, если выполнено условие равенства результатов обработки из ЦМ и ДМ, и время выполнения задачи ЦМ и ДМ находится в заданном интервале времени, и результаты вычислений функционального и контролирующего ядер равны. 3 ил.

Модуль центрального процессора промышленного контроллера, содержащий центральный микропроцессор, предназначенный для выполнения задачи прикладной программы, в результате которой обрабатываются входные данные от датчиков, и результатом обработки которых являются выходные данные, предназначенные для управления исполнительными механизмами, дополнительный микропроцессор с архитектурой ядра, отличной от архитектуры ядра центрального микропроцессора, и предназначенный для выполнения точно такой же задачи с точно такими же входными данными от датчиков, что и в центральном микропроцессоре, отличающийся тем, что он дополнительно содержит программируемую логическую интегральную схему с контроллером шины, предназначенным для обмена данными по шине между модулем центрального процессора и модулями ввода и/или вывода промышленного контроллера, и микроконтроллер безопасности, имеющий два ядра одинаковой архитектуры, одно из которых функциональное, а другое предназначено для контроля работы функционального ядра, и модуль сравнения, который предназначен для сравнения результатов вычислений с работающих параллельно с одним и тем же программным обеспечением и одними и теми же данными двух ядер, и предназначенный для сравнения результатов обработки из центрального микропроцессора и из дополнительного микропроцессора, и предназначенный для контроля времени выполнения задачи каждым из микропроцессоров, которое должно находиться в заданном интервале времени, который определяется исходя из объема обрабатываемых в задаче данных, и имеющий возможность разрешать контроллеру шины передачу выходных данных в шину, в случае если результаты вычислений ядер микроконтроллера безопасности равны, и результаты обработки из центрального и из дополнительного микропроцессоров равны, и время выполнения задачи каждым из микропроцессоров находится в заданном интервале времени.

| RU 94013455 A1, 20.09.1996 | |||

| Многоступенчатая активно-реактивная турбина | 1924 |

|

SU2013A1 |

| EP 1973017 A2, 24.09.2008 | |||

| СПОСОБ АВТОМАТИЧЕСКОГО ИЗМЕНЕНИЯ ДИСБАЛАНСА ВРАЩАЮЩЕЙСЯ СИСТЕМЫ | 2002 |

|

RU2237118C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ КОНТРОЛЯ СИСТЕМЫ С НЕСКОЛЬКИМИ ФУНКЦИОНАЛЬНЫМИ БЛОКАМИ | 1998 |

|

RU2175451C2 |

| МАШИНА ДЛЯ ВЫКОПКИ ПОСАДОЧНОГО (МАТЕРИАЛА | 0 |

|

SU180915A1 |

Даты

2019-10-21—Публикация

2019-04-19—Подача