Область техники, к которой относится изобретение

Это изобретение относится к области матричных преобразователей, а конкретнее - к области матричных преобразователей, содержащих двунаправленные переключатели.

УРОВЕНЬ ТЕХНИКИ

Матричный преобразователь в типичном случае представляет собой одноcтупенчатый преобразователь переменного тока в переменный, в котором используется матрица переключателей для преобразования первого сигнала переменного тока (любого числа фаз) во второй сигнал переменного тока (любого числа фаз) с произвольной амплитудой и частотой. Одно преимущество матричного преобразователя заключается в том, что не нужны никакие аккумулирующие энергию элементы большой емкости.

Типичные матричные преобразователи требуют, чтобы каждый переключатель в матрице переключателей был двунаправленным переключателем, выполненным с возможностью блокировки напряжения и проведения тока в обоих направлениях. Двухдиодный двухтранзисторный двунаправленный переключатель воплощает известный способ независимого управления током, протекающим в обоих направлениях в пределах матричного преобразователя. Известна предусматривающая четыре этапа последовательность коммутации такого двунаправленного переключателя (т.е., известен способ выключения первого двунаправленного переключателя и включения второго переключателя посредством избирательного переключения их транзисторов).

Один известный метод модуляции для матричного преобразователя предусматривает использование пространственно-векторной модуляции (ПВМ) для осуществления модуляции первого сигнала переменного тока. Специалистам в данной области техники известны несколько методов ПВМ, такие, как способы с тремя нулями, двумя нулями и одним нулем.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Изобретение охарактеризовано формулой изобретения.

В соответствии с первым аспектом изобретательского замысла, предложен матричный преобразователь, содержащий: m входных узлов для соединения с m-фазным источником напряжения, где m равно, по меньшей мере, единице; n выходных узлов для соединения с n-фазной нагрузкой, где n равно, по меньшей мере, единице и, по меньшей мере, одно из m или n равно двум или более; m × n двунаправленных переключателей, причем каждый двунаправленный переключатель подсоединен между одиночным входным узлом и одиночным выходным узлом, так что каждый выходной узел выполнен с возможностью избирательного соединения с каждым входным узлом посредством двунаправленного переключателя; и контроллер, подсоединенный с возможностью управления проводимостью упомянутых двунаправленных переключателей таким образом, что двунаправленное соединение между каждым входным узлом и каждым выходным узлом является избирательно управляемым, причем контроллер выполнен так, что минимальный период времени между изменением проводимости любого одиночного двунаправленного переключателя является не меньшим, чем предварительно определенный период времени.

Иными словами, матричный преобразователь можно адаптировать так, что двунаправленный переключатель будет иметь минимальное время переключения, вследствие чего ни один двунаправленный переключатель не сможет пульсировать, включаясь-выключаясь-выключаясь или выключаясь-включаясь-выключаясь, в пределах предварительно определенного периода времени. Это не исключает возможность, в соответствии с которой разница в периоде времени между первым состоянием переключения двунаправленного переключателя (например, от состояния выключения до состояния включения) и вторым состоянием переключения двунаправленного переключателя может быть меньшей, чем упомянутый предварительно определенный период времени.

По меньшей мере, в одном предпочтительном варианте осуществления, матричный преобразователь выполнен так, что в нем каждый двунаправленный переключатель содержит, по меньшей мере, один транзистор, контроллер подсоединен с возможностью управления проводимостью каждого транзистора и контроллер выполнен так, что минимальный период времени между изменением проводимости любого одиночного транзистора является не меньшим, чем упомянутый предварительно определенный период времени.

Иными словами, предложен матричный преобразователь, содержащий матрицу m × n двунаправленных переключателей. С этой матрицей соединено множество, состоящее из m входных узлов и n выходных узлов. Каждый двунаправленный переключатель подсоединен между входным узлом и выходным узлом некоторой особой пары, так что каждые из упомянутых входного и выходного узлов выполнены с возможностью соединения посредством двунаправленного переключателя. Каждый из двунаправленных переключателей содержит, по меньшей мере, один транзистор.

Контроллер обеспечивает подключение регулируемого напряжения к каждому транзистору упомянутых двунаправленных переключателей, чтобы управлять проводимостью транзисторов (т.е., управлять током, текущим через любой заданный транзистор). То есть, контроллер позволяет регулировать напряжения, подаваемые на затвор каждого транзистора, для управления проводимостью через транзистор (например, от истока или коллектора, соединенного со входным узлом, к стоку или эмиттеру, соединенному с выходным узлом). Таким образом, контроллер может управляемо соединять любой входной узел с любым выходным узлом.

Контроллер выполнен с возможностью изменения проводимости лишь какого-либо одиночного транзистора с минимальной предварительно определенной временной задержкой, т.е., каждый транзистор имеет максимальную допустимую частоту событий переключения, управляемую контроллером. Возможность изменять только проводимость некоторого заданного транзистора на максимальной частоте таким образом может позволить предотвратить избыточное температурное напряжение в приборах.

Это не исключает возможность изменения проводимости разных транзисторов за более короткий период времени. Например, в первый момент времени (ti1) первый транзистор может не позволять току течь, а второй транзистор может позволять току течь; во второй момент времени (ti2) проводимость первого транзистора можно изменить, позволяя току течь. В третий момент времени (ti3), когда после второго момента времени пройдет меньше, чем предварительно определенный период времени (tpd) (т.е., ti3 - ti2 < tpd), проводимость второго транзистора можно изменить, не позволяя току течь.

Опционально, контроллер представляет собой программируемую пользователем вентильную матрицу, FPGA. Такая FPGA может обеспечить, например, этот минимальный период времени между изменением проводимости, действуя как конечный автомат, чтобы обеспечить синхронизированные «состояния удержания», в котором напряжение (которое изменяет проводимость), прикладываемое к любому заданному транзистору, можно изменять лишь после истечения установленного периода времени «состояния удержания», и тогда происходит выход из этого состояния.

Такой матричный преобразователь может дополнительно содержать микроконтроллер, соединенный с FPGA, причем этот микроконтроллер выполнен с возможностью выбора того входного узла, с которым должен быть двунаправленно соединен выходной узел.

Матричный преобразователь можно адаптировать так, что период времени между изменением проводимости любого одиночного транзистора двунаправленных переключателей станет зависимым от n-фазной нагрузки, возбуждаемой выходными узлами.

Предварительно определенный период времени можно рассчитать на основе любого количества факторов, например: фазы нагрузки; фазы источника напряжения; способа модуляции; спецификации переключателей и их тепловых характеристик (например, технологии транзисторов и типа используемого корпуса); или напряжения, которое надлежит подать на нагрузку, или потерь, которые должны выдерживать переключатели.

Матричный преобразователь может дополнительно содержать, по меньшей мере, один конденсатор, подсоединенный между каждым из входных узлов.

Размеры конденсаторов могут зависеть от требуемой рабочей характеристики высокочастотных гармоник. Они могут быть достаточно большими, чтобы гарантировать пульсацию напряжения на входе преобразователя, достаточно малую для обеспечения правильной работы самого преобразователя. Квалифицированный читатель легко сможет рассчитать эти размеры.

В некоторых вариантах осуществления, каждый выходной узел является двунаправленно соединенным лишь с одним входным узлом одновременно.

Иными словами, протекание двунаправленного тока допустимо только от одного входного узла к одному выходному узлу. Иначе говоря, источник напряжения, предусмотренный во входном узле, может обеспечить двунаправленный ток для более чем одного выходного узла и подсоединяемых нагрузок, но ни один заданный выходной узел не может получать двунаправленный ток из более чем одного входного узла.

Возможный двунаправленный переключатель может содержать: первый транзистор и первый диод, скомпонованные последовательно; и второй транзистор и второй диод, скомпонованные последовательно, причем первый и второй транзисторы скомпонованы друг за другом, так что двунаправленный переключатель сконфигурирован с возможностью обеспечивать первое однонаправленное соединение от соответствующего входного узла к соответствующему выходному узлу или второе однонаправленное соединение от упомянутого выходного узла к упомянутому входному узлу.

Иными словами, каждый двунаправленный переключатель может содержать два однонаправленных переключателя, расположенных антипоследовательно.

Одна конфигурация возможного двунаправленного переключателя содержит первый и второй транзисторы и первый и второй диоды. Каждый транзистор содержит затвор, коллектор и эмиттер в качестве обычных электронных средств. В одном варианте осуществления, транзисторы расположены так, что эмиттер первого транзистора соединен с эмиттером второго транзистора, чтобы обеспечить управляемость двунаправленного тока. В такой конфигурации, входной узел матричного преобразователя может быть соединен с коллектора первого транзистора, а выходной узел может быть соединен с коллектором второго транзистора. При данной конфигурации, первый диод простирается от эмиттера первого транзистора к упомянутому выходному узлу, а второй диод простирается от эмиттера второго транзистора к упомянутому входному узлу. Таким образом, первый транзистор и первый диод соединены последовательно, и второй транзистор и второй диод тоже соединены последовательно.

Возможны и альтернативные компоновки двунаправленного переключателя, предусматривающие наличие первого и второго транзисторов и первого и второго диодов. Например, транзисторы можно скомпоновать так, что коллектор первого транзистора окажется соединенным с коллектором второго транзистора, обеспечивая управляемость двунаправленного тока. Соответственно, входной узел матричного преобразователя может быть на эмиттере первого транзистора, а выходной узел матричного преобразователя может быть на эмиттере второго транзистора. Для этой конфигурации, первый диод простирается от коллектора первого транзистора к упомянутому выходному узлу, а второй диод простирается от коллектора второго транзистора к упомянутому входному узлу. Таким образом, первый транзистор и первый диод остаются соединенными последовательно, и второй транзистор и второй диод тоже остаются соединенными последовательно.

Матричный преобразователь с такими двунаправленными переключателями, как эти, можно адаптировать так, что выходной узел окажется однонаправленно соединенным не более чем с двумя входными узлами одновременно.

Иными словами, в какой-либо заданный момент времени максимальное число однонаправленных переключателей двунаправленных переключателей, связанных с каким-либо заданным выходным узлом, которые могут обладать высокой проводимостью, составляет лишь два. Таким образом, возможный выходной узел может иметь первое однонаправленное соединение с первым входным узлом (например, току разрешается течь от первого входного узла к возможному выходному узлу) и второе однонаправленное соединение со вторым входным узлом (например, току разрешается течь от возможного выходного узла ко второму входному узлу).

В некоторых вариантах осуществления контроллер выполнен так, что предварительно определенный период времени является не меньшим, чем 2,5 мкс, например - не меньшим, чем 3,5 мкс.

В дополнительных вариантах осуществления контроллер дополнительно выполнен так, что минимальный период времени между изменением проводимости любого одиночного транзистора двунаправленных переключателей является не меньшим, чем 3,5 мкс.

В некоторых вариантах осуществления может оказаться предпочтительным ограничение минимального периода времени между изменением проводимости любого одиночного транзистора двунаправленного переключателя значением, не превышающим 5 мкс. В частности, установление такого длительного минимального периода может дать нежелательное искажение на выходе.

В соответствии с еще одним аспектом изобретательского замысла, предложен способ переключения двунаправленного соединения с выходным узлом от первого входного узла ко второму входному узлу, причем первый входной узел выполнен с возможностью соединения с выходным узлом первого двунаправленного переключателя, содержащего первый транзистор и первый диод, скомпонованные последовательно, и второй транзистор и второй диод, скомпонованные последовательно, причем первый и второй транзисторы скомпонованы друг за другом, а второй входной узел выполнен с возможностью соединения с выходным узлом второго двунаправленного переключателя, содержащего третий транзистор и третий диод, скомпонованные последовательно, и четвертый транзистор и четвертый диод, скомпонованные последовательно, причем третий и четвертый транзисторы скомпонованы друг за другом, при этом проводимостью каждого транзистора управляет контроллер, переключая ее между более высокой при включении и более низкой при выключении, причем в исходном состоянии первый и второй транзисторы оба включены, а третий и четвертый транзисторы оба выключены, при этом способ содержит этапы, на которых: в первый момент времени выключают первый транзистор; во второй момент времени включают третий транзистор; в третий момент времени выключают второй транзистор; в четвертый момент времени включают четвертый транзистор; а способ отличается тем, что дополнительно содержит этапы, на которых: в четвертый момент времени блокируют четвертый транзистор, оставляя его включенным; в пятый момент времени, деблокируют четвертый транзистор, причем пятый момент времени наступает после четвертого момента времени не раньше, чем по истечении предварительно определенного периода времени.

Например, этот предварительно определенный период времени предпочтительно составляет 2,5 мкс; вместе с тем, в других вариантах осуществления этот предварительно определенный периоде времени может составлять 3,5 мкс или 5 мкс.

Способ можно адаптировать так, что предварительно определенный максимальный период времени будет существовать, по меньшей мере, между одними из следующих: первым и вторым моментами времени; вторым и третьим моментами времени; и третьим и четвертым моментами времени.

Например, этот предварительно определенный максимальный период времени может составлять 1 мкс.

Предложен также способ эксплуатации матричного преобразователя, имеющего, по меньшей мере, один выходной узел и, по меньшей мере, два входных узла, причем каждый выходной узел является двунаправленно соединенным с каждым входным узлом посредством двунаправленного переключателя, при этом способ содержит этап, на котором: используют метод пространственно-векторной модуляции для управления порядком переключения двунаправленных соединений между, по меньшей мере, одним выходным узлом и, по меньшей мере, двумя входными узлами, причем этап переключения двунаправленного соединения осуществляют так, как описано выше.

Метод пространственно-векторной модуляции может представлять собой, например, способ модуляции с двумя нулями. В других вариантах осуществления, метод пространственно-векторной модуляции представляет собой способ модуляции с тремя нулями или одним нулем.

Способ модуляции с двумя нулями показан здесь как обеспечивающий n-фазный выходной сигнал с улучшенным полным коэффициентом гармоник. Для некоторых ситуаций, способ модуляции с тремя нулями может обеспечить улучшенную общую рабочую характеристику.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Теперь, со ссылками на прилагаемые чертежи, будут подробно описаны примеры изобретения, при этом:

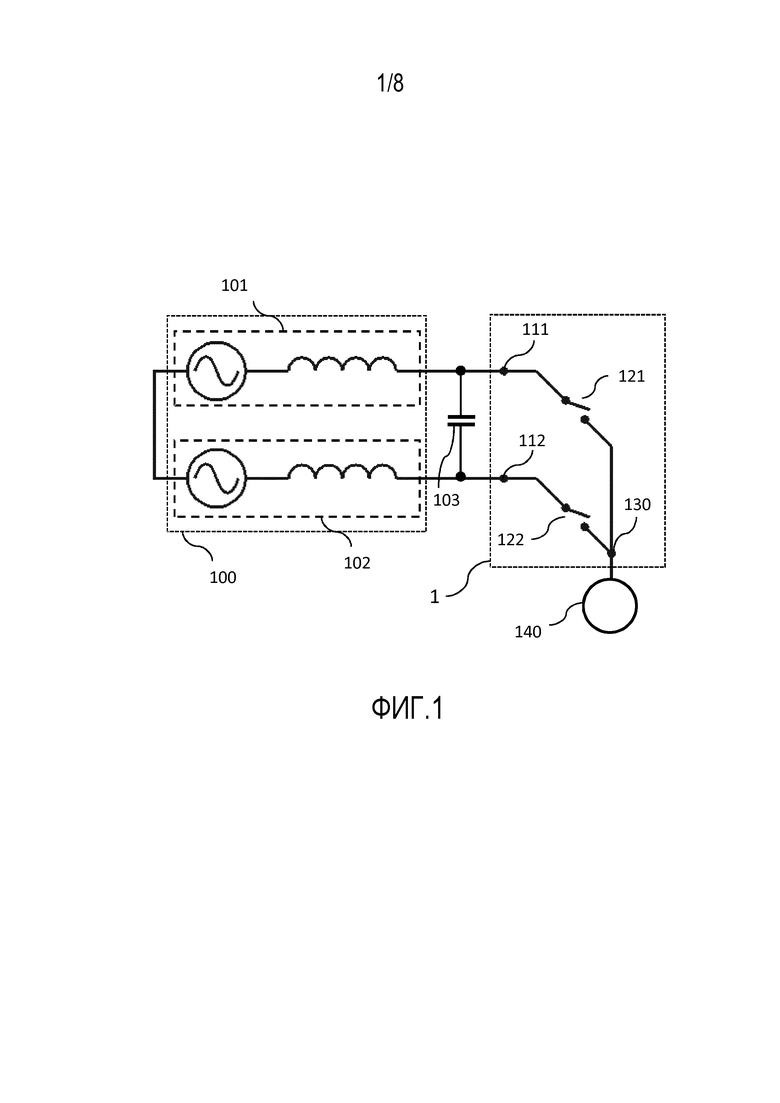

на фиг.1 иллюстрируется матричный преобразователь в соответствии с первым возможным вариантом осуществления;

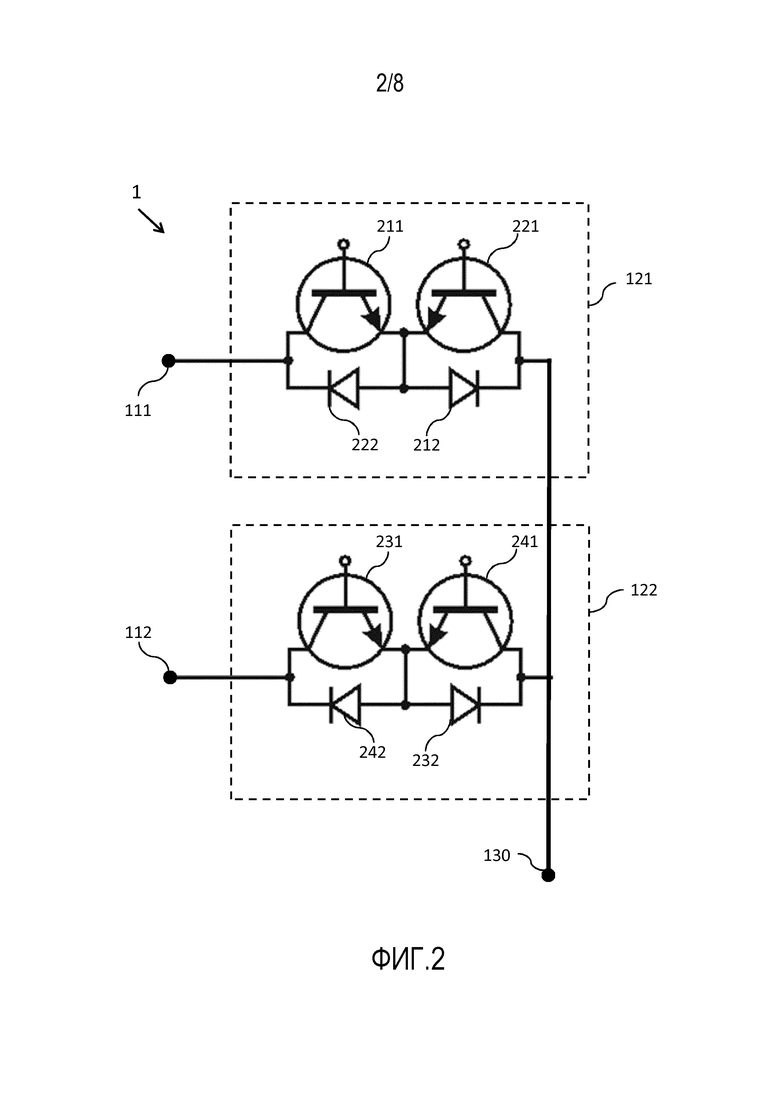

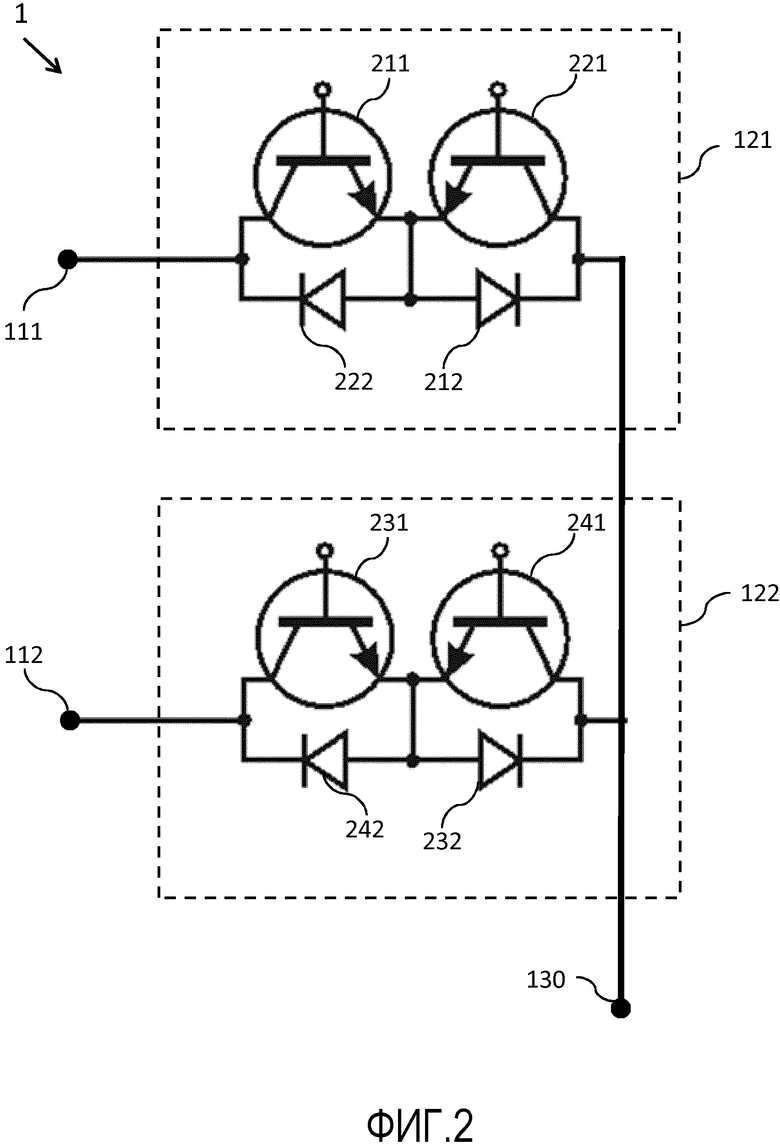

на фиг.2 изображен подробный вид матричного преобразователя в соответствии с первым возможным вариантом осуществления;

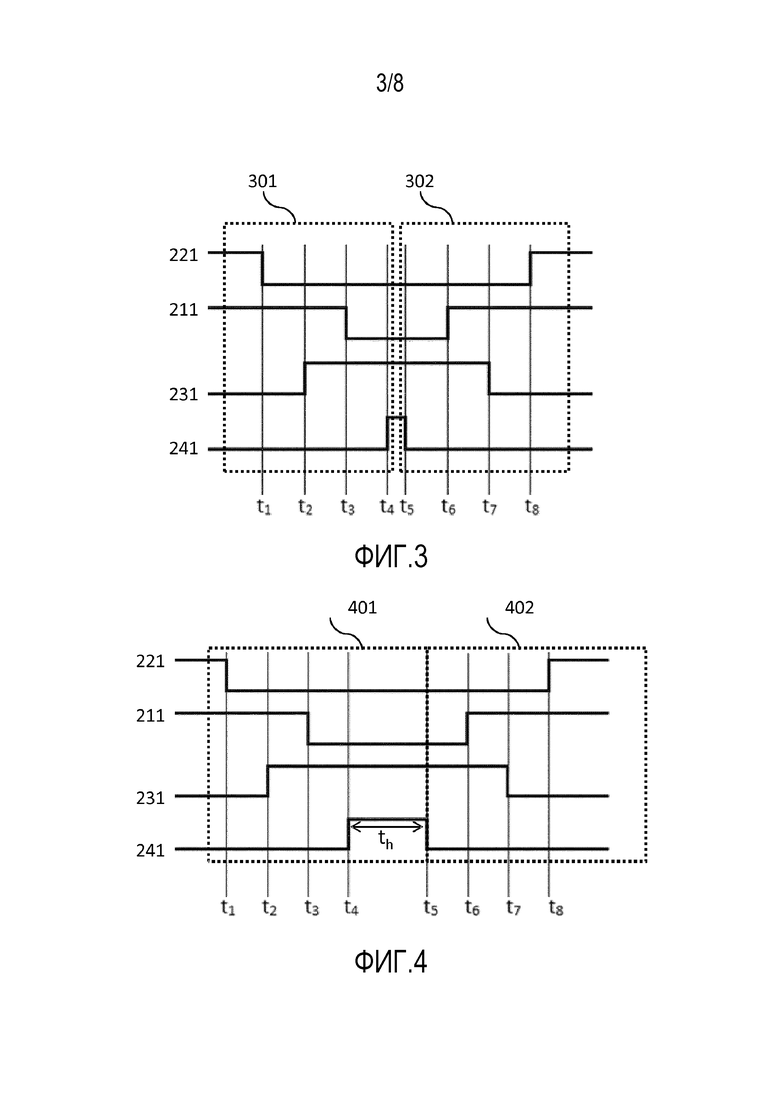

на фиг.3 представлен типичный граф известной последовательности вычислений;

на фиг.4 представлен типичный граф последовательности коммутации в соответствии с первым возможным вариантом осуществления;

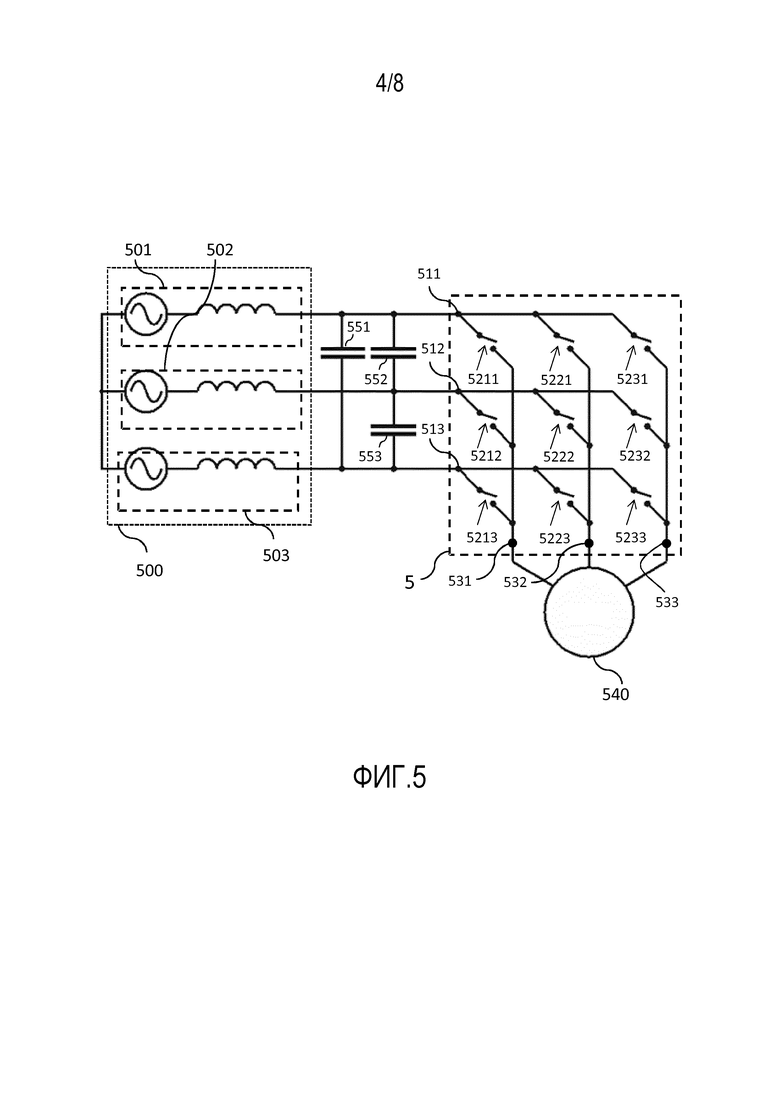

на фиг.5 иллюстрируется матричный преобразователь в соответствии со вторым возможным вариантом осуществления;

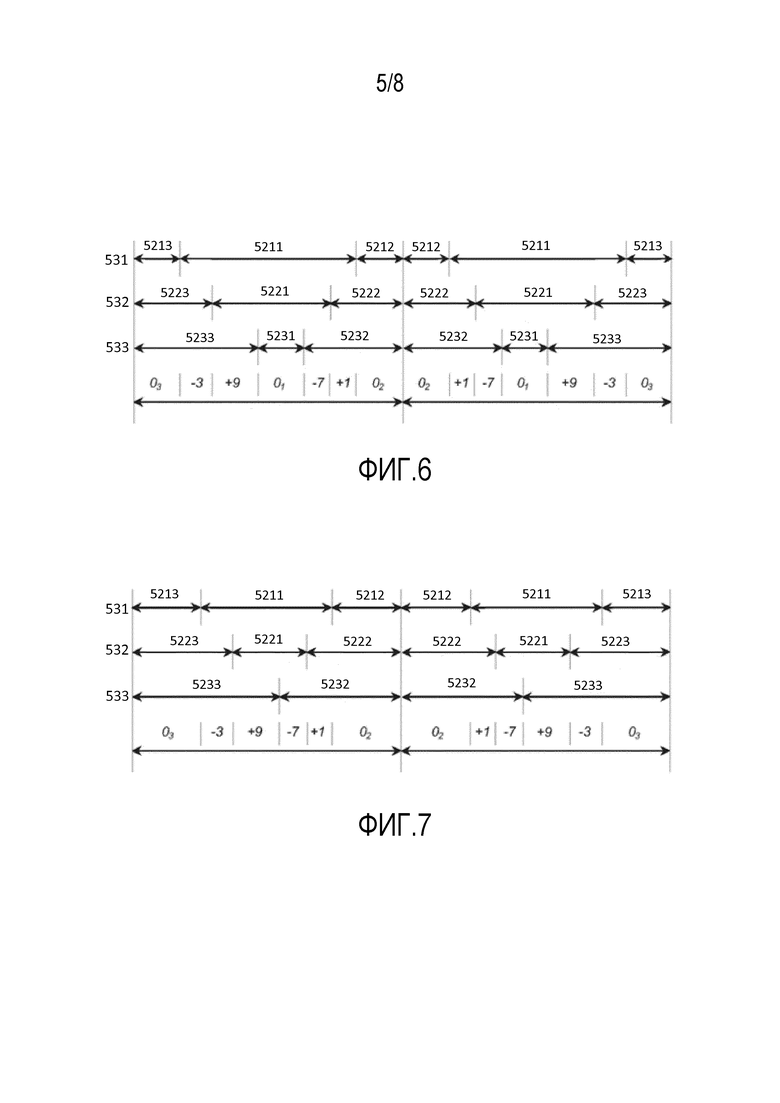

на фиг.6 представлена типичная диаграмма метода пространственно-векторной модуляции с тремя нулями для второго возможного варианта осуществления;

на фиг.7 представлена типичная диаграмма метода пространственно-векторной модуляции с двумя нулями для второго возможного варианта осуществления;

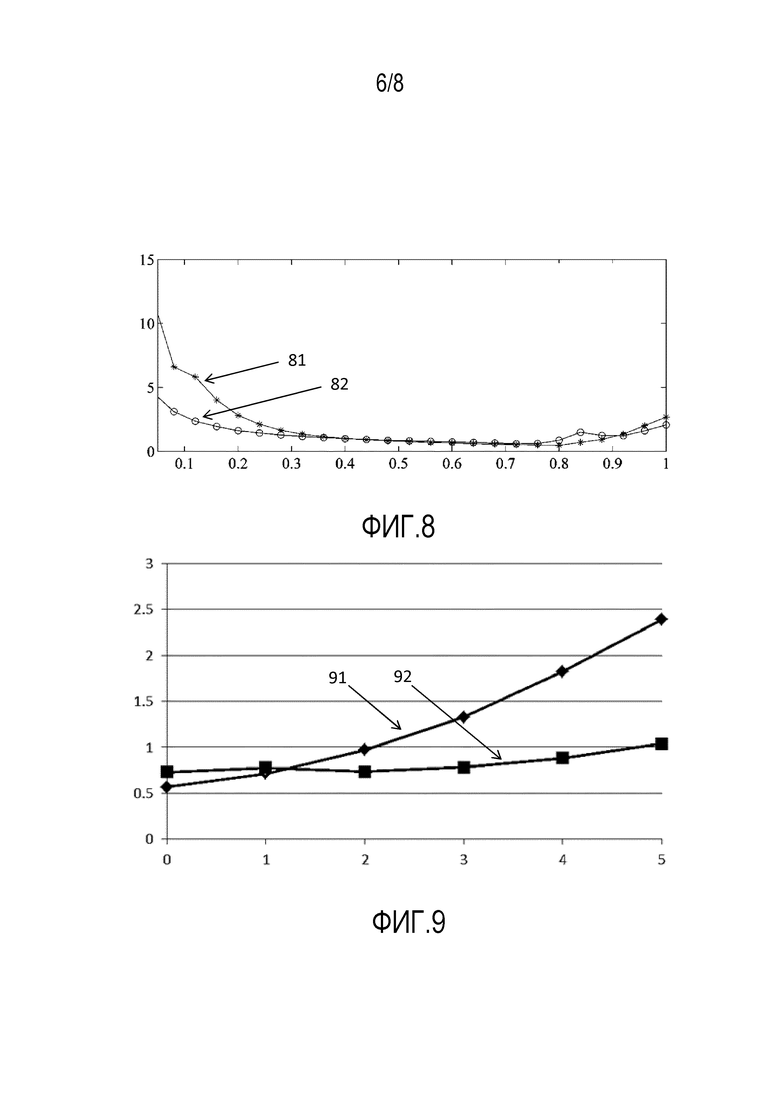

на фиг.8 представлен смоделированный график полного коэффициента гармоник (ПКГ) выходного тока для увеличения индекса модуляции согласно методам пространственно-векторной модуляции с тремя нулями и двумя нулями;

на фиг.9 представлен смоделированный график полного коэффициента гармоник (ПКГ) выходного тока для увеличения времени удержания коммутации согласно методам пространственно-векторной модуляции с тремя нулями и двумя нулями;

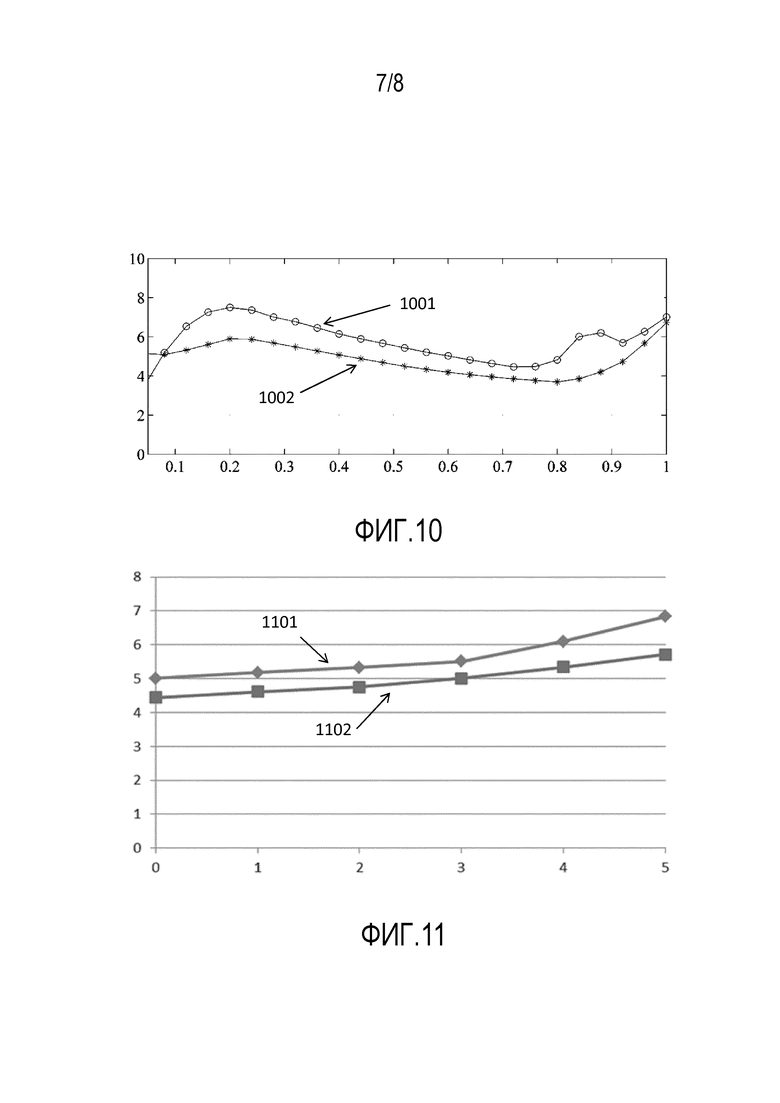

на фиг.10 представлен смоделированный график полного коэффициента гармоник (ПКГ) входного тока для увеличения индекса модуляции согласно методам пространственно-векторной модуляции с тремя нулями и двумя нулями;

на фиг.11 представлен смоделированный график полного коэффициента гармоник (ПКГ) входного тока для увеличения времени удержания коммутации согласно методам пространственно-векторной модуляции с тремя нулями и двумя нулями; и

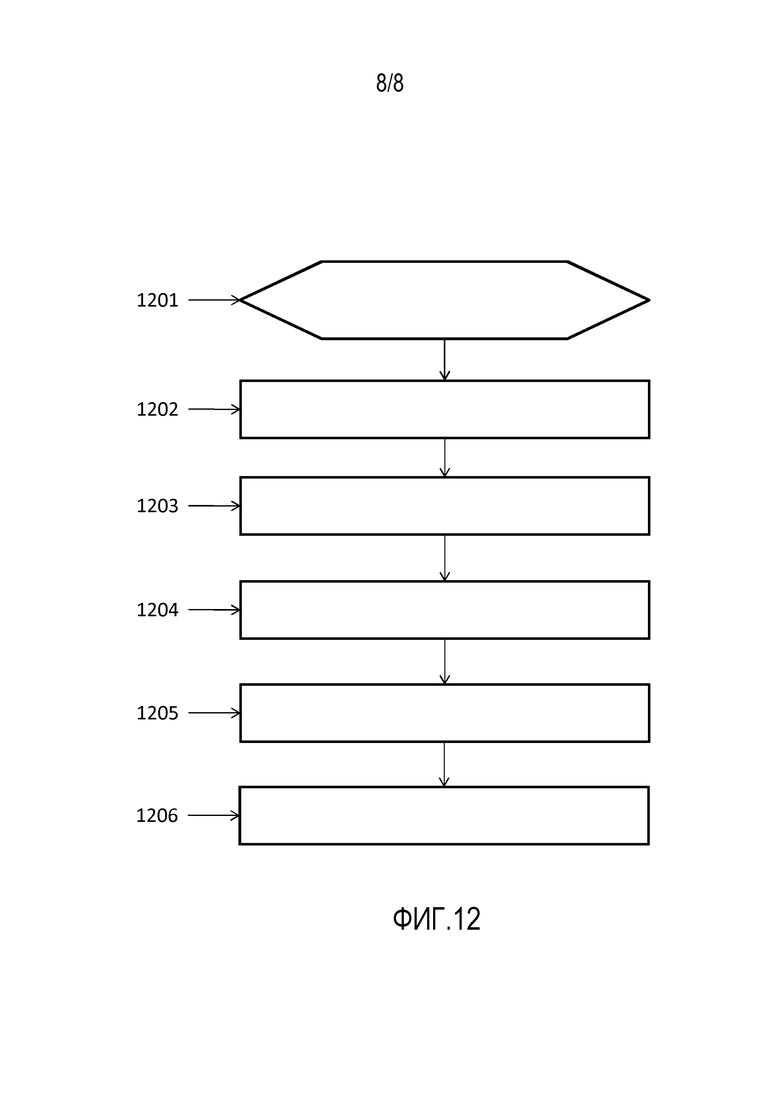

на фиг.12 представлена типичная блок-схема последовательности операций способа для последовательности коммутации в соответствии с первым возможным вариантом осуществления.

ПОДРОБНОЕ ОПИСАНИЕ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ

В изобретении предложен матричный преобразователь, выполненный с возможностью преобразования многофазного входного сигнала в многофазный выходной сигнал. Представлена концепция обеспечения минимального периода переключения транзистора для любого заданного транзистора в матричном преобразователе. В соответствии с ней, минимальный период переключения транзистора для любого заданного транзистора также подразумевает минимальный период переключения двунаправленных переключателей.

Обращаясь к фиг.1, отмечаем, что здесь показан первый вариант осуществления матричного преобразователя 1. Матричный преобразователь 1 представляет собой простой матричный преобразователь двухфазного сигнала в однофазный. Иными словами, двухфазный входной сигнал 100 можно модулировать посредством матричного преобразователя 1 на однофазную выходную нагрузку 140. Матричный преобразователь 1 содержит первый и второй входные узлы 111 и 112 для соединения с источником 100 напряжения первой и второй фаз 101 и 102. Матричный преобразователь 1 также содержит выходной узел 130 для соединения с выходной нагрузкой 140. Конденсатор 103 обеспечивает цепь индуктивного тока каждой фазы. Матричный преобразователь содержит первый и второй двунаправленные переключатели 121 и 122, которые обеспечивают модуляцию двух входных сигналов 101 и 102 фаз на выходную нагрузку 140. Чтобы модулировать два входных сигнала фаз, можно попеременно включать и выключать два двунаправленных переключателя (т.е., позволять двунаправленному току течь через переключатель). Управление этим переключением можно осуществлять, например, посредством программируемой пользователем вентильной матрицы, FPGA (не показана).

На фиг.2 возможный матричный преобразователь 1 изображен подробнее. Здесь показаны первый и второй возможные двунаправленные переключатели 121 и 122 для упомянутого матричного преобразователя 1.

Возможный первый двунаправленный переключатель 121 содержит первый и второй двунаправленные переключатели 211, 212 и 221, 222, скомпонованные антипоследовательно. Первый двунаправленный переключатель 211, 212 управляет протеканием тока в одном из двух направлений (например, в прямом направлении от соответствующего входного узла 111 к соответствующему выходному узлу 130), тогда как второй двунаправленный переключатель 221, 222 управляет протеканием тока в противоположном из двух направлений (например - в обратном, от соответствующего выходного узла 130 к соответствующему входному узлу 111). Таким образом, током в обоих направлениях - прямом и обратном - от каждого входного узла к выходному узлу можно управлять независимо посредством двунаправленного переключателя. Такому двунаправленному переключателю можно дать альтернативное название - переключательный элемент.

Аналогичным образом, второй двунаправленный переключатель 122 скомпонован с такими же компонентами и таким же образом, как первый двунаправленный переключатель 121, то есть, содержит первый двунаправленный переключатель 231, 232 и второй двунаправленный переключатель 241, 242, скомпонованные антипоследовательно.

Напряжение, прикладываемое к затвору транзистора, например - посредством FPGA, управляет проводимостью упомянутого транзистора. Если к упомянутому затвору прикладывается двухуровневый сигнал напряжения (например, сигнал напряжения, величина которого составляет либо 3,3 В, либо 0 В), то транзистор можно считать имеющим два состояния проводимости, «включен» или «выключен». В состоянии «включен», транзистор заперт, обладая высокой проводимостью, и может обеспечивать протекание через него тока. В состоянии «выключен» транзистор обладает низкой проводимостью и не может обеспечивать протекание через него тока. Например, соединением входного узла 111 с выходным узлом 130 в обоих направлениях тока можно управлять напряжением, прикладываемым к затворам транзисторов двунаправленного переключателя 121. Специалист в данной области техники поймет, что в рамках объема притязаний изобретения доступны другие способы управления транзисторами, а значит - и двунаправленными переключателями, такие, как с помощью микроконтроллера. Помимо этого, для управления проводимостью можно прикладывать к затворам напряжения других уровней (например, 5 В, 3 В).

Как упоминалось ранее, в одном способе модуляции двухфазного входного сигнала на однофазную выходную нагрузку следует попеременно включать и выключать двунаправленные переключатели. Чтобы предотвратить междуфазные короткие замыкания (входа), никакие два двунаправленных переключателя, связанные с одиночным выходным узлом, не следует переключать ни в какой заданный момент времени. Иными словами, двунаправленно соединенным с одиночным входным узлом в какой-либо заданный момент может быть только выходной узел 130, Аналогичным образом, чтобы гарантировать наличие цепи индуктивного тока каждой фазы входного сигнала, ни один выходной узел 130 не должен быть полностью отсоединен от каждого входного узла 112, 111, чтобы тем самым предотвратить возникновение больших перенапряжений. Иными словами, выходной узел 130 всегда должен быть соединен с источником 100 напряжения фаз. Эти два ограничения обеспечивают повышенную безопасность, надежность и долговечность приборов.

Ниже описывается один способ безопасного переноса соединения с выходным узлом 130 от первого входного узла 111 ко второму входному узлу 112. Эту процедуру можно назвать по-другому - коммутацией, и она подразумевает этапы, называемые последовательностью коммутации.

На фиг.3 показана типичная (для известного уровня техники) последовательность 301 коммутации, предназначенная для коммутации сначала соединения с выходным узлом 130 от первого входного узла 111 ко второму входному узлу 112 (t1 - t4) и последующего обращения последовательности 302 коммутации (t5 - t8). Граф демонстрирует представительные формы сигнала для двухуровневого сигнала напряжения, подаваемого на затворы соответственных транзисторов, включающего и выключающего эти транзисторы, соответственно.

Сначала включают полностью первый двунаправленный переключатель 121 и включают соответствующие двунаправленные переключатели прямого и обратного тока (т.е., первый двунаправленный переключатель 211, 212 и второй двунаправленный переключатель 221, 222, соответственно), и тогда связанные с ними транзисторы обладают высокой проводимостью, позволяя току течь. Аналогичным образом, второй двунаправленный переключатель 122 выключают полностью и выключают соответствующий двунаправленный переключатель прямого и обратного тока (т.е., третий двунаправленный переключатель 231, 232 и четвертый двунаправленный переключатель 241, 242, соответственно), и тогда связанные с ними транзисторы обладают низкой или почти нулевой проводимостью, позволяя течь лишь пренебрежимо малому току.

В первый момент времени (t1) выключают второй транзистор 221 (двунаправленный переключатель обратного тока первого двунаправленного переключателя 121).

Во второй момент времени (t2) включают третий транзистор 231 (двунаправленный переключатель прямого тока второго двунаправленного переключателя 122).

В третий момент времени (t3) выключают первый транзистор 211 (двунаправленный переключатель прямого тока второго двунаправленного переключателя 121). Теперь первый двунаправленный переключатель 121 полностью выключен.

В четвертый момент времени (t4) включают четвертый транзистор 241 (двунаправленный переключатель обратного тока второго двунаправленного переключателя 122). Теперь второй двунаправленный переключатель 122 полностью включен и последовательность коммутации завершается.

Затем процедуру обращают, чтобы коммутировать предусматриваемое соединение м выходным узлом таким образом, что оно является снова обеспечиваемым посредством первого входного узла. То есть:

в пятый момент времени (t5) выключают четвертый транзистор 241;

в шестой момент времени (t6) включают первый транзистор 211;

в седьмой момент времени (t7) выключают третий транзистор 231;

в восьмой момент времени (t8) включают второй транзистор 221.

Вышеописанная последовательность коммутации не имеет ограничений, накладываемых на частоту или периоды времени, в которые можно переключать транзисторы. Таким образом, создается возможность, в соответствии с которой, когда требуются две встречно-параллельные коммутации, длительность времени (t5 - t4), в течение которого четвертый транзистор включен, может стать исключительно малой.

На фиг.4 иллюстрируется модифицированная последовательность 401 коммутации в соответствии с одним вариантом осуществления изобретения. Эта последовательность предусматривает такие же первые четыре момента времени, как описанные со ссылками на фиг.3. Вместе с тем, адаптирован четвертый момент времени, в который напряжение, прикладываемое к четвертому транзистору 241, удерживается в течение некоторого минимального периода времени (th), другое название которого - время удержания коммутации. Иными словами, транзистор должен оставаться включенным, по меньшей мере, в течение времени th. Этот минимальный период времени предпочтительно является не меньшим, чем 2,5 мкс, а опционально является не меньшим, чем 3,5 мкс. Поэтому четвертый транзистор 241 нельзя переключать, выключая-включая-выключая, менее, чем за минимальный период времени.

Вторая - обратная - последовательность 402 коммутации может возникать сразу же после окончания упомянутого минимального периода времени, так что пятый момент времени (т.е., момент, когда четвертый транзистор 241 выключают) может наступать сразу же после истечения минимального периода времени, следующего за включением четвертого транзистора в момент t4. В случае, если минимальный период времени составляет, например, не менее, чем 2,5 мкс, отсюда следует, что:

t5 - t4≥2,5 мкм (1)

Таким образом, следующая последовательность коммутации гарантирует, что ни один транзистор матричного преобразователя 1 не может быть выключен-включен-выключен или не может «пульсировать» с периодом включения (т.е., с длительностью времени включения транзистора), меньшим (меньшей), чем время удержания коммутации (предварительно определенный период времени), например - 2,5 мкс. Помимо этого, можно понять, что если переключение между любыми двумя двунаправленными переключателями всегда проводится вышеописанным образом, ни один транзистор не будет пульсировать, включаясь-выключаясь-включаясь с периодом времени выключения (т.е., с длительностью времени выключения транзистора), меньшим (меньшей), чем время удержания коммутации.

Поскольку управление напряжением, прикладываемым к транзисторам, можно осуществлять посредством программируемой пользователем вентильной матрицы (FPGA), отсюда следует, что каждый из моментов времени можно соотнести с «состоянием» конечного автомата. В этом случае, поскольку конечный автомат (т.е., FPGA) проходит через каждое состояние, каждый процесс проводят в соответственный момент времени. Следовательно, например - в четвертый момент времени, можно войти в состояние удержания, при этом проводить дополнительные процессы и выходить из состояния удержания нельзя до тех пор, пока не истечет установленный период времени. Следовательно, такая FPGA может обеспечить соответствие выдвигаемому требованию, заключающемуся в том, что ни один транзистор не должен пульсировать в пределах временного интервала, например, 2,5 мкс.

Надо отметить, что последовательности коммутации, описанные со ссылками на фиг.3 и 4, не ограничиваются переключением, обеспечивающими обратный и прямой ток, только между двунаправленными переключателями некоторой пары, а применимы к переключению между последовательностями любого количества двунаправленных переключателей. Например, возможны приложения, где запрашивается последовательность для коммутации с исходного первого двунаправленного переключателя на второй двунаправленный переключатель (например, последовательность t1 - t4), а затем со второго двунаправленного переключателя на третий двунаправленный переключатель (например, взамен t5 - t8). Вследствие этого, можно осуществить любое количество коммутаций, чтобы предоставить некоторому произвольному выходному узлу, о котором пойдет речь, произвольное количество двунаправленных переключателей.

Должно быть ясно, что, обеспечивая минимальное время переключения транзистора (например, > 2,5 мкс) также обеспечивают минимальное значение времени переключения двунаправленного переключателя (т.е., каждый двунаправленный переключатель может пульсировать, включаясь-выключаясь-включаясь, в течение ограниченного периода времени, например, > 2,5 мкс).

На фиг.5 изображен матричный преобразователь 5 в соответствии со вторым возможным вариантом осуществления. Матричный преобразователь 5 представляет собой матричный преобразователь трехфазного сигнала в трехфазный. Иными словами, матричный преобразователь 5 содержит: первый, второй и третий входные узлы 511, 512 и 513 для соединения с первой, второй и третьей фазами 501, 502 и 503 источника 500 напряжения; и первый, второй и третий выходные узлы 531, 532 и 533 для соединения с первой, второй и третей фазами нагрузки 540. Источник напряжения может быть, например, типичным источником питания от трехфазной сети. Нагрузка 540 может быть, например, индуктивной нагрузкой или емкостной нагрузкой, так что матричный преобразователь может содержать индуктивный порт или емкостной порт, или их оба.

Каждый выходной узел выполнен с возможностью соединения с каждым входным узлом посредством двунаправленного переключателя. Таким образом, посредством матричного преобразователя обеспечиваются в общей сложности девять (3 × 3) двунаправленных переключателей в виде матрицы. Первый, второй и третий конденсаторы 551 и 552, 553 обеспечивают цепь индуктивного тока каждой фазы.

Первый выходной узел 531 выполнен с возможностью соединения с первым, вторым и третьим входными узлами 511, 512 и 513 посредством первого, второго и третьего двунаправленных переключателей 5211, 5212 и 5213, соответственно. Второй выходной узел 532 выполнен с возможностью соединения с первым, вторым и третьим входным узлами 511, 512 и 513 посредством четвертого, пятого и шестого двунаправленных переключателей 5221, 5222 и 5223, соответственно. Третий выходной узел 533 выполнен с возможностью соединения с первым, вторым и третьим входным узлами 511, 512 и 513 посредством седьмого, восьмого и девятого двунаправленных переключателей 5231, 5232 и 5233, соответственно. В данном варианте осуществления, каждый двунаправленный переключатель имеет такую же конфигурацию, как продемонстрированная на фиг.2.

Ко второму варианту осуществления применимы те же ограничения, что и к первому. Иными словами, чтобы предотвратить междуфазные короткие замыкания (источника напряжения), никакие два двунаправленных переключателя, связанные с одиночным выходным узлом, не должны переключаться ни в какой заданный момент. Например, переключать в какой-либо заданный момент можно лишь один из нижеследующих: первый двунаправленный переключатель 5211; второй двунаправленный переключатель 5212; и третий двунаправленный переключатель 5213. Аналогичным образом, чтобы гарантировать наличие цепи индуктивного тока каждой фазы входного сигнала, ни один выходной узел 231, 232, 533 не следует отсоединять от каждого входного узла 511, 512, 513, тем самым предотвращая возникновение больших перенапряжений. Иными словами, каждый выходной узел 531, 532, 533 всегда должен быть соединен с фазой источника 500 напряжения. Эти два ограничения обеспечивают повышенную безопасность, надежность и долговечность приборов.

Чтобы модулировать подключение источника напряжения к нагрузке, можно использовать метод модуляции для определения тактирования переключения двунаправленных переключателей. Один известный способ управления переключением двунаправленных переключателей представляет собой метод пространственно-векторной модуляции (ПВМ). Два типичных метода или алгоритма ПВМ продемонстрированы на фиг.6 и фиг.7. На обоих этих чертежах, горизонтальная ось (ось Х) считается осью времени, а ссылки на вертикальную ось (ось Y) считаются указанием выходного узла, с которым связывают разные двунаправленные переключатели.

Методы ПВМ, иллюстрируемые посредством фиг.6 и 7, предусматривают применение некоторой повторяющейся последовательности (т.е., той последовательности, которая показана на соответственных чертежах) или периода модуляции, векторов к матрице двунаправленных переключателей для регулирования модуляции матричного преобразователя. Вектор можно понимать как содержащий информацию о том, какие двунаправленные переключатели активны или включены в некоторый заданный момент. Например, на фиг.6 сначала активен вектор «03». Это соответствует (как указано на фиг.6) третьему, шестому и девятому двунаправленным переключателям 5213, 5223 и 5233, находящимся во включенном состоянии.

«Активный вектор» определяется как вектор, в котором представлено выходное напряжение (т.е., напряжение есть между выходными узлами, по меньшей мере, одной пары). Например, вектор «-3» соответствует первому, шестому и девятому двунаправленным переключателям 5211, 5223 и 5233, находящимся во включенном состоянии. А если так, то первый выходной узел соединен с первым входным узлом, а второй и третий выходные узлы оба соединены с третьим входным узлом. Следовательно, между парами первого и второго выходных узлов и первого и третьего выходных узлов может существовать некоторая разность напряжений (причем каждая такая разность соответствует разности напряжений между первым и третьим входными узлами).

«Вектор» определяется как вектор, в котором не представлено выходное напряжение (т.е., напряжение в каждом выходном узле относительно опорного напряжения является одним и тем же). Возможный нулевой вектор представляет собой вышеупомянутый вектор «03», в соответствии с которым все три выходных узла соединены с третьим входным узлом. А если так, то разность напряжений между первым, вторым и третьим выходными узлами отсутствует или является пренебрежимо малой (поскольку каждый выходной узел находится под одним и тем же напряжением).

Промежуток времени (ширина импульсов), в течение которого каждый активный вектор применяется к матрице двунаправленных переключателей определит: средний угол и амплитуду выходного напряжения; и угол входного тока. Таким образом, если отслеживают входные напряжения фаз, угол входного тока ПВМ можно синхронизировать с подачей, а на входе может быть достигнут коэффициент рассогласования, равный единице. Аналогичным образом, если выходное напряжение и угол непрерывно изменяются, можно достичь желаемого синусоидального выходного сигнала.

Остающееся время в пределах периода модуляции, т.е., повторяющейся последовательности векторов, заполняется нулевыми векторами. Каждый нулевой вектор также имеет связанную с ним ширину импульсов, соответствующую промежутку времени, в течение которого каждый упомянутый нулевой вектор применяется к матрице двунаправленных переключателей. Следовательно, считать минимальной можно ширину импульсов, которая является шириной кратчайшего одиночного импульса любых активных или нулевых векторов, применяемых в периоде модуляции.

Индекс модуляции соответствует пропорции или доле периода модуляции, которая заполнена активными векторами. В типичном случае, индекс модуляции более 0,86 считается соответствующим перемодуляции в матричном преобразователе. Такой случай рассматривают как соответствующий теоретическому максимальному индексу модуляции, используемому в ПВМ, не вызывая искажение форм сигналов на входе или выходе.

На фиг.6 показан метод ПВМ, предусматривающий применение трех нулевых векторов (способ с 3-мя нулями) для осуществления полной модуляции. Иными словами, в пределах периода модуляции задействованы три разных нулевых вектора («01», «02» и «03»). «01» соответствует первому, четвертому и седьмому двунаправленных переключателей 5211, 5221 и 5231, являющиеся активными. «02» соответствует второму, пятому и восьмому двунаправленным переключателям 5212, 5222 и 5232, являющимся активными.

На фиг.7 показан метод ПВМ, предусматривает применение двух нулевых векторов (способ с 2-мя нулями) для осуществления полной модуляции. Иными словами, в пределах периода модуляции задействованы два разных нулевых вектора («03» и «02»).

В обоих представленных алгоритмах ПВМ применяются четыре активных вектора. «-3» соответствует первому, шестому и девятому двунаправленным переключателям 5211, 5221 и 5233, являющимся активными. «+9» соответствует первому, четвертому и девятому двунаправленным переключателям 5211, 5211 и 5233, являющимся активными. «-7» соответствует первому, четвертому и восьмому двунаправленным переключателям 5211, 5221 и 5232, являющимся активными. «+1» соответствует первому, пятому и восьмому двунаправленным переключателям 5211, 5222 и 5232, являющимся активными. Специалист в данной области техники поймет, что в рамках объема притязаний изобретения есть и другие возможные активные векторы.

Обращаясь к фиг.6, отмечаем, что, поскольку индекс модуляции увеличивается, минимальная ширина импульсов возникает, когда нулевой вектор «01» делается малым. Это может обуславливать требование малого времени выключения-включения-выключения от транзистора в одном из двунаправленных переключателей, реализуемое посредством алгоритма модуляции, что потенциально обуславливает неподходящее термическое напряжение внутри транзистора.

Аналогичным образом, обращаясь к фиг.7, отмечаем, что, поскольку активные векторы становятся малыми (например, находятся между «+9» и «-7»), может потребоваться малое время выключения-включения-выключения.

Вместе с тем, если переключение между разными двунаправленными переключателями, т.е., изменение прикладываемого вектора, проводится в соответствии с последовательностью коммутации, описанной со ссылками на фиг.4, можно избежать малого времени выключения-включения-выключения. А если так, то каждый вектор имеет абсолютную минимальную ширину импульсов, эквивалентную промежутку времени th. Этот промежуток времени предпочтительно является не меньшим, чем 2,5 мкс, опционально не меньшим, чем 3,5 мкс.

Длительность абсолютной минимальной ширины импульсов может зависеть, например, от тепловых характеристик двунаправленного переключателя. Например, если двунаправленные переключатели содержат биполярные транзисторы с изолированными затворами, этот промежуток времени может составлять 2,5 мкс. Более мощные приборы могут потребовать большей минимальной ширины импульсов. Аналогичным образом, менее мощные приборы могут потребовать лишь меньшей (чем 2,5 мкс) минимальной ширины импульсов возникает.

В одном примере, ограничение минимальной ширины импульсов значениями менее 2,5 мкс соответствует ограничению индекса модуляции матричного преобразователя значением 0,75 при использовании ПВМ с 3-мя нулями (фиг.6) на частоте переключения транзистора 12,5 кГц. Ограничение глубины модуляции в ПВМ с 3-мя нулями вынуждает принятие вектором 01, который разделяет «+9» и «-7», минимального значения (т.е., оно сохраняется в течение минимального промежутка времени), и предотвращает малые импульсы.

Поэтому можно заметить, что один способ ограничения минимальной ширины импульсов (а значит - и последовательности коммутации) может быть предусматривающим ограничение индекса модуляции матричного преобразователя значениями, не превышающими предварительно определенный максимальный индекс модуляции, например, 0,75. Опционально, индекс модуляции может быть ограничен значениями, меньшими, чем предварительно определенный минимальный индекс модуляции. В некоторых вариантах осуществления, возможны предварительно определенный максимальный индекс модуляции и предварительно определенный минимальный индекс модуляции.

При использовании ПВМ с 2-мя нулями (фиг.7), активные вектора «+9» и «-7» во время типичной работы могут становиться слишком малыми, а переключатель 5221 может переключаться, выключаясь-включаясь-выключаясь слишком быстро. Это может происходить, например, во время каждого изменения входного или выходного сектора, когда входной или выходной угол приближается к границе следующего сектора (например, каждые 60° фазы, скажем - когда между принадлежащими некоторой паре фазами трехфазного входного сигнала существует пересечение). Ограничение промежутка времени, в течение которого может переключаться какой-либо заданный транзистор и которое ограничивает минимальную ширину импульсов двунаправленного переключателя, смягчает этот эффект.

Вместе с тем, один эффект ограничения индекса модуляции или минимальной ширины импульсов может заключаться в том, что максимальное выходное напряжение преобразователя можно ограничить. В модулируемый сигнал может быть внесено искажение, поскольку реальный выходной сигнал может больше не быть таким же, как желаемый выходной сигнал в случае, если малые вектора удлиняются, поскольку любые изменения, возникающие в требуемом выходном сигнале на протяжении времени, соответствующем минимальной ширине импульсов, будут утрачены.

На фиг.8 представлен смоделированный график полного коэффициента гармоник (ПКГ) сигнала выходного тока (ось Y) на протяжении увеличивающегося индекса модуляции (по оси Х вплоть до максимального значения единица), как для способа 81 ПВМ с 3-мя нулями, так и для способа 82 ПВМ с 2-мя нулями. Минимальный период времени между переключениями какого-либо транзистора устанавливают равным возможному значению 1 мкс. Можно заметить, что ПКГ в общем случае уменьшается по мере увеличения индекса модуляции. Вместе с тем, когда индекс модуляции достигает примерно 0,8, вынуждается ограниченная ширина импульсов (т.е., 1 мкс), а если так, то модулируемый выходной сигнал искажается. Соответственно, ПКГ увеличивается.

На фиг.9 изображен смоделированный график полного коэффициента гармоник (ПКГ) сигнала выходного тока (ось Y) на протяжении увеличивающегося времени удержания коммутации (по оси Х вплоть до максимального значения 5 мкс). Для моделирования устанавливали максимальный индекс модуляции 0,77. Моделировали как способ 91 ПВМ с 3-мя нулями, так и способ 92 ПВМ с 2-мя нулями. В случае способа 91 ПВМ с 3-мя нулями существует общая положительная динамика для ПКГ по мере увеличения времени удержания коммутации. Вместе с тем, способ 92 ПВМ с 2-мя нулями, по существу, сохраняет уровень. Поэтому в некоторых приложениях, способ с 2-мя нулями, предусматривающий некоторое время удержания коммутации (например, > 2,5 мкс), может зарекомендовать себя как более эффективный способ модуляции.

Максимальным значением, которое можно установить для минимального времени удержания, может быть период времени 5 мкс.

На фиг.10 изображен смоделированный график полного коэффициента гармоник (ПКГ) сигнала входного тока (ось Y) на протяжении увеличивающегося времени удержания коммутации (по оси Х вплоть до максимального значения единица), как для способа 1001 ПВМ с 3-мя нулями, так и для способа 1002 ПВМ с 2-мя нулями. И опять, минимальный период времени между переключениями какого-либо транзистора устанавливают равным возможному значению 1 мкс. Можно заметить, что спектральная характеристика способа с 2-мя нулями значительно лучше, чем у способа с 3-мя нулями, почти во всех рабочих точках. Помимо этого, полный коэффициент гармоник согласно способу с 3-мя нулями ухудшается по мере наложения ограниченной ширины импульсов (т.е., 1 мкс) (когда индекс модуляции больше 0,8). ПКГ согласно обоим способам значительно ухудшается при вхождении в область перемодуляции (> 0,86).

На фиг.11 представлен смоделированный график полного коэффициента гармоник (ПКГ) сигнала входного тока (ось Y) на протяжении увеличивающегося времени удержания коммутации (по оси Х вплоть до максимального значения 5 мкс). Для моделирования устанавливали максимальный индекс модуляции 0,77, и моделировали как способ 1101 ПВМ с 3-мя нулями, так и способ 1102 ПВМ с 2-мя нулями. Можно опять заметить, что результаты осуществления способа с 2-мя нулями дают улучшенный ПКГ, а значит - и улучшенную рабочую характеристику, по сравнению со способом с 3-мя нулями.

Рабочая характеристика метода пространственно-векторной модуляции с 2-мя нулями, продемонстрирована выше как обеспечивающая значительные повышения качества модулируемого сигнала. Поэтому может оказаться предпочтительной разработка матричного преобразователя, который работает по методу пространственно-векторной модуляции с 2-мя нулями и имеет последовательность коммутации с некоторым временем удержания коммутации.

Хотя это не обсуждалось, в рамках объема притязаний этого изобретения можно использовать и другие способы пространственно-векторной модуляции, такие, как метод ПВМ с одним нулем.

На фиг.12 изображена блок-схема последовательности операций для последовательности коммутации между первым и вторым двунаправленными переключателями, обеспечиваемыми изобретением. Последовательность коммутации предусматривает переключение двунаправленного соединения с выходным узлом с первого входного узла на второй входной узел, причем первый входной узел выполнен с возможностью соединения с выходным узлом первого двунаправленного переключателя, содержащим первый транзистор и первый диод, скомпонованные последовательно и второй транзистор и второй диод, скомпонованные последовательно, причем первый и второй транзисторы скомпонованы друг за другом, а второй входной узел выполнен с возможностью соединения с выходным узлом второго двунаправленного переключателя, содержащим третий транзистор и третий диод, скомпонованные последовательно, и четвертый транзистор и четвертый диод, скомпонованные последовательно, причем третий и четвертый транзисторы скомпонованы друг за другом, при этом проводимостью каждого транзистора управляет контроллер, переключая ее между более высокой при включении и более низкой при выключении.

Сначала - 1201 - как первый, так и второй транзисторы включены, и поэтому первый двунаправленный переключатель включен. Помимо этого, в тот же начальный момент, как третий, так и четвертый транзисторы выключены, и поэтому второй двунаправленный переключатель выключен.

В первый момент времени 1202 выключают первый транзистор;

во второй момент времени 1203 включают третий транзистор;

в третий момент времени 1204 выключают второй транзистор;

в четвертый момент времени 1205 выключают и блокируют четвертый транзистор, оставляя его включенным;

в пятый момент времени 1206, деблокируют четвертый транзистор и получают возможность выключить его, причем пятый момент времени наступает после четвертого момента времени не раньше, чем по истечении предварительно определенного периода времени.

Этот предварительно определенный период времени может составлять, например, не менее 2,5 мкс, например - не менее 3,5 мкс.

Как пояснялось выше, FPGA можно использовать для определения конечного автомата, который управляет последовательностью состояний переключения. Фактическими периодами времени между значениями переключаемых состояний может управлять, например, микроконтроллер, или они могут быть фиксированными.

Изучив чертежи, описание и прилагаемую формулу изобретения, специалисты в области практического осуществления изобретения смогут понять и внести другие изменения в раскрытые варианты осуществления. Специалисту в данной области техники будут известны двунаправленные переключатели, отличающиеся от раскрытых здесь в явном виде, например - двунаправленно переключающий элемент на основе диодного моста. В формуле изобретения, слово «содержащий» не исключает другие элементы или этапы, а признак единственного числа не исключает множество. Сам факт, что некоторые меры приводятся во взаимно различных зависимых пунктах формулы изобретения, не исключает возможность с выгодой использовать комбинацию этих мер. Любые позиции чертежей в формуле изобретения не следует считать ограничивающими объем притязаний.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ МОЩНОСТИ | 2012 |

|

RU2558749C1 |

| УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ МОЩНОСТИ | 2012 |

|

RU2570804C2 |

| УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ МОЩНОСТИ | 2012 |

|

RU2559042C1 |

| УСТРОЙСТВО И СПОСОБ УПРАВЛЕНИЯ ОБРАТИМЫМ ПРЕОБРАЗОВАТЕЛЕМ ЭНЕРГИИ ПЕРЕМЕННОГО ТОКА В ЭНЕРГИЮ ПЕРЕМЕННОГО ТОКА | 2002 |

|

RU2265947C2 |

| ИНВЕРТОР С ПРЯМЫМ МОСТОМ ПЕРЕМЕННОГО ТОКА И УЛУЧШЕННОЙ ТОПОЛОГИЕЙ ПРЕОБРАЗОВАНИЯ ПОСТОЯННОГО ТОКА В ПЕРЕМЕННЫЙ | 2018 |

|

RU2761179C2 |

| СИЛОВОЙ МОДУЛЬ | 2012 |

|

RU2503118C1 |

| Способ управления матричным преобразователем частоты | 2016 |

|

RU2641653C1 |

| СПОСОБ КОММУТАЦИИ ТОКА КЛЮЧАМИ ДВУХСТОРОННЕЙ ПРОВОДИМОСТИ МАТРИЧНЫХ ПРЕОБРАЗОВАТЕЛЕЙ (ВАРИАНТЫ) | 2002 |

|

RU2231191C2 |

| СПОСОБ УПРАВЛЕНИЯ ВХОДНЫМ/ВЫХОДНЫМ РЕЖИМОМ В УСТРОЙСТВЕ ПРЯМОГО ПРЕОБРАЗОВАНИЯ ПЕРЕМЕННОГО ТОКА В ПЕРЕМЕННЫЙ ТОК | 2007 |

|

RU2377711C1 |

| СИСТЕМА И СПОСОБ КОНТРОЛЯ ПОДАЧИ ЭЛЕКТРОЭНЕРГИИ | 2010 |

|

RU2538904C2 |

Изобретение относится к преобразователям переменного тока в переменный, в которых используется матрица переключателей для преобразования первого сигнала переменного тока (любого числа фаз) во второй сигнал переменного тока (любого числа фаз) с произвольной амплитудой и частотой, и предназначено для обеспечения возможности, в соответствии с которой разница в периоде времени между первым состоянием переключения двунаправленного переключателя и вторым состоянием переключения двунаправленного переключателя будет минимальной. Такого минимального периода переключения транзистора можно добиться путем внесения задержки в последовательность переключения, которую, как правило, используют для переключения выхода с первого входа на второй вход. 3 н. и 12 з.п. ф-лы, 12 ил.

1. Матричный преобразователь (1), содержащий:

m входных узлов (111, 112) для соединения с m-фазным источником (100) напряжения, где m равно по меньшей мере единице;

n выходных узлов (130) для соединения с n-фазной нагрузкой, где n равно по меньшей мере единице и по меньшей мере одно из m или n равно двум или более;

m × n двунаправленных переключателей (121, 122), причем каждый двунаправленный переключатель подсоединен между одиночным входным узлом и одиночным выходным узлом, так что каждый выходной узел выполнен с возможностью избирательного соединения с каждым входным узлом посредством двунаправленного переключателя; и

контроллер, подсоединенный с возможностью управления проводимостью упомянутых двунаправленных переключателей таким образом, что двунаправленное соединение между каждым входным узлом и каждым выходным узлом является избирательно управляемым,

причем контроллер выполнен так, что минимальный период времени между изменением проводимости любого одиночного двунаправленного переключателя является не меньшим, чем предварительно определенный период времени.

2. Матричный преобразователь по п.1, в котором:

каждый двунаправленный переключатель содержит по меньшей мере один транзистор;

контроллер подсоединен с возможностью управления проводимостью каждого транзистора и

контроллер выполнен так, что минимальный период времени между изменением проводимости любого одиночного транзистора является не меньшим, чем упомянутый предварительно определенный период времени.

3. Матричный преобразователь по любому из пп.1 и 2, в котором контроллер содержит программируемую пользователем вентильную матрицу, FPGA.

4. Матричный преобразователь по любому предыдущему пункту, в котором предварительно определенный период времени зависит от n-фазной нагрузки, возбуждаемой выходными узлами.

5. Матричный преобразователь по любому предыдущему пункту, в котором по меньшей мере один конденсатор (103) подсоединен между каждым из входных узлов.

6. Матричный преобразователь по любому предыдущему пункту, в котором каждый выходной узел является двунаправленно соединенным лишь с одним входным узлом одновременно.

7. Матричный преобразователь по любому предыдущему пункту, в котором каждый двунаправленный переключатель (121) содержит:

первый транзистор (211) и первый диод (212), скомпонованные последовательно; и

второй транзистор (221) и второй диод (222), скомпонованные последовательно,

причем первый и второй транзисторы скомпонованы друг за другом, так что двунаправленный переключатель сконфигурирован с возможностью обеспечивать первое однонаправленное соединение от соответствующего входного узла к соответствующему выходному узлу или второе однонаправленное соединение от упомянутого выходного узла к соответствующему входному узлу.

8. Матричный преобразователь по п.7, в котором каждый выходной узел однонаправленно соединен не более чем с двумя входными узлами одновременно.

9. Матричный преобразователь по любому предыдущему пункту, в котором контроллер дополнительно выполнен так, что предварительно определенный период времени является не меньшим, чем 2,5 мкс.

10. Матричный преобразователь по любому предыдущему пункту, в котором контроллер дополнительно выполнен так, что предварительно определенный период времени является не меньшим, чем 3,5 мкс.

11. Матричный преобразователь по любому из пп.3-10, дополнительно содержащий микроконтроллер, соединенный с FPGA, причем этот микроконтроллер выполнен с возможностью выбора того входного узла, с которым двунаправленно соединен выходной узел.

12. Способ переключения двунаправленного соединения с выходным узлом от первого входного узла ко второму входному узлу, причем первый входной узел выполнен с возможностью соединения с выходным узлом первого двунаправленного переключателя, содержащего первый транзистор и первый диод, скомпонованные последовательно, и второй транзистор и второй диод, скомпонованные последовательно, причем первый и второй транзисторы скомпонованы друг за другом, а второй входной узел выполнен с возможностью соединения с выходным узлом посредством второго двунаправленного переключателя, содержащего третий транзистор и третий диод, скомпонованные последовательно, и четвертый транзистор и четвертый диод, скомпонованные последовательно, причем третий и четвертый транзисторы скомпонованы друг за другом, при этом проводимостью каждого транзистора управляет контроллер, переключая ее между более высокой при включении и более низкой при выключении, причем в исходном состоянии (1201) первый и второй транзисторы оба включены, а третий и четвертый транзисторы оба выключены, при этом способ содержит этапы, на которых:

в первый момент времени (1202) выключают первый транзистор;

во второй момент времени (1203) включают третий транзистор;

в третий момент времени (1204) выключают второй транзистор;

в четвертый момент времени (1205) включают четвертый транзистор;

отличающийся тем, что способ содержит этапы, на которых:

в четвертый момент времени блокируют четвертый транзистор, оставляя его включенным;

в пятый момент времени (1206) деблокируют четвертый транзистор, причем пятый момент времени наступает после четвертого момента времени не раньше, чем по истечении предварительно определенного периода времени.

13. Способ по п.12, в котором имеется предварительно определенный максимальный период времени, по меньшей мере, между одними из следующих: первым и вторым моментами времени; вторым и третьим моментами времени; и третьим и четвертым моментами времени.

14. Способ по любому из пп.12 или 13, в котором контроллер представляет собой программируемую пользователем вентильную матрицу.

15. Способ эксплуатации матричного преобразователя, имеющего по меньшей мере один выходной узел и по меньшей мере два входных узла, причем каждый выходной узел является двунаправленно соединенным с каждым входным узлом посредством двунаправленного переключателя, при этом способ содержит этап, на котором:

используют метод пространственно-векторной модуляции для управления порядком переключения двунаправленных соединений между упомянутым по меньшей мере одним выходным узлом и упомянутыми по меньшей мере двумя входными узлами,

причем этап переключения двунаправленного соединения осуществляют по любому из пп.12-14.

| JP 2013106467 A, 30.05.2013 | |||

| US 2015130431 A1, 14.05.2015 | |||

| Способ защиты переносных электрических установок от опасностей, связанных с заземлением одной из фаз | 1924 |

|

SU2014A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ И РЕГУЛИРОВАНИЯ НАПРЯЖЕНИЯ МАТРИЧНОГО НЕПОСРЕДСТВЕННОГО ПРЕОБРАЗОВАТЕЛЯ ЧАСТОТЫ С ВЫСОКОЧАСТОТНОЙ СИНУСОИДАЛЬНОЙ ШИМ | 2010 |

|

RU2422975C1 |

Авторы

Даты

2019-11-06—Публикация

2016-05-13—Подача