Изобретение относится к устройствам передачи информационного сигнала и может найти применение в системах управления, контроля, измерения, вычислительных устройствах, устройствах связи различных отраслей техники.

Известна линия задержки, описанная, например, в [1] содержащая несколько последовательно включенных схем НЕ. К недостаткам такого устройства следует отнести необходимость управления потенциальным сигналом и наличие только одного выхода, что не позволяет осуществлять различную по времени задержку импульсного сигнала при передаче его на несколько управляемых линий.

Известно также устройство, описанное, например, в [2] содержащее двоичный счетчик импульсов и дешифратор с множеством выходов. Устройство позволяет подсчитывать импульсы, поступающие от внешнего генератора, и передавать их с задержкой на выходы. Такое устройство требует дополнительные элементы для восприятия импульсного управляющего сигнала и передачи его на несколько управляемых линий с различным временем задержки.

В качестве прототипа принято устройство, описанное в [2]

Целью настоящего изобретения является расширение функциональных возможностей, а именно возможность изменять время задержки прохождения импульсного сигнала и его длительность после реализации задержки, а также возможность передачи его с различными задержками на несколько выходных линий.

Поставленная цель достигается тем, что в устройство введены основной D-триггер, управляющий генератором прямоугольных импульсов, двоичный счетчик импульсов, дешифратор, две схемы ИЛИ, схема ИЛИ-НЕ, а также несколько идентичных выходных устройств (ячеек), каждая из которых содержит D-триггер, схему И и схему НЕ.

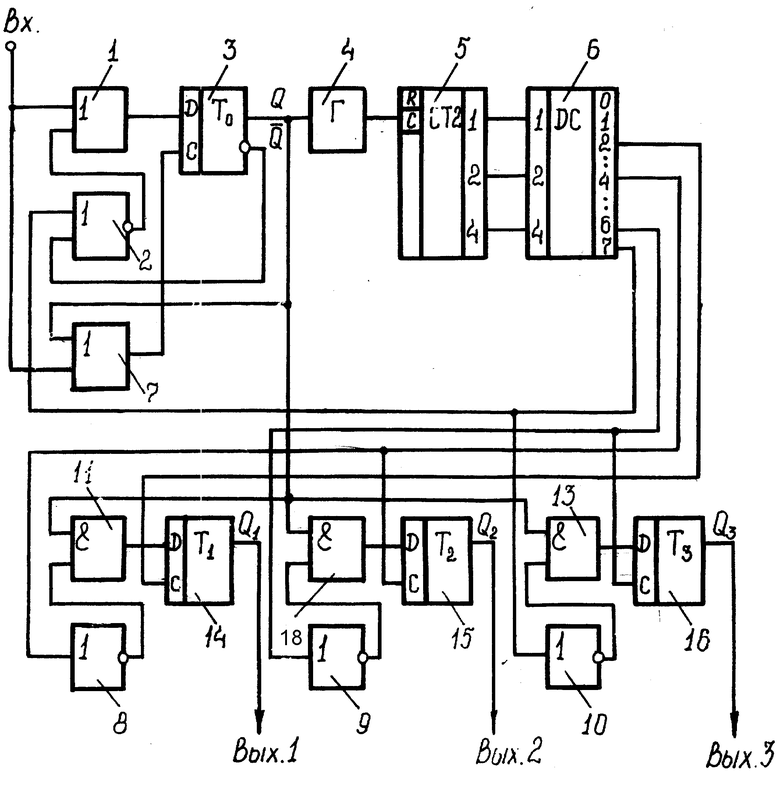

На чертеже приведена схема линии задержки на три выхода. Вход ВХ устройства подключен к одному из входов двухвходовой схемы ИЛИ 1, ко второму воду которой подключена выходом двухвходовая схема ИЛИ-НЕ 2. Выход схемы ИЛИ 1 подключен к D входу однотактного D-триггера Т0 3, выход Q которого подключен к генератору прямоугольных импульсов Г 4, выход которого, в свою очередь, подключен ко входу C двоичного счетчика СТ2 5. Двоичные выходы счетчика СТ2 подключены к соответствующим входам дешифратора ДС 6. Выход Q триггера Т0 3 подключен также к одному из входов схемы ИЛИ 7, к второму входу которой подключен вход Вх устройства, а выход ко входу C триггера Т0 3, причем его выход  подключен к одному из входов схемы ИЛИ-НЕ 2. Последний используемый выход дешифратора ДС 6 подключен к второму входу схемы ИЛИ-НЕ 2, а также к входам, например трех схем НЕ 8, 9 И 10, каждая из которых содержится, например, в трех выходных ячейках устройства. Выходы схем НЕ соединены с одним из входов схемы И 11, 12 и 13 соответственно своей выходной ячейки, выходы которых подключены ко входам D своих триггеров Т1, Т2 и Т3 14, 15 и 16, а их выходы Qi к выходам устройства Вых1, Вых2, Вых3 соответственно. Первый используемый выход, например 2, дешифратора ДС 6 подключен к входу C триггера Т1 14 первой выходной ячейки, второй, например 4, к входу C триггера Т2 15 второй выходной ячейки и к входу схемы НЕ 8, а третий, например 6, к входу C триггера Т3 16 третьей выходной ячейки и к входу схемы НЕ 9. Выходы дешифратора ДС выбираются в зависимости от требуемой длительности задержки времени передачи сигнала на выходные линии и длительностей выходных сигналов, величина которых задается посредством схем НЕ 8, 9 и 10.

подключен к одному из входов схемы ИЛИ-НЕ 2. Последний используемый выход дешифратора ДС 6 подключен к второму входу схемы ИЛИ-НЕ 2, а также к входам, например трех схем НЕ 8, 9 И 10, каждая из которых содержится, например, в трех выходных ячейках устройства. Выходы схем НЕ соединены с одним из входов схемы И 11, 12 и 13 соответственно своей выходной ячейки, выходы которых подключены ко входам D своих триггеров Т1, Т2 и Т3 14, 15 и 16, а их выходы Qi к выходам устройства Вых1, Вых2, Вых3 соответственно. Первый используемый выход, например 2, дешифратора ДС 6 подключен к входу C триггера Т1 14 первой выходной ячейки, второй, например 4, к входу C триггера Т2 15 второй выходной ячейки и к входу схемы НЕ 8, а третий, например 6, к входу C триггера Т3 16 третьей выходной ячейки и к входу схемы НЕ 9. Выходы дешифратора ДС выбираются в зависимости от требуемой длительности задержки времени передачи сигнала на выходные линии и длительностей выходных сигналов, величина которых задается посредством схем НЕ 8, 9 и 10.

Использование двух схем ИЛИ и схемы ИЛИ-НЕ, для последовательного включения и выключения D-триггера устройства и применение дешифратора для управления D-триггерами выходных ячеек посредством схем НЕ, И в источниках не обнаружено.

Устройство работает следующим образом. В исходном состоянии все триггеры находятся в состоянии Q=0;  1 (выключены), а запись в двоичном счетчике счета (счетчик "обнулен").

1 (выключены), а запись в двоичном счетчике счета (счетчик "обнулен").

При поступлении кратковременного управляющего сигнала на вход Вх устройства, он передается через схему ИЛИ 1 на вход D-триггера Т0 3 и одновременно через схему ИЛИ 7 на его вход C. Триггер переключается в состояние Q 1;  0 (включается), включая в работу генератор прямоугольных импульсов Г 4. Прямоугольные импульсы, генерируемые им, подаются на вход C двоичного счетчика СТ2 5, подсчитывающего и преобразующего их десятичное число в двоичный код, который, в свою очередь, передается на дешифратор ДС 6. Одновременно сигнал с выхода Q триггера Т0 3 поступает через схемы И 11, 12 и 13 на входы D триггеров Т1, Т2 и Т3 14, 15 и 16 выходных ячеек, подготавливая их к переключению, а также через схему ИЛИ 7 на вход C триггера Т0 3 устройства. Нулевой логический сигнал

0 (включается), включая в работу генератор прямоугольных импульсов Г 4. Прямоугольные импульсы, генерируемые им, подаются на вход C двоичного счетчика СТ2 5, подсчитывающего и преобразующего их десятичное число в двоичный код, который, в свою очередь, передается на дешифратор ДС 6. Одновременно сигнал с выхода Q триггера Т0 3 поступает через схемы И 11, 12 и 13 на входы D триггеров Т1, Т2 и Т3 14, 15 и 16 выходных ячеек, подготавливая их к переключению, а также через схему ИЛИ 7 на вход C триггера Т0 3 устройства. Нулевой логический сигнал  0 триггера Т0 3 поступает на один из входов схемы ИЛИ-НЕ 2, на втором входе которой также существует нулевой сигнал, снимаемый с последнего используемого выхода дешифратора ДС 6. С выхода схемы ИЛИ-НЕ 2 единичный сигнал через схему ИЛИ 1 передается на вход D-триггера Т0 3, удерживая его во включенном состоянии. После этого момента управляющий сигнал может быть снят.

0 триггера Т0 3 поступает на один из входов схемы ИЛИ-НЕ 2, на втором входе которой также существует нулевой сигнал, снимаемый с последнего используемого выхода дешифратора ДС 6. С выхода схемы ИЛИ-НЕ 2 единичный сигнал через схему ИЛИ 1 передается на вход D-триггера Т0 3, удерживая его во включенном состоянии. После этого момента управляющий сигнал может быть снят.

При подсчете первого заданного числа импульсов сигнал с соответствующего выхода дешифратора ДС 6, например 2, передается на вход C триггера Т1 14, который переключается в состояние Q 1,  0 (включается), осуществляя задержку сигнала на выходе Вых1, соответствующую времени подсчета двух импульсов (в данном варианте) генератора. При подсчете второго заданного числа импульсов, например 4, сигнал с дешифратора ДС 6 подается на вход C триггера Т2 15, который, включаясь, осуществляет подачу сигнала на выход Вых 2 с соответствующей задержкой во времени. При этом тот же сигнал с дешифратора поступает через схему НЕ 8 и схему И 11 в инверторном виде (нулевым) на вход D-триггера Т1 14, возвращая его в состояние Q1 0 и выключая сигнал на выходе Вых. 1. Выключение выходного сигнала может осуществляться и любым другим сигналом, снимаемым с дешифратора или другого элемента системы управления. Аналогично задерживается и следующий сигнал на выходе Вых.3, включение которого осуществляется подачей сигнала с выхода дешифратора СД 6, например 6, на вход C триггера Т3 16. Одновременно осуществляется выключение сигнала на выходе Вых.2 подачей сигнала на вход D-триггера Т2 15 в инверсной форме через схему НЕ 9 и схему И 12. Последний сигнал, заканчивающий серию задержек, снимается с выхода дешифратора ДС 6, например 7, выключает сигнал на выходе Вых. 3 через схему НЕ 10 и схему И 13 и одновременно через схему ИЛИ-НЕ 2 и схему ИЛИ 1 поступает на вход D-триггера Т0 3, переключая его в состояние Q 0;

0 (включается), осуществляя задержку сигнала на выходе Вых1, соответствующую времени подсчета двух импульсов (в данном варианте) генератора. При подсчете второго заданного числа импульсов, например 4, сигнал с дешифратора ДС 6 подается на вход C триггера Т2 15, который, включаясь, осуществляет подачу сигнала на выход Вых 2 с соответствующей задержкой во времени. При этом тот же сигнал с дешифратора поступает через схему НЕ 8 и схему И 11 в инверторном виде (нулевым) на вход D-триггера Т1 14, возвращая его в состояние Q1 0 и выключая сигнал на выходе Вых. 1. Выключение выходного сигнала может осуществляться и любым другим сигналом, снимаемым с дешифратора или другого элемента системы управления. Аналогично задерживается и следующий сигнал на выходе Вых.3, включение которого осуществляется подачей сигнала с выхода дешифратора СД 6, например 6, на вход C триггера Т3 16. Одновременно осуществляется выключение сигнала на выходе Вых.2 подачей сигнала на вход D-триггера Т2 15 в инверсной форме через схему НЕ 9 и схему И 12. Последний сигнал, заканчивающий серию задержек, снимается с выхода дешифратора ДС 6, например 7, выключает сигнал на выходе Вых. 3 через схему НЕ 10 и схему И 13 и одновременно через схему ИЛИ-НЕ 2 и схему ИЛИ 1 поступает на вход D-триггера Т0 3, переключая его в состояние Q 0;  1. Генератор импульсов Г 4 выключается и устройство прекращает работу. Помимо последнего сигнала, снимаемого с дешифратора ДС 6, выключение устройства может осуществляться сигналом от другого элемента системы управления. Время задержки и длительность задержанных сигналов определяется частотой генератора. Число разрядов двоичного счетчика и дешифратора принимается в зависимости от максимального времени задержки и длительности выходных сигналов.

1. Генератор импульсов Г 4 выключается и устройство прекращает работу. Помимо последнего сигнала, снимаемого с дешифратора ДС 6, выключение устройства может осуществляться сигналом от другого элемента системы управления. Время задержки и длительность задержанных сигналов определяется частотой генератора. Число разрядов двоичного счетчика и дешифратора принимается в зависимости от максимального времени задержки и длительности выходных сигналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТАЙМЕР | 1996 |

|

RU2100901C1 |

| ЛИНИЯ ЗАДЕРЖКИ | 1996 |

|

RU2117387C1 |

| ЛИНИЯ ЗАДЕРЖКИ | 1996 |

|

RU2103813C1 |

| СЕЛЕКТОРНЫЙ ПЕРЕКЛЮЧАТЕЛЬ ЭЛЕКТРИЧЕСКИХ ЦЕПЕЙ | 1997 |

|

RU2118044C1 |

| ТАЙМЕР | 1997 |

|

RU2130692C1 |

| ФОРМИРОВАТЕЛЬ ГРУППЫ ИМПУЛЬСОВ | 1996 |

|

RU2103807C1 |

| ЛИНИЯ ЗАДЕРЖКИ СИГНАЛА | 1998 |

|

RU2130231C1 |

| ТАЙМЕР | 1996 |

|

RU2103808C1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ РЕВЕРСИВНЫЙ ДВОИЧНЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1997 |

|

RU2115227C1 |

| РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ ТОКА | 1996 |

|

RU2124817C1 |

Линия задержки относится к устройствам передачи информационного сигнала и может найти применение в системах управления, контроля, измерения, вычислительных устройствах, устройствах связи и других устройствах различных отраслей техники. Линия связи содержит D-триггер, управляемый посредством схем ИЛИ, ИЛИ-НЕ, генератор прямоугольных импульсов, двоичный счетчик импульсов и дешифратор. Устройство имеет несколько выходных каналов, каждый из которых содержит D-триггер, управляемый схемами И и НЕ. Линия связи позволяет сдвигать по времени импульсный сигнал, передавая его на несколько выходов с различными временными задержками, величина которых вариантна. 1 ил.

Линия задержки, содержащая вход и по меньшей мере два выхода, двоичный счетчик импульсов, выходы которого поразрядно соединены с входами дешифратора, отличающаяся тем, что в устройство дополнительно введены генератор импульсов, однотактный D-триггер, две двухвходовые схемы ИЛИ и двухвходовая схема ИЛИ-НЕ, а также по меньшей мере две одинаковые выходные ячейки, состоящие из однотактного D-триггера, двухвходовй схемы И и схемы НЕ, при этом вход D однотактного D-триггера соединен с выходом двухвходовой схемы ИЛИ, один из входов которой соединен с входом устройства, а другой с выходом двухвходовой схемы ИЛИ-НЕ, один из входов которой соединен с последним используемым выходом дешифратора, а другой с выходом  однотактного D-триггера, выход Q которого соединен с входом генератора импульсов, выход которого соединен с входом C двоичного счетчика импульсов, выходы дешифратора соединены с C входами однотактовых D-триггеров выходных ячеек, вход C однотактного D-триггера соединен с выходом двухвходовой схемы ИЛИ, один из входов которой соединен с входом устройства, а другой с выходом Q однотактного D-триггера, при этом вход D однотактного D-триггера каждой выходной ячейки соединен с выходом двухвходовой схемы И, один из входов которой соединен с выходом Q однотактного D-триггера, а другой с выходом схемы НЕ, вход которой соединен с соответствующими выходами дешифратора, при этом выход Qi однотактного D-триггера каждой выходной ячейки соединен с соответствующим выходом устройства.

однотактного D-триггера, выход Q которого соединен с входом генератора импульсов, выход которого соединен с входом C двоичного счетчика импульсов, выходы дешифратора соединены с C входами однотактовых D-триггеров выходных ячеек, вход C однотактного D-триггера соединен с выходом двухвходовой схемы ИЛИ, один из входов которой соединен с входом устройства, а другой с выходом Q однотактного D-триггера, при этом вход D однотактного D-триггера каждой выходной ячейки соединен с выходом двухвходовой схемы И, один из входов которой соединен с выходом Q однотактного D-триггера, а другой с выходом схемы НЕ, вход которой соединен с соответствующими выходами дешифратора, при этом выход Qi однотактного D-триггера каждой выходной ячейки соединен с соответствующим выходом устройства.

| Гольденберг Л.М | |||

| Импульсные устройства | |||

| - М.: Радио и связь, 1981, с | |||

| Халат для профессиональных целей | 1918 |

|

SU134A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Бирюков С.А | |||

| Цифровые устройства на интегральных микросхемах | |||

| - М.: Радио и связь, 1987, с | |||

| Способ подготовки рафинадного сахара к высушиванию | 0 |

|

SU73A1 |

| Клапанный регулятор для паровозов | 1919 |

|

SU103A1 |

Авторы

Даты

1997-12-27—Публикация

1996-12-03—Подача