Изобретение относится к области радиотехники и может быть использовано в устройствах приема аналоговых информационных сигналов с фазовой модуляцией и для выделения (измерения) фазового сдвига принимаемого и опорного сигналов в системах фазовой синхронизации.

Известен аналоговый фазовый детектор [1], в котором входной и опорный сигналы обрабатываются двухзатворным полевым транзистором. Его недостатком является приближенная нелинейная аналоговая обработка сигналов и высокая погрешность оценки сдвига фаз.

Известен фазовый детектор [2], в котором выполняется преобразование фазового сдвига в интервал времени и измерение интервала времени методом дискретного счета высокочастотных тактовых импульсов. Недостатком указанной схемы является то, что для корректного определения фазовых сдвигов требуется априорная информация о знаке временного рассогласования сигналов.

Близким к предлагаемому устройству является цифровой фазовый детектор [3], в котором проводится обработка комплексных отсчетов принимаемого и опорного сигналов с формированием сигнала, пропорционального удвоенной фазовой ошибке. Его недостатками являются необходимость обеспечения идентичности каналов формирования комплексных отсчетов, отсутствие усреднения результатов при медленном изменении фазового сдвига и собственной частотной селективности детектора, что приводит к искажению результата и ухудшению помехоустойчивости.

Наиболее близким по технической сущности и внутренней структуре к предлагаемому устройству является цифровой обнаружитель узкополосных сигналов [4], способный выполнять функции амплитудного детектора. Его недостатком является отсутствие возможности фазового детектирования принимаемого и опорного сигналов.

Задачей предлагаемого технического решения является обеспечение высокоскоростного цифрового фазового детектирования принимаемого сигнала с высокой помехоустойчивостью и устранением неидентичности квадратурных каналов обработки сигнала.

Поставленная задача решается тем, что цифровой фазовый детектор, содержащий аналого-цифровой преобразователь (АЦП), регистр сдвига многоразрядных кодов на четыре отсчета, первый и второй n-каскадные каналы квадратурной обработки (ККО) сигналов и генератор тактовых импульсов (ГТИ), дополнительно содержит нормирующее устройство (НУ), цифровой формирователь (ЦФ) арктангенса и блок коррекции фазы (КФ), первый и второй информационные входы НУ соединены с выходами первого и второго ККО, выход НУ подключен к входу ЦФ, выход которого соединен с входом КФ, на выходе которого формируется двоичный код сдвига фаз принимаемого сигнала относительно импульсов ГТИ.

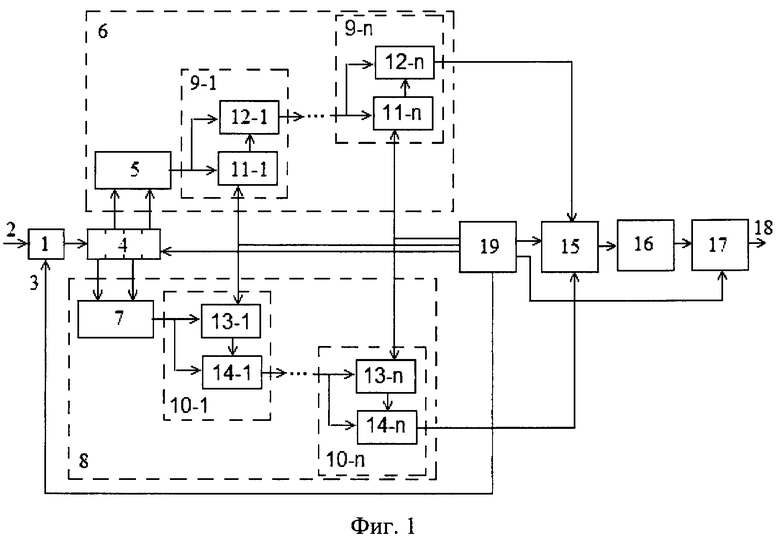

Предлагаемое техническое решение поясняется чертежами.

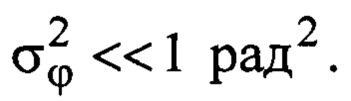

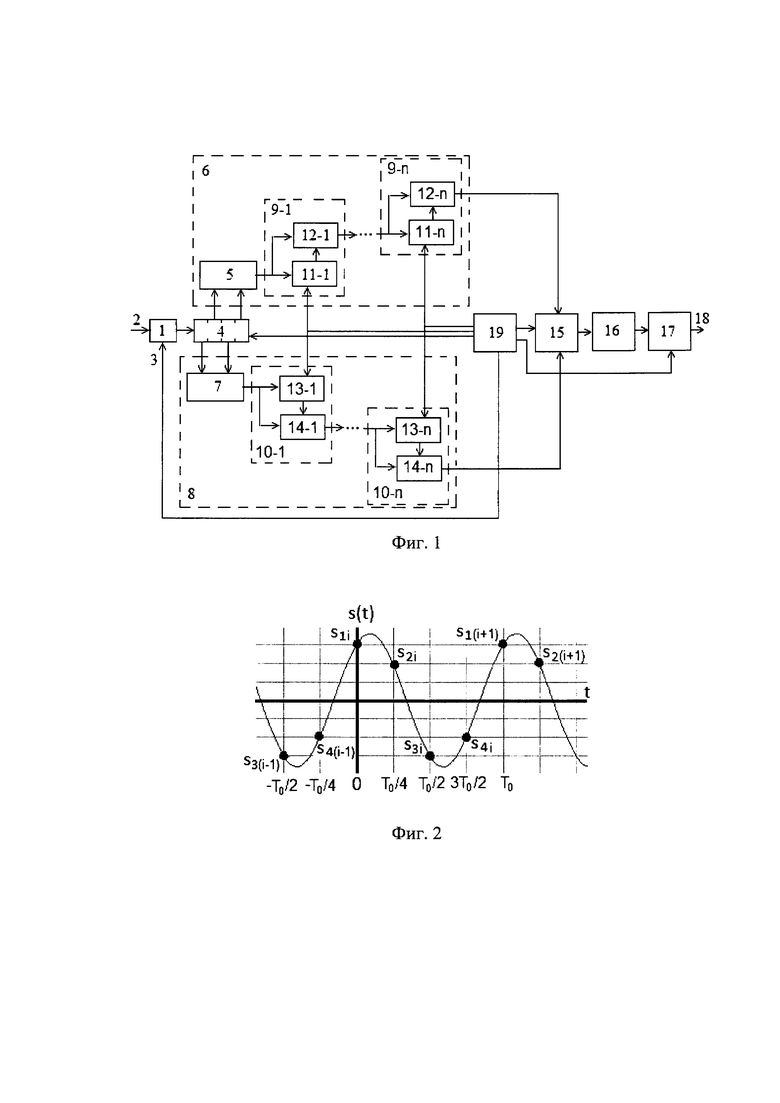

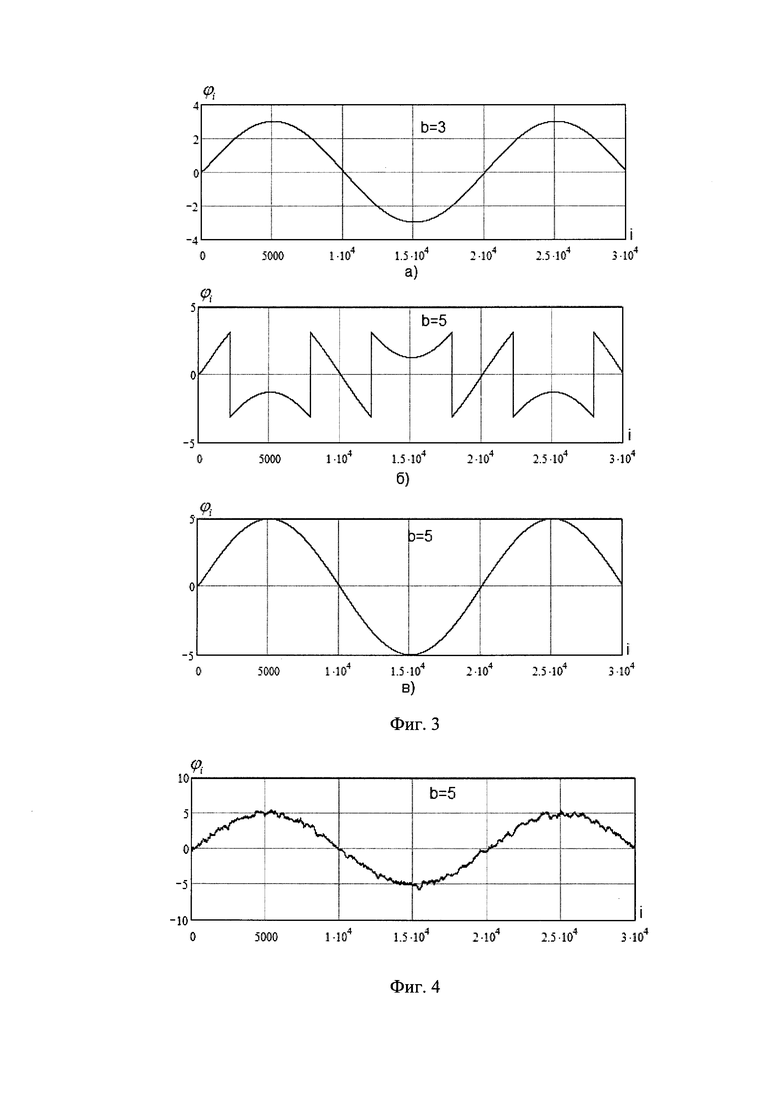

На фиг. 1 представлена структурная схема предлагаемого устройства, на фиг. 2 - процесс квантования входного сигнала (по 4 отсчета на период), на фиг. 3 и фиг. 4 - результаты моделирования работы демодулятора при отсутствии и наличии шума соответственно.

Устройство содержит АЦП 1, на вход которого поступает принимаемый сигнал 2 с выхода усилителя промежуточной частоты приемника, а на управляющий вход - тактовые импульсы 3. Выход АЦП 1 соединен с входом регистра 4 сдвига многоразрядных кодов на четыре отсчета, четные выходы которого соединены с соответствующими входами вычитателя 5 первого ККО 6, а нечетные выходы - с соответствующими входами вычитателя 7 второго ККО 8. Каждый ККО помимо вычитателя содержит n каскадно соединенных блоков накопления отсчетов (БНО). Количество БНО n зависит от числа N периодов накопления сигнала и определяется двоичным логарифмом N (n=log2N). Такое построение устройства обеспечивает минимальное количество БНО, при этом число обрабатываемых периодов сигнала равно N=2n, а длительность накопления равна NT0. Здесь T0=1/ƒ0 - период принимаемого сигнала с несущей частотой ƒ0.

Первый ККО 6 содержит последовательно соединенные БНО 9-1, …, 9-n, а второй ККО 8 - последовательно соединенные БНО 10-1, …, 10-n. Каждый из БНО состоит из регистра сдвига многоразрядных кодов и сумматора. Блоки 9-1, …, 9-n накопления отсчетов содержат регистры 11-1, …, 11-n сдвига многоразрядных кодов и сумматоры 12-1, …, 12-n соответственно, а БНО 10-1, …, 10-n - соответственно регистры 13-1, …, 13-n сдвига многоразрядных кодов и сумматоры 14-1, …, 14-n. В каждом блоке 9 (10) накопления отсчетов первый вход регистра 11 (13) сдвига является входом блока 9 (10) накопления отсчетов и соединен с первым входом сумматора 12 (14). Второй вход сумматора 12 (14) соединен с выходом регистра 11 (13) сдвига. Выход сумматора 12 (14) является выходом блока 9 (10) накопления отсчетов, а тактовый вход регистра 11 (13) сдвига является управляющим входом блока 9(10) накопления отсчетов.

Выход вычитателя 5 соединен с входом блока 9-1 накопления отсчетов ККО 6, а выход блока 9-n накопления отсчетов ККО 6 - с первым входом НУ. Выход вычитателя 7 соединен с входом блока 10-1 накопления отсчетов ККО 8, а выход блока 10-n накопления отсчетов ККО 8 - с вторым входом НУ. Выход НУ соединен с входом ЦФ, а его выход подключен к входу КФ, выход которого является выходом устройства. Тактовые входы АЦП, регистра сдвига многоразрядных кодов на 4 отсчета, всех БНО, НУ и КФ подключены к выходам ГТИ.

Устройство работает следующим образом.

Имеющийся на входе 2 детектора сигнал с фазовой модуляцией s(t)=Ssin[2πƒ0t+ϕ(t)], где S - амплитуда, ƒ0 - несущая частота, ϕ(t) - текущая начальная фаза, поступает на вход АЦП 1, который формирует по четыре отсчета входного сигнала на период повторения Т0=1/ƒ0 в соответствии с тактовыми импульсами 3 с частотой 4ƒ0. Процесс квантования для i-го периода показан на фиг. 2.

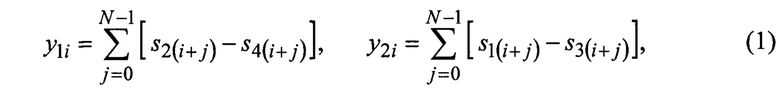

После обработки i-го периода (заполнения многоразрядного регистра сдвига на 4 отсчета) на вход вычитателя 5 поступают отсчеты s2i и s4i, а на его выходе формируется разность s2i-s4i=Ssinϕ-(-Ssinϕ)=2Ssinϕ, которая запоминается в многоразрядном регистре сдвига 11-1. В следующем периоде сигнала на выходе вычитателя 5 получим величину s2(i+1)-s4(i+1)=2Ssinϕ (фиг. 2), а на выходе сумматора 12-1 - s2i-s4i+s2(i+1)-s4(i+1)=4Ssinϕ. После поступления N=2n периодов входного сигнала (n - число БНО в каждом ККО) при отсутствии помех на выходе сумматора 12-n ККО 6 получим результат

y1i=s2i-s4i+s2(i+1)-s4(i+1)+…+s2(i+N-1)-s4(i+N-1)=2NSsinϕ

обработки 2N четных отсчетов принятого сигнала (полагается, что за время NT0 начальная фаза входного сигнала меняется незначительно).

Аналогично на вход вычитателя 7 сначала поступают отсчеты s1i и s3i, на выходе формируется разность s1i-s3i=Scosϕ-(-Scosϕ)=2Scosϕ, которая запоминается в регистре 13-1. В результате после поступления N периодов входного сигнала на выходе сумматора 14-n ККО 8 получим результат

y1i=s1i-s3i+s1(i+1)-s3(i+1)+…+s1(i+N-1)-s3(i+N-1)=2NScosϕ.

В каналах квадратурной обработки производится суммирование N=2n разностей четных и нечетных отсчетов сигнала на текущем периоде T0, их последовательности сдвинуты во времени на T0/4 (или по фазе на π/2). Результаты y1i и y2i можно записать в виде

где i - номер текущего первого обрабатываемого периода сигнала (текущее нормированное к T0 время начала интервала накопления длиной N=2n периодов).

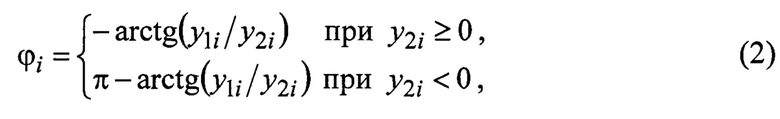

Двоичные коды величин y1i и y2i поступают в нормирующее устройство 15 (на основе регистров сдвига), обеспечивающее путем совместного сдвига кодов полное заполнение разрядной сетки наибольшего по модулю из них. Далее результаты поступают в цифровой формирователь арктангенса 16, в котором определяется величина

равная сдвигу фаз между принимаемым и опорным сигналами. Вычисления в (2) наиболее целесообразно реализовать аппаратно на базе постоянного запоминающего устройства (ПЗУ), в котором коды величин y1i и y2i образуют адрес ячейки памяти, в которой записан двоичный код ϕi. Если выбрать разрядность нормированных кодов y1i и y2i равной 10 (20-ти разрядная шина адреса ПЗУ), и разрядность кода ϕi равной 8, то потребуется ПЗУ общей емкостью 1 Мбайт.

Фаза сигнала многозначна с интервалом 2π, так что при большом диапазоне изменения фазы принимаемого сигнала решения на основе (2) могут приводить к скачкам результата. В этой связи значения ϕi поступают в блок коррекции фазы 17, где выделяются разности Δϕi-=ϕi-ϕi-1, и если, например, Δϕi>π/2, то к значению ϕi добавляется код числа 2π, а если Δϕi<-π/2, то - вычитается. Скорректированный код ϕi с выхода КФ 17 является откликом цифрового фазового детектора.

В предлагаемом устройстве обеспечивается минимум арифметических операций на период сигнала и, следовательно, высокая скорость цифровой обработки сигнала. Процедура квантования сигнала обеспечивает идентичность каналов квадратурной обработки.

Технически устройство наиболее целесообразно реализовать на базе программируемых логических интегральных схем (ПЛИС).

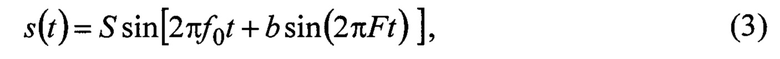

Примеры аналоговой фазовой демодуляции в устройстве, реализованном согласно блок-схеме фиг. 1, показаны на фиг. 3 при N=1024 для сигнала с тональной ФМ вида

где ƒ0=10 МГц - несущая частота, F=500 Гц - частота модуляции фазы, b - амплитуда изменения фазы, i - номер текущего периода (ось нормированного времени). Временная диаграмма сигнала и процедура его квантования представлены на фиг. 2. Функцию вида (3) можно рассматривать и как сигнал с аналоговой (тональной) ЧМ, при этом величина b является индексом ЧМ, а девиация частоты равна ΔF=bF.

На фиг. 3а показаны результаты имитационного моделирования работы фазового детектора сигнала (3) при b=3 рад, при этом изменение фазы не выходит за пределы 2π и не требуется ее коррекция. На фиг. 3б приведен результат демодуляции при увеличенном диапазоне изменения фазы с b=5 рад без ее коррекции (видно, что в этом случае имеют место скачкообразные изменения кода отклика детектора). На фиг. 3в показан результат детектирования с использованием коррекции фазы, при этом отклик детектора повторяет форму модулирующего сигнала.

При воздействии шумовой помехи возникают искажения выходного сигнала.

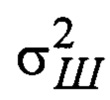

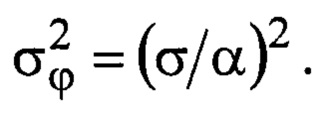

Значения y1i и y2i в (1) при отсутствии шума равны соответственно 2NSsinϕi и 2Ncosϕi. В случае искажения полезного сигнала полосовым гауссовским шумом с дисперсией  шумовые компоненты y1i и y2i описываются нормальным распределением вероятностей с нулевым средним значением и дисперсией, равной сумме дисперсий отсчетов

шумовые компоненты y1i и y2i описываются нормальным распределением вероятностей с нулевым средним значением и дисперсией, равной сумме дисперсий отсчетов

и являются приближенно статистически независимыми.

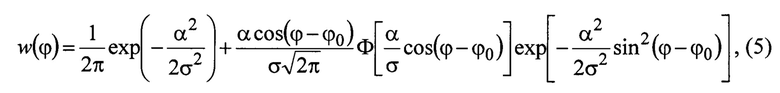

В литературе [5] рассмотрены статистические свойства случайного вектора с нормальными декартовыми координатами x и y со средними значениями a и b соответственно и дисперсией σ2. Согласно [5] для плотности вероятности фазы при a=2NSsinϕi, b=2NSsinϕi и σ2 (4) имеем

|ϕ-ϕ0|≤π.

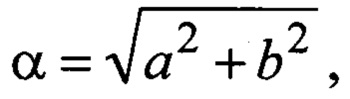

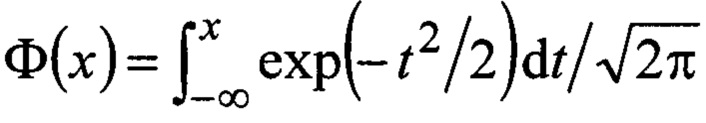

Здесь  ϕ0=arctg(b/a), а

ϕ0=arctg(b/a), а  - интеграл вероятности.

- интеграл вероятности.

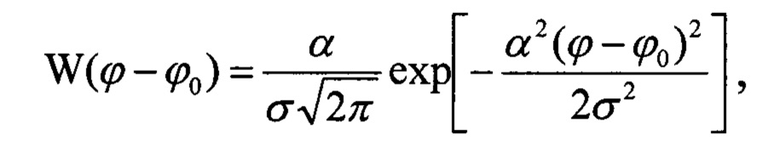

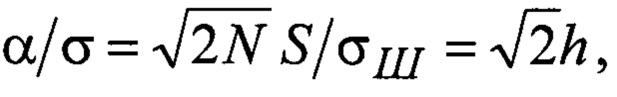

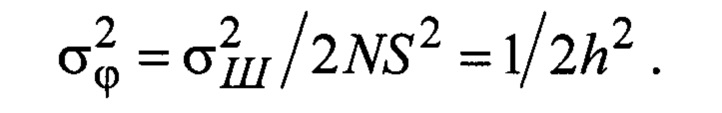

При больших величинах α/σ (α/σ>10) плотность вероятности фазы (5) близка нормальной (гауссовской) плотности вероятности вида

где среднее значение распределения равно ϕ0, а дисперсия -

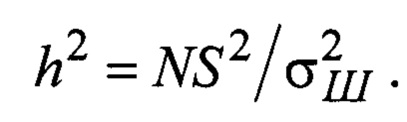

Отношение сигнал/шум на выходе квадратурных каналов обработки сигнала (отношение мощности сигнальной компоненты последовательности отсчетов к мощности шумовой составляющей) определится как

Тогда  и дисперсия фазы на выходе алгоритма демодуляции ФМ сигнала равна

и дисперсия фазы на выходе алгоритма демодуляции ФМ сигнала равна

Величина  характеризует среднеквадратическое отклонение оценки фазы, вызванным шумом на входе демодулятора.

характеризует среднеквадратическое отклонение оценки фазы, вызванным шумом на входе демодулятора.

На практике, как правило, отношение сигнал/шум h2>>1, так что дисперсия фазы  Например, при h>5 получим σϕ<0,14 рад.

Например, при h>5 получим σϕ<0,14 рад.

Отметим также, что при амплитуде изменения фазы b в несколько радиан даже при небольшом отношении сигнал/шум h уровень выходного шума фазового детектора будет сравнительно низким, что свидетельствует о высокой помехоустойчивости фазомодулированных сигналов и предлагаемого алгоритма их детектирования.

На фиг. 4 показаны результаты статистического имитационного моделирования работы фазового детектора при N=256 (n=8), S=1, σШ=5, (h>3,2) и b=5. Отсюда следует, что применение предложенного детектора обеспечивает высокую помехоустойчивость детектирования сигнала с аналоговой фазовой модуляцией.

Литература

1. Хвалов А.Н., Бородинов Л.Ю. Фазовый детектор // Авторское свидетельство SU 1107268А, МПК H03D 3/02 от 07.08.84 (Бюлл. №29).

2. Метрология и радиоизмерения / Под ред. В.И. Нефедова. - М.: Высшая школа, 2003. - 526 с.

3. Жиленков М.Г., Курицын С.А., Новиков И.А. Цифровой фазовый детектор // Авторское свидетельство SU 1467785А1, МПК H04L 27/22 от 23.03.89 (Бюлл. №11).

4. Глушков А.Н., Литвиненко В.П., Проскуряков Ю.Д. Цифровой обнаружитель узкополосных сигналов // Патент №2257671 С1, МПК Н04В 1/10 от 27.07.2005 (Бюлл. №21); заявка №2003135817/09 от 09.12.2003.

5. Левин Б.Р. Теоретические основы статистической радиотехники. Книга первая. М.: Советское радио, 1969. - 752 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ДЕМОДУЛЯТОР СИГНАЛОВ С МНОГОПОЗИЦИОННОЙ ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МАНИПУЛЯЦИЕЙ | 2021 |

|

RU2776968C1 |

| Цифровой демодулятор сигналов с амплитудной - относительной фазовой манипуляцией | 2022 |

|

RU2790205C1 |

| ЦИФРОВОЙ ИЗМЕРИТЕЛЬ СДВИГА ФАЗ ГАРМОНИЧЕСКИХ СИГНАЛОВ | 2020 |

|

RU2751020C1 |

| Цифровой демодулятор сигналов с двухуровневой амплитудно-фазовой манипуляцией и относительной оценкой амплитуды символа | 2022 |

|

RU2790140C1 |

| ЦИФРОВОЙ ДЕМОДУЛЯТОР СИГНАЛОВ С АМПЛИТУДНО-ФАЗОВОЙ МАНИПУЛЯЦИЕЙ | 2022 |

|

RU2786159C1 |

| ЦИФРОВОЕ КВАДРАТУРНОЕ УСТРОЙСТВО ФАЗОВОЙ СИНХРОНИЗАЦИИ И ДЕМОДУЛЯЦИИ | 2015 |

|

RU2591032C1 |

| ЦИФРОВОЙ НЕКОГЕРЕНТНЫЙ ДЕМОДУЛЯТОР ЧЕТЫРЕХПОЗИЦИОННЫХ СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МАНИПУЛЯЦИЕЙ | 2017 |

|

RU2649782C1 |

| ЦИФРОВОЙ ДЕМОДУЛЯТОР СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МАНИПУЛЯЦИЕЙ | 2011 |

|

RU2505922C2 |

| ЦИФРОВОЙ КОГЕРЕНТНЫЙ ДЕМОДУЛЯТОР ЧЕТЫРЕХПОЗИЦИОННОГО СИГНАЛА С ФАЗОВОЙ МАНИПУЛЯЦИЕЙ | 2017 |

|

RU2656577C1 |

| НЕКОГЕРЕНТНЫЙ ЦИФРОВОЙ ДЕМОДУЛЯТОР "В ЦЕЛОМ" КОДИРОВАННЫХ СИГНАЛОВ С ФАЗОВОЙ МАНИПУЛЯЦИЕЙ | 2014 |

|

RU2556429C1 |

Изобретение относится к области радиотехники и может быть использовано в устройствах приема аналоговых информационных сигналов с фазовой модуляцией и для выделения (измерения) фазового сдвига, принимаемого и опорного сигналов в системах фазовой синхронизации. Техническим результатом является обеспечение высокоскоростного цифрового фазового детектирования принимаемого сигнала с высокой помехоустойчивостью и устранением неидентичности квадратурных каналов обработки сигнала. Упомянутый технический результат достигается тем, что цифровой фазовый детектор, содержащий аналого-цифровой преобразователь, регистр сдвига многоразрядных кодов на четыре отсчета, первый и второй n-каскадные каналы квадратурной обработки сигналов и генератор тактовых импульсов (ГТИ), дополнительно содержит нормирующее устройство, цифровой формирователь арктангенса и блок коррекции фазы, на выходе которого формируется двоичный код сдвига фаз принимаемого сигнала относительно импульсов ГТИ. 6 ил.

Цифровой фазовый детектор, содержащий аналого-цифровой преобразователь (АЦП), регистр сдвига многоразрядных кодов на четыре отсчета, первый и второй n-каскадные каналы квадратурной обработки (ККО) сигналов и генератор тактовых импульсов (ГТИ), отличающийся тем, что он дополнительно содержит нормирующее устройство (НУ), цифровой формирователь (ЦФ) арктангенса и блок коррекции фазы (КФ), первый и второй информационные входы НУ соединены с выходами первого и второго ККО, выход НУ подключен к входу ЦФ, выход которого соединен с входом КФ, на выходе которого формируется двоичный код сдвига фаз принимаемого сигнала относительно импульсов ГТИ.

| ГЛУШКОВ А.Н | |||

| Быстрый цифровой алгоритм оценки амплитуды, мгновенной частоты и фазы узкополосного радиосигнала, Вестник Воронежского института МВД России, 2013 | |||

| ЗВЕРЕВ В.А | |||

| и др Выделение сигналов из помех численными методами, Нижний Новгород: ИПФ РАН, 2001 | |||

| Устройство для измерения ортогональныхСОСТАВляющиХ СигНАлА | 1978 |

|

SU834548A2 |

| ЦИФРОВОЙ ОБНАРУЖИТЕЛЬ УЗКОПОЛОСНЫХ СИГНАЛОВ | 2003 |

|

RU2257671C1 |

| Цифровой фазовый детектор | 1986 |

|

SU1467785A1 |

| US 6590426 | |||

Авторы

Даты

2020-06-11—Публикация

2018-10-01—Подача