УРОВЕНЬ ТЕХНИКИ

Настоящее изобретение в целом относится к цифроаналоговому преобразованию, в частности к реализациям высокоскоростного и маломощного цифроаналогового преобразователя с повышением частоты. В области высокоскоростных систем для цифроаналогового преобразования, в частности для спутниковых систем, предпринимают постоянные усилия по включению преобразования с повышением частоты в цифровую область путем реализации более высокоскоростных цифроаналоговых преобразовательных схем с повышением частоты с помощью интегральных схем устройства цифрового микширования. Однако проблема, связанная с временным расхождением цифровых информационных сигналов после схемы микширующего устройства, заключается в обеспечении технических характеристик высокоскоростной системы преобразования с повышением частоты. Временные расхождения отчасти обусловлены различиями между логическими переходами информационных сигналов и переходами тактового сигнала преобразования на входах схемы устройства цифрового микширования.

Предпринимались попытки уменьшить временные расхождения различными обычными средствами. Для частичного уменьшения временных расхождений могут быть использованы, например, топологии логических схем с переключением тока, однако их недостаток заключается в увеличении рассеяния мощности без существенного улучшения технических характеристик системы. Еще одним обычным средством устранения временных расхождений является ручная регулировка физических каналов для передачи сигнала в цифроаналоговом преобразователе с повышением частоты, однако этот этап может отнимать много времени, а также может и не быть реализован на практике, если цифроаналоговый преобразователь с повышением частоты используют для решения различных задач (например, преобразования с повышением частоты при различных скоростях передачи данных).

РАСКРЫТИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

В настоящем документе раскрыты системы и способы в соответствии с одним или более вариантами реализации, которые обеспечивает улучшенный подход к высокоскоростному цифроаналоговому преобразованию с повышением частоты. Высокоскоростная система для цифроаналогового преобразования обеспечивает преобразование множества битов параллельных цифровых данных в аналоговый выходной сигнал напряжения. В одном из примеров цифроаналоговый преобразователь с повышением частоты содержит различные цифровые схемные компоненты для выполнения логических операций и преобразования частоты входящих битов параллельных цифровых данных из более низкого диапазона в более высокий диапазон, причем биты параллельных цифровых данных приобретают временное расхождение по отношению друг к другу после преобразования частоты за счет различий в логических состояниях между тактовым сигналом частотного преобразования и каждым из битов данных. Обеспечивают прохождение параллельных цифровых слов, соответствующих имеющим временное расхождение битам данных, в схему синхронизирующего устройства. Схема синхронизирующего устройства выравнивает по времени биты параллельных цифровых данных и выдает выровненные по времени биты параллельных цифровых данных на коммутационную сеть, в которой указанные биты данных преобразуют в аналоговый сигнал напряжения.

В одном из вариантов реализации система содержит схему декодирующего устройства, выполненную с возможностью приема множества битов входных данных декодирующего устройства и возможностью выдачи множества декодированных битов параллельных цифровых данных, причем схему декодирующего устройства работает при заданной частоте дискретизации, а указанная система также содержит схему микширующего устройства, соединенную со схемой декодирующего устройства и выполненную с возможностью объединения каждого из декодированных битов параллельных цифровых данных с тактовым сигналом преобразования для получения битов цифровых данных со сдвигом частоты, которые имеют временное расхождение по отношению друг к другу, а указанная система также содержит схему синхронизирующего устройства, соединенную со схемой микширующего устройства, располагающую тактовым сигналом для синхронизирующего устройства и выполненную с возможностью выравнивания по времени битов цифровых данных со сдвигом частоты в ответ на тактовый сигнал для синхронизирующего устройства, и коммутационную сеть, соединенную со схемой синхронизирующего устройства и выполненную с возможностью генерирования аналогового выходного сигнала в ответ на выровненные по времени биты цифровых данных со сдвигом частоты.

Еще в одном варианте реализации предложен способ, включающий прием, посредством схемы декодирующего устройства, множества битов входных данных декодирующего устройства, обеспечение, посредством схемы декодирующего устройства, множества декодированных битов параллельных цифровых данных, причем схема декодирующего устройства работает при заданной частоте дискретизации, объединение, посредством схемы микширующего устройства, соединенной декодирующего устройства, каждого из указанных декодированных битов параллельных цифровых данных с тактовым сигналом преобразования для получения битов цифровых данных со сдвигом частоты, которые имеют временное расхождение по отношению друг к другу, выравнивание, посредством схемы синхронизирующего устройства, соединенной со схемой микширующего устройства, битов цифровых данных со сдвигом частоты в ответ на тактовый сигнал для синхронизирующего устройства и генерирование, посредством коммутационной сети, соединенной со схемой синхронизирующего устройства, аналогового выходного сигнала в ответ на выровненные по времени биты цифровых данных со сдвигом частоты.

Объем настоящего изобретения задан пунктами формулы изобретения, которые введены в данный раздел посредством ссылки. При ознакомлении с приведенным далее подробным описанием одного или более вариантов реализации у специалистов в данной области техники возникнет более полное понимание вариантов реализации настоящего изобретения и его дополнительных преимуществ. Сначала будут вкратце описаны прилагаемые чертежи, на которые ниже будут приведены ссылки.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

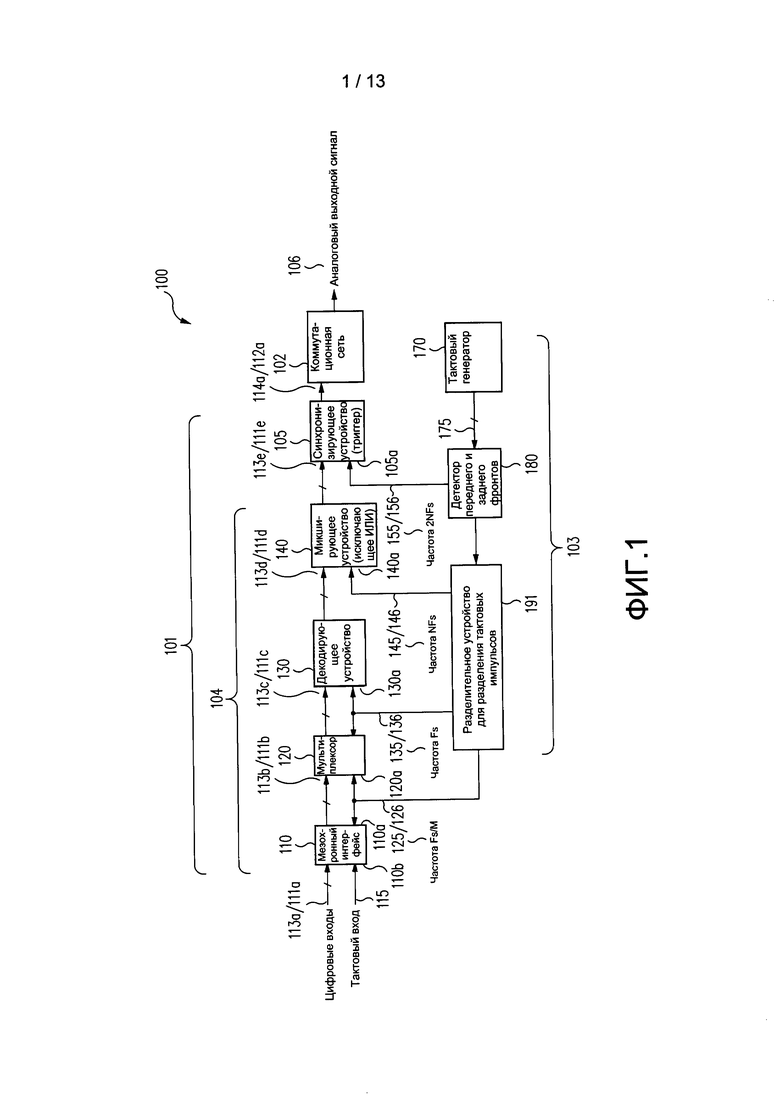

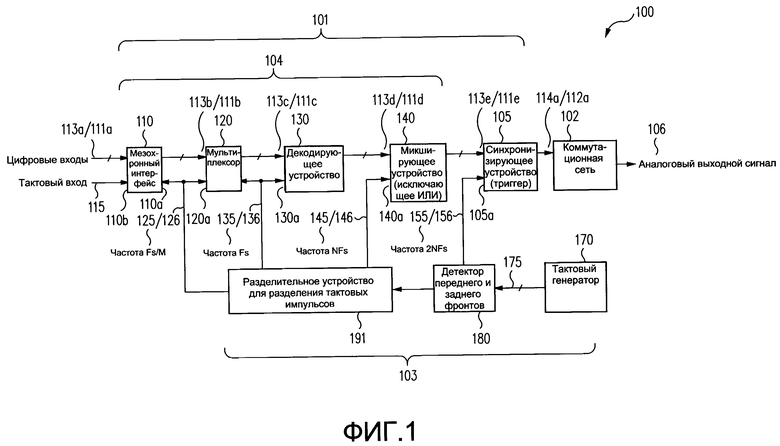

На фиг. 1 показана структурная схема системы цифроаналогового преобразования в соответствии с одним из вариантов реализации настоящего изобретения.

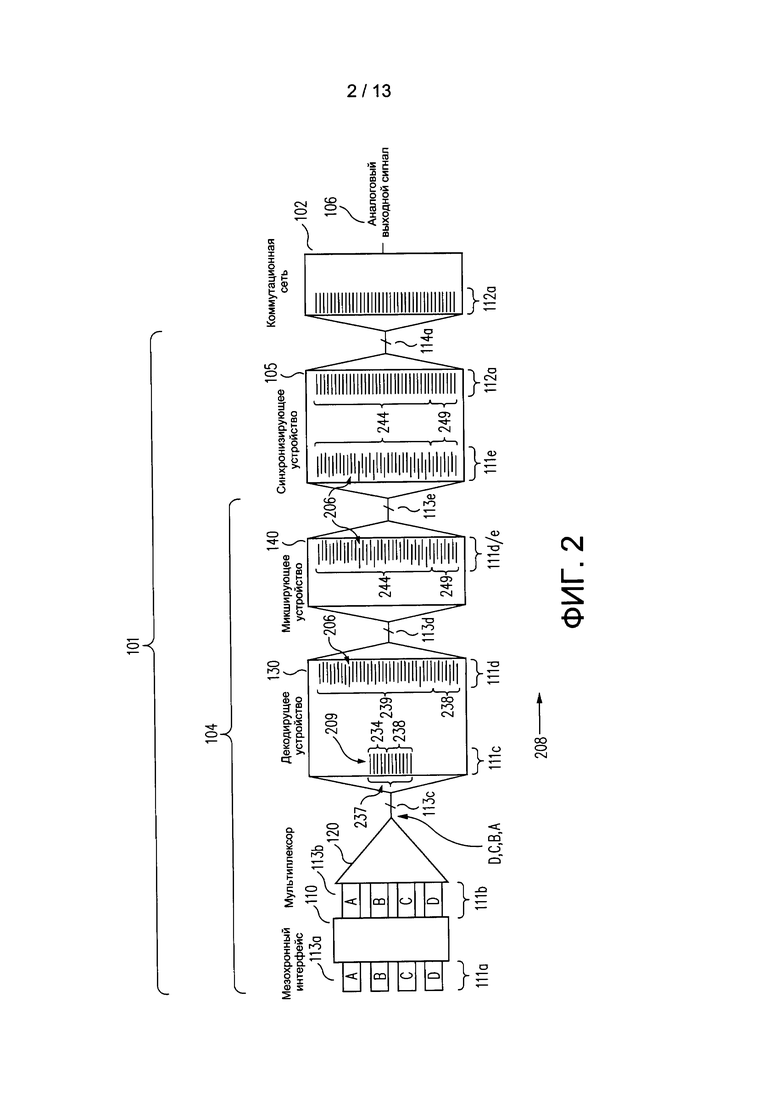

На фиг. 2 показаны различные биты данных, проходящие через параллельные каналы для передачи данных в системе цифроаналогового преобразования в соответствии с одним из вариантов реализации настоящего изобретения.

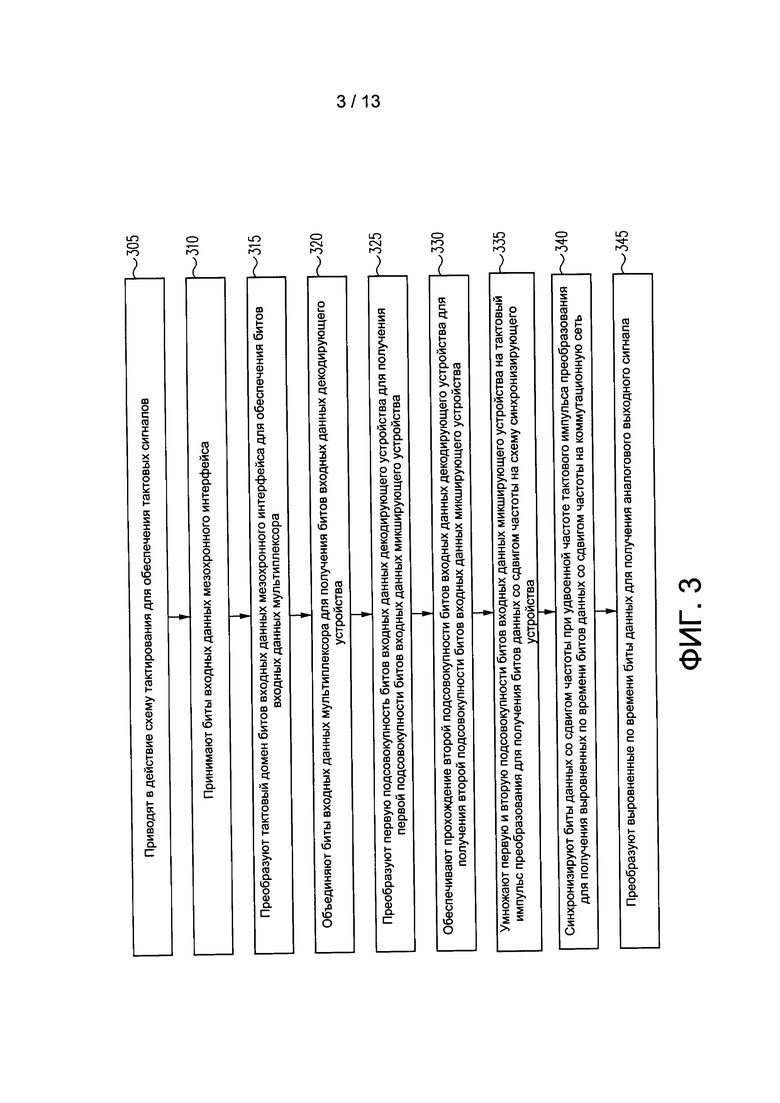

На фиг. 3 показан процесс работы системы цифроаналогового преобразования в соответствии с одним из вариантов реализации настоящего изобретения.

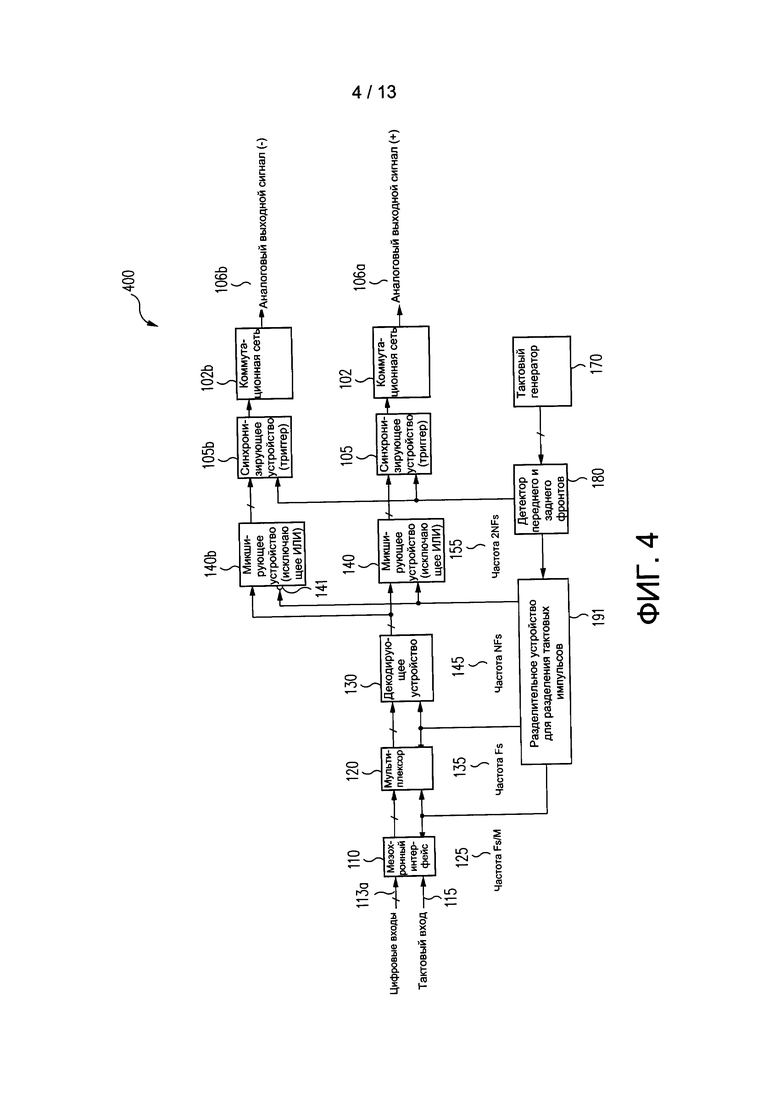

На фиг. 4 показана структурная схема системы цифроаналогового преобразования, выдающей дифференциальные выходные данные, в соответствии с одним из вариантов реализации настоящего изобретения.

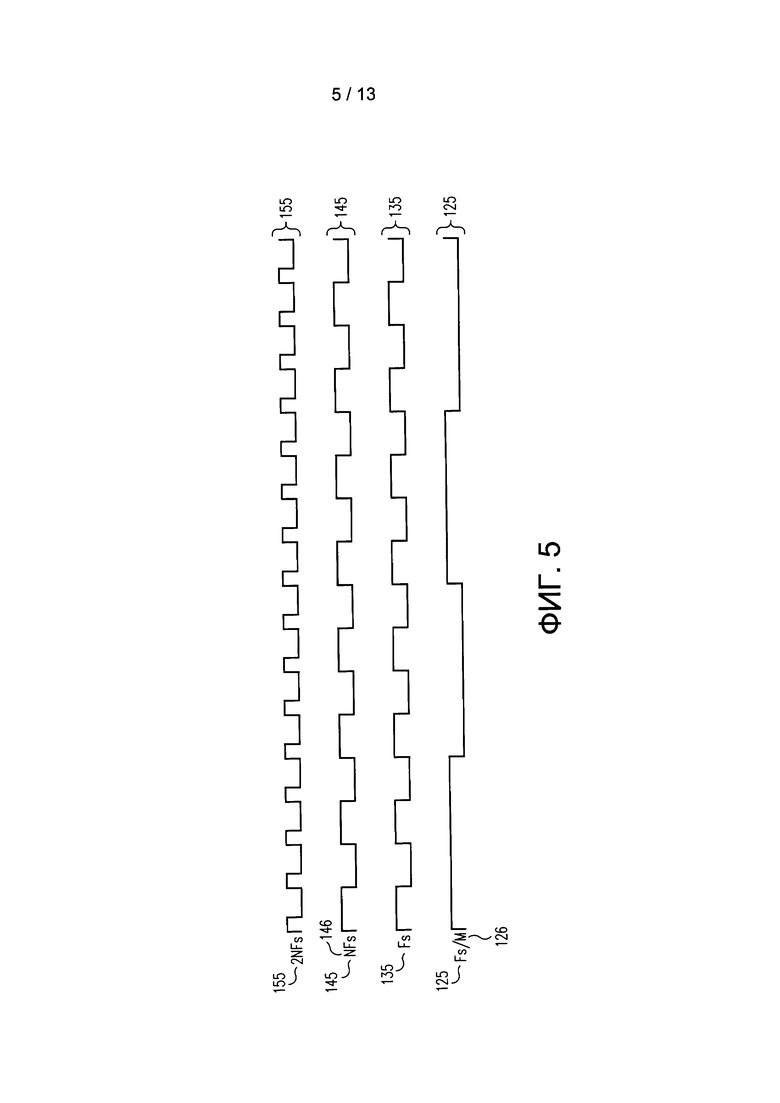

На фиг. 5 показана временная диаграмма схемы тактирования в соответствии с одним из вариантов реализации настоящего изобретения.

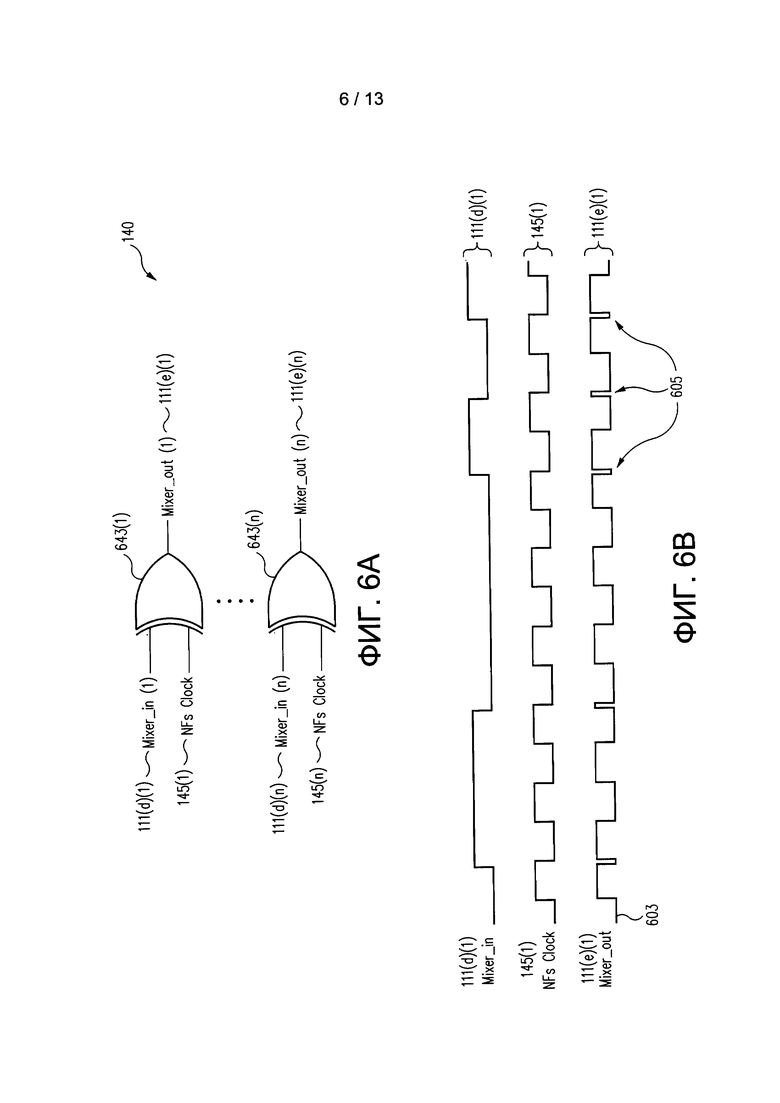

На фиг. 6А показана структурная схема, иллюстрирующая схему микширующего устройства в соответствии с одним из вариантов реализации настоящего изобретения.

На фиг. 6В показана временная диаграмма схемы микширующего устройства в соответствии с одним из вариантов реализации настоящего изобретения.

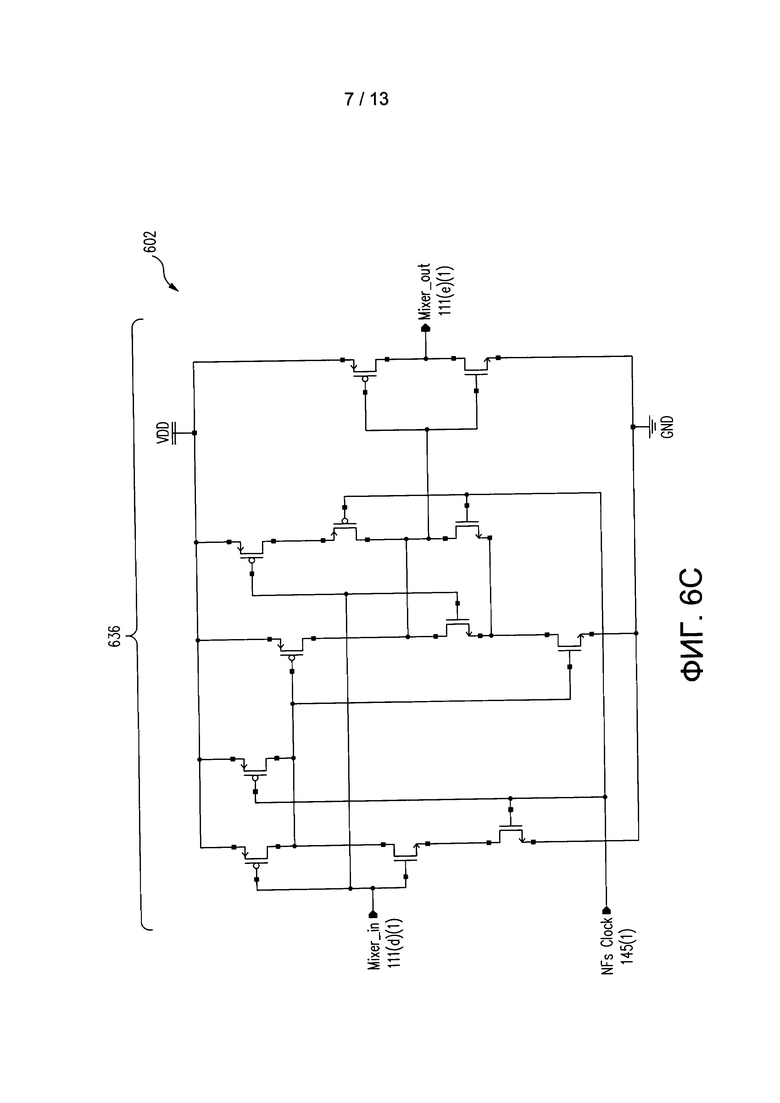

На фиг. 6С показана структурная схема, иллюстрирующая схему микширующего устройства в соответствии с одним из вариантов реализации настоящего изобретения.

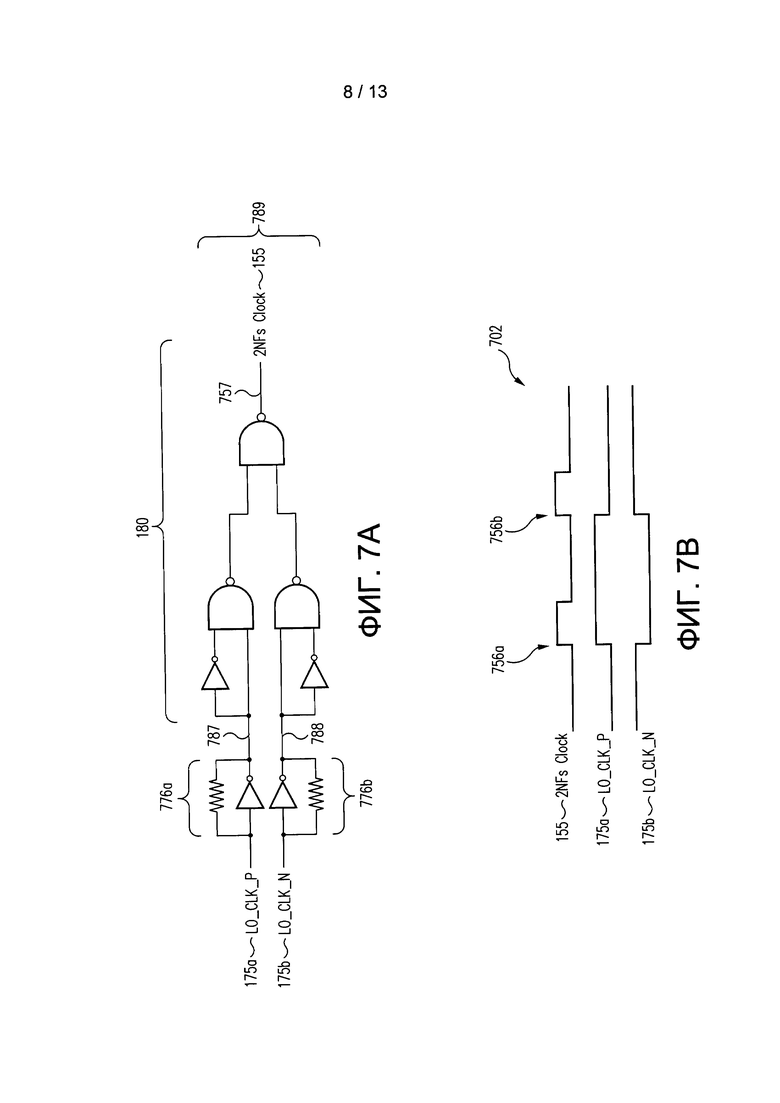

На фиг. 7А показана структурная схема, иллюстрирующая схему детектора переднего и заднего фронтов в соответствии с одним из вариантов реализации настоящего изобретения.

На фиг. 7В показана временная диаграмма схемы детектора переднего и заднего фронтов в соответствии с одним из вариантов реализации настоящего изобретения.

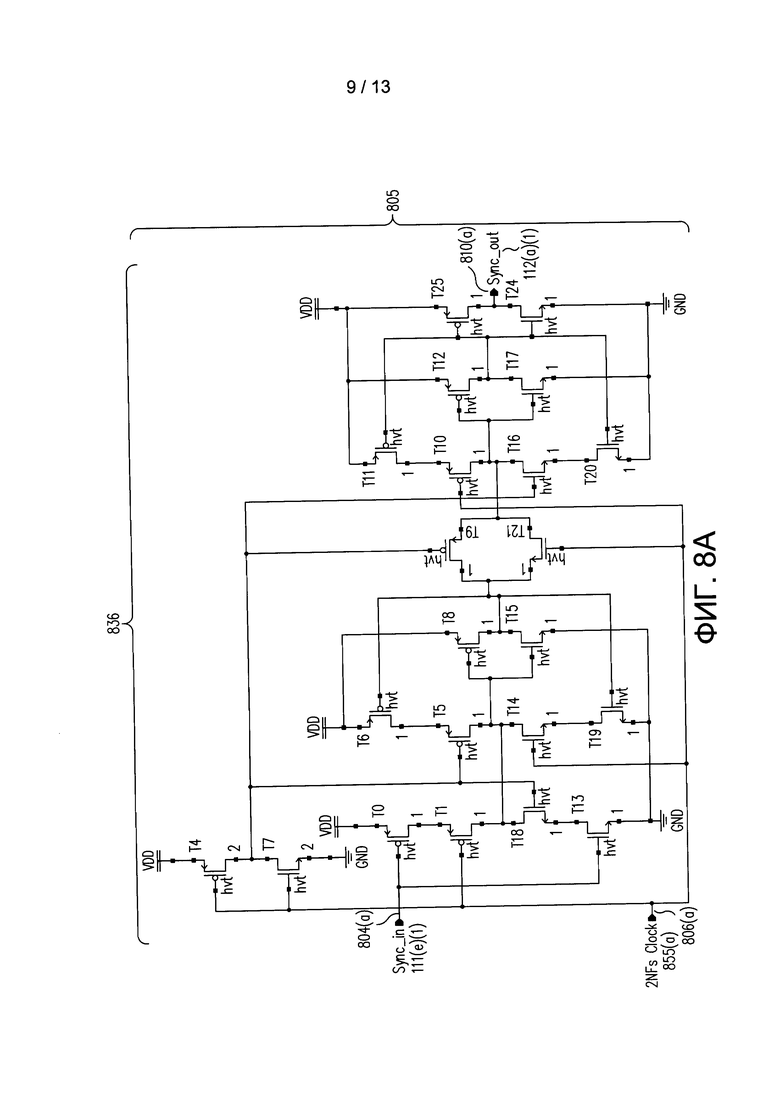

На фиг. 8А показана структурная схема, иллюстрирующая схему синхронизирующего устройства в соответствии с одним из вариантов реализации настоящего изобретения.

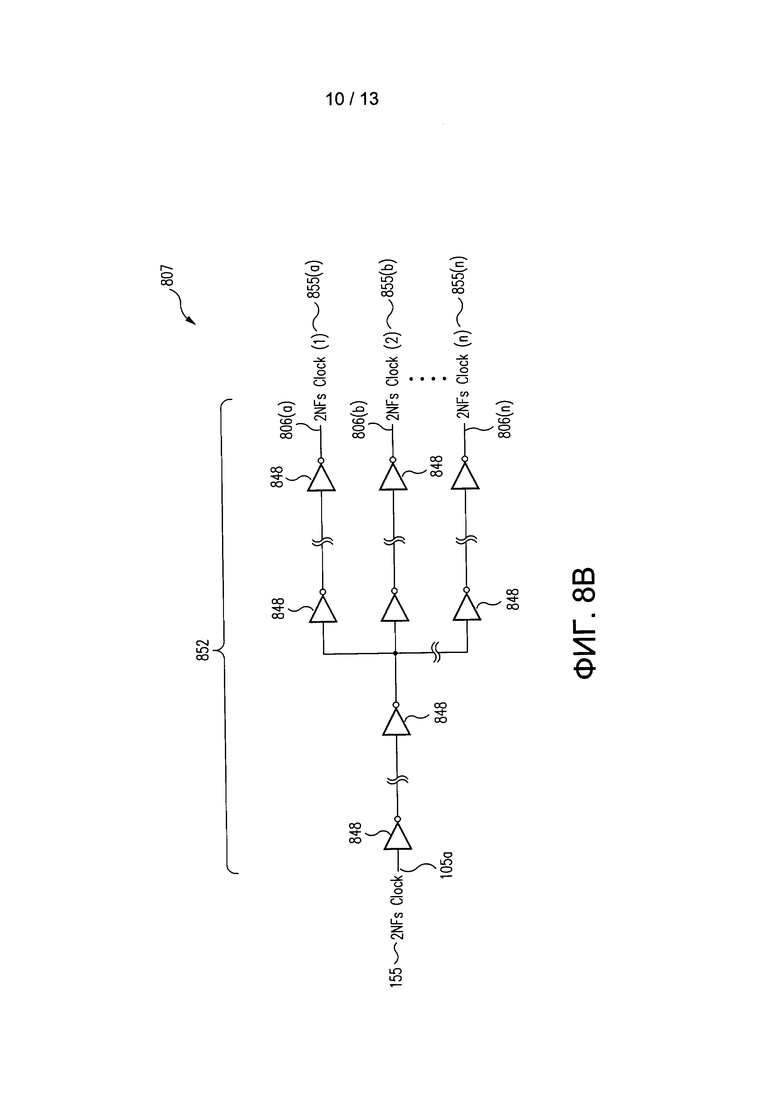

На фиг. 8В показана структурная схема, иллюстрирующая схему распределения тактовых импульсов для синхронизирующего устройства в соответствии с одним из вариантов реализации настоящего изобретения.

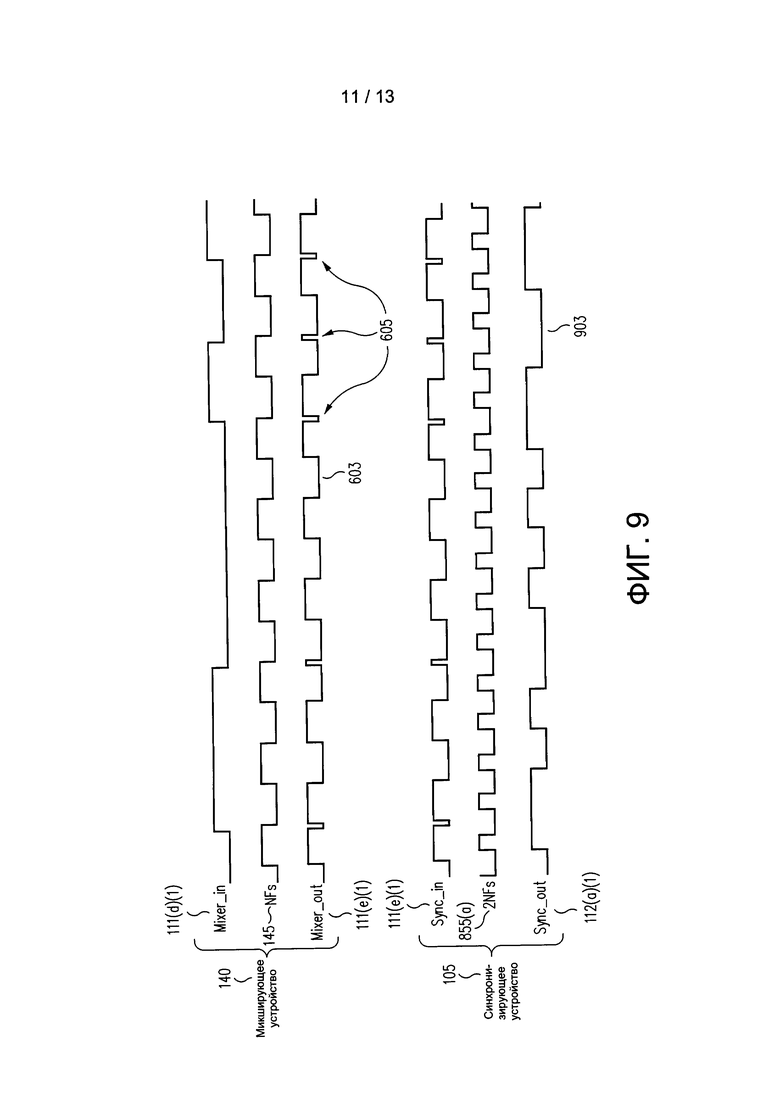

На фиг. 9 показаны временные диаграммы схемы микширующего устройства и схемы синхронизирующего устройства в соответствии с одним из вариантов реализации настоящего изобретения.

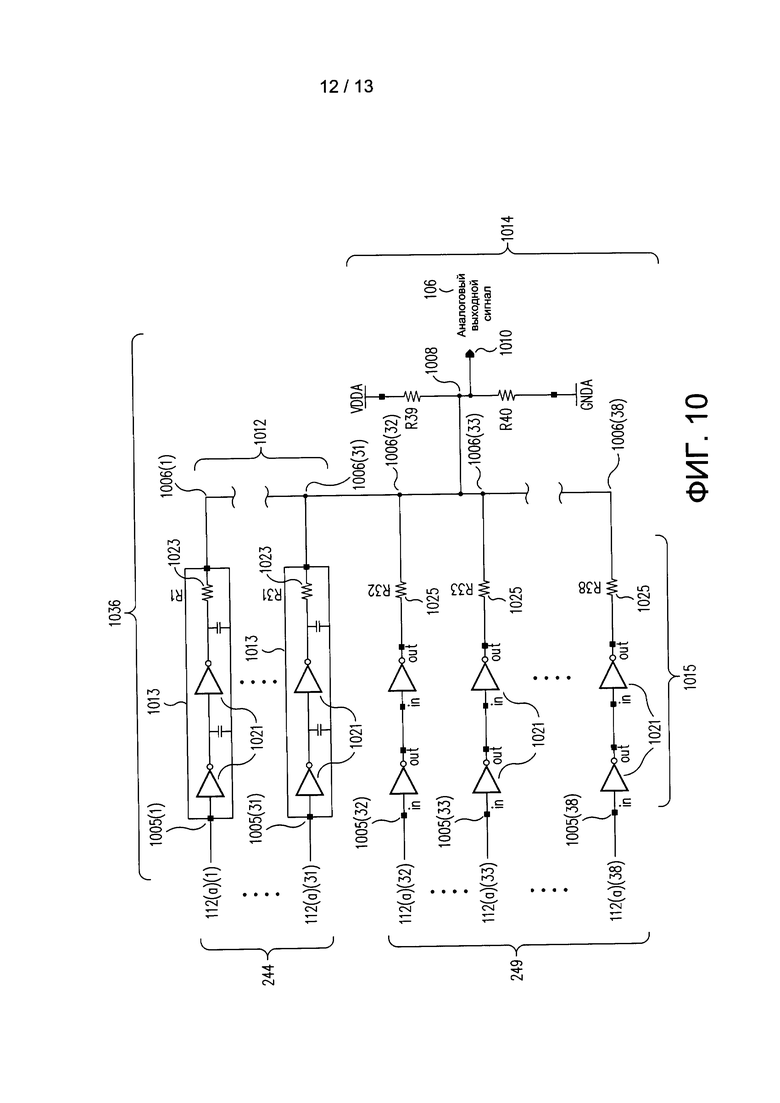

На фиг. 10 показана структурная схема, иллюстрирующая коммутационную сеть в соответствии с одним из вариантов реализации настоящего изобретения.

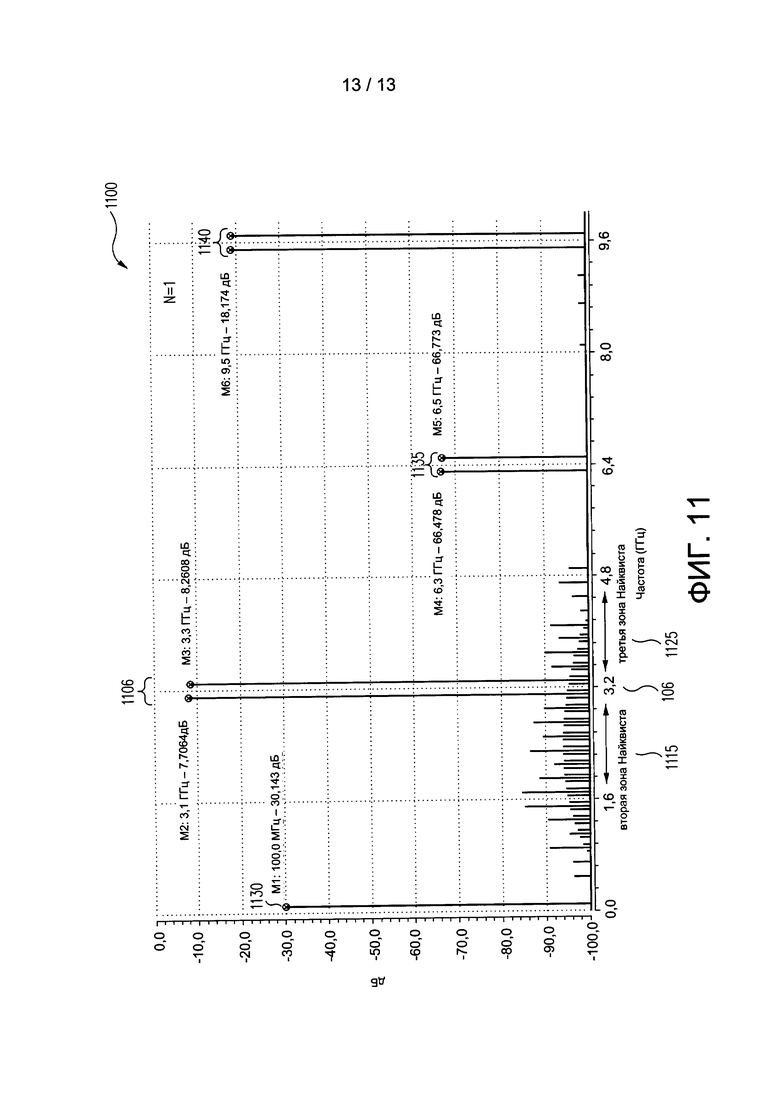

На фиг. 11 показан график зависимости энергии сигнала от частоты для цифроаналогового преобразователя с повышением частоты в соответствии с одним из вариантов реализации настоящего изобретения.

ОСУЩЕСТВЛЕНИЕ ИЗОБРЕТЕНИЯ

Для уменьшения временного расхождения битов параллельных цифровых данных по отношению друг к другу перед преобразованием в аналоговый сигнал используют различные реализации системы цифроаналогового преобразования с повышением частоты. Система цифроаналогового преобразования с повышением частоты содержит декодирующее устройство, микширующее устройство, синхронизирующее устройство, коммутационную сеть, а также схему тактирования, используемую для преобразования битов параллельных цифровых данных в аналоговое напряжение. В различных вариантах реализации цифроаналоговый преобразователь с повышением частоты принимает биты параллельных цифровых данных из внешнего источника, такого как процессор для цифровой обработки сигналов. В некоторых вариантах реализации цифроаналоговый преобразователь с повышением частоты содержит каналы для передачи данных, в том числе различные цифровые компоненты для выполнения в отношении битов параллельных цифровых данных логических операций, включающих мультиплексирование, декодирование и умножение, причем биты параллельных цифровых данных приобретают временное расхождение друг с другом после этапа умножения за счет различий в переходах логического состояния на выходах декодирующего устройства относительно переходов логического состояния в тактовом импульсе для умножения (например, таком как тактовый сигнал 145 преобразования, показанный на фиг. 1).

В различных вариантах реализации цифроаналоговый преобразователь с повышением частоты содержит схему синхронизирующего устройства для осуществления выравнивания по времени имеющих временное расхождение битов параллельных цифровых данных. При этом схема синхронизирующего устройства обеспечивает выравнивание по времени битов цифровых данных перед коммутационной сетью. Выравнивание по времени битов цифровых данных на входе в коммутационную сеть является важным для обеспечения высокоэффективного цифроаналогового преобразования. В частности, схема синхронизирующего устройства способствует постоянной выработке энергии при частоте передачи данных и изменениях температуры на выходе коммутационной сети для максимизации эффективного количества битов, то есть основного показателя технических характеристик цифроаналогового преобразователя.

В различных вариантах реализации схема синхронизирующего устройства реализована в виде параллельных триггеров, каждый из которых принимает один из имеющих временное расхождение битов параллельных цифровых данных. Тактовый сигнал для синхронизирующего устройства выдают на каждый триггер для дискретизации имеющего расхождение по времени бита данных. В некоторых вариантах реализации каждый триггер может представлять собой Д-триггер, реализованный с возможностью дискретизации бита данных в ответ на тактовый сигнал для синхронизирующего устройства. В некоторых вариантах реализации имеющие временное расхождение биты данных дискретизируют при частоте, вдвое превышающей частоту преобразования, для устранения каких-либо искажений или временных расхождений у битов цифровых данных.

В различных вариантах реализации схема тактирования реализована в виде тактового генератора для генерирования дифференциального локального тактового импульса, схемы детектора переднего и заднего фронтов и схемы разделительного устройства для разделения тактовых импульсов. Дифференциальный локальный тактовый импульс выполняет функцию задающего тактового импульса, при этом дифференциальный локальный тактовый сигнал выдают на детектор переднего и заднего фронтов. Детектор переднего и заднего фронтов преобразует дифференциальный сигнал в одиночный конечный тактовый сигнал для синхронизирующего устройства. В некоторых вариантах реализации тактовый сигнал для синхронизирующего устройства представляет собой одиночный конечный импульсной выходной тактовый сигнал, причем каждый импульсный выходной сигнал генерируют при переднем фронте и заднем фронте дифференциального тактового сигнала для получения частоты, вдвое превышающей частоту дифференциального тактового сигнала. В значительной степени схема синхронизирующего устройства обеспечивает адаптируемость для изменения основного дифференциального локального тактового сигнала и поддержания быстродействия без необходимости в ручной перенастройке каналов для передачи цифровых данных.

Схема разделительного устройства для разделения тактовых импульсов реализована с возможностью разделения одиночного конечного тактового сигнала для синхронизирующего устройства для получения тактового сигнала преобразования, тактового сигнала для декодирующего устройства и тактового сигнала для мультиплексора. При этом система цифроаналогового преобразования с повышением частоты реализована с помощью одиночных конечных тактовых сигналов для обеспечения уменьшения рассеяния энергии и уменьшения потребления энергии. В частности, для уменьшения общего размера и мощности в системе цифроаналогового преобразования с повышением частоты использованы стандартные цифровые методики изготовления на основе КМОП-технологии и топологии несимметричных схем, работающих в режиме напряжения. Например, каждый из схемных блоков не потребляет по существу никакой энергии смещения и первоначально рассеивает энергию исключительно во время переходов логического состояния.

На фиг. 1 показана структурная схема системы цифроаналогового преобразования 100 в соответствии с одним из вариантов реализации настоящего изобретения. Система 100 может быть использована для преобразования цифровых информационных сигналов в аналоговые сигналы напряжения в соответствии с различными технологиями, описанными в данном документе. Система 100 может быть использована на множестве различных платформ, таких как наземная платформа, авиационная платформа или космическая платформа. В одном из вариантов реализации система 100 может быть использована в системе спутниковой связи. Еще в одном варианте реализации система 100 может быть использована в наземной или авиационной радарной системе.

В одном из вариантов реализации система 100 содержит цифровой преобразователь 101 с повышением частоты, коммутационную сеть 102, а также схему 103 тактирования. Система 100 может быть реализована в виде высокоскоростной системы для цифроаналогового преобразования, в которой принимают параллельные цифровые информационные сигналы, которые сдвигают по частоте и преобразуют в аналоговый сигнал.

Цифровой преобразователь 101 с повышением частоты может содержать, например, канал 104 для передачи данных и схему 105 синхронизирующего устройства. Канал 104 для передачи данных содержит различные цифровые компоненты, такие как схема 110 мезохронного интерфейса, схема 120 мультиплексора, схема 130 декодирующего устройства и схема 140 микширующего устройства. Компоненты канала 104 для передачи данных обеспечивают передачу в тактовом домене битов 111а входных данных схемы мезохронного интерфейса (например, слова входных данных мезохронного интерфейса) с помощью схемы 110 мезохронного интерфейса, мультиплексирование битов 111b входных данных мультиплексора (например, множество слов параллельных цифровых данных) с помощью схемы 120 мультиплексора, декодирование битов 111с входных данных декодирующего устройства с помощью схемы 130 декодирующего устройства, а также частотное смещение битов 111d входных данных микширующего устройства (например, декодированные биты параллельных цифровых данных) с помощью схемы 140 микширующего устройства.

В некоторых вариантах реализации канал 104 для передачи данных содержит параллельные шины 113a-d данных, причем каждая параллельная шина 113a-d данных имеет соответственно биты 111a-d данных. Биты 111a-d данных, проходящие через канал 104 для передачи данных, могут приобрести временное расхождение по отношению друг к другу после схемы 140 микширующего устройства за счет различий по времени между переходами логического состояния на выходах схемы 130 декодирующего устройства (например, такие как биты 238/239 параллельных цифровых данных, показанные на фиг. 2) и переходами логического состояния тактового сигнала 145 преобразования во время операций умножения, осуществляемых схемой 140 микширующего устройства. В некоторых вариантах реализации непреднамеренные искажения могут возникать на выходах схемы 140 микширующего устройства.

В одном из вариантов реализации схему 105 синхронизирующего устройства содержит, например, множество Д-триггеров, каждый из которых принимает соответствующий один из имеющих временное расхождение битов 111e данных по параллельной шине 113е данных с обеспечением синхронизации имеющих временное расхождение битов 111e данных и выдачи выровненных по времени битов 112а данных со сдвигом частоты на коммутационную сеть 102 по соответствующей параллельной шине 114а данных.

В некоторых вариантах реализации коммутационная сеть 102 принимает выровненные по времени биты 112а данных и преобразует выровненные по времени биты 112а данных в одиночный конечный аналоговый выходной сигнал 106. Коммутационная сеть 102 может быть реализована в виде множества инверторных схем на комплементарных структурах металл-оксид-полупроводник, управляющих резисторной схемой, причем каждая инверторная схема на комплементарных структурах металл-оксид-полупроводник принимает соответствующий выровненный по времени бит 112а данных со сдвигом частоты. Каждую конфигурацию из инверторной схемы на комплементарных структурах металл-оксид-полупроводник и резисторной схемы определяют на основании весового коэффициента, присвоенного соответствующего выровненному по времени биту 112а данных. Весовой коэффициент каждому из выровненных по времени битов 112а данных со сдвигом частоты присваивают с помощью схемы 130 декодирующего устройства. В некоторых вариантах реализации выровненные по времени биты 112а цифровых данных со сдвигом частоты могут представлять собой комбинацию двоично-кодированного весового коэффициента и/или кодированного весового коэффициента термометра, как описано в данном документе.

В некоторых вариантах реализации схема 103 тактирования содержит тактовый генератор 170 для генерирования дифференциального локального тактового импульса, схему 180 детектора переднего и заднего фронтов и схему 191 разделительного устройства для разделения тактовых импульсов. Дифференциальный локальный тактовый сигнал 175 выдают на схему 180 детектора переднего и заднего фронтов с помощью тактового генератора 170 для генерирования дифференциального локального тактового импульса. Дифференциальный локальный тактовый сигнал 175 преобразуют в одиночный конечный тактовый сигнал 155 для синхронизирующего устройства с помощью детектора 180 переднего и заднего фронтов, имеющего целое 156 кратное от дифференциального локального тактового сигнала 175, и выдают на схему 105 синхронизирующего устройства на тактовом входе 105а синхронизирующего устройства. В некоторых вариантах реализации целое кратное 156 дифференциального локального тактового сигнала 175 представляет собой множитель на два для получения частоты (2NFs) тактового сигнала для синхронизирующего устройства, которая в два раза превышает дифференциальный локальный тактовый сигнал 175 для синхронизации имеющих временное расхождение битов 111e данных в схеме 105 синхронизирующего устройства.

В некоторых вариантах реализации схема 191 разделительного устройства для разделения тактовых импульсов принимает одиночный конечный тактовый сигнал 155 для синхронизирующего устройства и делит тактовый сигнал 155 для синхронизирующего устройства на целочисленное значение 146 для получения тактового сигнала 145 преобразования на тактовом входе 140а схемы микширующего устройства. В некоторых вариантах реализации схема 191 разделительного устройства для разделения тактовых импульсов реализована для деления тактового сигнала 145 преобразования на целочисленное значение 136 для получения тактового сигнала 135 для декодирующего устройства на тактовом входе 130а декодирующего устройства. В различных вариантах реализации схема 191 разделительного устройства для разделения тактовых импульсов реализована с возможностью разделения тактового сигнала 135 для декодирующего устройства на целочисленное значение 126 (например, целочисленное значение М) для получения тактового сигнала 125 для мультиплексора на тактовом входе 120а мультиплексора.

Тактовый сигнал 125 мультиплексора может быть подан на схему 110 мезохронного интерфейса на тактовый выход 110а мезохронного интерфейса. Схема 110 мезохронного интерфейса может принять тактовый сигнал 115 для мезохронного интерфейса на тактовом входе 110b мезохронного интерфейса. В некоторых вариантах реализации тактовый сигнал 115 для мезохронного интерфейса является мезохронным по отношению к тактовому сигналу 125 для мультиплексора, что обеспечивает его действие при частоте, эквивалентной частоте тактового сигнала 125 для мультиплексора. Также предусмотрены и другие варианты реализации системы 100 цифроаналогового преобразования, которая обеспечивает выравнивание по времени имеющих временное расхождение битов 111e параллельных данных и преобразование выровненных по времени битов 112а цифровых данных со сдвигом частоты в аналоговый выходной сигнал 106 напряжения.

Например, на фиг. 4 показана структурная схема системы 400, обеспечивающей дифференциальные выходные данные, в соответствии с одним из вариантов реализации настоящего изобретения. Как показано на фиг. 4, система 400 может быть реализована с помощью дифференциального аналогового выходного сигнала 106а и 106b. При этом система 400 обеспечивает схожие компоненты, используемые в системе 100 для получения аналогового выходного сигнала 106а, однако в качестве дополнения содержит компоненты для выдачи дополнительного аналогового выходного сигнала 106b. Как показано на фиг. 4, дополнительные схема 140b микширующего устройства, схема 105b синхронизирующего устройства и коммутационная сеть 102b обеспечивают дополнительный аналоговый выходной сигнал 106b, причем дополнительные компоненты работают по существу схожим образом. Кроме того, тактовый сигнал 145 преобразования инвертируют на тактовом входе 141 схемы 140b микширующего устройства для получения дополнительного аналогового выходного сигнала 106b. В частности, схемы 140 и 140b микширующего устройства представляют собой цифровые множительные устройства. В одном из вариантов реализации схемы 140 и 140b микширующего устройства поочередно перемножают выходные данные схемы 130 декодирующего устройства (например, биты 111d параллельных цифровых данных) на +/-1 (например, высокий логический уровень/низкий логический уровень). Дополнительная схема 140b микширующего устройства работает в противоположной фазе по отношению к схеме 140 микширующего устройства для генерирования дополнительного аналогового выходного сигнала 106b. Несмотря на то, что будет описана система 100, различные варианты реализации, приведенные в данном документе, применяют к системе 400 в тех случаях, в которых это применимо.

На фиг. 2 показаны различные биты 111а-е данных, проходящие через параллельные каналы 104 для передачи данных в системе 100 в соответствии с одним из вариантов реализации настоящего изобретения. На фиг. 2 показана обработка битов 111а-е данных по мере прохождения битов 111а-е данных через мезохронный интерфейс 110 цифровых компонентов, схему 120 мультиплексора, схему 130 декодирующего устройства и схему 140 микширующего устройства. Параллельная шина 113а данных может содержать биты 111а данных, обеспеченные в параллельных цифровых словах A-D. В некоторых вариантах реализации каждое из цифровых слов A-D (например, слов входных данных мезохронного интерфейса) содержит двенадцать бит 111а параллельных данных. Схема 110 мезохронного интерфейса обеспечивает прохождение битов 111а входных данных мезохронного интерфейса, соответствующих параллельным цифровым словам A-D, на схему 120 мультиплексора при тактовой частоте (Fs/M) мультиплексора и тактовом домене мультиплексора, как описано в данном документе.

Схема 120 мультиплексора принимает биты 111b входных данных мультиплексора, соответствующие словам A-D параллельных цифровых данных (например, словам 111b параллельных цифровых данных), по параллельной шине 113b данных и обеспечивает последовательный поток 208 данных, соответствующий одному биту 209 каждого из параллельных цифровых слов A-D (например, двенадцать бит 111 с данных каждого из параллельных цифровых слов A-D) на схему 130 декодирующего устройства по параллельной шине 113c данных. При этом схема 120 мультиплексора выдает слова А, В, С, D параллельных цифровых данных в последовательном порядке по параллельной шине 113с данных, причем схема 120 мультиплексора выбирает последовательный порядок слов А, В, С, D цифровых данных, а слово А цифровых данных тактируют первым вслед за словами В, С и D, как показано на фиг. 2. В качестве примера, мультиплексор типа 4:1 показан на фиг. 2. Однако в других вариантах реализации возможны и другие конфигурации мультиплексора.

Схема 130 декодирующего устройства принимает параллельное цифровое слово 237 (например, одно из параллельных цифровых слов А, В, С или D), в том числе биты 111c входных данных декодирующего устройства по параллельной шине 113c данных. Биты 111c данных содержат первую подсовокупность 234 (например, пять бит 111c данных) и вторую подсовокупность 238 (например, семь бит 111c данных). В некоторых вариантах реализации схема 130 декодирующего устройства преобразует первую подсовокупность 234 во второй формат 239. В некоторых вариантах реализации пять бит с двоичным кодом (например, первая подсовокупность 234) преобразуют в тридцать один термометрический кодированный бит 111d данных (например, второй формат 239) для выдачи тридцати восьми декодированных бит 111d параллельных цифровых данных, состоящих из тридцати одного термометрического кодированного бита 111d данных и семи бит 111d данных с двоичным кодом, по параллельной шине 113d данных. Один или более битов 111d данных могут иметь расхождение по времени друг с другом по причине задержек 206, связанных с логическими операциями, выполняемыми в декодирующей схеме 130. Будет понятно, что другие варианты реализации могут содержать кодированные биты данных иных типов, а схема декодирующего устройства может декодировать большее или меньшее количество битов данных в конфигурации декодирования одного или более типов.

Схема 140 микширующего устройства принимает декодированные биты 111d параллельных цифровых данных (например, биты 111d входных данных микширующего устройства) по параллельной шине 113d данных. В некоторых вариантах реализации декодированные биты 111d параллельных цифровых данных могут содержать первую подсовокупность 244 битов 111d данных (например, первую подсовокупность термометрических кодированных битов данных) и вторую подсовокупность 249 битов 111d данных (например, вторую подсовокупность битов данных с двоичным кодом). В некоторых вариантах реализации биты 111d входных данных микширующего устройства сдвигают по частоте с использованием тактового сигнала 145 преобразования. В некоторых вариантах реализации тактовый сигнал 145 преобразования по существу имеет ту же частоту, что и частота дифференциального тактового сигнала 175. В других вариантах реализации тактовый сигнал 145 преобразования представляет собой целое кратное от частоты дифференциального тактового сигнала 175. Биты 111e цифровых данных со сдвигом частоты, в том числе имеющие временное расхождение биты 111e данных из сдвинутых по частоте первой подсовокупности 244 и второй подсовокупности 249, подают на схему 105 синхронизирующего устройства по параллельной шине 113е данных. Один или более битов 111e цифровых данных со сдвигом частоты могут иметь расхождение по времени друг с другом после перемножения операций, выполняемых схемой 140 микширующего устройства, как описано в данном документе.

В одном из вариантов реализации схема 105 синхронизирующего устройства принимает имеющие временное расхождение биты 111e данных из сдвинутой по частоте первой подсовокупности 244 и второй подсовокупности 249 по параллельной шине 113е данных. Биты 111e данных принимают из схемы 140 микширующего устройства в канале 104 для передачи данных. Схема 105 синхронизирующего устройства выполняет операции по выравниванию по времени битов 111e данных для выдачи выровненных по времени битов 112а цифровых данных со сдвигом частоты по параллельной шине 114а данных, как описано в данном документе. В различных вариантах реализации схема 105 синхронизирующего устройства выполняет выравнивание по времени имеющих временное расхождение битов 111e данных при частоте тактового сигнала 155 для синхронизирующего устройства, которая вдвое превышает частоту дифференциального тактового сигнала 175, для уменьшения восприимчивости системы 100 к процессу, температуре и изменениям при подаче энергии питания. Однако для тактового сигнала 155 синхронизирующего устройства возможны и другие частоты, кратные частоте дифференциального тактового сигнала 175. Выходные данные (например, биты 112а данных) схемы 105 синхронизирующего устройства выдают на коммутационную сеть 102. Коммутационная сеть 102 преобразует биты 112а данных в аналоговый выходной сигнал 106. Основная спектральная энергия аналогового выходного сигнала 106 сосредоточена вокруг частоты тактового сигнала 145 преобразования.

На фиг. 3 показан процесс работы системы 100 в соответствии с одним из вариантов реализации настоящего изобретения. При описании процесса работы системы 100 на одну или более из фиг. 4-11 может быть приведена ссылка. Кроме того, этапы, показанные на фиг. 3, могут быть осуществлены в порядке, отличном от порядка, описанного в данном документе.

В блоке 305 процесс начинается с приведения в действие схемы 103 тактирования для выдачи тактовых сигналов на компоненты системы 100. При этом схема 103 тактирования содержит тактовый генератор 170 для генерирования дифференциального локального тактового импульса, схему 180 детектора переднего и заднего фронтов и схему 191 разделительного устройства для разделения тактовых импульсов, как описано в данном документе. Схема 180 детектора переднего и заднего фронтов принимает дифференциальный локальный тактовый сигнал 175 от тактового генератора 170 для генерирования дифференциального локального тактового импульса для получения одиночного конечного тактового сигнала 155 для синхронизирующего устройства, как описано в данном документе. На фиг. 7А показана структурная схема схемы 180 детектора переднего и заднего фронтов в соответствии с одним из вариантов реализации настоящего изобретения.

Согласно фиг. 7А, положительный дифференциальный тактовый сигнал 175а (например, сигнал LO_CLK_P) подают на первый вход 787 схемы 180 детектора переднего и заднего фронтов. Отрицательный дифференциальный тактовый сигнал 175b (например, сигнал LO_CLK_N) подают на второй вход 788 схемы 180 детектора переднего и заднего фронтов. Положительный и отрицательный дифференциальные тактовые сигналы 175а и 175b проходят соответственно резистивные усилители 776а и 776b с обратной связью. Схема 180 детектора переднего и заднего фронтов содержит множество логических вентилей 789 для выполнения логических операций в ответ на положительный дифференциальный тактовый сигнал 175а и отрицательный дифференциальный тактовый сигнал 175b для образования тактового сигнала 155 для синхронизирующего устройства (например, сигнал 2NFs Clock), причем тактовый сигнал 155 для синхронизирующего устройства представляет собой одиночный конечный тактовый сигнал 757, имеющий частоту (2NFs), которая вдвое превышает частоту дифференциального тактового сигнала 175 (NFs).

На фиг. 7В показана временная диаграмма 702 схемы 180 детектора переднего и заднего фронтов в соответствии с одним из вариантов реализации настоящего изобретения. Согласно фиг. 7В, временная диаграмма 702 иллюстрирует соотношение между тактовым сигналом 155 для синхронизирующего устройства, а также положительным дифференциальным тактовым сигналом 175а и отрицательным дифференциальным тактовым сигналом 175b. На фиг. 7В показано, что первый тактовый импульс 756а для синхронизирующего устройства образуют в ответ на передний фронт положительного дифференциального тактового сигнала 175а и/или задний фронт отрицательного дифференциального тактового сигнала 175b. Кроме того, второй тактовый импульс 756b синхронизирующего устройства образуют в ответ на задний фронт положительного дифференциального тактового сигнала 175а и/или передний фронт отрицательного дифференциального тактового сигнала 175b. При этом тактовый сигнал 155 для синхронизирующего устройства реализует частоту, вдвое превышающую (например, в целое число раз) частоту дифференциального локального тактового сигнала 175.

Согласно фиг. 3, в блоке 305 схема 191 разделительного устройства для разделения тактовых импульсов принимает одиночный конечный тактовый сигнал 155 для синхронизирующего устройства и делит этот тактовый сигнал 155 для синхронизирующего устройства на целочисленное значение 146 для получения тактового сигнала 145 преобразования, как описано в данном документе. Схема 191 разделительного устройства для разделения тактовых импульсов реализована с возможностью деления тактового сигнала 145 преобразования на целочисленное значение 136 для получения тактового сигнала 135 для декодирующего устройства, как описано в данном документе. Схема 191 разделительного устройства для разделения тактовых импульсов реализована с возможностью разделения тактового сигнала 135 для декодирующего устройства на целочисленное значение 126 (например, целочисленное значение М) для получения тактового сигнала 125 для мультиплексора, как описано в данном документе. На фиг. 5 показана временная диаграмма схемы 103 тактирования в соответствии с одним из вариантов реализации настоящего изобретения.

На фиг. 5 показана взаимосвязь между тактовым сигналом 155 для синхронизирующего устройства, тактовым сигналом 145 преобразования, тактовым сигналом 135 для декодирующего устройства и тактовым сигналом 125 для мультиплексора. Например, в показанном варианте реализации целое кратное 146 равно одному, целое 126 кратное равно четырем. Кроме того, дифференциальный локальный тактовый сигнал 175 (не показан) имеет 3,2 миллиарда выборок в секунду (Gsps). При этом тактовый сигнал 145 преобразования и тактовый сигнал 135 для декодирующего устройства имеют 3,2 миллиардов выборок в секунду (Gsps), а тактовый сигнал 125 для мультиплексора имеет 0,8 миллиардов выборок в секунду (Gsps). В некоторых вариантах реализации тактовый сигнал 135 для декодирующего устройства работает при заданной частоте дискретизации Fs. Как показано на фиг. 5, тактовый сигнал 155 для синхронизирующего устройства представляет собой удвоенный дифференциальный локальный тактовый сигнал 175 или имеет 6,4 миллиардов выборок в секунду (Gsps). Кроме того, имеющие временное расхождение биты 111e данных дискретизируют при 6,4 миллиардах выборок в секунду (Gsps) посредством схемы 105 синхронизирующего устройства. Дискретизирование посредством схемы 105 синхронизирующего устройства при частоте дискретизации тактового сигнала 155 для синхронизирующего устройства способствует постоянной выработке энергии при частоте передачи данных и изменениях температуры на информационном выходе коммутационной сети, как описано в данном документе. Следует понимать, что временная диаграмма, показанная на фиг. 5, обеспечивает неограничивающий вариант реализации настоящего изобретения. В других вариантах реализации возможны иные временные диаграммы с другими тактовыми частотами.

Согласно фиг. 3, в блоке 310 схема 110 мезохронного интерфейса принимает биты 111а входных данных, соответствующие словам A-D параллельных цифровых данных (например, словам входных данных мезохронного интерфейса) по параллельной шине 113а данных. Мезохронный интерфейс принимает тактовый сигнал 125 для мультиплексора на тактовом выходе 110b мезохронного интерфейса и тактовый сигнал 115 для мезохронного интерфейса на тактовом входе 110а мезохронного интерфейса, причем тактовый сигнал 115 для мезохронного интерфейса является мезохронным по отношению к тактовому сигналу 125 для мультиплексора, как описано в данном документе. Биты 111а входных данных мезохронного интерфейса тактируют посредством тактового сигнала 115 для мезохронного интерфейса с обеспечением приема битов 111а входных данных мезохронного интерфейса в мезохронном интерфейсе 110.

В блоке 315 мезохронный интерфейс 110 преобразует тактовую область битов 111а входных данных мезохронного интерфейса с использованием тактового сигнала 125 для мультиплексора для тактирования битов 111b входных данных мультиплексора на схему 120 мультиплексора. Биты 111b входных данных мультиплексора соответствуют словам A-D параллельных цифровых данных.

В блоке 320 схема 120 мультиплексора принимает биты 111b входных данных мультиплексора, соответствующие словам A-D параллельных цифровых данных, по параллельной шине 113b данных. Схема 120 мультиплексора объединяет биты 111b входных данных мультиплексора для получения битов 111с входных данных декодирующего устройства, тактируемых посредством тактового сигнала 135 для декодирующего устройства, на схему 130 декодирующего устройства. При этом схема 120 мультиплексора выбирает соответствующее одно из слов A-D параллельных цифровых данных, причем одно из слов A-D параллельных цифровых данных выбирают с обеспечением его выдачи на схему 130 декодирующего устройства. Последующие тактовые циклы обеспечивают остальные слова A-D параллельных цифровых данных. Порядок слов параллельных цифровых данных при тактировании составляет А, В, С, D, причем слово А цифровых данных тактируют первым, а за ним следуют слова В, С и D. Тактирование слов A-D цифровых данных с использованием тактового сигнала 135 для декодирующего устройства обеспечивает эквивалент тактированию слов A-D с использованием тактового сигнала 125 для мультиплексора.

В блоке 325 схема 130 декодирующего устройства принимает биты 111c входных данных декодирующего устройства, в том числе первую подсовокупность 234 и вторую подсовокупность 238, причем каждая подсовокупность 234 и 238 имеют первый формат (например, такие как биты данных с двоичным кодом). В некоторых вариантах реализации по меньшей мере первую подсовокупность 234 битов 111с входных данных декодирующего устройства преобразуют во второй формат 239 (например, такие как термометрические кодированные биты данных). При этом первую подсовокупность 244 декодированных битов 111d данных выдают на схему 140 микширующего устройства.

В блоке 330 в некоторых вариантах реализации обеспечивают прохождение второй подсовокупности 249 битов 111d данных в схему 140 микширующего устройства без декодирования (например, остальные биты данных с двоичным кодом), как описано в данном документе.

В блоке 335 схема 140 микширующего устройства принимает биты 111d входных данных микширующего устройства, в том числе биты 244 данных из первой подсовокупности и биты 249 данных из второй подсовокупности. На фиг. 6А показана структурная схема, иллюстрирующая схему 140 микширующего устройства в соответствии с одним из вариантов реализации настоящего изобретения. Согласно фиг. 6А, в некоторых вариантах реализации схема 140 микширующего устройства содержит множество логических компонентов 643(1)-643(n) типа исключающее ИЛИ, принимающих тактовые сигналы 145(1)-145(n) преобразования (например, сигналы NFs Clock) и декодированные биты 111(d)(1) параллельных цифровых данных (например, Mixer_in(1))-111(d)(n) (например, Mixer-in (n)), и выдающих биты 111(е(1) цифровых данных со сдвигом частоты (например, Mixer_out(l))-111(e)(n) (например, Mixer_out(n). При этом каждая схема 643 типа исключающее ИЛИ в микширующем устройстве объединяет один бит 111d данных и один тактовый сигнал 145 преобразования для выдачи соответствующего бита 111e цифровых данных со сдвигом частоты. Возможны и другие варианты реализации схемы 140 микширующего устройства. Например, схема 140 микширующего устройства может содержать мультиплексоры или сложные логические вентили для реализации рабочих функциональных возможностей схемы 140 микширующего устройства.

На фиг. 6В показана временная диаграмма схемы 140 микширующего устройства в соответствии с одним из вариантов реализации настоящего изобретения. Согласно фиг. 6В, на временной диаграмме представлены биты 111(d)(1) входных данных микширующего устройства (например, Mixer_in), тактовый сигнал 145(1) преобразования (например, NFs Clock) и информационный сигнал 603 из битов 111(e)(1) выходных данных микширующего устройства (например, Mixer_out). Как показано, логические операции осуществляют в отношении битов 111(d)(1) данных и тактового сигнала 145(1) для получения битов 111(e)(1) данных. При этом информационный сигнал 603 из битов 111(e)(1) данных имеет верхний переход, когда биты 111(d)(1) данных и тактовый сигнал 145(1) находятся в различных логических состояниях, что обеспечивает эффективное умножение битов 111(d)(1) данных на тактовый сигнал 145 преобразования с обеспечением сдвига энергии битов 111(d)(1) данных для сосредоточения вокруг частоты NFs тактового сигнала преобразования.

Как показано на фиг. 6В, биты 111e цифровых данных со сдвигом частоты могут приобрести временное расхождение по отношению друг к другу за счет временного расхождения, связанного с переходами логического состояния каждого из указанных декодированных битов 111(d) параллельных цифровых данных и переходами логического состояния тактового сигнала 145 преобразования. Кроме того, биты 111e данных могут иметь нежелательные искажения 605 вследствие временного расхождения фронтов между битами 111(d)(1) входных данных микширующего устройства и тактовым сигналом 145(1) преобразования.

На фиг. 6С показана структурная схема, иллюстрирующая схему 602 микширующего устройства (например, ячейку цифрового микширующего устройства) в соответствии с одним из вариантов реализации настоящего изобретения. Согласно схематическому изображению, показанному на фиг. 6С, схема 602 микширующего устройства обеспечивает одиночный бит 111(d)(1) входных данных микширующего устройства (например, Mixer_in), тактовый сигнал 145(1) преобразования (например, NFs Clock) и бит 111(e)(1) выходных данных микширующего устройства (например, Mixer_out). В некоторых вариантах реализации схему 140 микширующего устройства содержит схему 602 микширующего устройства для каждого бита 111d данных. При этом необходимое количество схем 602 микширующего устройства может изменяться на основании количества декодированных битов 244 данных и недекодированных битов 249 данных из битов 111d данных, выданных схемой 130 декодирующего устройства. В различных вариантах реализации логические операции осуществляют в отношении каждого из битов 111d данных на входах микширующего устройства с помощью тактового сигнала 145 преобразования для получения возможных имеющих временное расхождение битов 111e данных на схему 105 синхронизирующего устройства.

Как показано на фиг. 6С, схема 602 микширующего устройства реализована в виде КМОП-схемы 636 с управлением по напряжению. Статическая энергия уменьшается ввиду отсутствия постоянных источников тока, включенных в КМОП-схему 636 с управлением по напряжению. Кроме того, энергия первоначально рассеивается во время переходов логического состояния данных и тактового импульса, что в результате приводит к уменьшению рассеяния энергии. При этом топология с управлением по напряжению обеспечивает уменьшение рассеяния энергии и уменьшение потребления энергии, что важно для областей применения, связанных с космосом.

В блоке 340 имеющие временное расхождение биты 111e данных синхронизируют для выдачи выровненных по времени битов 112а цифровых данных со сдвигом частоты на коммутационную сеть 102. На фиг. 8А показана структурная схема, иллюстрирующая схему 105 синхронизирующего устройства в соответствии с одним из вариантов реализации настоящего изобретения. Согласно структурной схема, показанной на фиг. 8А, схема 105 синхронизирующего устройства обеспечивает одиночный бит 111(e)(1) входных данных синхронизирующего устройства (например, Sync_in) на информационном входе 804(a) схемы синхронизирующего устройства, тактовый сигнал 855(a) для синхронизирующего устройства (например, сигнал 2NFs Clock) на тактовом входе 806(a) схемы синхронизирующего устройства и бит 112(a)(1) выходных данных синхронизирующего устройства (например, Sync_out) на информационном выходе 810(a) схемы синхронизирующего устройства.

В некоторых вариантах реализации схема 105 синхронизирующего устройства реализована в виде схемы 805 Д-триггера, причем схема 805 Д-триггера защелкивает имеющий временное расхождение бит 111(e)(1) данных в ответ на тактовый сигнал 855а для синхронизирующего устройства для получения выровненного по времени бита 112(a)(1) цифровых данных со сдвигом частоты на информационном выходе 810(a) схемы синхронизирующего устройства. При этом имеющий временное расхождение бит 111(e)(1) данных сохраняют на информационном входе 804(a) схемы синхронизирующего устройства до тех пор, пока передний фронт одиночного конечного тактового сигнала 855а для синхронизирующего устройства не обеспечат на тактовом входе 806(a) схемы синхронизирующего устройства для выдачи выровненного по времени бита 112(a)(1) данных на коммутационную сеть 102.

В некоторых вариантах реализации схема 105 синхронизирующего устройства содержит множество цепей 805 Д-триггера, причем каждая схема 805 Д-триггера обеспечена для каждого бита 111(е)(1)-111(е)(n) данных. При этом необходимое количество схем 805 Д-триггера может изменяться на основании количества имеющих временное расхождение битов 111e данных из поднабора 244 и поднабора 249, обеспеченных схемой 140 микширующего устройства. В некоторых вариантах реализации схема 805 Д-триггера и схема 105 синхронизирующего устройства реализованы в виде КМОП схемы 836 с управлением по напряжению.

В некоторых вариантах реализации тактовый сигнал 155 для синхронизирующего устройства разветвляют на каждую схему 805 Д-триггера. На фиг. 8В показана структурная схема, иллюстрирующая схему распределения тактовых импульсов синхронизирующего устройства 807 в соответствии с одним из вариантов реализации настоящего изобретения. Согласно фиг. 8В, схема 807 синхронизирующего устройства для распределения тактовых импульсов обеспечивает тактовое распределение тактового сигнала 155 для синхронизирующего устройства на каждую из схем 805 Д-триггера в схеме 105 синхронизирующего устройства.

Как показано на фиг. 8В, канал 852 для распределения тактовых импульсов обеспечивает идентичное количество инверторных каскадов 848 для каждого тактового сигнала 855а-n для синхронизирующего устройства вдоль канала для передачи сигналов из тактового входа 105а синхронизирующего устройства на каждый соответствующий тактовый вход 806а-n схемы синхронизирующего устройства. При обеспечении наличия эквивалентного количества инверторных каскадов 848 вдоль каждого канала для передачи тактовых сигналов 855а-n для синхронизирующего устройства, сведена к минимуму задержка на время прохождения между тактовыми сигналами 855а-n на тактовых входах 806а-n. В значительной степени одновременные передние фронты тактовых сигналов 855а-n для синхронизирующего устройства выдают на соответствующие тактовые входы 806а-n соответствующей схемы 805а-n Д-триггера для одновременного тактирования имеющих временное расхождение битов 111(е)(1)-111(е)(n) данных для получения выровненных по времени битов 112(а)(1)-112(а)(n) данных на соответствующие информационные выходы 810а-n схемы Д-триггера. При этом схема 105 синхронизирующего устройства выдает выровненные по времени биты 112а данных на коммутационную сеть 102.

На фиг. 9 показаны временные диаграммы схемы 140 микширующего устройства и схемы 105 синхронизирующего устройства в соответствии с вариантами реализации настоящего изобретения. На фиг. 9 показаны временные функции для одного бита 111e данных в схеме 140 микширующего устройства и одного бита 112а данных в схеме 105 синхронизирующего устройства для иллюстрации того, как искажения 605 могут возникать на выходе микширующего устройства, а также того, как схема 105 синхронизирующего устройства устраняет искажения 605 в дополнение к выравниванию многочисленных битов 111e данных с использованием тактового сигнала 155 для синхронизирующего устройства. Согласно фиг. 9, временные диаграммы обеспечивают схему 140 микширующего устройства, биты 111(d)(1) входных данных микширующего устройства (например, Mixer_in), тактовый сигнал 145(1) преобразования (например, NFs Clock) и информационный сигнал 603 битов 111(e)(1) выходных данных микширующего устройства (например, Mixer_out). Кроме того, временные диаграммы обеспечивают схему 105 синхронизирующего устройства, биты 111(e)(1) входных данных синхронизирующего устройства (например, Sync_in), тактовый сигнал 855(a) для синхронизирующего устройства (например, 2NFs Clock) и информационный сигнал 903 битов 112(a)(1) выходных данных синхронизирующего устройства (например, Sync_out). На фиг. 9 показан сдвиг частоты битов 111(d)(1) данных для получения имеющих временное расхождение битов 111(e)(1) данных, которые также могут иметь нежелательные искажения 605 за счет временного расхождения фронтов между битами 111(d)(1) входных данных микширующего устройства и тактовым сигналом 145 преобразования, как описано в данном документе. Биты 111(e)(1) цифровых данных со сдвигом частоты выдают в схему 105 синхронизирующего устройства, причем эти биты 111(e)(1) данных дискретизируют для получения выровненных по времени битов 112(a)(1) цифровых данных со сдвигом частоты, а также для устранения искажений 605.

На фиг. 9 показано, как тактовый сигнал 855(a) для синхронизирующего устройства дискретизирует биты 111(e)(1) входных данных синхронизирующего устройства для обеспечения точного и высокоскоростного выравнивания по времени битов 111(e)(1) данных, как описано в данном документе. В некоторых вариантах реализации частота тактового сигнала 145(1) преобразования сдвигает биты 111(e)(1) данных при частоте преобразования, составляющей 3,2 миллиардов выборок в секунду (Gsps). Тактовый сигнал 855(a) для синхронизирующего устройства дискретизирует биты 111(e)(1) данных при тактовой частоте синхронизирующего устройства, составляющей 6,4 миллиарда выборок в секунду (Gsps) и в два раза превышающей частоту дискретизации схемы микширующего устройства. Однако с другими вариантами реализации возможны и более высокие или более низкие частоты дискретизации. Схема 105 синхронизирующего устройства обеспечивает адаптируемость для модификации частот дискретизации без необходимости в перенастройке или перепроектировании системы 100.

В блоке 345 выровненные по времени биты 112а цифровых данных со сдвигом частоты преобразуют в аналоговые сигналы напряжения и суммируют для получения аналогового выходного сигнала 106. При этом коммутационная сеть 102 принимает выровненные по времени биты 112а данных и преобразует эти выровненные по времени биты 112а данных в соответствующие аналоговые сигналы напряжения, как описано в данном документе. На фиг. 10 показана структурная схема коммутационной сети 102 в соответствии с одним из вариантов реализации настоящего изобретения.

Согласно фиг. 10, в некоторых вариантах реализации коммутационная сеть 102 может быть реализована в виде множества инверторных схем на комплементарных структурах металл-оксид-полупроводник, управляющих резисторной схемой (например, такой как схемы 1013 с термометрическим взвешиванием и схемы 1015 с двоичным взвешиванием), причем каждая резисторная схема с инверторными схемами на комплементарных структурах металл-оксид-полупроводник принимает соответствующий выровненный по времени бит 112а данных на основании весового коэффициента, присвоенного биту 112а данных, и преобразует соответствующий бит 112а цифровых данных в соответствующий сигнал 1006 напряжения. Сигналы 1006 напряжения суммируют в суммирующем узле 1008 и выдают в виде аналогового выходного сигнала 106. Следует учитывать, что количество сигналов 1006 напряжения и/или резисторы 1023/1025 могут изменяться на основании количества выровненных по времени битов 112а цифровых данных со сдвигом частоты.

В некоторых вариантах реализации, как показано на фиг. 10, первую подсовокупность 244 из декодированных битов 112(а)(1)-112(а)(31) данных термометра выдают на матрицу 1012 схем с термометрическим взвешиванием, а вторую подсовокупность 249 из недекодированных битов 112(а)(32)-112(а)(38) двоичных данных выдают на матрицу 1014 схем с двоичным взвешиванием. При этом коммутационная сеть 102 принимает термометрические декодированные биты 112(а)(1)-112(а)(31) данных соответственно на информационном входе 1005(1)-1005(31) коммутационной сети. Коммутационная сеть 102 принимает недекодированные биты 112(а)(32)-112(а)(38) двоичных данных соответственно на информационном входе 1005(32)-005(38) коммутационной сети.

В некоторых вариантах реализации каждая из множества схем 1013 с термометрическим взвешиванием в коммутационной сети 102 содержит последовательные пары из инверторных схем 1021 и резистора 1023 постоянного сопротивления. При этом каждому из термометрических декодированных битов 112(а)(1)-112(а)(31) данных присвоены одинаковые весовые коэффициенты, а по существу эквивалентное напряжение на выходе 1006(1)-1006(31) выдают на суммирующий узел 1008 посредством каждой из схем 1013 с термометрическим взвешиванием.

В некоторых вариантах реализации каждая из множества схем 1015 с двоичным взвешиванием в коммутационной сети 102 содержит последовательные пары из инверторных схем 1021 и переменного резистора 1025. Значение резистора 1025 переменного сопротивления для каждого бита 112(а)(32)-112(а)(38) данных идентифицируют на основании веса битов 112(а)(32)-112(а)(38) двоичных данных. Например, бит 112(а)(38) данных может иметь меньшую значимость по сравнению с битом 112(а)(31) данных. При этом сигнал напряжения на выходе 1006(38), соответствующем биту 112(а)(38) данных, может быть слабее сигнала напряжения на выходе 1006(31), соответствующем биту 112(а)(31) данных. Соответственно, переменный резистор 1025, соединенный с выходом 1006(38), имел бы большее значение по сравнению с переменным резистором 1025, соединенный с выходом 1006(31). При этом каждому из недекодированных битов 112(а)(32)-112(а)(38) двоичных данных весовой коэффициент присваивают пропорционально значимости этого бита (например, от наименьшей значимости до наибольшей значимости), а соответствующие напряжения выдают на выходах 1006(31)-1006(38) в суммирующий узел 1008. В некоторых вариантах реализации коммутационная сеть 102 реализована в виде КМОП-схемы 1036 с управлением по напряжению для обеспечения низкого рассеивания мощности и низкого потребления энергии.

В некоторых вариантах реализации коммутационная сеть 102 содержит резисторы R39 и R40 смещения. Резистор R39 смещения соединен с источником напряжения (VDDA) на первом конце и соединен с суммирующим узлом 1008 на втором конце. Резистор R40 смещения соединен с землей (GNDA) (например, замыкание постоянного тока на землю) на первом конце и соединен с суммирующим узлом 1008 на втором конце. В некоторых вариантах реализации сопротивление резистора R39 смещения по существу равно сопротивлению резистора R40 смещения. Резистор R39 смещения и/или резистор R40 смещения задают напряжение 1010 смещения аналогового выходного сигнала 106. Кроме того, выходной импеданс аналогового выходного сигнала 106 установлен фиксированным путем комбинирования резисторов R39/R40 смещения и резисторов 1023/1025.

На фиг. 11 показан график 1100 зависимости энергии сигнала от частоты для цифроаналогового преобразователя с повышением частоты в соответствии с одним из вариантов реализации настоящего изобретения. Согласно фиг. 11, график 1100 иллюстрирует основную спектральную энергию 1106 аналогового выходного сигнала 106, сосредоточенного при частоте в приблизительно 3,2 ГГц, а именно между второй зоной 1115 Найквиста и третьей зоной 1125 Найквиста. В данном примере частота (Fs) дискретизации, используемая схемой 130 декодирующего устройства, составляет 3,2 ГГц, а цифровые данные, обрабатываемые схемой 130 декодирующего устройства, имеют частоту 100 МГц (например, частоту информационного сигнала), как показано посредством сигнала 1130 на графике 1100. Частота (NFs) микширующего устройства также составляет 3,2 ГГц, при этом схема 140 устройства цифрового микширования сдвигает большее количество из энергии в цифровых данных до 3,1 ГГц и 3,3 ГГц (например, частота микширующего устройства +/- частота информационного сигнала), как показано сигналами 1106 на графике 1100. Гармоники, имеющие меньшую мощность, возникают при кратных значениях частоты микширующего устройства (например, 6,4 ГГц и 9,6 ГГц), как показано сигналами 1135 и сигналами 1140 на графике 1100. Частота синхронизации составляет 6,4 ГГц и не может быть распознана на графике 1100 спектральной энергии.

Ввиду настоящего изобретения, следует учитывать, что обеспечение системы 100 в соответствии с различными вариантами реализации, заданными в данном документе, может обеспечивает адаптируемое и высокоскоростное цифроаналоговое преобразование с повышением частоты множества битов параллельных цифровых данных в аналоговый выходной сигнал напряжения. При этом за счет осуществления преобразования из внешнего во внутренний тактовый домен, мультиплексирования параллельных информационных сигналов, декодирования битов параллельных цифровых данных и операции сдвига частоты битов параллельных цифровых данных из параллельных каналов для передачи данных, а также выравнивания по времени битов параллельных цифровых данных, которые приобретают временное расхождение по отношению друг к другу, все включены в топологии схем с управлением по напряжению и несимметричные тактирующие схемы, настроенные на низкое рассеяние энергии и низкое потребление энергии, адаптируемое высокоскоростное цифроаналоговое преобразование с высоким разрешением может быть реализовано для системы спутниковой связи.

В случаях, где это применимо, различные варианты реализации, описанные в данном документе, могут быть реализованы с использованием аппаратных средств, программного обеспечения или их комбинации. Кроме того, в случаях, где это применимо, различные аппаратные компоненты и/или программные компоненты, заданные в данном документе, могут быть объединены в составные компоненты, содержащие программное обеспечение и/или аппаратные средства, без выхода за рамки сущности настоящего изобретения. В случаях, где это применимо, различные аппаратные компоненты и/или программные компоненты, заданные в данном документе, могут быть разделены на подкомпоненты, содержащие программное обеспечение и/или аппаратные средства, без выхода за рамки сущности настоящего изобретения. Кроме того, в случаях, где это применимо, предполагается, что программные компоненты могут быть реализованы в виде аппаратных компонентов и наоборот.

Программное обеспечение в соответствии с настоящим изобретением, такое как программный код и/или данные, может храниться в одном или более некратковременных машиночитаемых носителях для данных. Кроме того, предполагается, что программное обеспечение, указанное в данном документе, может быть реализовано с использованием одного или более компьютеров общего назначения или специального назначения и/или вычислительных систем, в частности систем, объединенных в сеть и/или связанных иным образом. В случаях, где это применимо, порядок различных этапов, описанных в данном документе, может быть изменен, при этом указанные этапы могут быть объединены в более составные этапы и/или могут быть разделены на подэтапы для обеспечения признаков, описанных в данном документе.

Вышеописанные варианты реализации иллюстрируют, но не ограничивают настоящее изобретение. Кроме того, следует понимать, что в соответствии с принципами настоящего изобретения возможны многочисленные модификации и изменения. Соответственно, объем настоящего изобретения задан исключительно приведенной далее формулой изобретения.

Группа изобретений относится к области цифроаналогового преобразования, в частности к реализациям высокоскоростного и маломощного цифроаналогового преобразователя с повышением частоты. Техническим результатом является уменьшение временного расхождения битов параллельных цифровых данных по отношению друг к другу. Устройство содержит схему декодирующего устройства, причем схема декодирующего устройства работает при заданной частоте дискретизации, схему микширующего устройства, соединенную со схемой декодирующего устройства и выполненную с возможностью объединения каждого из декодированных битов параллельных цифровых данных с тактовым сигналом преобразования для получения битов цифровых данных со сдвигом частоты, которые имеют временное расхождение по отношению друг к другу, схему синхронизирующего устройства, соединенную со схемой микширующего устройства, располагающую тактовым сигналом для синхронизирующего устройства и выполненную с возможностью выравнивания по времени указанных битов цифровых данных со сдвигом частоты в ответ на тактовый сигнал для синхронизирующего устройства, и коммутационную сеть, соединенную со схемой синхронизирующего устройства. 2 н. и 18 з.п. ф-лы, 15 ил.

1. Система (100) для цифроаналогового преобразования, содержащая:

схему (130) декодирующего устройства, выполненную с возможностью приема множества битов (111c) входных данных декодирующего устройства и возможностью выдачи множества декодированных битов (111d) параллельных цифровых данных, причем схема декодирующего устройства работает при заданной частоте дискретизации (Fs),

схему (140) микширующего устройства, соединенную со схемой декодирующего устройства и выполненную с возможностью объединения каждого из декодированных битов параллельных цифровых данных с тактовым сигналом (145) преобразования для получения битов (111e) цифровых данных со сдвигом частоты, которые имеют временное расхождение по отношению друг к другу,

схему (105) синхронизирующего устройства, соединенную со схемой микширующего устройства, располагающую тактовым сигналом (155) для синхронизирующего устройства и выполненную с возможностью выравнивания по времени указанных битов цифровых данных со сдвигом частоты в ответ на тактовый сигнал для синхронизирующего устройства, и

коммутационную сеть (102), соединенную со схемой синхронизирующего устройства и выполненную с возможностью генерирования аналогового выходного сигнала (106) в ответ на выровненные по времени биты (112a) цифровых данных со сдвигом частоты.

2. Система по п. 1, в которой биты цифровых данных со сдвигом частоты имеют временное расхождение по отношению друг к другу за счет временного расхождения, связанного с переходами логического состояния каждого из декодированных битов параллельных цифровых данных и переходами логического состояния тактового сигнала преобразования.

3. Система по п. 1, в которой схема микширующего устройства выполнена с возможностью преобразования декодированных битов параллельных цифровых данных при первой частоте (Fs) в биты цифровых данных со сдвигом частоты при второй частоте (NFs) и работы при частоте, превышающей в N раз заданную частоту дискретизации,

причем схема синхронизирующего устройства выполнена с возможностью работы при частоте, вдвое превышающей частоту схемы микширующего устройства.

4. Система по п. 1, в которой аналоговый выходной сигнал имеет полосу (1130) пропускания, соответствующую полосе пропускания битов входных данных декодирующего устройства,

причем основная спектральная энергия (1106) аналогового выходного сигнала сосредоточена вокруг частоты (NFs) тактового сигнала преобразования.

5. Система по п. 1, дополнительно содержащая схему (120) мультиплексора, соединенную со схемой декодирующего устройства и выполненную с возможностью приема множества слов (111b) параллельных цифровых данных в ответ на тактовый сигнал (125) для мультиплексора и возможностью получения соответствующего одного из указанных слов (237) параллельных цифровых данных, содержащих биты входных данных декодирующего устройства при заданной частоте дискретизации,

причем тактовый сигнал для мультиплексора имеет частоту (Fs/M) дискретизации, превышающую в 1/M раз заданную частоту дискретизации.

6. Система по п. 5, дополнительно содержащая схему (110) мезохронного интерфейса, соединенную со схемой мультиплексора и выполненную с возможностью приема от внешнего источника множества слов (111a) входных данных мезохронного интерфейса, синхронизированных посредством внешнего тактового сигнала (115), и возможностью получения указанного множества слов параллельных цифровых данных, синхронизированных посредством тактового сигнала для мультиплексора,

причем внешний тактовый сигнал является асинхронным по отношению к тактовому сигналу для мультиплексора.

7. Система по п. 1, в которой

схема микширующего устройства представляет собой первую схему микширующего устройства,

схема синхронизирующего устройства представляет собой первую схему синхронизирующего устройства,

коммутационная сеть представляет собой первую коммутационную сеть, а

аналоговый выходной сигнал представляет собой первый аналоговый выходной сигнал (106a),

при этом указанная система дополнительно содержит:

вторую схему (140b) микширующего устройства, соединенную со схемой декодирующего устройства и выполненную с возможностью объединения каждого из декодированных битов параллельных цифровых данных с тактовым сигналом преобразования для получения битов цифровых данных со сдвигом частоты, которые имеют временное расхождение по отношению друг к другу,

вторую схему (105b) синхронизирующего устройства, соединенную со второй схемой микширующего устройства, располагающую тактовым сигналом для синхронизирующего устройства и выполненную с возможностью выравнивания по времени битов цифровых данных со сдвигом частоты в ответ на тактовый сигнал для синхронизирующего устройства,

вторую коммутационную сеть (102b), соединенную со второй схемой синхронизирующего устройства и выполненную с возможностью генерирования второго аналогового выходного сигнала (106b) в ответ на выровненные по времени биты цифровых данных со сдвигом частоты, причем второй аналоговый выходной сигнал представляет собой дополнительный сигнал по отношению к первому аналоговому выходному сигналу,

причем схема декодирующего устройства, первая и вторая схемы микширующего устройства, первая и вторая схемы синхронизирующего устройства, а также первая и вторая коммутационные сети содержат несимметричные схемы (636, 836, 1036) на комплементарных структурах металл-оксид-полупроводник.

8. Система по п. 1, в которой тактовый сигнал для синхронизирующего устройства представляет собой одиночный конечный тактовый сигнал, а

указанная система дополнительно содержит схему (180) детектора переднего и заднего фронтов, выполненную с возможностью преобразования дифференциального тактового сигнала (175), имеющего первую частоту (NFs), в одиночный конечный тактовый сигнал, имеющий вторую частоту (2NFs), которая вдвое превышает первую частоту.

9. Система по п. 1, в которой коммутационная сеть содержит множество резисторов (1023, 1025), расположенных с образованием схемы параллельного соединения, причем соответствующие резисторы из указанных резисторов соединены с соответствующими одними из выровненных по времени битов цифровых данных со сдвигом частоты,

при этом коммутационная сеть дополнительно содержит суммирующий узел (1008), связанный с аналоговым выходным сигналом, а

каждый из указанных резисторов выборочно соединен с суммирующим узлом в ответ на соответствующий выровненный по времени бит данных со сдвигом частоты.

10. Система по п. 9, в которой коммутационная сеть дополнительно содержит по меньшей мере один резистор (R39) смещения, соединенный с суммирующим узлом на первом конце и с источником напряжения (VDDA) на втором конце и задающий напряжение (1010) смещения аналогового выходного сигнала,

причем указанный по меньшей мере один резистор смещения и указанные резисторы объединены для установления фиксированного выходного импеданса аналогового выходного сигнала.

11. Способ цифроаналогового преобразования, включающий:

прием (325), посредством схемы (130) декодирующего устройства, множества битов (111c) входных данных декодирующего устройства,

получение (325, 330), посредством схемы декодирующего устройства, множества декодированных битов (111d) параллельных цифровых данных, причем схема декодирующего устройства работает при заданной частоте (Fs) дискретизации,

объединение (335), посредством схемы (140) микширующего устройства, соединенной со схемой декодирующего устройства, каждого из указанных декодированных битов параллельных цифровых данных с тактовым сигналом (145) преобразования для получения битов (111e) цифровых данных со сдвигом частоты, которые имеют временное расхождение по отношению друг к другу,

выравнивание (340), посредством схемы (105) синхронизирующего устройства, соединенной со схемой микширующего устройства, указанных битов цифровых данных со сдвигом частоты в ответ на тактовый сигнал (155) для синхронизирующего устройства и

генерирование (345), посредством коммутационной сети (102), соединенной со схемой синхронизирующего устройства, аналогового выходного сигнала (106) в ответ на выровненные по времени биты (112a) цифровых данных со сдвигом частоты.

12. Способ по п. 11, согласно которому биты цифровых данных со сдвигом частоты имеют временное расхождение по отношению друг к другу за счет временного расхождения, связанного с переходами логического состояния каждого из указанных декодированных битов параллельных цифровых данных и переходами логического состояния тактового сигнала преобразования.

13. Способ по п. 11, дополнительно включающий:

преобразование (335), посредством схемы микширующего устройства, указанных декодированных битов параллельных цифровых данных при первой частоте (Fs) в биты цифровых данных со сдвигом частоты при второй частоте (NFs),

приведение в действие (335) схемы микширующего устройства при частоте (NFs), превышающей в N раз заданную частоту дискретизации, и

приведение в действие (340) схемы синхронизирующего устройства при частоте (2NFs), вдвое превышающей частоту микширующего устройства.

14. Способ по п. 11, согласно которому аналоговый выходной сигнал имеет полосу (1130) пропускания, соответствующую полосе пропускания битов входных данных декодирующего устройства,

причем основная спектральная энергия (1106) аналогового выходного сигнала сосредоточена вокруг частоты (NFs) тактового сигнала преобразования.

15. Способ по п. 11, дополнительно включающий:

прием (320), посредством схемы (120) мультиплексора, соединенной со схемой декодирующего устройства, множества слов (111b) параллельных цифровых данных в ответ на тактовый сигнал (125) для мультиплексора и

получение (320), посредством схемы мультиплексора, соответствующего одного из указанных слов (237) параллельных цифровых данных, содержащих биты входных данных декодирующего устройства при заданной частоте дискретизации,

причем тактовый сигнал мультиплексора имеет частоту дискретизации (FS/M), превышающую в 1/M раз заданную частоту дискретизации.

16. Способ по п. 15, дополнительно включающий:

прием (310), посредством схемы (110) мезохронного интерфейса, соединенной со схемой мультиплексора, множества слов (111a) входных данных мезохронного интерфейса, синхронизированных посредством внешнего тактового сигнала (115), и

получение (315), посредством схемы мезохронного интерфейса, указанного множества слов параллельных цифровых данных, синхронизированных посредством тактового сигнала для мультиплексора,

причем внешний тактовый сигнал является асинхронным по отношению к тактовому сигналу для мультиплексора.

17. Способ по п. 11, согласно которому

схема микширующего устройства представляет собой первую схему микширующего устройства,

схема синхронизирующего устройства представляет собой первую схему синхронизирующего устройства,

коммутационная сеть представляет собой первую коммутационную сеть, а

аналоговый выходной сигнал представляет собой первый аналоговый выходной сигнал (106a),

при этом указанный способ включает:

объединение, посредством второй схемы (140b) микширующего устройства, соединенной со схемой декодирующего устройства, каждого из указанных декодированных битов параллельных цифровых данных с тактовым сигналом преобразования для получения битов цифровых данных со сдвигом частоты, которые имеют временное расхождение по отношению друг к другу,

выравнивание, посредством второй схемы (105b) синхронизирующего устройства, соединенной со второй схемой микширующего устройства, битов цифровых данных со сдвигом частоты в ответ на тактовый сигнал для синхронизирующего устройства,

генерирование, посредством второй коммутационной сети (102b), соединенной со второй схемой синхронизирующего устройства, второго аналогового выходного сигнала (106b) в ответ на выровненные по времени биты цифровых данных со сдвигом частоты, причем второй аналоговый выходной сигнал представляет собой дополнительный сигнал по отношению к первому аналоговому выходному сигналу,

причем схема декодирующего устройства, первая и вторая схемы микширующего устройства, первая и вторая схемы синхронизирующего устройства, а также первая и вторая коммутационные сети содержат несимметричные схемы (636, 836, 1036) на комплементарных структурах металл-оксид-полупроводник.

18. Способ по п. 11, согласно которому тактовый сигнал для синхронизирующего устройства представляет собой одиночный конечный тактовый сигнал, а

указанный способ включает преобразование (305), посредством схемы (180) детектора переднего и заднего фронтов, дифференциального тактового сигнала (175), имеющего первую частоту (NFs), в одиночный конечный тактовый сигнал, имеющий вторую частоту (2NFs), которая вдвое превышает первую частоту.

19. Способ по п. 11, согласно которому коммутационная сеть содержит множество резисторов (1023, 1025), расположенных с образованием схемы параллельного соединения, причем соответствующие резисторы из указанных резисторов соединены с соответствующими битами из указанных выровненных по времени битов цифровых данных со сдвигом частоты,

причем коммутационная сеть дополнительно содержит суммирующий узел (1008), связанный с аналоговым выходным сигналом, а

указанный способ включает выборочное соединение каждого из указанных резисторов с суммирующим узлом в ответ на соответствующий выровненный по времени бит данных со сдвигом частоты.

20. Способ по п. 19, согласно которому коммутационная сеть дополнительно содержит по меньшей мере один резистор (R39) смещения, соединенный с суммирующим узлом на первом конце и источником напряжения (VDDA) на втором конце и задающий напряжение (1010) смещения аналогового выходного сигнала,

причем указанный по меньшей мере один резистор смещения и указанные резисторы объединены для установления фиксированного выходного импеданса аналогового выходного сигнала.

| US 6690313 B1, 10.02.2004 | |||

| US 7528754 B1, 05.05.2009 | |||

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

| Способ защиты переносных электрических установок от опасностей, связанных с заземлением одной из фаз | 1924 |

|

SU2014A1 |

| ЦИФРО-АНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2013 |

|

RU2523950C1 |

| Кулачковая или зубчатая муфтовая пара системы перемены передач автомобиля, трактора и т.п. | 1950 |

|

SU102443A1 |

Авторы

Даты

2021-04-22—Публикация

2017-08-28—Подача