Изобретение относится к области аналого-цифровых преобразований, а именно к системам считывания информации аналого-информационного преобразователя (АИП) с динамическим профилем интегрирования (ДПИ) и представляет собой систему считывания данных входного сигнала для аналого-информационного преобразователя (АИП). Данные устройства могут использоваться в системах связи, датчиках, радарах, магнитно-резонансной томографии в случаях, когда целевой сигнал находится в широкой полосе частот, но полезная информация сконцентрирована в узкой полосе.

Аналого-информационные преобразователи или АИП (analog-to-information converters) – устройства, предназначенные для извлечения полезной информации из широкополосного входного сигнала. В основе работы АИП лежит теория сжатой дискретизации. Основные преимущества АИП заключаются в использовании малого, по сравнению с аналого-цифровыми преобразователями (АЦП), количества отсчетов для извлечения полезной информации из сигнала, уменьшение затрат на энергию за счет уменьшения частоты дискретизации внутренних АЦП.

На данный момент существует ряд архитектур считывания информации для АИП. Архитектура неравномерной дискретизации (non-uniform sampling или NUS) напрямую реализует теорию сжатой дискретизации: собирает отсчеты входного сигнала в случайный момент времени. Такие архитектуры как случайный демодулятор (random demodulator или RD), пред-интегратор случайной модуляции (random modulator pre-integrator или RMPI), сжимающий мультиплексор (compressive multiplexer или CMUX) используют случайные последовательности для смешивания сигнала. В результате смешения полезная информация распространяется по всему спектру, попадая и в полосу работы АЦП.

Известна архитектура неравномерной дискретизации или НРД, описанная в патенте CN101558567A: Method and apparatus for detecting the presence of a signal in a frequency band using non-uniform sampling, которая дискретизирует входной сигнал через неравномерные интервалы времени. При наличии оцифрованного значения и момента дискретизации, восстанавливают информацию о сигнале.

Недостатком данной архитектуры является ограниченная область применения, поскольку она рассчитана только для частотно-разреженного сигнала, устройство выборки-хранения должно быть рассчитано на сигнал с частотами, больше частоты дискретизации АЦП, меньший уровень разреженности (условие для входного сигнала).

Наиболее близким к заявленному изобретению является случайный демодулятор или СД (random demodulator или RD), описанный в статье S. Kirolos, J. Laska, M. Wakin, M. Duarte, D. Baron, T. Ragheb, Y. Massoud, and R. Baraniuk. Analog-to-Information Conversion via Random Demodulation. in Proc. IEEE Dallas/CAS Workshop on Design, Applications, Integration and Software, Oct. 2006, pp. 71–74. doi:10.1109/dcas.2006.321036, который смешивает входной сигнал со случайной последовательностью +/-1, далее результат смешивания поступает на интегратор и после равномерно дискретизируется и оцифровывается обычным АЦП. Данный демодулятор выбран в качестве прототипа заявленного изобретения.

Недостатками прототипа являются, во-первых, недостаточная производительность, вследствие низкого коэффициента передискретизации, и проявления наилучших характеристик только в режиме работы, при котором интегрирование происходит в течение времени оцифровки.

Техническим результатом изобретения является создание системы считывания аналого-информационного преобразователя (АИП) с динамическим профилем интегрирования (ДПИ) со сниженным энергопотреблением, за счет уменьшенного времени сбора информации о сигнале; с увеличенной производительностью, за счет использования ДПИ, которое увеличивает несогласованность между матрицей считывания и матрицей разреженного представления, что позволяет увеличить коэффициент передискретизации; с расширенной областью применения не только для частотно-разреженного сигнала, в режиме, когда минимальный интервал интегрирования не меньше времени оцифровки используемого АЦП; с увеличенной скоростью функционирования, за счет использования блока управления АЦП интегратором, что позволяет увеличить диапазон возможных комбинаций для интегрирования, что позволяет сократить время сбора данных; с улучшенной функциональностью, за счет использования смешивающего устройства на базе УВХ на переключаемых конденсаторах, которое позволяет увеличить диапазон возможных комбинаций для интегрирования за счет умножения сигнала на дискретные значения из диапазона (0;1), что увеличивает несогласованность и позволяет обрабатывать менее разреженный целевой сигнал; с улучшенной производительностью, за счет использования смешивающего устройства и фильтра низких частот, что позволяет обрабатывать целевой сигнал из широкой полосы частот.

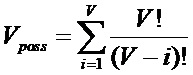

Поставленный технический результат достигнут путем создания системы считывания аналого-информационного преобразователя (АИП) с динамическим профилем интегрирования (ДПИ), содержащей генератор 14 случайной последовательности вход которого является первым входом системы, а выход которого соединен с первым входом смешивающего устройства 12, второй вход которого является вторым входом системы, а выход которого соединен с первым входом интегратора 17, выход которого соединен с первым входом аналого-цифрового преобразователя (АЦП) 112, второй вход которого соединен с первым выходом блока 19 управления АЦП и интегратором, вход которого является третьим входом системы, а второй выход которого соединен с вторым входом интегратора 17, причем

- генератор 14 случайной последовательности выполнен с возможностью формирования случайной последовательности 13 значений +/-1, значений из диапазона (0;1) и передачи ее на первый вход

- смешивающего устройства 12, которое выполнено с возможностью смешивания внешнего входного сигнала 11 со случайной последовательностью 13, при этом формирования смешанного сигнала 16 и передачи его на первый вход

- интегратора 17, выполненного с возможностью интегрирования смешанного сигнала 16 с использованием сигнала 111 управления интегратором, при этом формирования интегрированного смешанного сигнала 18 и передачи его на первый вход

- АЦП 112, который выполнен с возможностью преобразования интегрированного смешанного сигнала 18 в цифровой код, с использованием сигнала управления АЦП, оцифровки и с возможностью передачи цифрового кода в систему восстановления данных (СВД);

- блок 19 управления интегратором и АЦП, выполнен с возможностью формирования сигнала управления АЦП и сигнал управления интегратором с использованием внешнего опорного тактового сигнала fr 15.

В предпочтительном варианте осуществления системы интегратор 17, выполнен с возможностью интегрирования смешанного сигнала 16 с использованием сигнала 111 управления интегратором, при этом интервал времени интегрирования сигнала принимает случайное целое значение в заданном диапазоне, для определения которого используют псевдослучайные бинарные последовательности (ПБП), а счетчик выполнен с возможностью отсчета полученного случайного значения, используя опорный тактовый сигнал fr 15, причем во время работы счетчика сигнал со смешивающего устройства 12 интегрируется, при этом по окончании отсчета устройство выборки/хранения АЦП выполнено с возможностью дискретизации интегрированного сигнала, после чего происходит оцифровка полученного значения

В предпочтительном варианте осуществления системы время работы АЦП 112 значительно больше периода опорного тактового сигнала fr 15, а во время оцифровки интегратор 17 и смешивающее устройство 12 отключены.

Для лучшего понимания заявленного изобретения далее приводится его подробное описание с соответствующими графическими материалами.

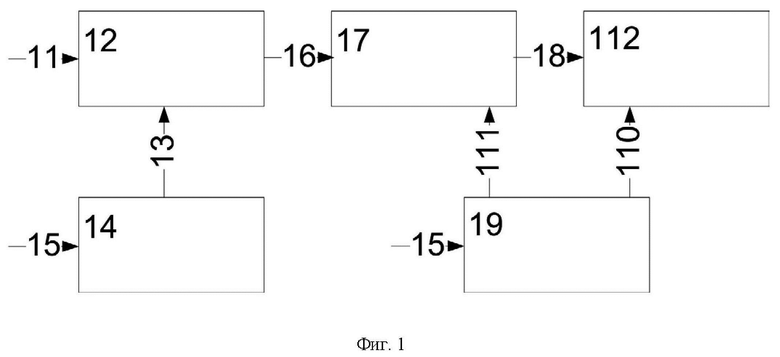

Фиг. 1. Общая структурная схема системы считывания информации аналого-информационного преобразователя (АИП) с динамическим профилем интегрирования (ДПИ), выполненная согласно изобретению.

Элементы

11 – входной сигнал;

12 – смешивающее устройство;

13 – случайная последовательность +/-1 (значений из диапазона (0;1));

14 – генератор случайной последовательности;

15 – опорный тактовый сигнал fr;

16 – результат смешения входного сигнала со случайной последовательностью;

17 – интегратор;

18 – интегрированный смешанный сигнал;

19 – блок управления АЦП и интегратором (генератор случайной последовательности + счетчик);

110 – сигнал управления АЦП;

111 – сигнал управления интегратором;

112 – АЦП.

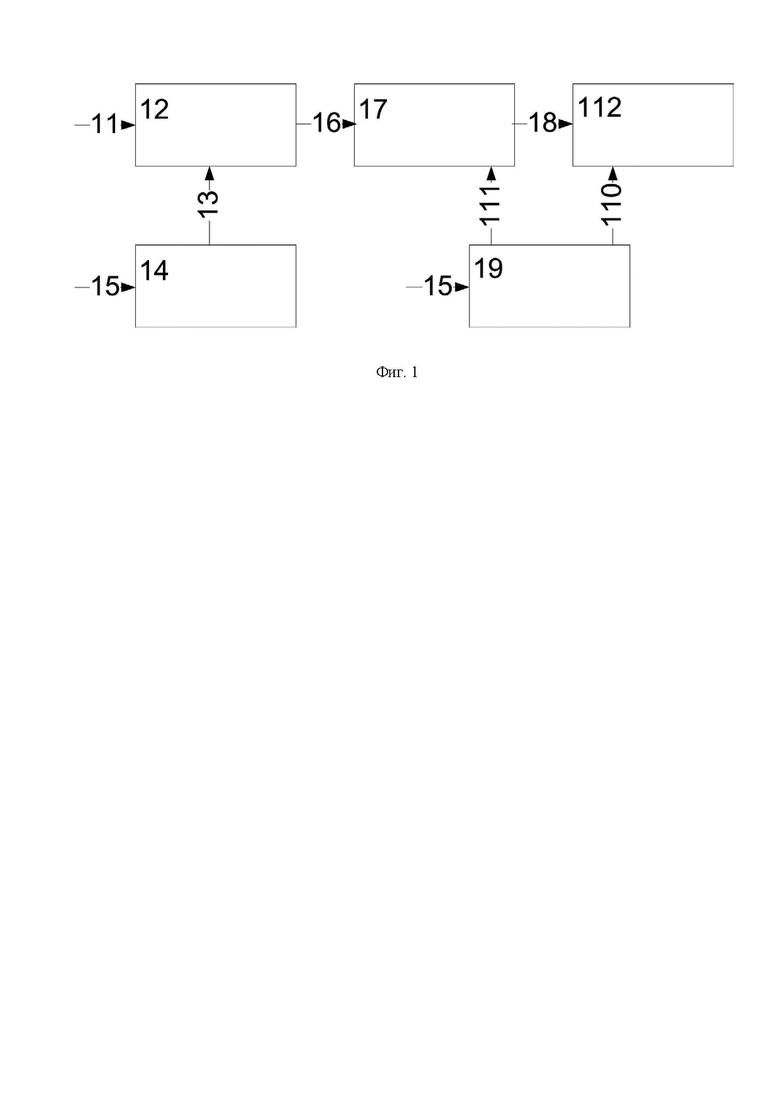

Фиг. 2. Общая структурная схема устройства выборки/хранения (УВХ) в АЦП последовательного приближения, выполненная согласно изобретению.

Элементы

11 – входной сигнал;

21 - емкости УВХ, номиналом С1, С2, С3, С4;

22 – остальная часть емкостного ЦАП;

23 - входные ключи;

24 – ключ дискретизации;

25 – опорный потенциал.

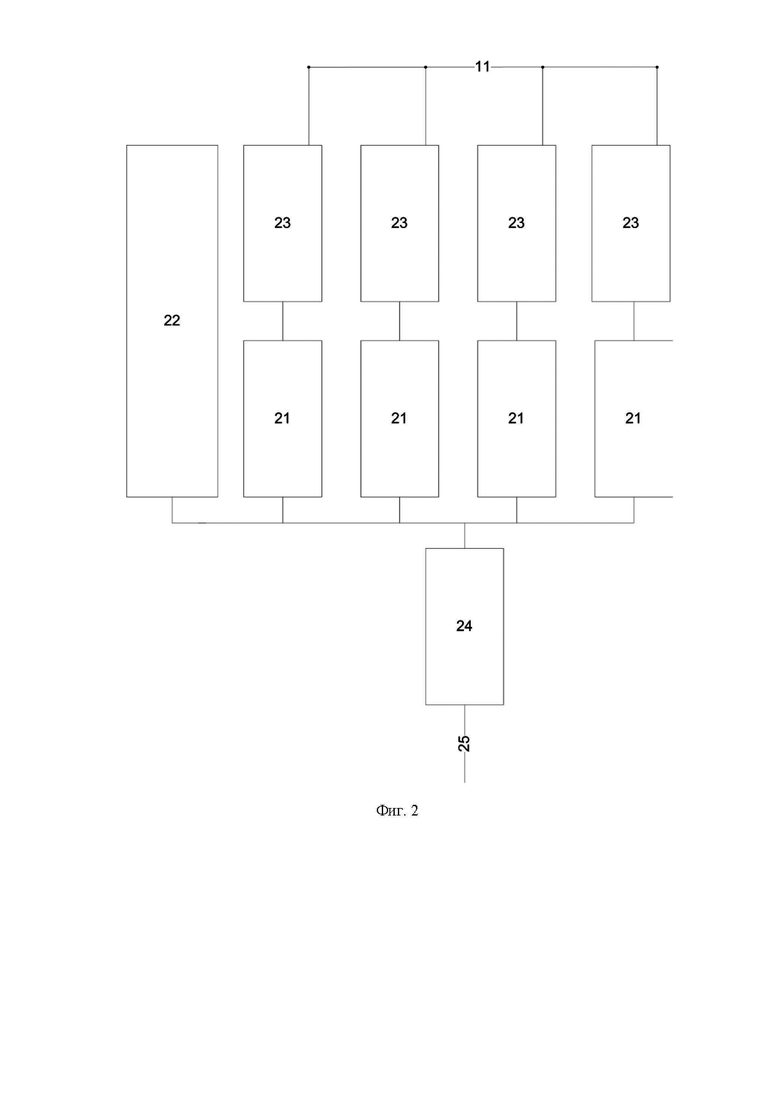

Фиг. 3. Общая структурная схема реализации аналого-информационного преобразователя (АИП) с динамическим профилем интегрирования (ДПИ), выполненная согласно изобретению.

Элементы

11 – входной сигнал;

15 – опорный тактовый сигнал fr;

25 – опорный потенциал;

31 – устройство выборки/хранения;

32 – емкостной ЦАП АЦП;

33 – сигналы управления входными ключами и ключом дискретизации;

34 – сигнал управления АЦП;

35 – квантователь АЦП;

36 – результат преобразования АЦП.

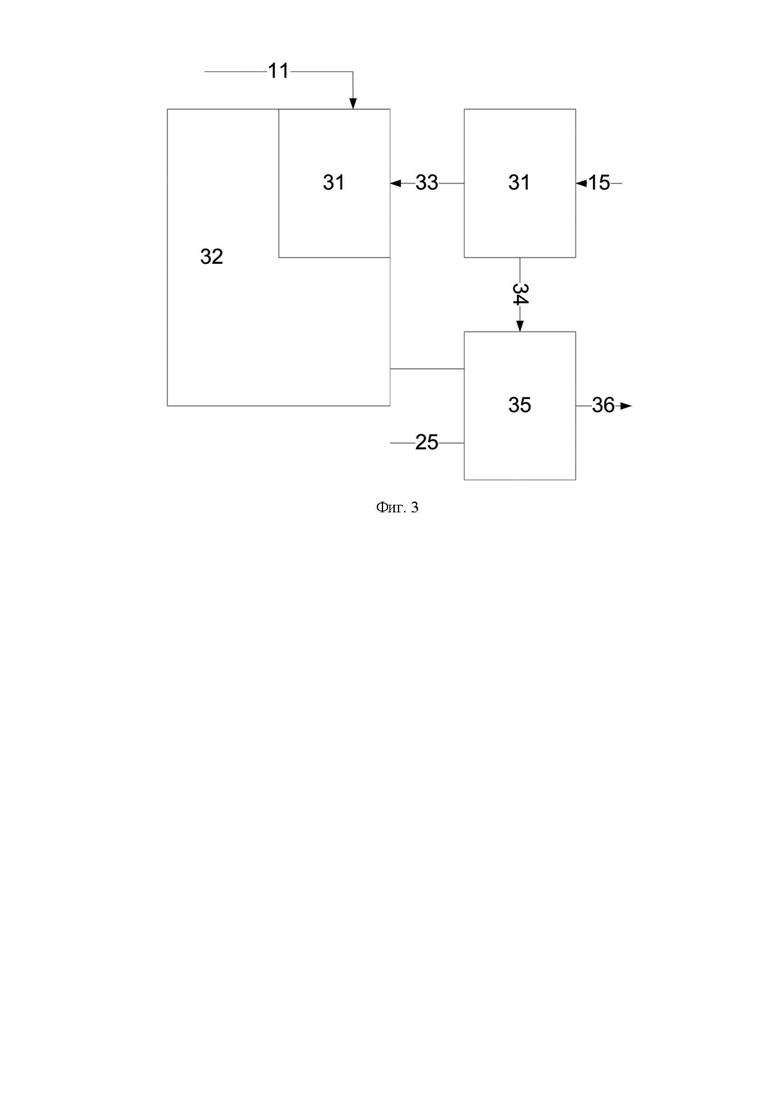

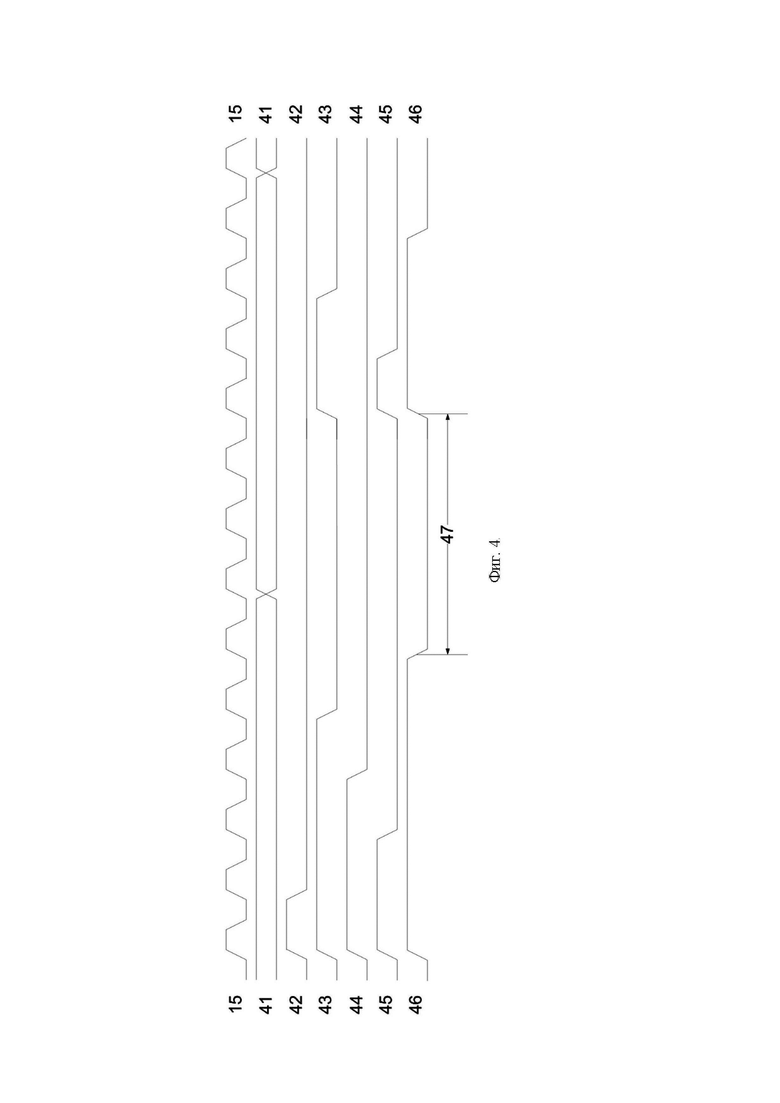

Фиг. 4. Временная диаграмма работы аналого-информационного преобразователя (АИП) с динамическим профилем интегрирования (ДПИ), выполненная согласно изобретению.

Элементы

15 – опорный тактовый сигнал fr;

41 – значения случайной последовательности (Х-изменение значнения);

42 – сигнал управления входным ключом емкости С1(логическая 1 – ключ замкнут);

43 – сигнал управления входным ключом емкости С2(логическая 1 – ключ замкнут);

44 – сигнал управления входным ключом емкости С3(логическая 1 – ключ замкнут);

45 – сигнал управления входным ключом емкости С4(логическая 1 – ключ замкнут);

46 – сигнал управления ключом дискретизации (логическая 1 – ключ замкнут);

47 – время оцифровки, равен N=4 тактам опорной частоты.

Рассмотрим принцип функционирования заявленной системы считывания аналого-информационного преобразователя (АИП) с динамическим профилем интегрирования (ДПИ) (Фиг. 1).

Система предназначена для разреженного сигнала, в частности частотно-разреженного. Сигнал называется разреженным, если существует такое представление входного сигнала 11, в котором все члены представления, кроме некоторых, равны нулю либо пренебрежимо малы. Матрица перехода в разреженное представление входного сигнала 11 называется базис разреженного представления.

На вход системы считывания, в смешивающее устройство 12, поступает входной разреженный сигнал 11. Входной сигнал 11 смешиваются со случайной последовательностью 13 +/-1 или со случайной последовательностью 13 чисел из диапазона (0;1). В качестве случайных последовательностей 13 используют псевдослучайные бинарные последовательности (ПБП), например, коды Голда, коды Кассами или м-последовательности. Значения последовательности 13 меняются с частотой внешнего опорного тактового сигнала fr 15. В результате смешивания информация распространяется по всему спектру.

Далее смешанный сигнал 16 поступает на интегратор 17. Интервал времени интегрирования сигнала принимает случайное целое значение в заданном диапазоне. Для его определения так же может быть использована ПБП. Счетчик отсчитывает полученное случайное значение, используя опорный сигнал fr 15. Во время работы счетчика сигнал со смешивающего устройства 12 интегрируется. По окончании отсчета происходит дискретизация интегрированного сигнала устройством выборки/хранения АЦП 112, после чего происходит оцифровка полученного значения. Время работы АЦП 112 может быть значительно больше периода опорного сигнала 15. Во время оцифровки интегратор 17 и смешивающее устройство 12 могут быть отключены. После оцифровки полученное значение передается в систему восстановления данных (СВД).

В СВД, используя информацию о последовательности смешивания и интервалах интегрирования, восстанавливают полезную информацию о входном сигнале.

Рассмотрим более подробно функционирование заявленной системы считывания аналого-информационного преобразователя (АИП) с динамическим профилем интегрирования (ДПИ) (Фиг. 1-4).

На Фиг. 1 представлена общая структурная схема архитектуры системы считывания аналого-информационного преобразователя (АИП) с динамическим профилем интегрирования (ДПИ). Основными функциональными блоками данной архитектуры являются: смешивающее устройство 12, генератор случайной последовательности 14, интегратор 17, АЦП 112, блок 19 управления интегратором и АЦП.

Аналого-информационный преобразователь (АИП) с динамическим профилем интегрирования (ДПИ) реализован на базе емкостного АЦП 32 последовательного приближения, в котором устройство выборки/хранения (УВХ) является частью емкостного цифро-аналогового преобразователя (ЦАП) 32. На Фиг. 2 представлено УВХ. Данное УВХ выполняет функцию смешивающего устройства и интегратора. Так как УВХ это часть ЦАП, то каждая емкость будет сохранять заряд, составляющий какую-то часть от максимального заряда, который может хранить используемая емкостная матрица. Доля или вес каждой емкости УВХ находится при калибровке разрядов матрицы ЦАП. Последовательное размыкание входных ключей сохраняет на емкости заряд, пропорциональный входному сигналу 11 и емкости в момент размыкания. Другими словами, напряжение входного сигнала 11 умножается на число, равное доле матрицы данной емкости. Для соблюдения временных интервалов между моментами дискретизации используется опорная частота fr. При размыкании ключа дискретизации (КД) 24 сохраненные заряды на УВХ суммируются, что эквивалентно интегрированию соответствующего прямоугольного сигнала за интервал времени. Далее, результат суммирования обрабатывается АЦП 112 стандартным образом.

Если входной сигнал дифференциальный, то можно дополнительно модифицировать исходную архитектуру для повышения несогласованности системы считывания за счет умножения входного сигнала на +/-1. Умножение на -1 для гармонического сигнала эквивалентно сдвигу фазы входного сигнала на 180 градусов. Так как используем дифференциальный сигнал, переключаясь между фазами сигнала, мы реализуем данный сдвиг. В остальном маршрут работы устройства не изменится.

Кроме умножения на +/-1, можем увеличить несогласованность за счет увеличения набора возможных коэффициентов умножения. Это достигается с помощью размыкания одного или более ключей. Количество вариантов возрастает многократно. Так же это позволяет сократить время сбора данных, что позволяет еще больше сэкономить на потреблении и позволяет обрабатывать менее разреженный сигнал. Кроме этого данное решение позволяет уменьшить время сбора информации.

При изменении порядка размыкания и количества входных ключей 23, размыкаемых в каждом такте, изменяется порядок чисел, на которые умножается входной сигнал 11 и интервал интегрирования. Изменяя порядок между тактами оцифровки АЦП случайным образом, входной сигнал 11 смешивается со случайной последовательностью. Для определения порядка и количества размыкаемых ключей используется случайная последовательность. В качестве случайной последовательности используется псевдослучайная двоичная последовательность максимального периода или м–последовательность, генерируемая регистром сдвига с линейной обратной связью. Разрядность полинома зависит от количества снимаемых отсчетов и количества вариантов переключения ключей. Длина последовательности должна быть больше количества снимаемых отчетов, чтобы не возникло повторяющихся паттернов. Так же разрядность полинома должна быть на 3-4 разряда больше двоичного представления числа, равного количеству возможных наборов переключаемых емкостей, чтобы принимаемые значения были равновероятны (использоваться будут только младшие разряды случайного числа). Для случая, когда в состав УВХ входит V емкостей, и при условии, что размыкаться каждый раз будет 1 входной ключ, количество возможных наборов равно

Для интерпретации числа случайной последовательности используется блок управления интегратора и АЦП, который в этом случае так же реализует смешивание входного сигнала со случайной последовательностью. Основные составляющие этого блока: память, которая, хранит порядок и количество размыкаемых ключей и счетчик, который управляет временем интегрирования. Так как УВХ является частью емкостного ЦАП, то слежение и интегрирование во время работы АЦП невозможно. Для перехода из режима оцифровки в слежение пропускается N тактов опорного тактового сигнала. За это время АЦП оцифровывает сохраненное значение. Параллельно во время оцифровки рассчитывается следующее случайное значение. Структурная схема реализации аналого-информационного преобразователя (АИП) представлена на Фиг. 3.

Порядок работы аналого-информационного преобразователя (АИП) с динамическим профилем интегрирования (ДПИ) следующий.

Шаг 1. УВХ находится в режиме слежения. Замкнутыми будут только входные ключи 23, определенные значением случайной последовательности. Пропускается такт опорного тактового сигнала для зарядки емкостей УВХ.

Шаг 2. По каждому следующему такту опорного тактового сигнала размыкается один из замкнутых ключей в порядке, определенным значением случайной последовательности. Параллельно счетчик начинает отсчет количества размыкаемых ключей до значения, определенного значением случайной последовательности.

Шаг 3. После размыкания всех входных ключей 23, по следующему такту опорного тактового сигнала размыкается ключ дискретизации 24.

Шаг 4. Начинается отсчет N тактов опорного тактового сигнала, отведенное на оцифровку. Параллельно рассчитывается и интерпретируется следующее случайное значение.

Шаг 5. После отсчета N тактов, УВХ переходит в режим слежения. Для слежения используют входные ключи, определяемые значением случайной последовательности. АЦП 112 выдает результат оцифровки.

Шаг 6. В дальнейшей работе АИП ДПИ повторяют шаги с 1 по 6.

Временная диаграмма работы АИП ДПИ представлена на Фиг. 4.

Для случая, когда входной сигнал может находиться в широкой полосе (сотни МГц) использование смешивающего устройства и интегратора на базе переключаемых конденсаторов невозможно. Для этого случая удобно использовать смесители и интеграторы на базе операционных усилителей. В смесителе смешивать входной сигнал со случайной последовательностью +/-1 с последующим интегрировании смешанного сигнала в интеграторе. Далее интегрированный сигнал дискретизируется АЦП через случайные интервалы времени, определяемые последовательностью. На время работы АЦП смеситель и интегратор можно отключить для уменьшения затрат на энергию.

В лучшем варианте выполнения заявленного аналого-информационного преобразователя (АИП) с динамическим профилем интегрирования (ДПИ):

a) Используют дифференциальный входной сигнал на УВХ. Это позволяет дополнительно умножать обрабатываемый сигнал на +/-1 для увеличения количества вариантов возможных наборов.

b) Размыкают одновременно один или больше ключей во время слежения. Это позволяет многократно увеличить количество возможных вариантов переключения емкостей. Так же это позволяет сократить время сбора данных, что позволяет еще больше сэкономить на потреблении и позволяет обрабатывать менее разреженный сигнал.

c) Используют смеситель и фильтр низких частот для высокочастотных входных сигналов.

Заявленная система считывания аналого-информационного преобразователя (АИП) с динамическим профилем интегрирования (ДПИ) обладает следующими преимуществами.

Архитектура системы считывания аналого-информационного преобразователя (АИП) с динамическим профилем интегрирования (ДПИ) позволяет уменьшить время сбора информации о сигнале, в отличие от архитектуры RD прототипа, что позволяет сократить энергопотребление. Использование ДПИ увеличивает несогласованность между матрицей считывания и матрицей разреженного представления, что позволяет увеличить коэффициент передискретизации. В случае, когда минимальный интервал интегрирования не меньше времени оцифровки используемого АЦП, данную архитектуру можно использовать не только для частотно-разреженного сигнала.

Использование блока управления интегратором и АЦП позволяет увеличить диапазон возможных комбинаций для интегрирования, что положительно сказывается на этапе восстановления данных и позволяет сократить время сбора данных.

Использование смешивающего устройства 12 на базе УВХ на переключаемых конденсаторах позволяет увеличить диапазон возможных комбинаций для интегрирования за счет умножения сигнала на дискретные значения из диапазона (0;1), что увеличивает несогласованность и позволяет обрабатывать менее разреженный целевой сигнал.

Использование стандартных решений в виде смешивающего устройства 12 и фильтра низких частот позволяет обрабатывать целевой сигнал из широкой полосы частот.

Хотя описанный выше вариант выполнения изобретения был изложен с целью иллюстрации настоящего изобретения, специалистам ясно, что возможны разные модификации, добавления и замены, не выходящие из объема и смысла настоящего изобретения, раскрытого в прилагаемой формуле изобретения.

Изобретение относится к области аналого-цифровых преобразований. Техническим результатом изобретения является создание системы считывания аналого-информационного преобразователя (АИП) со сниженным энергопотреблением, за счет уменьшенного времени сбора информации о сигнале; с увеличенной производительностью, за счет использования ДПИ; с расширенной областью применения не только для частотно-разреженного сигнала, в режиме, когда минимальный интервал интегрирования не меньше времени оцифровки используемого АЦП; с увеличенной скоростью функционирования, за счет использования блока управления АЦП интегратором; с улучшенной функциональностью, за счет использования смешивающего устройства на базе УВХ на переключаемых конденсаторах; с улучшенной производительностью, за счет использования смешивающего устройства и фильтра низких частот, что позволяет обрабатывать целевой сигнал из широкой полосы частот. 2 з.п. ф-лы, 4 ил.

1. Система считывания аналого-информационного преобразователя (АИП) с динамическим профилем интегрирования (ДПИ), содержащая генератор 14 случайной последовательности, вход которого является первым входом системы, а выход которого соединен с первым входом смешивающего устройства 12, второй вход которого является вторым входом системы, а выход которого соединен с первым входом интегратора 17, выход которого соединен с первым входом аналого-цифрового преобразователя (АЦП) 112, второй вход которого соединен с первым выходом блока 19 управления АЦП и интегратором, вход которого является третьим входом системы, а второй выход которого соединен с вторым входом интегратора 17, причем

- генератор 14 случайной последовательности выполнен с возможностью формирования случайной последовательности 13 значений +/-1, значений из диапазона (0;1) и передачи ее на первый вход

- смешивающего устройства 12, которое выполнено с возможностью смешивания внешнего входного сигнала 11 со случайной последовательностью 13, при этом формирования смешанного сигнала 16 и передачи его на первый вход

- интегратора 17, выполненного с возможностью интегрирования смешанного сигнала 16 с использованием сигнала 111 управления интегратором, при этом формирования интегрированного смешанного сигнала 18 и передачи его на первый вход

- АЦП 112, который выполнен с возможностью преобразования интегрированного смешанного сигнала 18 в цифровой код, с использованием сигнала управления АЦП, оцифровки и с возможностью передачи цифрового кода в систему восстановления данных (СВД);

- блок 19 управления интегратором и АЦП выполнен с возможностью формирования сигнала управления АЦП и сигнала управления интегратором с использованием внешнего опорного тактового сигнала fr 15.

2. Система по п. 1, отличающаяся тем, что интегратор 17 выполнен с возможностью интегрирования смешанного сигнала 16 с использованием сигнала 111 управления интегратором, при этом интервал времени интегрирования сигнала принимает случайное целое значение в заданном диапазоне, для определения которого используют псевдослучайные бинарные последовательности (ПБП), а счетчик выполнен с возможностью отсчета полученного случайного значения, используя опорный тактовый сигнал fr 15, причем во время работы счетчика сигнал со смешивающего устройства 12 интегрируется, при этом по окончании отсчета устройство выборки/хранения АЦП выполнено с возможностью дискретизации интегрированного сигнала, после чего происходит оцифровка полученного значения.

3. Система по п. 1, отличающаяся тем, что время работы АЦП 112 значительно больше периода опорного тактового сигнала fr 15, а во время оцифровки интегратор 17 и смешивающее устройство 12 отключены.

| S | |||

| KIROLOS et al, Analog-to-Information Conversion via Random Demodulation, in Proc | |||

| IEEE Dallas/CAS Workshop on Design, Applications, Integration and Software, Oct | |||

| Пломбировальные щипцы | 1923 |

|

SU2006A1 |

| Контрольный стрелочный замок | 1920 |

|

SU71A1 |

| CN 101558567 A, 14.10.2009 | |||

| US 9287979 B2, 15.03.2016 | |||

| КОГЕРЕНТНЫЙ ДЕМОДУЛЯТОР AM-СИГНАЛА С ИСПОЛЬЗОВАНИЕМ ВЗВЕШЕННОЙ СУММЫ НИЖНЕЙ БОКОВОЙ ПОЛОСЫ/ВЕРХНЕЙ БОКОВОЙ ПОЛОСЫ ДЛЯ ПОДАВЛЕНИЯ ПОМЕХ | 2004 |

|

RU2342772C2 |

Авторы

Даты

2021-08-11—Публикация

2020-12-02—Подача