(54) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ И КОНТРОЛЯ НЕЛИНЕЙНОСТИ АМПЛИТУДНОЙ ХАРАКТЕРИСТИКИ КВАЗИЛИНЕЙНЫХ Изобретение относится к технике измерений и может быть использовано в автоматизированных системах измерения и контроля нелинейности групповых и линейных трактов и их составных частей в сис темах передачи с частотным разделением каналов. Известно устройство, реализующее кор реляционный способ измерения нелинейных искажений четырехполюсников с нелинейностью вида показательной функиии при наличии аддитивного шума. Устройство содержит генератор шумового измерительного сигнала и двумерный статистический анализатор, измеряющий двумерную функцию распределения вероятностей входного и выходного сигналов четырехполюсника, по которой на элект ронно-вычислительной машине находится оценка нелинейных искажений 11. Недостатком этого устройства является сложность оборудования, требующего применения вычислительной 4aшины.

СИСТЕМ Наиболее близким к предлагаемому является устройство для измерения и конт роля нелинейности квазилинейных систем, содержащее генератор измерительного сигнала с заданным распределением мгновенных значений, два элемента сравнения, квадратичный детектор, усилитель с регулируемым коэффициентом передачи, интег- piaTOp, регулируемый источник компенсирующего напряжения, индикатор С2 . Недостатком этого устройства являеРся значительная погрешность измерения нелинейности по искажению одномерного распределения мгновенных значений выходного сигнала квазилинейной системы. Цель изобретения - повышение точности измерения и контроля нелинейности квазилинейных систем. Поставленная цель достигается тем, что в устройство для измерения и контроля нелинейности амплитудной характеристики квазилинейных систем, содержащее блок индикации, источник опорного напряжения, генератор измерительного сигнала. подключенный к первой клемме устройства элемент сравнения ,. к первому входу которого подключены последовательно соединен ные квадратичный детектор и усилитель с регулируемым коэффициентом передачи, введены линия задержки, регулируемая линия задержки, второй квадратичный детектор, второй усилитель с регулируемым коэффициентом передачи, два аналого-цифровых преобразователя (А11П), блок п ересчета, блок управления, два триггера, два элемента И и реверсивный счетчик, при этом первые входы первого и второго аналого-цифровых преобразователей через последовательно соединенные регулируемую линию задержки и первый элемент И, второй вход которого соединен с выходом первого триггера, а третий вход - с выходом второго триггера, подключены к вы ходу элемента сравнения, второй вход ко- торого соединен с первой клеммой устройства и с входом упомянутого квадратичного детектора, второй вход первого аналого-цифрового преобразователя непосредственно, а второй вход второго аналого- цифрового преобразователя через последовательно соединенные линию задержки, вт рой квадратичный детектор и второй усилитель с регулируемым коэффициентом передачи подключены к второй клемме устройства, третий и четвертый входы первого и второго аналого-цифровых преобразователей соединены с соответствующими вькодами источника опорного напряжения, а пятый вход первого и второго аналого-цифровых преобразователей соединен одним из выходов блока управления, синхронизирующий выход первого аналогоцифрового преобразователя соединен с пер вым входом блока управления, первые выходы первого и второго аналого-цифровых преобразователей через второй элемент И соединены с вторым входом блока управления, второй выход блока управления соединен со счетным входом первого и второго триггеров, а третий выход блока управления соединен с инверсным входом первого триггера,, а инверсный вход второго триггера через блок пересчета соеди нен с выходом регулируемой лшии задерж ки, вторые выходы первого и второго аналого-цифровых преобразователей подключены соответственно к суммирующему и вычитающему входам реверсивного счетчика, выходом соединенного с входом блока индикации. Первый аналого-цифровой преобразователь выполнен в виде трех ключей аналогового элемента памяти, интегратора, бло ка начальной установки интегратора, двух элементов сравнения, трех- триггеров, генератора тактовых импульсов и элемента И| при этом входы первого и второго ключей соединены соответственно с третьим и четвертым входами аналого-цифрового преобразователя, а выходы ключей соединены с входами интегратора и блока начальной установки интегратора, выходы которых подключены к первым входам элементов сравнения, второй вход первого элемента сравнения через последовательно соединенные третий ключ и аналоговый элемент памяти соединен с вторым входом аналого-цифрового преобразователя, а второй вход второго элемента сравнения подключен к пятому входу аналого-цифрового преобразователя, выход первого элемента сравнения подсоединен к входу третьего триггера и к инверсному входу первого триггера, выход второго элемента срав- . нения подключен к инверсным входам второго и третьего триггеров, выход первого триггера соединен с одним из входов элемента И, с синхронизирующим выходом аналого-цифрового преобразователя и с управляющим входом второго ключа, инверсный выход первого триггера соединен с управляющим входом третьего ключа, вход первого триггера соединен с первым входом аналого-цифрового преобразователя и с входом второго триггера, инверсный выход которого соединен с управляющим входом блока -начальной установки интегратора и с первым выходом аналого-цифрового преобразователя, выход третьего триггера подключен к управляющему входу первого ключа, второй вход элемента И соединен с генераторомтактовых импульсов, а выход элемента И подключен к первому выходу аналого-цифрового преобразователя. Второй АШ выполнен в виде двух ключей, интегратора, блока начальной установки интегратора, двух элементов сравнения трех триггеров, генератора тактовых импульсов и элемента И, при этом вхоаы первого и второго триггеров соединены с первым входом аналого-цифрового преобразователя, информационные входы первого и второго ключей соединены соответственно с третьим и четвертым входами лип, первые входы первого и второго элементов сравнения соединены с выходом интегратора и с выходом блока начальной установки интегратора, вторь е входы элементов сравнения соединены соответс:твенно с вторым и с пятым входами АШЧ, выходы первого и второго ключей подключсны к входу интегратора, и к входу блока начальной установки интегратора, выход первого элемента сравнения соединен с инверсным входом первого триггера и входом второго триггера, выход второго глемента сравнения соединен с инверсным входами второго и третьего триггеров, управляющие входы первого и второго ключей подключены, соответственно к выхода первого и третьего триггеров. Инверсный выход второго триггера соединен с управляющим входом блока начальной установки интегратора и вторым выходом А11П, и выход третьего триггера соединен с первым входом элемента И, второй вход которого соединен с выходом генератора тактовых импульсов, а выход - с первым выходом АШ;

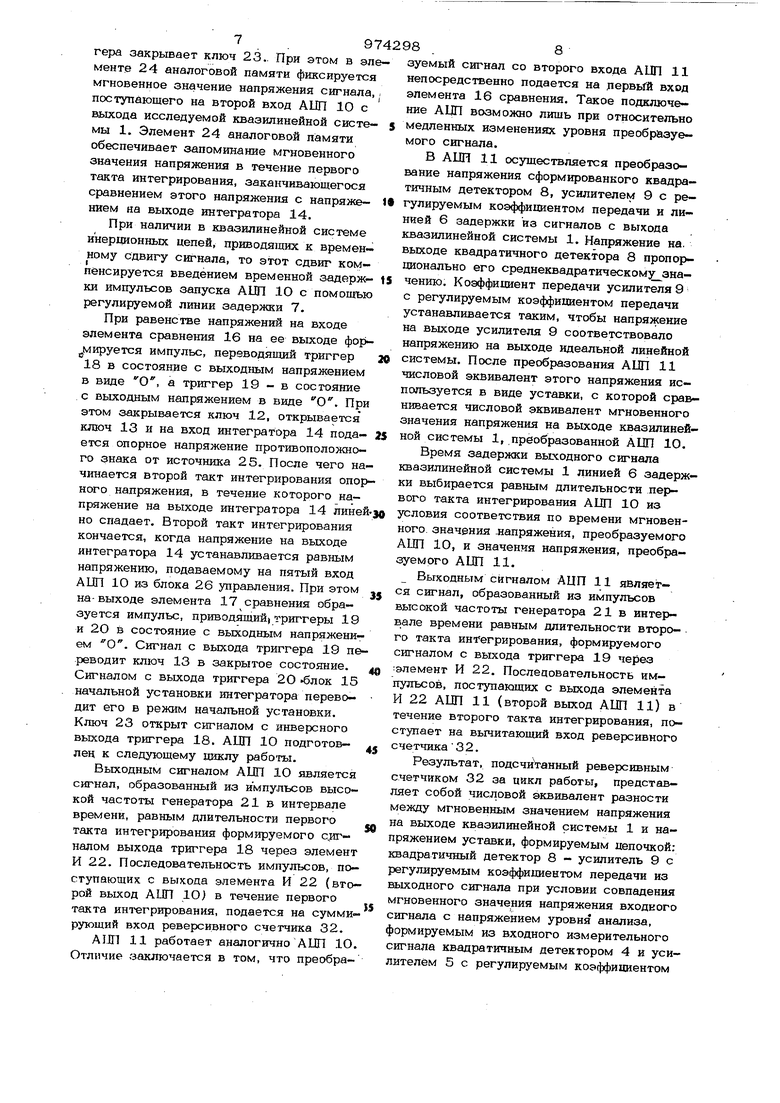

На чертеже представлена блок-схема устройства,

Устройство содержит исследуемую квазилинейную систему 1, генератор 2 измерительного сигнала, элемент 3 сравнения, первый квадратичный детектор 4, первый усилитель 5 с регулируемым коэф(}щциентом передачи, линию 6 задержки, регулируемую линию задержки 7, второй квадратичный детектор 8, второй усилитель 9 с регулируемым коэффициентом передачи, первый и второй аналого-цифровые преоб- разователи 10 и 11, включающие в себя ключи 12. и 13, интегратор 14, блок 15 начальной установки интегратора, элементъ1 16 и 17 сравнения, триггеры 18 - 20, генератор 21 тактовых импульсов, элемент И 22, третий ключ 23 И, элемент 24 аналоговой памяти, источник 25 опорного напряжения, блок 26 управления, первый и второй триггеры 27 и 28, первый и второй элементы И 29 и ЗО, блок пересчета 31, реверсивный счетчик 32 и блок 33 индикации и первую и вторую клеммы устройства 34 и 35.

Устройство работает следующим образом.

В исходном состоянии на выходе триггеров 27 и 28 устанавливается уровень О. В начале первого шжла работы триггеры 27 и 28 переводятся в состояние 1 сигналом от блока 26 управления. При этом дается разрешение на прохожде- .ние через элемент И 29 и регулируемую линию задержки 7 импульса запуска от элемента сравнения 3 на первые входы аналого-цифровых преобразователей 10v и 11. Импульс запуска на выходе элемента 3 сравнения возникает при равенстве на ее входе мгновенного значения напряжения измерительного сигнала, поступающего от генератора 2, и опорного напряжения уровня анализа, формируемого квадратичным детектором 4 и усилителем 5 с регулируемым коэффициентом передачи из сигнала измерительного генератора.

Напряжение на выходе квадратичного детектора 4 пропорционально среднеквад- ратическому (действующему) значению юмерительного сигнала. Напряжение на выходе усилителя 5 с регулируемым коэффициентом передачи устанавливается из условия требуемого превьпиения уровня анализа над среднеквадратическим значением измерительного сигнала. При контроле нелинейности уровень превышения среднеквадратического значения может быть задан в виде нормы.

После поступления импульса запуска с выхода элемента 3 сравнения через , элемент И 29 и регулируемую линию задержки 7 на первые входы начинается цикл работы ЛИП 10 и 11.

лип 10 и 11 выполнены по схеме двухтактного интегрирования опорного ; напряжения со сравнением результата интегрирования с преобразуемым значением измерительного сигнала.

В них осуществляется преобразование значений аналогового сигнала в длительность импульсов широтно-модулированног сигнала с последующим заполнением импульсами высокой частоты и подсчетом количестваимпульсов счетчикрм.

В исходном сэсюянии на выходе триггеров 18-20 ЛИП 10 и 11 устанавливается уровень О. При этом ключи 12 и 13 закрыты сигналами с выходом триггеров 18 и 19. Исходное состояние интегратора 14 обеспечивается схемой 15, которая .приведена в режим начальной ус- танов1ки сигналом, поступающим с инверсного выхода триггера 2О, Ключ 23 ЛИП 10 открыт сигналом с инверсного выхода .триггера 18.

После поступления импульса запуска на первые входы АШ 1О и 11 триггеры 18 и 20 приводятся в состояние с выходным уровнем, равным О, блок 15 переводит интегратор 14 из режима начальной установки в рабочий режим. При этом на вход интеграторов через ключ 12 поступает опорное напряжение, подаваемое на третьи входы АШ 1О и 11. На выхо.де интегрйтора 14 напряжение линейно нарастает, что соответствует началу первого такта интегрирования.

При срабатывании триггера 18 АШ. 10 в начале первого такта интегрирования сигнал с инверсного выхода этого триг- 797 гера закрывает ключ 23.. При этом в эле менте 24 аналоговой памяти фиксируется мгновенное значение напряжения сигнала, поступающего на второй вход А ЦП 10 с выхода исследуемой квазилинейной снстемы 1. Элемент 24 аналоговой памяти обеспечивает запоминание мгновенного значения напряжения в течение первого такта интегрирования, заканчивающегося сравнением этого напряжения с напряжением на выходе интегратора 14. При наличии в квазилинейной системе инерционных цепей, приводящих к временному сдвигу сигнала, то этот сдвиг компёнсируется введением временной задержки импульсов запуска AUDI 1О с помощью ре гулируемой линии задержки 7. При равенстве напряжений на входе элемента сравнения 16 на ее выходе фор- мируется импульс, переводяишй триггер 18 в состояние с выходным напряжением в виде О, а триггер 19 - в состояние с выходным напряжением в виде О. При этом закрывается ключ 12, открывается ключ 13 н на вход интегратора 14 пода- И

ется опорное напряжение противоположного знака от источника 25. После чего начинается второй такт интегрирования опорного напряжения, в течение которого на- пряжение на выходе интегратора 14 линей-дд но спадает. Второй такт интегрирования кончается, когда напряжение на выходе интегратора 14 устанавливается равным напряжению, подаваемому на пятый вход АИП 1О из блока 26 управления. При этом на- выходе элемента 17 сравнения образуется импульс, приводящий) триггеры 19 и 2О в состояние с выходным напряжением О. Сигнал с выхода триггера 19 пе реводит ключ 13 в закрытое состояние. Сигналом с выхода триггера 20 «блок 15 начальной установки интегратора переводит его в режим начальной установки. Ключ 23 открыт сигналом с инверсного выхода триггера 18. АПП 10 подготовлен к следующему циклу работы. Выходным сигналом А11П Ю является сигнал, образованный из импульсов высокой частоты генератора 21 в интервале времени, равным длительности первого такта интегрирования формируемого cjir- налом выхода триггера 18 через элемент И 22. Последовательность импульсов, поступающик с выхода элемента И 22 (второй выход Aim ДО) в течение первого такта интегрирования, подается на суммирующий вход реверсивного счетчика 32. AUn 11 работает аналогично АШ Ю Отличие заключается в том, что преобраВремя задержки выходного сигнала квазилинейной системы 1 линией 6 задержки выбирается равным длительности первого такта интегрирования АШ 10 из 88 зуемый сигнал со второго входа АШ 11 непосредственно подается на дервьШ вход элемента 16 сравнения. Такое подключение АШ возможно лишь при относительно медленных изменениях уровня преобразуемого сигнала. В АШ 11 осуществляется преобразование напряжения сформированного квадратичным детектором 8, усилителем 9 с регулируемым коэффициентом передачи и линией 6 задержки из сигналов с выхода квазилинейной системы 1. Напряжение на. выходе квадратичного детектора 8 пропоргионально его среднеквадратическом значению. Коэффициент передачи усилителя 9 с регулируемым коэффициентом передачи устанавливается таким, чтобы напряжение на выходе усилителя 9 соответствовало напряжению на выходе идеальной линейной системы. После преобразования АШ 11 числовой эквивалент этого напряжения используется в виде уставки, с которой сравнивается числовой эквивалент мгновенного значения напряжения на выходе квазилинейной системы 1, .преобразованной А11П 1О. условия соответствия по времени мгновенного. значения .напряжения, преобразуемого АШ Ю, и значения напряжения, преобразуемого АШ 11. Выходным сигналом АЦП 11 является сигнал, образованный из импульсов высокой частоты генератора 21 в интервале времени равным длительности второ- го такта интегрирования, формируемого сигналом с выхода триггера 19 через :элемент И 22. Последовательность импульсов, поступающих с выхода элемента И 22 АШ 11 (второй выход АШ 11) в течение второго такта интегрирования, поступает на вычитающий вход реверсивного счетчика 32. Результат, подсчиУанный реверсивным счетчиком 32 за цикл работы, представляет собой числовой эквивалент разности между мгновенным значением напряжения на выходе квазилинейной системы 1 и напряжением уставки, формируемым цепочкой; квадратичный детектор 8 - усилитель 9 с регулируемым коэффициентом передачи из выходного сигнала при условии совпадения мгновенного значения напряжения входного сигнала с напряжением уровня анализа, формируемым из входного измерительного сигнала квадратичным детектором 4 и усилителем 5 с регулируемым коэффициентом передачи. Согласование соответствующих моментов времени в цикле обеспечивается линией 6 задержки, регулируемой линией задержки 7 и эквивалентом аналоговой па мяти АШ 10. Повторный запуск АУЛ 1О и 11 возможер не в момент очередного совпадени мгновенного значения напряжения входног сигнала и напряжение уровня анализа на входе элемента 3 сравнения, а лишь толь ко после окончания полного цикла работы обеспечиваемого следящей цепью, состоящей из элемента И 29 и триггера 27. Досле запуска сигнал с третьего выхода А1Ш 10 через блок 26 управления переводит триггер i27 в состояние с выходны напряжением в виде О . При .этом на входе элемента И 29 напряжение, запрещающее прохождение импульсов запуска на первые входы АШ 1О и 11. Последующий повторный запуск возможен лишь после поступления на вход триггера. 27 через блок 26 управления и элемент И 30сигналов с первых выходов АШ 1О и 11, выдаваемых после окончани шпсла преобразования. Блок пересчета 31 и триггер 28 осуществляют операции статистического усре нения. Отношение разности между двумя последовательностями импульсов, подсчитанной реверсивным счетчиком 32 за N циклов к количеству циклов (запусков) N, задаваемому с помощью блока пересчета 31и триггера 28, при условии, что в мо менты запуска входной сигнал принимает заданное фиксированное значение, являет ся статистической оценкой условного сред него значения (математического ожидания Началом пересчета служит сигнал с блока 26 управления, переводящий триггер 28 в состояние с выходным напряжением в виде 1. После чего вьщается разрешающий сигнал для прохождения импульсов запуска через элемент И 29 на первые входы АШ Ю и 11. После прохождения N импульсов запуска на выходе блока пересчета 31 возникает импульс, возвращающий.триггер 28 в состояние с выходным напряжением в вид О, а на вход элемента И 29 выдается сигнал, запрещающий прохождение импульсов запуска. Число п , зафиксированное реверсивным счетчиком 32 за N циклов, определяется из выражения ()) о,Ыдк( гпр d - коэффициент пропорциональности; X ц( -оценкиусловныхсреонихзна чений напряжений, преобразован- ных AUn 10 и 11 за циклов измерений; , .. дх - отклонение XV. от 5t V. Если коэффициент пересчета 1 выбрать равным величине то оценка л х определяется из выражения лх-п-10 где число, указывающее положение запятой при представлении в десятичной системе счисления. Результат выдается на блок 33 индикации. Блок 33 индикации может, иметь шкалу с указанием номинального значения и границ допустимого изменения дХ..Результаты измерения и контроля могут бытьвьщаны на внешние устройства считывания и использованы в автоматизированной системе измерений и контроля. Формула изобретения 1. Устройство для измерения п контроля нелинейности амплитудной характеристики квазилинейных систем, содержащее блок индикации, источник опорного нацряжения, генератор измерительного сигнала, подключенный к первой клемме устройства, элемент сравнения, к первому входу которого подключены последовательно соединенные квадратичный детектор и усилитель с регулируемым коэффициентом передачи, отличающееся тем, что, с целью повьпиения точности измерения и контроля, в него введены линия задержки, регулируемая линия задержки, второй квадратичный детектор, второй усилитель с регулируемым коэффициентом передачи, два аналого-цифровых преобразователя, блок пересчета, блок управления, два триггера, два элемента И и реверсивный счетчик; причем первые входы первого и второго аналого-цифровых преобразователей . через последовательно соединенные регулируемую линию задержки и первый элемент И, второй вход которого соединен с выходом первого триггера, а третий входс выходом второго триггера, подключены к выходу элемента сравнения, второй вход которого соединен с первой клеммой уст ройства и с входом упомянутого квадратичного детектора, второй вход первого аналого-цифрового преобразователя непо- средетвенно, а второй вход второго аналого-цифрового преобразователя через после девательно соединенные линию задеряски второй квадратичный детектор и второй уси яителъ с регулируемым коэффихшентом передачн подключены к второй клемме уст ройства, третий к четвертый входы первого и второго аналого-цифровых преобразователей соединены с соответствующими вы ходами источника опорного напряжения, а пятый вход первого и второго аналогоцифровых преобразователей соединен од- ним из выходов блока управления, синхронизирующий выход первого аналого-цифрового преобразователя соединен с первым входом блока управления, первые выходы первого и второго аналого-цифровых преобразователей через второй элемент И соединены с вторым входом блока управления, второй выход блока управления соеди нен со счетным входом первого и второго 1риггеров, а третий выход блока управления соединен с инверсным входом первого триггера, а инверсный вход второго триггера через блок пересчета соединен с выходом регулируемой линии задержки, вторые выходы первого и второго аналогоцифровых преобразователей подключены соответственно к суммирующему и вычитаюшему входам реверсивного счетчика, выходом соединенного с входом блока индикации. 2. Устройство по п. 1, отлича ю - ш е е с я тем, что второй аналого-цифровой преобразователь выполнен в виде двух клю- чей, интегратора, блока начальной установки интегратора, двух элементов сравнения, трех триггеров, генератора тактовых импульсов и элемента И, при этом входы первого и второго триггеров соединены с первым входом аналого-цифровдго преобразователя, информационные входы первого и второго ключей соединены соответст венно с третьим и четвертым входами аналого-цифрового преобразователя, первые входы первого и второго элементов сравнения соединены с выходом интегратора и с выходом блока начальной установки интегратора, вторые входы элементов сравнения соединены соответственно с вторым и с пятым входами аналогоцифрового преобразователя,, выходы перво- го и второго ключей подключены ко входу интегратора, и к входу блока начальной установки интегратора, выход первого эле мента сравнения соединен с инверсным входом первого триггера и входом второго триггера, выход второго элемента срав нения соединен с инверсными входами вто рого и третьего триггеров, управляющие входы первого и второго ключей подключены соответственно к выходам первого и третьего триггеров, инверсный выход второго триггера соединен с управляющим входом блока начальной установки интегратора и BTopiJM выходом аналого-цифрового преобразователя, а выход третьего триггера соединен с первым входом элемента И, второй вход которого соединен с выходом генератора тактовых импулглов, а выход - с первым выходом аналого-цифрового преобразователя. 3. Устройство по п, 1, отлича ющ е е с я тем, что первый аналого-цифровой преобразователь вьшолнен в виде трех ключей, аналогового элемента памяти, интегратора, блока начальной установки интегратора, двух элементов сравнения, трех триггеров, генератора тактовых импульсов и элемента И, при этом входы первого и второго ключей соединены соответственно с третьим и четвертым входами аналого-цифрового преобразователя, а выходы ключей соединены с входами интегратора и блока начальной установки интегратора, выходы которых подключены к первым входам элементов сравнения, второй вход первого из которых через последовательно соединенные третий ключ и аналоговый элемент памяти соединен с вторым входом аналого-цифрового преобразователя, а второй вход второго элемента сравнения подключен к пятому входу зналого-цифрового преобразователя, вы- ход первого элемента сравнения подсоеди.нен к входу третьего триггера и к инверсному входупервого триггера, выход вто jporo элемента сравнения подключен к инверсным входам второго и третьего триггеров, выход первого триггера соединен с одним из входом элемента И, с синхронизирующим выходом .аналого-цифрового преобразователя и с управляющим входом второго ключа, инверсный выход первого триггера соединен с управляющим входом третьего ключа, вход первого триггера соединен с первым входом аналого-цифрового преобразователя и с входом в торого триггера, инверсный выход которого соединен с управляющим входом блока начальной установки интегратора и с первым выходом аналого-дифрового преобразователя, выход третьего триггера подключен к управляющему входу первого ключа, второй вход элемента И соединен с генератором тактовыж импульсов, а выход элемента И подключен к первому выходу аналого-цифрового преобразователя. 13 Источники информации, принятые во внимание при экспе|зтиэе 1. Авторское свидетельство СССР № 361449, кл. q 01 R 29/ОО, 1972. f 74208 2. Т. Корд. Новый метод измерения и испытания нелинейности квазилинейных систем с помоигью стох.чг гического измерительного сигнала. Hiradastehn ka , 5 1976; № 2, с. 43 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения и контроля нелинейности амплитудной характеристики квазилинейных систем | 1982 |

|

SU1100576A2 |

| Устройство для сжатия информации | 1986 |

|

SU1336080A1 |

| Двухтактный измеритель энергии одиночных импульсов | 1990 |

|

SU1721520A1 |

| Устройство для коррекции нелинейности | 1982 |

|

SU1056228A1 |

| Устройство для цифровой записи-воспроизведения цифровой информации | 1990 |

|

SU1788521A1 |

| Устройство для измерения средней мощности сигналов в каналах и трактах систем связи | 1983 |

|

SU1095083A1 |

| Прецизионный датчик перемещений | 1983 |

|

SU1158856A1 |

| МОДУЛЯЦИОННЫЙ РАДИОМЕТР | 2001 |

|

RU2187824C1 |

| Аналого-цифровой преобразователь двойного интегрирования | 1981 |

|

SU1001464A1 |

| УСТРОЙСТВО ПОИСКА И СОПРОВОЖДЕНИЯ СИГНАЛА СИНХРОНИЗАЦИИ В СПУТНИКОВЫХ СИСТЕМАХ СВЯЗИ ПО ПРИЕМУ | 1995 |

|

RU2093964C1 |

Авторы

Даты

1982-11-15—Публикация

1981-05-11—Подача