Изобретение относится к области передачи цифровой информации и вычислительной техники, устройствам шифрования данных. В частности, может использоваться для аутентификации аппаратных средств в системах управления комплексов подводной добычи газа и построенных в виде систем на кристалле (СнК).

Известно изобретение по патенту RU 2 585 988 С1 (патентообладатель Открытое Акционерное Общество «Байкал электронике», МПК G06F 21/60, H04L 9/00), относящееся к области шифрования потоков данных, содержащее устройство шифрования, с помощью которого данные могут быть зашифрованы или расшифрованы по алгоритму криптографического преобразования ГОСТ 28147-89, при этом схема предполагает хранение таблиц замен, секретного ключа для шифрования/расшифрования, инициализирующего вектора синхропосылки, используемого для шифрования в режиме гамммирования и гаммирования с обратной связью, инициализирующего вектора имитовставки. Также схема содержит центральный процессор, блок внутренней коммутации, контроллер доступа к памяти, внутренней или внешней (в зависимости от исполнения). Данное решение является наиболее близким к заявляемому изобретению, но имеет ряд недостатков:

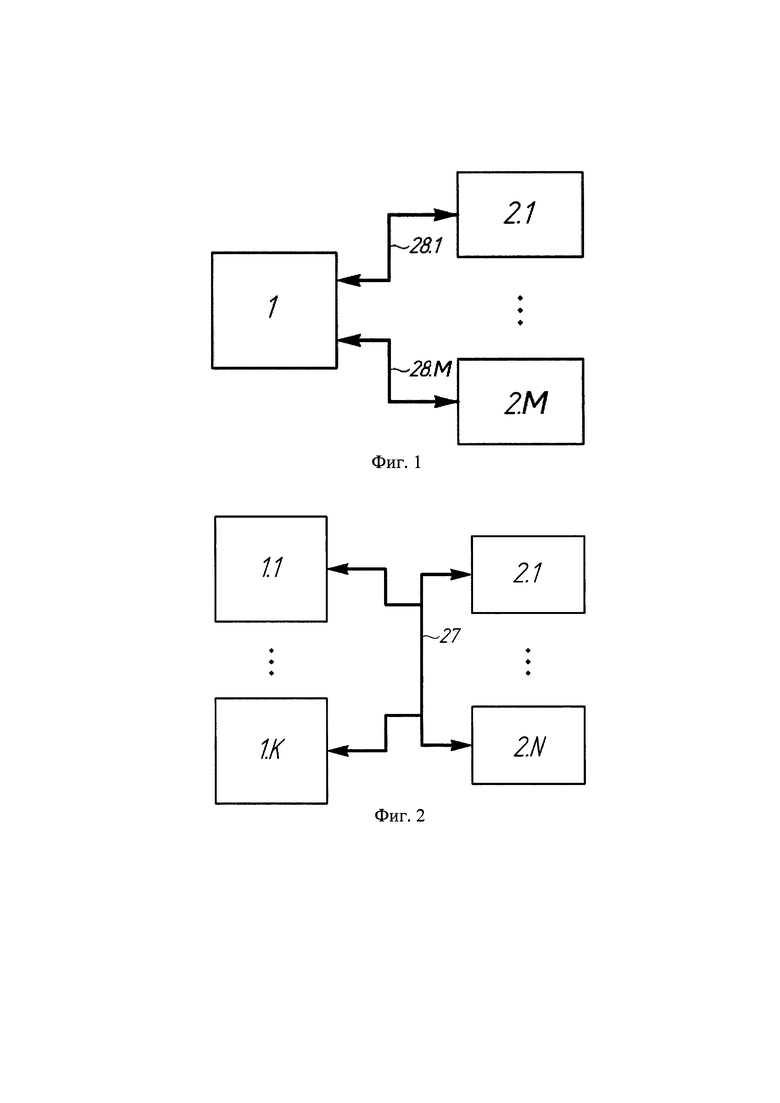

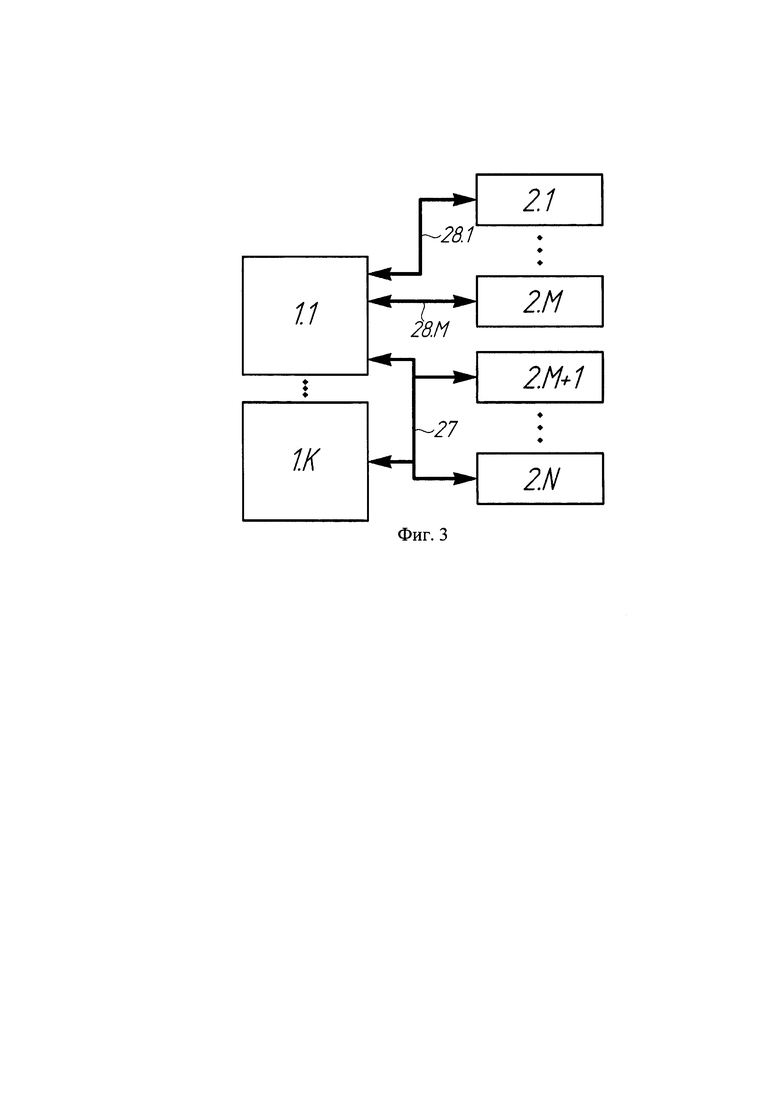

а) Отсутствие технической возможности осуществления строгой аутентификации по ГОСТ Р ИСО/МЭК 9594-8-98 между абонентами в соответствии со схемами аутентификации Фиг. 1, Фиг. 2, Фиг. 3.

б) Использование одновременно только одного ключа в процедуре шифрования по ГОСТ 28147-89.

Задачей изобретения является создание устройства с возможностью осуществления строгой аутентификации по ГОСТ Р ИСО/МЭК 9594-8-98 между абонентами и использованием двух ключей в процедуре шифрования по ГОСТ 28147-89.

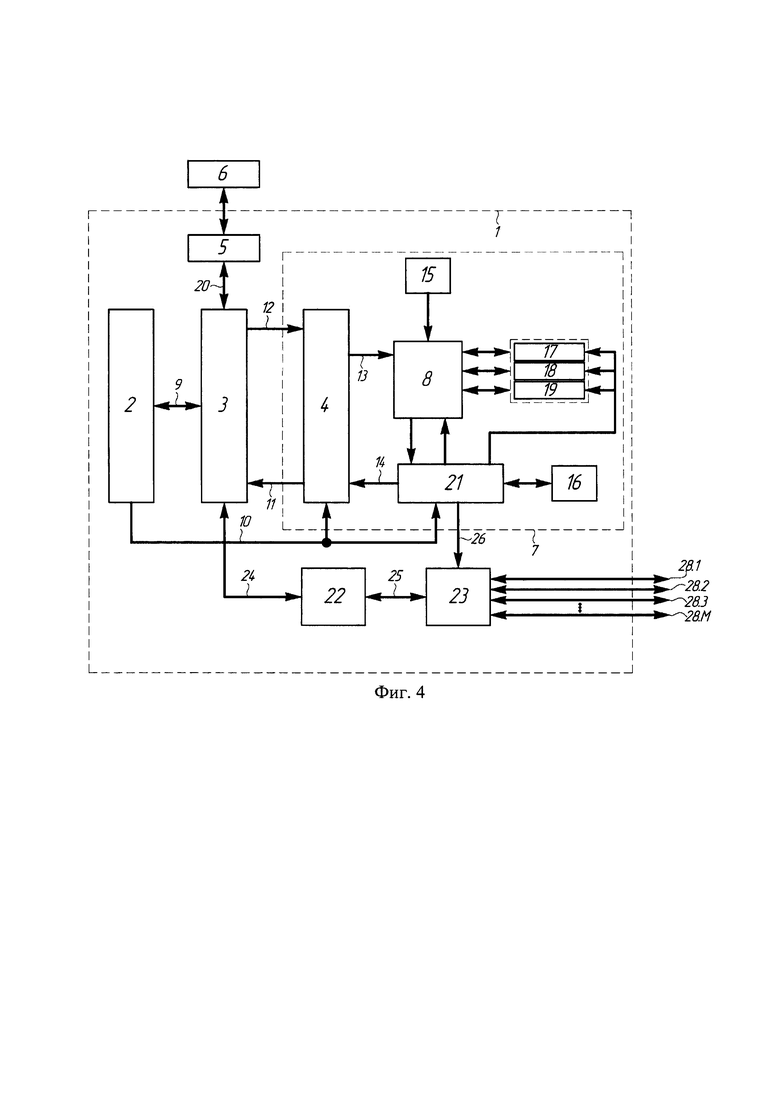

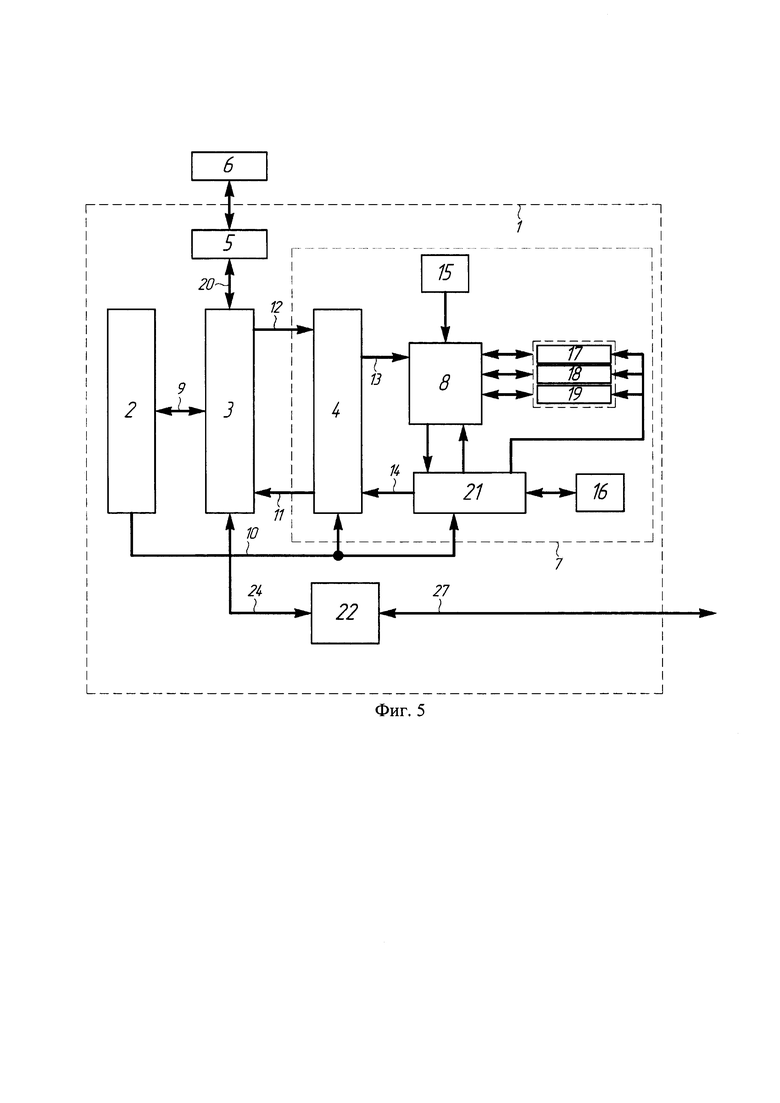

Заявленное изобретение представляет собой устройство симметричного шифрования данных с использованием алгоритма строгой аутентификации (УСШД) по ГОСТ Р ИСО/МЭК 9594-8-98 для аутентификации аппаратных средств, объединенных по схеме Фиг. 1, Фиг. 2 или Фиг. 3 (3 варианта), использующее симметричный алгоритм криптографического преобразования ГОСТ 28147-89 и реализованное в виде СнК с функциональными модулями (3 варианта). СнК (1) играет роль удаленного управляющего устройства (сервера) в системе управления, СнК (2.1…2.N) выполняют функции блоков контроля и управления (контроллеров) на объекте управления и могут соединяться с удаленными управляющими устройствами (1.1…1.K) в зависимости от варианта реализации устройства шифрования данных только по мультиплексированным шинам внешнего интерфейса (28.1…28.М), общей шине данных внешнего интерфейса (27) или по нескольким типам шин одновременно (27 и 28.1…28.М).

Краткое описание чертежей

Фиг. 1 - Схема аутентификации устройств при использовании мультиплексированных шин передачи данных;

Фиг. 2 - Схема аутентификации устройств при использовании общей шины передачи данных;

Фиг. 3 - Схема аутентификации устройств при использовании комбинации мультиплексированных и общей шин передачи данных;

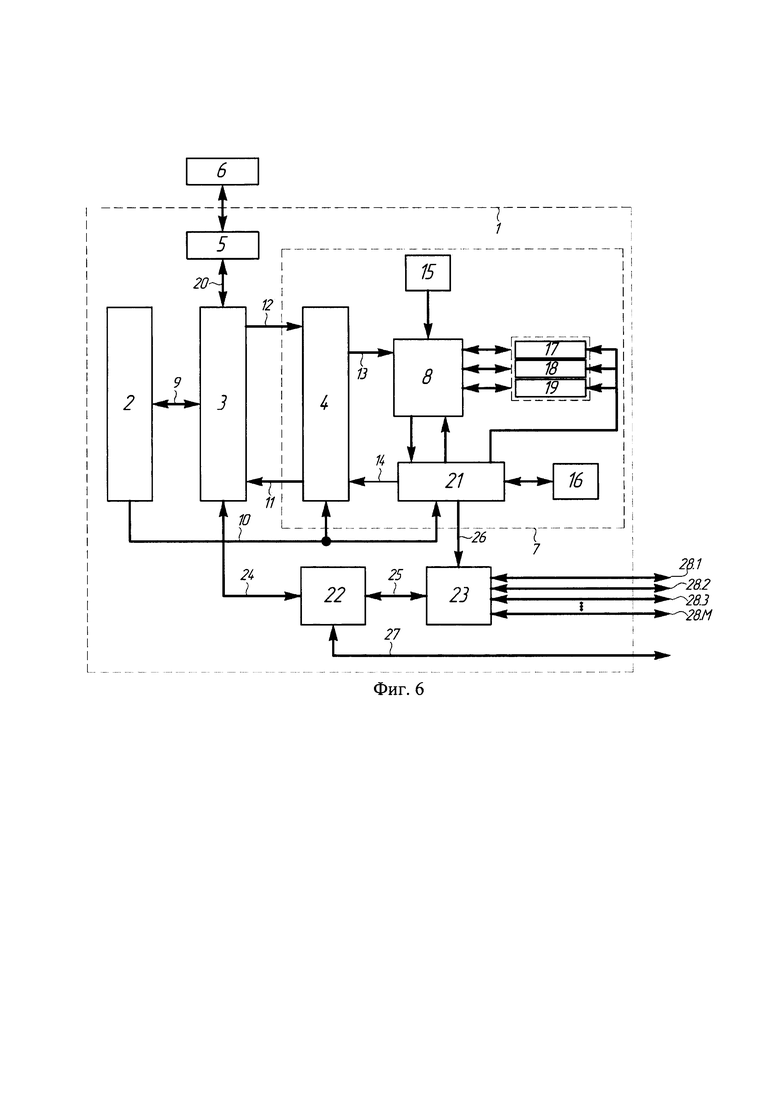

Фиг. 4 - Архитектура УСШД с мультиплексированными шинами передачи данных;

Фиг. 5 - Архитектура УСШД с общей шиной передачи данных;

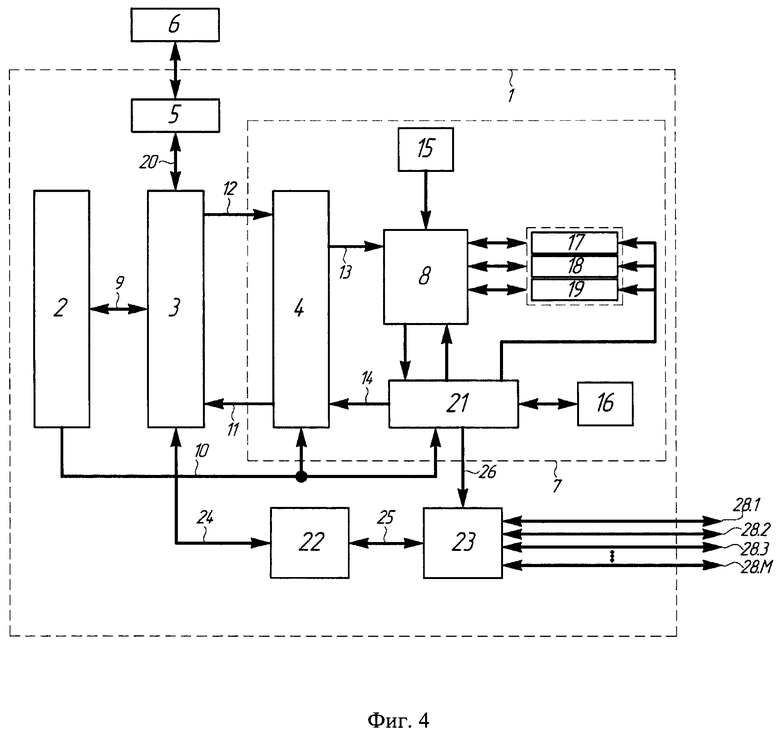

Фиг. 6 - Архитектура УСШД с комбинацией мультиплексированных и общей шин передачи данных.

УСШД реализуется в виде СнК (1), может быть выполнены в трех вариантах (Вариант 1 - Фиг. 4, Вариант 2 - Фиг. 5, Вариант 3 - Фиг. 6) и содержит следующие функциональные блоки и компоненты:

(2) - центральный процессор;

(3) - блок внутренней коммутации;

(4) - контроллер прямого доступа к памяти;

(5) - контроллер доступа к памяти;

(6) - память;

(7) - устройство шифрования;

(8) - вычислительный модуль;

(10) - конфигурационный интерфейс;

(9), (11), (12), (13), (14), (20), (24) - внутренние шины адрес-данные (ШД);

(15) - генератор псевдослучайных чисел;

(16) -таймер;

(17) - регистр общего назначения для хранения таблицы замен (РОН ТЗ);

(18), (19) - регистры общего назначения для хранения секретных ключей шифрования (РОН КШ);

(21) - блок управления;

(22) - контроллер внешнего интерфейса;

(23) - блок мультиплексирования;

(25) - мультиплексируемая шина данных;

(26) - шина управления блоком мультиплексирования;

(27) - общая шина данных внешнего интерфейса;

(28.1…28.М) - мультиплексированные шины внешнего интерфейса.

Связи между элементами СнК согласно Варианту 1:

СнК (1) содержит в своем составе центральный процессор (2), блок коммутации (3), контроллер доступа к памяти (5), контроллер внешнего интерфейса (22), блок мультиплексирования (23) и устройство шифрования (7), в состав которого входят: контроллер прямого доступа к памяти (4), вычислительный модуль (8), генератор псевдослучайных чисел (15), таймер (16), РОН ТЗ (17), РОН КШ (18, 19) и блок управления (21). Память (6) может быть реализована как в составе СнК (1), так и быть внешней по отношению к нему, что не влияет на достижение технического результата.

Центральный процессор (2), связан ШД (9) с блоком внутренней коммутации (3), а также конфигурационным интерфейсом (10) с контроллером прямого доступа в память (4) и блоком управления (21).

Блок внутренней коммутации (3) связан ШД (11, 12) с контроллером прямого доступа к памяти, а также ШД (20) и ШД (24) с контроллером доступа к памяти (5) и контроллером внешнего интерфейса (22) соответственно. Контроллер доступа к памяти (5) связан с памятью (6), а контроллер внешнего интерфейса (22) через мультиплексируемую шину данных (25) связан с блоком мультиплексирования (23), который также принимает сигналы от блока управления (21) через шину управления блоком мультиплексирования (26) и имеет мультиплексированные шины внешнего интерфейса (28.1…28.М) поступающие на выход СнК (1).

Вычислительный модуль (8) взаимосвязан с РОН ТЗ (17), РОН КШ (18, 19), блоком управления (21) и принимает сигналы от блока внутренней коммутации через ШД (13) и генератора псевдослучайных чисел (15).

Блок управления (21) посылает сигналы в РОН ТЗ (17), РОН КШ (18, 19), через ШД (14) в блок внутренней коммутации (4) и взаимосвязан с таймером (16).

Вариант 2 отличается от Варианта 1 следующим:

1. Отсутствует блок мультиплексирования и связанные с ним мультиплексируемая шина данных, шина управления блоком мультиплексирования, мультиплексированные шины внешнего интерфейса.

2. Введена общая шина данных внешнего интерфейса (27), которая из контроллера внешнего интерфейса (22) поступает на выход СнК (1).

Вариант 3 объединяет в себе Варианты 1 и 2, и отличается от Варианта 1 тем, что дополнительно введена общая шина данных внешнего интерфейса (27), которая из контроллера внешнего интерфейса (22) поступает на выход СнК (1).

Принцип работы устройства симметричного шифрования данных с использованием алгоритма строгой аутентификации.

Устройство шифрования (7) работает в режиме простой замены. Данные для передачи/приема по внешнему интерфейсу хранятся в памяти (6), и поступают из нее в устройство шифрования и в обратную сторону блоками по 64 бит каждый. Таким образом память (6) играет роль буфера данных внешнего интерфейса.

Данные для шифрования и результаты шифрования передаются между блоком (3) внутренней коммутации, контроллером (4) прямого доступа к памяти и вычислительным устройством (8) по внутренним шинам (11), (12), (13), (14), (20) пакетами, состоящими из кадров, равными по размеру блоку обрабатываемых данных (64 бит).

Блок внутренней коммутации (3) передает данные в контроллер прямого доступа к памяти (4) и принимает их из него. Для исключения задержек при работе с внешней памятью данные могут накапливаться во встроенных буферах контроллера (4).

Вычислительный модуль (8) используется для реализации базового цикла шифрования. Ключи хранятся во внутренних регистрах (18), (19) устройства шифрования (7).

Процесс осуществления строгой аутентификации аппаратных средств следующий:

1) Секретный ключ группы «устройство управления - исполнительные устройства» K0…511, загружается в регистры (18), (19), при этом личный ключ инициатора передачи информации Kл=K0…255 сохраняется в регистре (18), а ключ приемника информации Ko=K256…511 - в регистре (19).

2) УСШД, реализованное на СнК (1) и выступающее в виде управляющего устройства (УУ), показано на Фиг. 1 как (1) и на Фиг. 2, Фиг. 3 как (1.1…1.K). Т.к. применяется несколько таких СнК, УУ создает неповторяющийся маркер (случайное число) с помощью генератора псевдослучайных чисел (15), запускает таймер (16), отправляет по каналу(лам) связи 27 или (28.1…28.N) сообщение исполнительному устройству (2.1…2.N) либо (2.1…2.М), сформированное по следующему закону:

Xл_mast (№_sl, Xo_sl(CЧ_mast_N, Данные)),

где Xл_mast(x) - зашифрование информации х с использованием личного ключа инициатора передачи информации (управляющего устройства) Kл=K0…255;

Xo_sl(x) - зашифрование информации х с использованием личного ключа приемника информации (исполнительного устройства) Kо=K256…511;

№_sl - номер приемника информации;

CЧ_mast-N - случайное число (неповторяющийся маркер), сгенерированное инициатором передачи, необходимое для строгой аутентификации во время обмена;

Данные - данные для передачи.

3) Блок контроля и управления (БКУ), в качестве которого выступает СнК (1) в роли исполнительного устройства, на Фиг. 1 и Фиг. 2 и Фиг. 3 показано как (2.1…2.N) для вариантов с общей шиной данных и (2.1…2.М) для вариантов с мультиплексированными шинами данных. БКУ дешифрует принятые данные с использованием ключа инициатора передачи Kл=K0…255 и ключа приемника информации Kо=K256…511.

Процедура аутентификации продолжается только с тем ИУ, номер №_sl которого соответствует указанному в сообщении от УУ и только такое ИУ способно расшифровать CЧ_mast_N и Данные.

4) БКУ (2.1…2.N) либо (2.1…2.М) создает неповторяющийся маркер (случайное число), запускает таймер (16) БКУ и отправляет ответ, формируя его по формуле:

Xл_sl(№_mast, Xo_mast (Ответ, CЧ_mast_N, CЧ_sl_N)),

где Хл_sl(x) - зашифрование информации х с использованием личного ключа инициатора передачи информации Kл=K0…255;

Xo_mast(x) - зашифрование информации х с использованием ключа приемника информации (управляющего устройства) Kл=К256…511;

№_mast - номер инициатора передачи информации;

Ответ - код ошибки получения приказа;

СЧ_ mast-N - случайное число (неповторяющийся маркер), полученное от инициатора передачи;

CЧ_sl-N - случайное число, сгенерированное получателем информации (БКУ) (2.1) или … (2.N) и необходимое для строгой аутентификации во время обмена.

5) УУ (1.1…1.K) дешифрует принятое сообщения с использованием личного ключа инициатора передачи Kл=K0…255 и далее с использованием ключа приемника информации, сравнивая при этом полученный маркер CЧ_mast-N с созданным. При их совпадении процедура аутентификации продолжается по п. 6, иначе действия несанкционированные, процедура аутентификации прерывается.

6) УУ (1) отправляет по каналу связи подтверждение, сформированное следующим образом

Xл_mast (№_sl, СЧ_ sl_N).

7) БКУ (2.1…2.N) либо (2.1…2.М) дешифрует принятые данные с использованием личного ключа инициатора передачи Kл=K0…255, сравнивает полученный маркер СЧ_ sl_N с созданным и при их совпадении осуществляет разрешенные действия с данными, полученными в п. 3.

Заявленное устройство симметричного шифрования данных с использованием алгоритма строгой аутентификации, работающее в составе системы (Фиг. 1, Фиг. 2 или Фиг. 3) и позволяющее выполнять процедуру строгой аутентификации по ГОСТ Р ИСО/МЭК 9594-8-98, используя при этом алгоритм криптографического преобразования ГОСТ 28147-89 в режиме простой замены взамен криптосистемы RSA, что позволяет ускорить процесс аутентификации и в большей степени защитить передаваемые по каналу данные в системах, построенных по схемам Фиг. 1, Фиг. 2, Фиг. 3, включает в себя устройство шифрования (7), выполняющее процедуру шифрования, расшифрования данных в процессе аутентификации, генератор псевдослучайных чисел (15), создающий неповторяющийся маркер (номер) сообщения для трех шагов процедуры строгой аутентификации (выполнен в виде комбинационной схемы), таймер (16), ограничивающий время ожидания при выполнении процедуры зашифрования/расшифрования данных, (выполнен в виде специализированной микросхемы), внешнее или внутреннее по отношению к устройству шифрования (7) запоминающее устройство (6) с контроллером доступа (5), являющееся буфером для хранения в зашифрованном виде передаваемых по каналу данных, что гарантирует невозможность извлечения полезной информации и позволяет защитить систему от несанкционированного доступа к данным (выполняется в виде статического ОЗУ), центральный процессор общего назначения (2), исполняющий основную программу устройства (может выполняться на микросхеме микропроцессора), блок внутренней коммутации (3), обеспечивающий обмен данными между элементами системы (выполнен в виде комбинационной схемы), контроллер внешнего интерфейса (22), организующий интерфейс передачи данных для обмена с внешними устройствами по общей (27) или мультиплексируемой (25) шинам (выполняется в виде специализированных микросхем), блок мультиплексирования шин (23) внешнего интерфейса передачи данных, осуществляющий коммутацию последовательной шины (25) на несколько мультиплексированных последовательных шин передачи данных (28.1), (28.2),…, (28.М) (выполняется в виде комбинационной схемы с оптоэлектронной развязкой). Общая шина (27) может быть выполнена по стандарту CAN или RS-485, мультиплексированная - по стандарту RS-232. Контроллер доступа к памяти (5) может быть встроен в центральный процессор (2).

Возможность применения двух ключей шифрования и проведения процедуры строгой аутентификации по ГОСТ Р ИСО/МЭК 9594-8-98 обеспечивают: центральный процессор (2), вычислительный модуль (8), генератор псевдослучайных чисел (15), таймер (16), РОН ТЗ (17), РОН КШ (18, 19), а также контроллер внешнего интерфейса (22) и/или блок мультиплексирования (23), в зависимости от варианта СнК.

Устройство шифрования (7) включает в себя контроллер (4) прямого доступа к памяти (6), обеспечивающий передачу полученных по шине (24) и записанных в память (6) зашифрованных данных (выполняется в виде специализированной микросхемы), а также передачу зашифрованных данных из устройства шифрования в память (6) на каждом этапе осуществления строгой аутентификации, вычислительный модуль (8), осуществляющий алгоритм криптографического преобразования ГОСТ 28147-89 в режиме простой замены и формирование зашифрованных пакетов данных для аутентификации, управляющие регистры (17) (512 бит), в который загружается таблица замен, регистр (18), в который загружается личный ключ инициатора передачи информации Kл=K0…255 (256 бит), регистр (19), в который загружается общий ключ приемника информации Kо=K256…511, блок управления (21) для синхронизации работы блоков устройства шифрования (7), а также выбора текущей шины для отправки зашифрованного сообщения строгой аутентификации (реализуется в виде конечного автомата).

Устройство может быть осуществлено в трех вариантах: СнК только с мультиплексированными шинами передачи данных (Фиг. 4), СнК только с общей шиной передачи данных (Фиг. 5), СнК с комбинацией мультиплексированных и общей шин передачи данных (Фиг. 6), при этом БКУ реализуется по архитектуре Фиг. 4 (с отсутствующим блоком мультиплексирования шин внешнего интерфейса (23)) или архитектуре Фиг. 5.

Команды (данные), генерируемые устройством управления поступают из внутренних регистров процессора (2) по шинам (9), (12), (13) в вычислительный модуль (8), где происходит формирование сообщений в описанном выше формате, их шифрование по алгоритму ГОСТ 28147-89 в режиме простой замены. Зашифрованные сообщения поступают по шинам (14), (20) в память (6), откуда посредством контроллера внешнего интерфейса передаются по одному из каналов передачи данных в БКУ 2.1 или 2.N в зависимости от необходимого приемника информации (номера БКУ), указанного в сообщении. При этом центральный процессор (2) генерирует сигналы управления блоком внутренней коммутации (3), контроллером прямого доступа к памяти (4), а также блоком управления (21) устройства шифрования (7) (по конфигурационному интерфейсу (10)), определяющие направление передачи: в устройство шифрования (7), из устройства шифрования (7) в память (6). Блок управления (21) устройства шифрования (7) осуществляет выставку сигналов на запуск таймера (16), начало цикла шифрования/расшифрования, извлечение случайного числа из блока генерации псевдослучайного числа (15), сброс схемы в начальное состояние в случае поступления от таймера (16) сигнала переполнения при длительном ожидании ответного сообщения, а также выставляет сигнал выбора текущей шины передачи данных (27), (28.1), (28.2), … или (28.М) по конфигурационному интерфейсу (26). Ответное (входящее) сообщение, поступающее по внешней шине 27, 28.1, 28.2,… или 28.М посредством контроллера внешнего интерфейса (22) в память (6), передается в устройство шифрования (7), где происходит расшифрование сообщения по алгоритму ГОСТ 28147-89, формирование ответного сообщения (при совпадении случайного числа), его зашифрование и отправка по каналу связи по описанной выше процедуре.

Таким образом заявлено устройство симметричного шифрования данных с использованием алгоритма строгой аутентификации согласно ГОСТ 28147-89, реализующееся в виде СнК (1), включающее в себя центральный процессор (2), взаимосвязанный с блоком внутренней коммутации (3) а также передающий сигнал на блок управления (21) и контроллер прямого доступа к памяти (4), который взаимосвязан с блоком внутренней коммутации (3) и передает сигнал на вычислительный модуль (8), контроллер доступа к памяти (5) взаимосвязанный с блоком внутренней коммутации (3) и памятью (6), вычислительный модуль (8) с возможностью реализации шифрования данных в соответствии с алгоритмом криптографического преобразования взаимосвязанный с РОН ТЗ (17) и РОН КШ (18), блок управления (21) принимающий сигнал от вычислительного модуля (8) и передающий сигналы на РОН ТЗ (17) и РОН КШ (18), при этом устройство работает по ГОСТ Р ИСО/МЭК 9594-8-98, в СнК (1) введены контроллер внешнего интерфейса (22) и блок мультиплексирования (23), в устройство шифрования (7) также введены генератор псевдослучайных чисел (15), дополнительный РОН КШ (19) и таймер (16), взаимосвязанный с блоком управления (21), который подключен через шину управления к блоку мультиплексирования (23) и связан с РОН КШ (19) и вычислительным модулем (8), который взаимосвязан с РОН КШ (19) и принимает сигнал от генератора псевдослучайных чисел (15); контроллер внешнего интерфейса (22) связан с блоком внутренней коммутации (3), блок мультиплексирования (23), осуществляющий коммутацию мультиплексируемой шины данных, соединяющей контроллер внешнего интерфейса (22) с блоком мультиплексирования (23), а также мультиплексированные шины на выходе блока мультиплексирования (23); в качестве ОЗУ используется статическая память, хранящая только зашифрованные по ГОСТ 28147-89 данные.

Также возможны варианты устройства симметричного шифрования данных с использованием алгоритма строгой аутентификации:

- с включением общей шины данных на выходе контроллера внешнего интерфейса.

- с исключением блока мультиплексирования и связанных с ним мультиплексируемой шины данных, шины управления блоком мультиплексирования и мультиплексированных шин внешнего интерфейса, при этом с включением общей шины данных на выходе контроллера внешнего интерфейса.

Техническим результатом изобретения является устройство с возможностью осуществления строгой аутентификации по ГОСТ Р ИСО/МЭК 9594-8-98 между абонентами и использованием двух ключей в процедуре шифрования по ГОСТ 28147-89.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ШИФРОВАНИЯ ДАННЫХ (ВАРИАНТЫ), СИСТЕМА НА КРИСТАЛЛЕ С ЕГО ИСПОЛЬЗОВАНИЕМ (ВАРИАНТЫ) | 2015 |

|

RU2585988C1 |

| УСТРОЙСТВО ПРОГРАММНО-АППАРАТНОГО КОМПЛЕКСА ФОРМИРОВАНИЯ КЛЮЧЕВОЙ ИНФОРМАЦИИ И РАДИОДАННЫХ ДЛЯ РАДИОСТАНЦИИ | 2016 |

|

RU2636092C1 |

| РЕШЕНИЕ ЗАДАЧИ ПРОПУСКА ПРОЦЕДУРЫ АУТЕНТИФИКАЦИИ ВО ВРЕМЯ ПЕРЕХОДА К СЕТИ С КОММУТАЦИЕЙ КАНАЛОВ (CSFB) ДЛЯ СОКРАЩЕНИЯ ВРЕМЕНИ УСТАНОВЛЕНИЯ ВЫЗОВА | 2015 |

|

RU2644386C1 |

| СИСТЕМА НА КРИСТАЛЛЕ ДЛЯ ВЫПОЛНЕНИЯ БЕЗОПАСНОЙ ЗАГРУЗКИ, УСТРОЙСТВО ФОРМИРОВАНИЯ ИЗОБРАЖЕНИЙ, ИСПОЛЬЗУЮЩЕЕ ЕЕ, И СПОСОБ ДЛЯ НЕГО | 2013 |

|

RU2651213C2 |

| Программируемый логический контроллер для управления устройствами реального времени | 2024 |

|

RU2825561C1 |

| УСТРОЙСТВО ЗАЩИТЫ ИНФОРМАЦИИ ОТ НЕСАНКЦИОНИРОВАННОГО ДОСТУПА ДЛЯ КОМПЬЮТЕРОВ ИНФОРМАЦИОННО-ВЫЧИСЛИТЕЛЬНЫХ СИСТЕМ | 2006 |

|

RU2321055C2 |

| Система и способ управления устройствами реального времени | 2024 |

|

RU2828598C1 |

| СИСТЕМА НА КРИСТАЛЛЕ ДЛЯ ВЫПОЛНЕНИЯ БЕЗОПАСНОЙ НАЧАЛЬНОЙ ЗАГРУЗКИ, ИСПОЛЬЗУЮЩЕЕ ЕЕ УСТРОЙСТВО ФОРМИРОВАНИЯ ИЗОБРАЖЕНИЯ И СПОСОБ ЕЕ ИСПОЛЬЗОВАНИЯ | 2013 |

|

RU2628325C2 |

| МЕХАНИЗМ ВЗАИМОАУТЕНТИФИКАЦИИ В РАСПРЕДЕЛЕННЫХ ИНФОРМАЦИОННО-УПРАВЛЯЮЩИХ СИСТЕМАХ РЕАЛЬНОГО ВРЕМЕНИ | 2000 |

|

RU2178913C1 |

| АДРЕСАЦИЯ ДОВЕРЕННОЙ СРЕДЫ ИСПОЛНЕНИЯ С ИСПОЛЬЗОВАНИЕМ КЛЮЧА ПОДПИСИ | 2017 |

|

RU2756040C2 |

Изобретение относится к области шифрования данных. Техническим результатом является обеспечение строгой аутентификации между абонентами в процедуре шифрования. Раскрыто устройство симметричного шифрования данных (УСШД), реализующееся в виде системы на кристалле (СнК), включающее в себя центральный процессор, блок внутренней коммутации, контроллер внешнего интерфейса, блок мультиплексирования и устройство шифрования, в состав которого входят: контроллер прямого доступа к памяти, вычислительный модуль, генератор псевдослучайных чисел, таймер, регистр общего назначения для хранения таблицы замен (РОН ТЗ), регистр общего назначения для хранения секретных ключей шифрования (РОН КШ), дополнительный РОН КШ и блок управления; при этом центральный процессор связан шиной данных (ШД) с блоком внутренней коммутации, а также конфигурационным интерфейсом с контроллером прямого доступа к памяти и блоком управления; блок внутренней коммутации связан шинами данных с контроллером прямого доступа к памяти, а также шинами данных с контроллером доступа к памяти и контроллером внешнего интерфейса; контроллер доступа к памяти связан с памятью, а контроллер внешнего интерфейса через мультиплексируемую шину данных связан с блоком мультиплексирования, который также принимает сигналы от блока управления через шину управления блоком мультиплексирования и имеет мультиплексированные шины внешнего интерфейса, поступающие на выход СнК; вычислительный модуль взаимосвязан с РОН ТЗ, РОН КШ и дополнительным РОН КШ, блоком управления и принимает сигналы от контроллера прямого доступа к памяти через ЩД и генератора псевдослучайных чисел; блок управления посылает сигналы в РОН ТЗ, РОН КШ и дополнительный РОН КШ через ШД в контроллер прямого доступа к памяти и взаимосвязан с таймером. 2 н. и 1 з.п. ф-лы, 6 ил.

1. Устройство симметричного шифрования данных (УСШД), реализующееся в виде системы на кристалле (СнК), включающее в себя центральный процессор (2), блок внутренней коммутации (3), контроллер внешнего интерфейса (22), блок мультиплексирования (23) и устройство шифрования (7), в состав которого входят: контроллер прямого доступа к памяти (4), вычислительный модуль (8), генератор псевдослучайных чисел (15), таймер (16), регистр общего назначения для хранения таблицы замен (РОН ТЗ) (17), регистр общего назначения для хранения секретных ключей шифрования (РОН КШ) (18), дополнительный РОН КШ (19) и блок управления (21); при этом центральный процессор (2) связан шиной данных (ШД) (9) с блоком внутренней коммутации (3), а также конфигурационным интерфейсом (10) с контроллером прямого доступа к памяти (4) и блоком управления; блок внутренней коммутации (3) связан шинами данных (11), (12) с контроллером прямого доступа к памяти (4), а также шинами данных (20), (24) с контроллером доступа к памяти (5) и контроллером внешнего интерфейса (22); контроллер доступа к памяти (5) связан с памятью (6), а контроллер внешнего интерфейса (22) через мультиплексируемую шину данных (25) связан с блоком мультиплексирования (23), который также принимает сигналы от блока управления (21) через шину управления блоком мультиплексирования (26) и имеет мультиплексированные шины внешнего интерфейса (28.1…28.М), поступающие на выход СнК (1); вычислительный модуль (8) взаимосвязан с РОН ТЗ (17), РОН КШ (18) и дополнительным РОН КШ (19), блоком управления (21) и принимает сигналы от контроллера прямого доступа к памяти через ЩД (13) и генератора псевдослучайных чисел (15); блок управления (21) посылает сигналы в РОН ТЗ (17), РОН КШ (18) и дополнительный РОН КШ (19) через ШД (14) в контроллер прямого доступа к памяти (4) и взаимосвязан с таймером (16); устройство шифрования (7) работает в режиме простой замены, данные для передачи/приема по внешнему интерфейсу хранятся в памяти (6) и поступают из нее в устройство шифрования и в обратную сторону блоками по 64 бит каждый, таким образом память (6) играет роль буфера данных внешнего интерфейса; данные для шифрования и результаты шифрования передаются между блоком внутренней коммутации (3), контроллером прямого доступа к памяти (4) и вычислительным модулем (8) по внутренним шинам пакетами, состоящими из кадров, равными по размеру блоку обрабатываемых данных; блок внутренней коммутации (3) передает данные на контроллер прямого доступа к памяти (4) и принимает их из него; вычислительный модуль (8), используется для реализации базового цикла шифрования; при этом устройство шифрования (7) выполняет процедуру шифрования, расшифрования данных в процессе аутентификации, генератор псевдослучайных чисел (15) создает неповторяющийся маркер сообщения, который является случайным числом, таймер (16) ограничивает время ожидания при выполнении процедуры зашифрования/расшифрования данных, внешнее или внутреннее по отношению к устройству шифрования (7) запоминающее устройство (6) является буфером для хранения в зашифрованном виде передаваемых по каналу данных, контроллер внешнего интерфейса (22) организует интерфейс передачи данных для обмена с внешними устройствами, блок мультиплексирования шин (23) внешнего интерфейса передачи данных осуществляет коммутацию последовательной шины (25) на несколько мультиплексированных последовательных шин передачи данных (28.1), (28.2), …, (28.М); вычислительный модуль (8) осуществляет алгоритм криптографического преобразования ГОСТ 28147-89 в режиме простой замены и формирование зашифрованных пакетов данных для аутентификации, в РОН ТЗ (17) загружается таблица замен, блок управления (21) обеспечивает синхронизацию работы блоков устройства шифрования (7), а также выбор текущей шины для отправки зашифрованного сообщения строгой аутентификации; при этом в системе управления, содержащей устройства симметричного шифрования данных, реализованные на СнК (1) и выступающие в виде управляющих устройств, и блоки контроля и управления (БКУ), в качестве которых выступают устройства симметричного шифрования данных, реализованные на СнК (1), в роли исполнительных устройств (ИУ), строгая аутентификация осуществляется следующим образом:

1) секретный ключ группы «устройство управления - исполнительные устройства» К0…511 загружается в регистр РОН КШ (18) и дополнительный РОН КШ (19), при этом личный ключ инициатора передачи информации Кл=К0…255 сохраняется в РОН КШ (18), а ключ приемника информации Ко=256…511 - в дополнительном РОН КШ (19);

2) УСШД, реализованное на СнК (1) и выступающее в виде управляющего устройства (УУ) (1.1…1.К), создает неповторяющийся маркер, который является случайным числом, с помощью генератора псевдослучайных чисел (15), запускает таймер (16), отправляет по мультиплексированным шинам (28.1…28.М) сообщение исполнительному устройству, сформированное по следующему закону:

Хл_mast(_sl, Xo_sl(CЧ_mast_N, Данные)),

где Хл_mast(x) - зашифрование информации х с использованием личного ключа инициатора передачи информации, который является управляющим устройством, Кл=К0…255;

Xo_sl(x) - зашифрование информации х с использованием личного ключа приемника информации, который является исполнительным устройством, Ко=К256…511;

_sl - номер приемника информации;

CЧ_mast_N - неповторяющийся маркер, сгенерированный инициатором передачи, необходимый для строгой аутентификации во время обмена;

Данные - данные для передачи;

3) БКУ дешифрует принятые данные с использованием ключа инициатора передачи Кл=К0…255 и ключа приемника информации Ко=К256…511;

процедура аутентификации продолжается только с тем ИУ, номер _sl которого соответствует указанному в сообщении от УУ, и только такое ИУ способно расшифровать CЧ_mast_N и Данные;

4) БКУ создает неповторяющийся маркер, который является случайным числом, запускает таймер (16) БКУ и отправляет ответ, формируя его по формуле:

Xn_sl(_mast, Xo_mast(Ответ, CЧ_mast_N, CЧ_sl_N)),

где Xn_sl(x) - зашифрование информации х с использованием личного ключа инициатора передачи информации Кл=К0…255;

Xo_mast(x) - зашифрование информации х с использованием ключа приемника информации Ко=К256…511;

_mast - номер инициатора передачи информации;

Ответ - код ошибки получения приказа;

CЧ_mast_N - неповторяющийся маркер, полученный от инициатора передачи;

CЧ_sl_N - неповторяющийся маркер, сгенерированный получателем информации (БКУ) и необходимый для строгой аутентификации во время обмена;

5) УУ (1.1…1.К) дешифрует принятое сообщение с использованием личного ключа инициатора передачи Кл=К0…255 и далее с использованием ключа приемника информации, сравнивая при этом полученный маркер CЧ_mast_N с созданным, при их совпадении процедура аутентификации продолжается по пункту 6), иначе действия несанкционированные, процедура аутентификации прерывается;

6) УУ (1) отправляет по каналу связи подтверждение, сформированное следующим образом:

Хл_mast (_sl, CЧ_sl_N);

7) БКУ дешифрует принятые данные с использованием личного ключа инициатора передачи Кл=К0…255, сравнивает полученный маркер CЧ_sl_N с созданным и при их совпадении осуществляет разрешенные действия с данными, полученными в пункте 3);

при этом команды и данные, генерируемые устройством управления, поступают из внутренних регистров процессора (2) по шинам в вычислительный модуль (8), где происходит формирование сообщений в описанном выше формате, их шифрование по алгоритму ГОСТ 28147-89 в режиме простой замены; зашифрованные сообщения поступают по шинам в память (6), откуда посредством контроллера внешнего интерфейса (22) передаются по одному из каналов передачи данных в БКУ (2.1…2.М) в зависимости от необходимого приемника информации, указанного в сообщении; при этом центральный процессор (2) генерирует сигналы управления блоком внутренней коммутации (3), контроллером прямого доступа к памяти (4), а также блоком управления (21) устройства шифрования (7) по конфигурационному интерфейсу (10), определяющие направление передачи: в устройство шифрования (7), из устройства шифрования (7) в память (6); блок управления (21) устройства шифрования (7) осуществляет выставку сигналов на запуск таймера (16), начало цикла шифрования/расшифрования, извлечение случайного числа из генератора псевдослучайных чисел (15), сброс схемы в начальное состояние в случае поступления от таймера (16) сигнала переполнения при длительном ожидании ответного сообщения, а также выставляет сигнал выбора текущей шины передачи данных по конфигурационному интерфейсу (26); ответное входящее сообщение, поступающее по внешней шине посредством контроллера внешнего интерфейса (22) в память (6), передается в устройство шифрования (7), где происходит расшифрование сообщения по алгоритму ГОСТ 28147-89, формирование ответного сообщения при совпадении случайного числа, его зашифрование и отправка по каналу связи.

2. Устройство по п. 1, отличающееся тем, что включает в себя общую шину данных внешнего интерфейса (27) на выходе контроллера внешнего интерфейса (22); при этом УСШД, выступающее в виде управляющего устройства (1.1…1.К), дополнительно отправляет по общей шине данных внешнего интерфейса (27) сообщение исполнительному устройству (2.1…2.N).

3. Устройство симметричного шифрования данных (УСШД), реализующееся в виде системы на кристалле (СнК), включающее в себя центральный процессор (2), блок внутренней коммутации (3), контроллер внешнего интерфейса (22) и устройство шифрования (7), в состав которого входят: контроллер прямого доступа к памяти (4), вычислительный модуль (8), генератор псевдослучайных чисел (15), таймер (16), регистр общего назначения для хранения таблицы замен (РОН ТЗ) (17), регистр общего назначения для хранения секретных ключей шифрования (РОН КШ) (18), дополнительный РОН КШ (19) и блок управления (21); при этом центральный процессор (2) связан шиной данных (ШД) (9) с блоком внутренней коммутации (3), а также конфигурационным интерфейсом (10) с контроллером прямого доступа к памяти (4) и блоком управления; блок внутренней коммутации (3) связан шинами данных (11), (12) с контроллером прямого доступа к памяти (4), а также шинами данных (20), (24) с контроллером доступа к памяти (5) и контроллером внешнего интерфейса (22); контроллер доступа к памяти (5) связан с памятью (6), а из контроллера внешнего интерфейса (22) на выход СнК (1) поступает общая шина данных внешнего интерфейса (7); вычислительный модуль (8) взаимосвязан с РОН ТЗ (17), РОН КШ (18) и дополнительным РОН КШ (19), блоком управления (21) и принимает сигналы от контроллера прямого доступа к памяти через НТД (13) и генератора псевдослучайных чисел (15); блок управления (21) посылает сигналы в РОН ТЗ (17), РОН КШ (18) и дополнительный РОН КШ (19) через ШД (14) в контроллер прямого доступа к памяти (4) и взаимосвязан с таймером (16); устройство шифрования (7) работает в режиме простой замены, данные для передачи/приема по внешнему интерфейсу хранятся в памяти (6) и поступают из нее в устройство шифрования и в обратную сторону блоками по 64 бит каждый, таким образом память (6) играет роль буфера данных внешнего интерфейса; данные для шифрования и результаты шифрования передаются между блоком внутренней коммутации (3), контроллером прямого доступа к памяти (4) и вычислительным модулем (8) по внутренним шинам пакетами, состоящими из кадров, равными по размеру блоку обрабатываемых данных; блок внутренней коммутации (3) передает данные на контроллер прямого доступа к памяти (4) и принимает их из него; вычислительный модуль (8), используется для реализации базового цикла шифрования; при этом устройство шифрования (7) выполняет процедуру шифрования, расшифрования данных в процессе аутентификации, генератор псевдослучайных чисел (15) создает неповторяющийся маркер сообщения, который является случайным числом, таймер (16) ограничивает время ожидания при выполнении процедуры зашифрования/расшифрования данных, внешнее или внутреннее по отношению к устройству шифрования (7) запоминающее устройство (6) является буфером для хранения в зашифрованном виде передаваемых по каналу данных, контроллер внешнего интерфейса (22) организует интерфейс передачи данных для обмена с внешними устройствами по общей шине данных внешнего интерфейса (27); вычислительный модуль (8) осуществляет алгоритм криптографического преобразования ГОСТ 28147-89 в режиме простой замены и формирование зашифрованных пакетов данных для аутентификации, в РОН ТЗ (17) загружается таблица замен, блок управления (21) обеспечивает синхронизацию работы блоков устройства шифрования (7), а также выбор текущей шины для отправки зашифрованного сообщения строгой аутентификации; при этом в системе управления, содержащей устройства симметричного шифрования данных, реализованные на СнК (1) и выступающие в виде управляющих устройств, и блоки контроля и управления (БКУ), в качестве которых выступают устройства симметричного шифрования данных, реализованные на СнК (1), в роли исполнительных устройств (ИУ), строгая аутентификация осуществляется следующим образом:

1) секретный ключ группы «устройство управления - исполнительные устройства» К0…511 загружается в регистр РОН КШ (18) и дополнительный РОН КШ (19), при этом личный ключ инициатора передачи информации Кл=К0…255 сохраняется в РОН КШ (18), а ключ приемника информации Ко=256…511 - в дополнительном РОН КШ (19);

2) УСШД, реализованное на СнК (1) и выступающее в виде управляющего устройства (УУ) (1.1…1.К), создает неповторяющийся маркер, который является случайным числом, с помощью генератора псевдослучайных чисел (15), запускает таймер (16), отправляет по общей шине данных внешнего интерфейса (27) сообщение исполнительному устройству, сформированное по следующему закону:

Хл_mast(_sl, Xo_sl(CЧ_mast_N, Данные)),

где Хл_mast(x) - зашифрование информации х с использованием личного ключа инициатора передачи информации, который является управляющим устройством, Кл=К0…255;

Xo_sl(x) - зашифрование информации х с использованием личного ключа приемника информации, который является исполнительным устройством, Ко=К256…511;

_sl - номер приемника информации;

CЧ_mast_N - неповторяющийся маркер, сгенерированный инициатором передачи, необходимый для строгой аутентификации во время обмена;

Данные - данные для передачи;

3) БКУ дешифрует принятые данные с использованием ключа инициатора передачи Кл=К0…255 и ключа приемника информации Ко=К256…511;

процедура аутентификации продолжается только с тем ИУ, номер _sl которого соответствует указанному в сообщении от УУ, и только такое ИУ способно расшифровать СЧ_mast_N и Данные;

4) БКУ создает неповторяющийся маркер, который является случайным числом, запускает таймер (16) БКУ и отправляет ответ, формируя его по формуле:

Хл_sl(_mast, Xo_mast (Ответ, CЧ_mast_N, CЧ_sl_N)),

где Хл_sl(x) - зашифрование информации х с использованием личного ключа инициатора передачи информации Кл=К0…255;

Xo_mast(x) - зашифрование информации х с использованием ключа приемника информации Ко=К256…511;

_mast - номер инициатора передачи информации;

Ответ - код ошибки получения приказа;

CЧ_mast_N - неповторяющийся маркер, полученный от инициатора передачи;

CЧ_sl_N - неповторяющийся маркер, сгенерированный получателем информации (БКУ) и необходимый для строгой аутентификации во время обмена;

5) УУ (1.1…1.К) дешифрует принятое сообщение с использованием личного ключа инициатора передачи Кл=К0…255 и далее с использованием ключа приемника информации, сравнивая при этом полученный маркер CЧ_mast_N с созданным, при их совпадении процедура аутентификации продолжается по пункту 6), иначе действия несанкционированные, процедура аутентификации прерывается;

6) УУ (1) отправляет по каналу связи подтверждение, сформированное следующим образом:

Хл_mast (_sl, CЧ_sl_N);

7) БКУ дешифрует принятые данные с использованием личного ключа инициатора передачи Кл=К0…255, сравнивает полученный маркер CЧ_sl_N с созданным и при их совпадении осуществляет разрешенные действия с данными, полученными в пункте 3);

при этом команды и данные, генерируемые устройством управления, поступают из внутренних регистров процессора (2) по шинам в вычислительный модуль (8), где происходит формирование сообщений в описанном выше формате, их шифрование по алгоритму ГОСТ 28147-89 в режиме простой замены; зашифрованные сообщения поступают по шинам в память (6), откуда посредством контроллера внешнего интерфейса (22) передаются по общей шине данных внешнего интерфейса в БКУ (2.1…2.N) в зависимости от необходимого приемника информации, указанного в сообщении; при этом центральный процессор (2) генерирует сигналы управления блоком внутренней коммутации (3), контроллером прямого доступа к памяти (4), а также блоком управления (21) устройства шифрования (7) по конфигурационному интерфейсу (10), определяющие направление передачи: в устройство шифрования (7), из устройства шифрования (7) в память (6); блок управления (21) устройства шифрования (7) осуществляет выставку сигналов на запуск таймера (16), начало цикла шифрования/расшифрования, извлечение случайного числа из генератора псевдослучайных чисел (15), сброс схемы в начальное состояние в случае поступления от таймера (16) сигнала переполнения при длительном ожидании ответного сообщения; ответное входящее сообщение, поступающее по внешней шине посредством контроллера внешнего интерфейса (22) в память (6), передается в устройство шифрования (7), где происходит расшифрование сообщения по алгоритму ГОСТ 28147-89, формирование ответного сообщения при совпадении случайного числа, его зашифрование и отправка по каналу связи.

| УСТРОЙСТВО ШИФРОВАНИЯ ДАННЫХ (ВАРИАНТЫ), СИСТЕМА НА КРИСТАЛЛЕ С ЕГО ИСПОЛЬЗОВАНИЕМ (ВАРИАНТЫ) | 2015 |

|

RU2585988C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ВЗАИМНОЙ АУТЕНТИФИКАЦИИ | 2007 |

|

RU2420896C2 |

| US 5878142 A, 02.03.1999 | |||

| US 6028937 A, 22.02.2000. | |||

Авторы

Даты

2022-01-28—Публикация

2020-05-14—Подача