Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны устройства сравнения двоичных чисел (см., например, рис. 4.18 на стр. 163 в книге Бибило П.Н. Основы языка VHDL. М.: Солон-Р, 2000 г. ), выполняющие распознавание отношений А≥В, А<В, где А, В есть четырехразрядные двоичные числа, задаваемые двоичными сигналами.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных устройств сравнения двоичных чисел, относятся ограниченные функциональные возможности, обусловленные тем, что не выполняется распознавание отношений А>В и А=В.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятое за прототип устройство сравнения двоичных чисел (патент РФ 2677371, кл. G06F 7/02, 2019 г.), которое содержит элементы 2ИЛИ, элементы 2И, четыре элемента НЕ, шесть мажоритарных элементов и выполняет распознавание отношений А>В, А=В, А<В, где А, В есть четырехразрядные двоичные числа, задаваемые двоичными сигналами.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относятся большие аппаратурные затраты, обусловленные тем, что прототип содержит четыре элемента 2ИЛИ и четыре элемента 2И.

Техническим результатом изобретения является уменьшение аппаратурных затрат при сохранении функциональных возможностей прототипа.

Указанный технический результат при осуществлении изобретения достигается тем, что в устройстве сравнения двоичных чисел, содержащем два элемента 2ИЛИ, два элемента 2И, четыре элемента НЕ и шесть мажоритарных элементов, первый, второй входы k-го  элемента 2ИЛИ и второй, третий входы j-го

элемента 2ИЛИ и второй, третий входы j-го  мажоритарного элемента соединены соответственно с первым, вторым входами k-го элемента 2И и первым, вторым входами (j+3)-го мажоритарного элемента, а второй вход k-го элемента 2ИЛИ и выходы третьего, шестого мажоритарных элементов подключены соответственно к выходу k-го элемента НЕ и первому, второму выходам устройства сравнения двоичных чисел, особенность заключается в том, что первый вход k-го мажоритарного элемента, подключенного третьим входом к выходу (k+2)-го элемента НЕ, и выход k-го элемента 2И соединены соответственно с выходом k-го элемента 2ИЛИ и третьим входом (k+3)-го мажоритарного элемента, первый, второй входы третьего и второй, третий входы шестого мажоритарных элементов соединены соответственно с выходами второго, первого и выходами четвертого, пятого мажоритарных элементов, а второй вход k-го мажоритарного элемента, вход (k+2)-го элемента НЕ и первый вход k-го элемента 2ИЛИ, вход k-го элемента НЕ подключены соответственно к (2×k-1)-му, (2×k+3)-му и (2×k)-му, (2×k+4)-му входам устройства сравнения двоичных чисел.

мажоритарного элемента соединены соответственно с первым, вторым входами k-го элемента 2И и первым, вторым входами (j+3)-го мажоритарного элемента, а второй вход k-го элемента 2ИЛИ и выходы третьего, шестого мажоритарных элементов подключены соответственно к выходу k-го элемента НЕ и первому, второму выходам устройства сравнения двоичных чисел, особенность заключается в том, что первый вход k-го мажоритарного элемента, подключенного третьим входом к выходу (k+2)-го элемента НЕ, и выход k-го элемента 2И соединены соответственно с выходом k-го элемента 2ИЛИ и третьим входом (k+3)-го мажоритарного элемента, первый, второй входы третьего и второй, третий входы шестого мажоритарных элементов соединены соответственно с выходами второго, первого и выходами четвертого, пятого мажоритарных элементов, а второй вход k-го мажоритарного элемента, вход (k+2)-го элемента НЕ и первый вход k-го элемента 2ИЛИ, вход k-го элемента НЕ подключены соответственно к (2×k-1)-му, (2×k+3)-му и (2×k)-му, (2×k+4)-му входам устройства сравнения двоичных чисел.

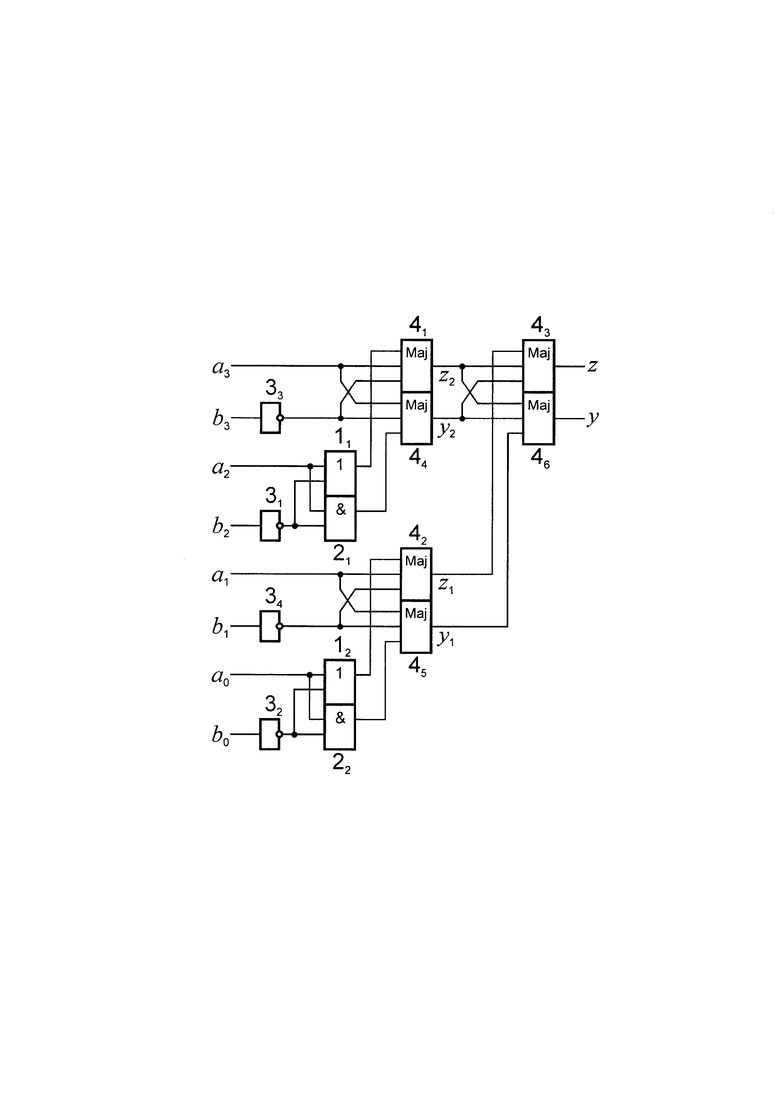

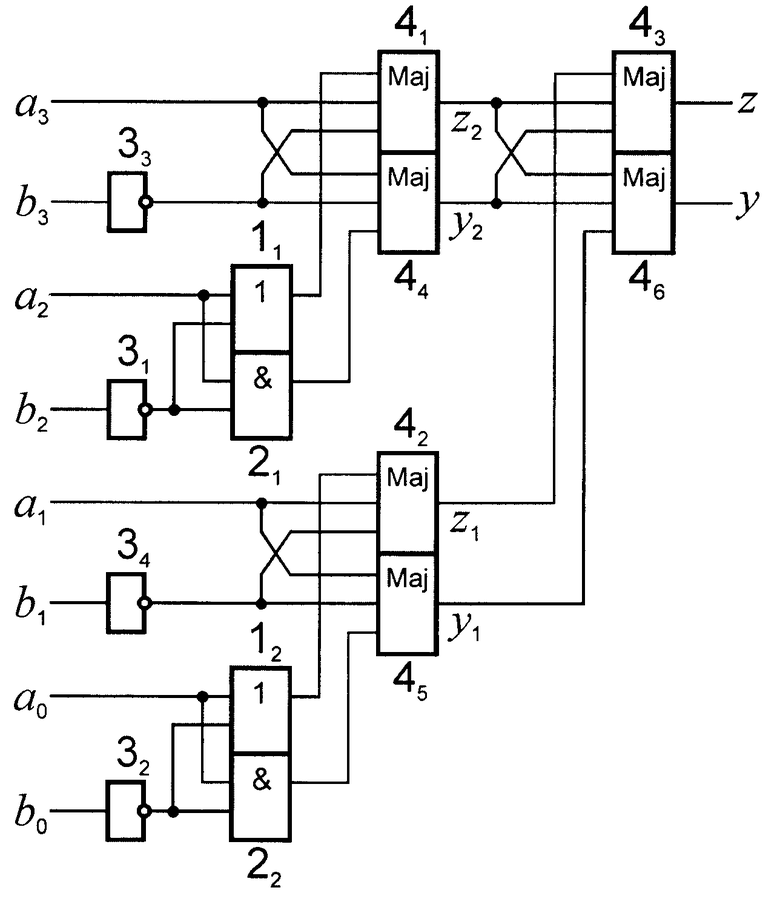

На чертеже представлена схема предлагаемого устройства сравнения двоичных чисел.

Устройство сравнения двоичных чисел содержит элементы 2ИЛИ 11, 1,2, элементы 2И 21, 22, элементы НЕ 31,…,34 и мажоритарные элементы 41,…,46, причем первый, второй входы элемента 1k  и второй, третий входы элемента 4j

и второй, третий входы элемента 4j  соединены соответственно с первым, вторым входами элемента 2k и первым, вторым входами элемента 4j+3, второй вход элемента 2k, третий вход элемента 4k+3 и первый, третий входы элемента 4k подключены соответственно к выходам элементов 3k, 2k и 1k, 3k+2, первый, второй входы элемента 43 и второй, третий входы элемента 46 соединены соответственно с выходами элементов 42, 41 и 44, 45, а второй вход элемента 4k, вход элемента 3k+2 и первый вход элемента 1k, вход элемента 3k подключены соответственно к (2×k-1)-му, (2×k+3)-му и (2×k)-му, (2×k+4)-му входам устройства сравнения двоичных чисел, первый и второй выходы которого соединены соответственно с выходами элементов 43 и 46.

соединены соответственно с первым, вторым входами элемента 2k и первым, вторым входами элемента 4j+3, второй вход элемента 2k, третий вход элемента 4k+3 и первый, третий входы элемента 4k подключены соответственно к выходам элементов 3k, 2k и 1k, 3k+2, первый, второй входы элемента 43 и второй, третий входы элемента 46 соединены соответственно с выходами элементов 42, 41 и 44, 45, а второй вход элемента 4k, вход элемента 3k+2 и первый вход элемента 1k, вход элемента 3k подключены соответственно к (2×k-1)-му, (2×k+3)-му и (2×k)-му, (2×k+4)-му входам устройства сравнения двоичных чисел, первый и второй выходы которого соединены соответственно с выходами элементов 43 и 46.

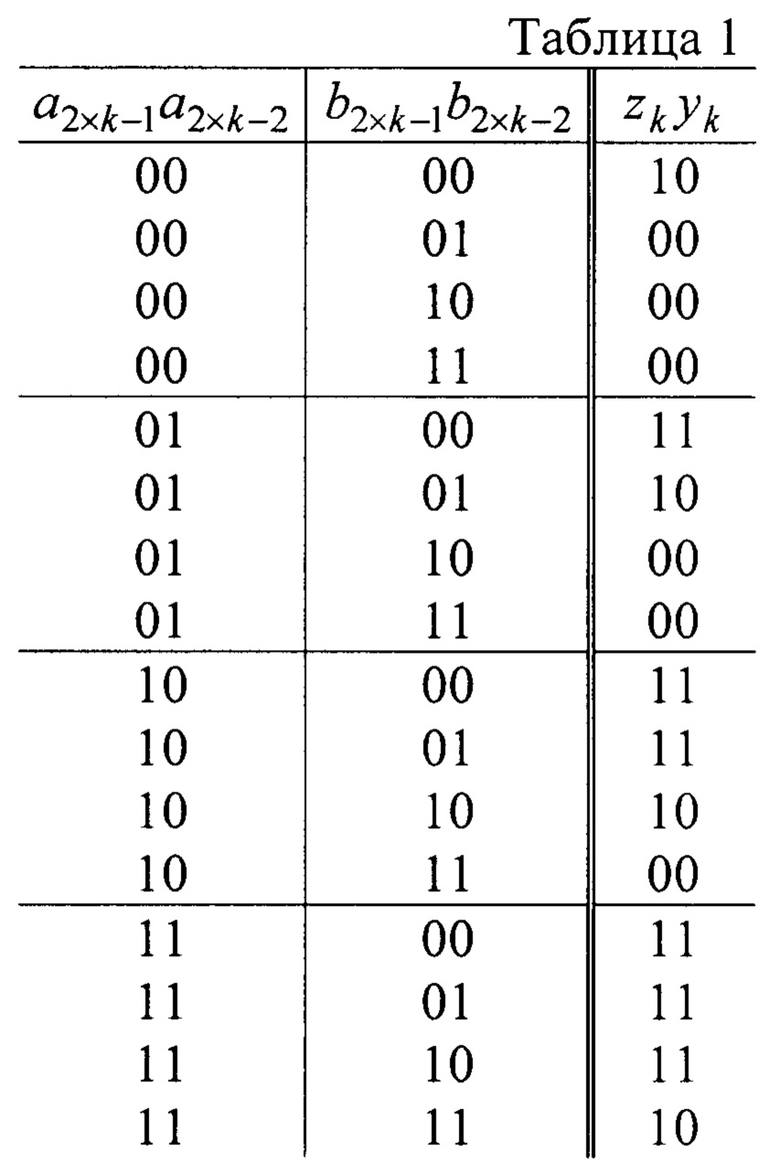

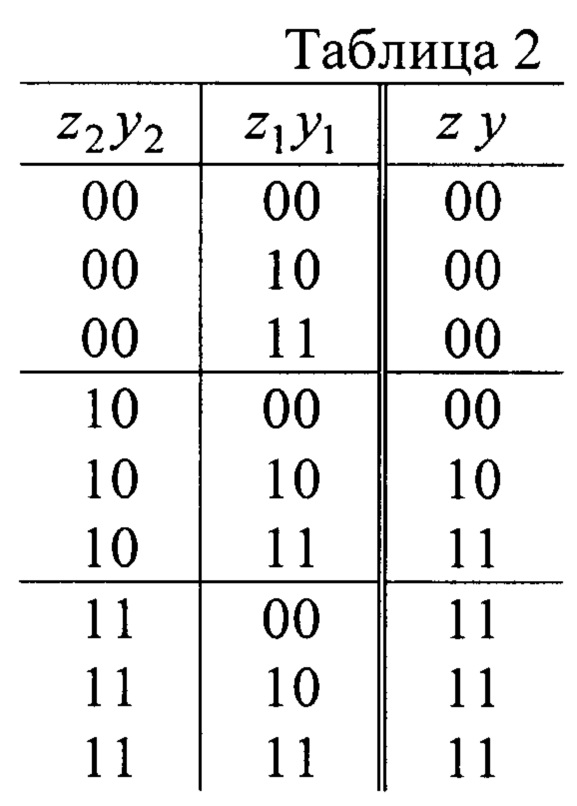

Работа предлагаемого устройства сравнения двоичных чисел осуществляется следующим образом. На его первый, …, четвертый и пятый, …, восьмой входы подаются соответственно произвольные двоичные сигналы а3, …, а0 ∈ {0,1} и b3, …, b0 ∈ {0,1}, которые задают подлежащие сравнению четырехразрядные двоичные числа А=а3а2а1a0, B=b3b2b1b0 (а3, b3 определяют значения старших, а а0, b0 - младших разрядов). В представленных ниже табл. 1 и табл. 2 приведены соответственно значения внутренних сигналов zk  ук предлагаемого устройства, полученные для всех возможных наборов значений сигналов a2×k-1, a2×k-2, b2×k-1, b2×k-2, и значения его выходных сигналов z, у, полученные для всех возможных наборов значений сигналов z1, y1, z2, y2.

ук предлагаемого устройства, полученные для всех возможных наборов значений сигналов a2×k-1, a2×k-2, b2×k-1, b2×k-2, и значения его выходных сигналов z, у, полученные для всех возможных наборов значений сигналов z1, y1, z2, y2.

Согласно табл. 1, табл. 2 имеем z=y=1 при А>В, z=1, у=0 при А=В, z=y=0 при А<В.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемое устройство сравнения двоичных чисел выполняет распознавание отношений А>В, А=В, А<В, где А, В есть четырехразрядные двоичные числа, задаваемые двоичными сигналами, и обладает меньшими по сравнению с прототипом аппаратурными затратами.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ | 2023 |

|

RU2809253C1 |

| УСТРОЙСТВО СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ | 2017 |

|

RU2677371C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2023 |

|

RU2805141C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2021 |

|

RU2764709C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2021 |

|

RU2776923C1 |

| МАЖОРИТАЛЬНЫЙ МОДУЛЬ | 2021 |

|

RU2778677C1 |

| ДВОИЧНЫЙ СУММАТОР | 2020 |

|

RU2758184C1 |

| УСТРОЙСТВО СЕЛЕКЦИИ БОЛЬШЕГО ИЗ ДВОИЧНЫХ ЧИСЕЛ | 2017 |

|

RU2676891C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2018 |

|

RU2700552C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2021 |

|

RU2775589C1 |

Изобретение относится к области вычислительной техники. Техническим результатом изобретения является уменьшение аппаратурных затрат при сохранении функциональных возможностей прототипа. Технический результат достигается за счет устройства сравнения двоичных чисел, предназначенного для распознавания отношений А>В, А=В, А<В, где А, В есть четырехразрядные двоичные числа, задаваемые двоичными сигналами, изобретение может быть использовано в системах цифровой вычислительной техники как средство компараторной обработки информации. Устройство содержит два элемента 2ИЛИ (11, 12), два элемента 2И (21, 22), четыре элемента НЕ (31,…, 34) и шесть мажоритарных элементов (41,…, 46). В результате достигнуто уменьшение аппаратурных затрат при сохранении функциональных возможностей прототипа. 1 ил., 2 табл.

Устройство сравнения двоичных чисел, содержащее два элемента 2ИЛИ, два элемента 2И, четыре элемента НЕ и шесть мажоритарных элементов, причем первый, второй входы k-го  элемента 2ИЛИ и второй, третий входы j-го

элемента 2ИЛИ и второй, третий входы j-го  мажоритарного элемента соединены соответственно с первым, вторым входами k-го элемента 2И и первым, вторым входами (j+3)-го мажоритарного элемента, а второй вход k-го элемента 2ИЛИ и выходы третьего, шестого мажоритарных элементов подключены соответственно к выходу k-го элемента НЕ и первому, второму выходам устройства сравнения двоичных чисел, отличающееся тем, что первый вход k-го мажоритарного элемента, подключенного третьим входом к выходу (k+2)-го элемента НЕ, и выход k-го элемента 2И соединены соответственно с выходом k-го элемента 2ИЛИ и третьим входом (k+3)-го мажоритарного элемента, первый, второй входы третьего и второй, третий входы шестого мажоритарных элементов соединены соответственно с выходами второго, первого и выходами четвертого, пятого мажоритарных элементов, а второй вход k-го мажоритарного элемента, вход (k+2)-го элемента НЕ и первый вход k-го элемента 2ИЛИ, вход k-го элемента НЕ подключены соответственно к (2×k-1)-му, (2×k+3)-му и (2×k)-му, (2×k+4)-му входам устройства сравнения двоичных чисел.

мажоритарного элемента соединены соответственно с первым, вторым входами k-го элемента 2И и первым, вторым входами (j+3)-го мажоритарного элемента, а второй вход k-го элемента 2ИЛИ и выходы третьего, шестого мажоритарных элементов подключены соответственно к выходу k-го элемента НЕ и первому, второму выходам устройства сравнения двоичных чисел, отличающееся тем, что первый вход k-го мажоритарного элемента, подключенного третьим входом к выходу (k+2)-го элемента НЕ, и выход k-го элемента 2И соединены соответственно с выходом k-го элемента 2ИЛИ и третьим входом (k+3)-го мажоритарного элемента, первый, второй входы третьего и второй, третий входы шестого мажоритарных элементов соединены соответственно с выходами второго, первого и выходами четвертого, пятого мажоритарных элементов, а второй вход k-го мажоритарного элемента, вход (k+2)-го элемента НЕ и первый вход k-го элемента 2ИЛИ, вход k-го элемента НЕ подключены соответственно к (2×k-1)-му, (2×k+3)-му и (2×k)-му, (2×k+4)-му входам устройства сравнения двоичных чисел.

| УСТРОЙСТВО СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ | 2017 |

|

RU2677371C1 |

| УСТРОЙСТВО СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ | 2009 |

|

RU2420789C1 |

| US 20040039770 A1, 26.02.2004 | |||

| УСТРОЙСТВО СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ | 2005 |

|

RU2298220C1 |

Авторы

Даты

2022-04-15—Публикация

2021-04-02—Подача