Изобретение относится к вычислительной технике и может быть использовано при построении средств автоматики, функциональных узлов систем управления и др.

Известны мажоритарные модули (см., например, патент РФ 2700552, кл. G06F 7/57, 2019 г.), которые содержат элементы «2И», элементы «2ИЛИ» и реализуют мажоритарную функцию семи аргументов - входных двоичных сигналов.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных мажоритарных модулей, относятся ограниченные функциональные возможности, обусловленные тем, что не обеспечивается реализация мажоритарной функции девяти аргументов - входных двоичных сигналов.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип мажоритарный модуль (патент РФ 2665226, кл. G06F7/57, 2018 г.), который содержит элементы «2И», элементы «2ИЛИ» и реализует мажоритарную функцию девяти аргументов - входных двоичных сигналов.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относятся большие аппаратурные затраты, обусловленные тем, что прототип содержит 21 элемент «2ИЛИ» и 22 элемента «2И».

Техническим результатом изобретения является уменьшение аппаратурных затрат при сохранении функциональных возможностей прототипа.

Указанный технический результат при осуществлении изобретения достигается тем, что в мажоритарном модуле, содержащем семнадцать элементов «2ИЛИ» и семнадцать элементов «2И», особенность заключается в том, что первый, второй входы семнадцатого и первый, второй входы i-го  элементов «2И» соединены соответственно с выходами тринадцатого, семнадцатого и первым, вторым входами i-го элементов «2ИЛИ», первый, второй входы k-го

элементов «2И» соединены соответственно с выходами тринадцатого, семнадцатого и первым, вторым входами i-го элементов «2ИЛИ», первый, второй входы k-го  и первый, второй входы (k+6)-то элементов «2ИЛИ» подключены соответственно к выходам (k+2)-го, (k+4)-го элементов «2ИЛИ» и выходам (k+2)-го, (k+4)-го элементов «2И», первый, второй входы четырнадцатого и первый вход (k+8)-го элементов «2ИЛИ» соединены соответственно с выходами седьмого, восьмого и выходом k-го элементов «2И», первый, второй входы четырнадцатого и второй вход (k+8)-го элементов «2И» подключены соответственно к выходам первого, второго и выходу (k+6)-го элементов «2ИЛИ», первый, второй входы одиннадцатого и первый, второй входы двенадцатого элементов «2ИЛИ» соединены соответственно с выходами девятого, десятого элементов «2ИЛИ» и выходами девятого, десятого элементов «2И», первый вход (k+14)-го элемента «2И» и выход (k+10)-го элемента «2ИЛИ» подключены соответственно к выходу (k+13)-го и второму входу (k+14)-го элементов «2И», второй вход (k+14)-го элемента «2ИЛИ» и выход (13-k)-го элемента «2И» соединены соответственно с выходом (k+13)-го и первым входом (k+14)-го элементов «2ИЛИ», первый, второй входы тринадцатого и первый вход семнадцатого элементов «2ИЛИ» подключены соответственно к выходам шестнадцатых элементов «2И», «2ИЛИ» и выходу тринадцатого элемента «2И», а первый, второй входы (k+2)-го, первый, второй входы (k+4)-го и второй вход семнадцатого элементов «2ИЛИ» подключены соответственно к (4×k-3)-му, (4×k-2)-му, (4×k-1)-му, (4×k)-му и девятому входам мажоритарного модуля, выходом которого является выход семнадцатого элемента «2И».

и первый, второй входы (k+6)-то элементов «2ИЛИ» подключены соответственно к выходам (k+2)-го, (k+4)-го элементов «2ИЛИ» и выходам (k+2)-го, (k+4)-го элементов «2И», первый, второй входы четырнадцатого и первый вход (k+8)-го элементов «2ИЛИ» соединены соответственно с выходами седьмого, восьмого и выходом k-го элементов «2И», первый, второй входы четырнадцатого и второй вход (k+8)-го элементов «2И» подключены соответственно к выходам первого, второго и выходу (k+6)-го элементов «2ИЛИ», первый, второй входы одиннадцатого и первый, второй входы двенадцатого элементов «2ИЛИ» соединены соответственно с выходами девятого, десятого элементов «2ИЛИ» и выходами девятого, десятого элементов «2И», первый вход (k+14)-го элемента «2И» и выход (k+10)-го элемента «2ИЛИ» подключены соответственно к выходу (k+13)-го и второму входу (k+14)-го элементов «2И», второй вход (k+14)-го элемента «2ИЛИ» и выход (13-k)-го элемента «2И» соединены соответственно с выходом (k+13)-го и первым входом (k+14)-го элементов «2ИЛИ», первый, второй входы тринадцатого и первый вход семнадцатого элементов «2ИЛИ» подключены соответственно к выходам шестнадцатых элементов «2И», «2ИЛИ» и выходу тринадцатого элемента «2И», а первый, второй входы (k+2)-го, первый, второй входы (k+4)-го и второй вход семнадцатого элементов «2ИЛИ» подключены соответственно к (4×k-3)-му, (4×k-2)-му, (4×k-1)-му, (4×k)-му и девятому входам мажоритарного модуля, выходом которого является выход семнадцатого элемента «2И».

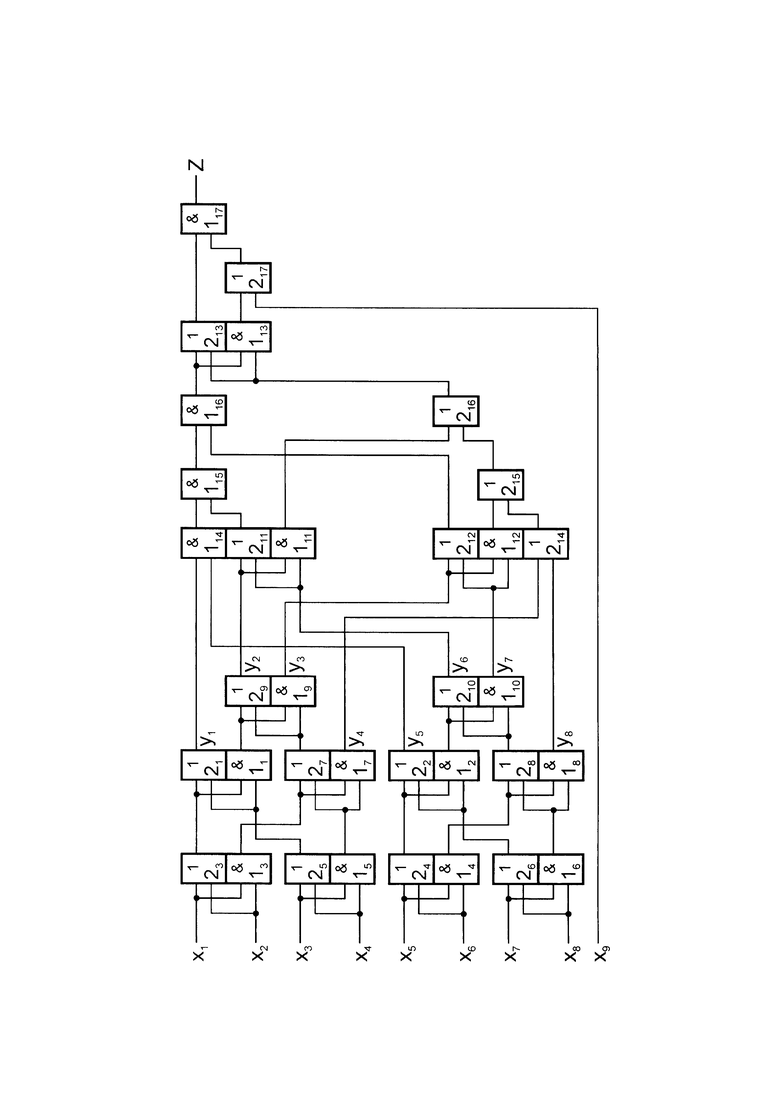

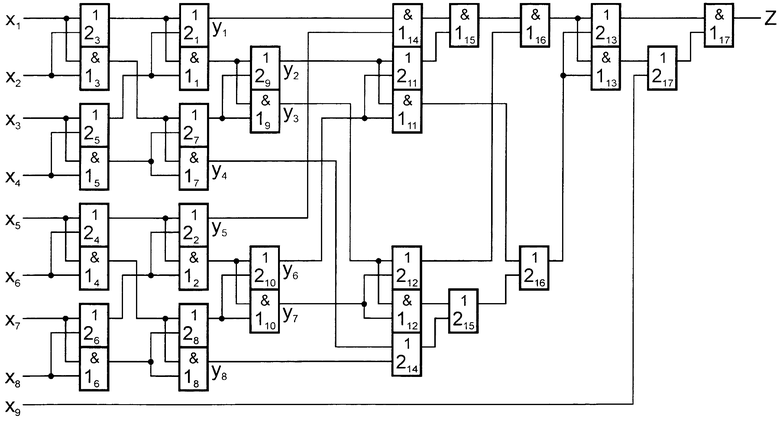

На чертеже представлена схема предлагаемого мажоритарного модуля.

Мажоритарный модуль содержит элементы «2И» 11, …, 117 и элементы «2ИЛИ» 21, …, 117, причем первый, второй входы элемента 117 и первый, второй входы элемента 1i,  соединены соответственно с выходами элементов 213, 217 и первым, вторым входами элемента 2i первый, второй входы элемента 2k

соединены соответственно с выходами элементов 213, 217 и первым, вторым входами элемента 2i первый, второй входы элемента 2k  и первый, второй входы элемента 2k+6 подключены соответственно к выходам элементов 2k+2, 2k+4 и 1k+2, 1k+4, первый, второй входы элемента 214 и первый вход элемента 2k+8 соединены соответственно с выходами элементов 17, 18 и 1k, первый, второй входы элемента 114 и второй вход элемента 1k+8 подключены соответственно к выходам элементов 21, 22 и 2k+6, первый, второй входы элемента 211 и первый, второй входы элемента 212 соединены соответственно с выходами элементов 29, 210 и 19, 110, первый вход элемента 1k+14 и выход элемента 2k+10 подключены соответственно к выходу элемента 1k+13 и второму входу элемента 1k+14, второй вход элемента 2k+14 и выход элемента 113-k соединены соответственно с выходом элемента 2k+13 и первым входом элемента 2k+14, первый, второй входы элемента 213 и первый вход элемента 217 подключены соответственно к выходам элементов 116, 216 и 113, а первый, второй входы элемента 2k+2, первый, второй входы элемента 2k+4 и второй вход элемента 217 подключены соответственно к (4×k-3)-му, (4×k-2)-му, (4×k-1)-му, (4×k)-му и девятому входам мажоритарного модуля, выходом которого является выход элемента 117.

и первый, второй входы элемента 2k+6 подключены соответственно к выходам элементов 2k+2, 2k+4 и 1k+2, 1k+4, первый, второй входы элемента 214 и первый вход элемента 2k+8 соединены соответственно с выходами элементов 17, 18 и 1k, первый, второй входы элемента 114 и второй вход элемента 1k+8 подключены соответственно к выходам элементов 21, 22 и 2k+6, первый, второй входы элемента 211 и первый, второй входы элемента 212 соединены соответственно с выходами элементов 29, 210 и 19, 110, первый вход элемента 1k+14 и выход элемента 2k+10 подключены соответственно к выходу элемента 1k+13 и второму входу элемента 1k+14, второй вход элемента 2k+14 и выход элемента 113-k соединены соответственно с выходом элемента 2k+13 и первым входом элемента 2k+14, первый, второй входы элемента 213 и первый вход элемента 217 подключены соответственно к выходам элементов 116, 216 и 113, а первый, второй входы элемента 2k+2, первый, второй входы элемента 2k+4 и второй вход элемента 217 подключены соответственно к (4×k-3)-му, (4×k-2)-му, (4×k-1)-му, (4×k)-му и девятому входам мажоритарного модуля, выходом которого является выход элемента 117.

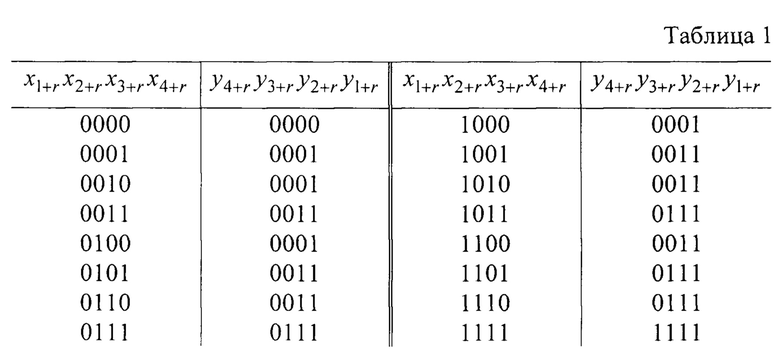

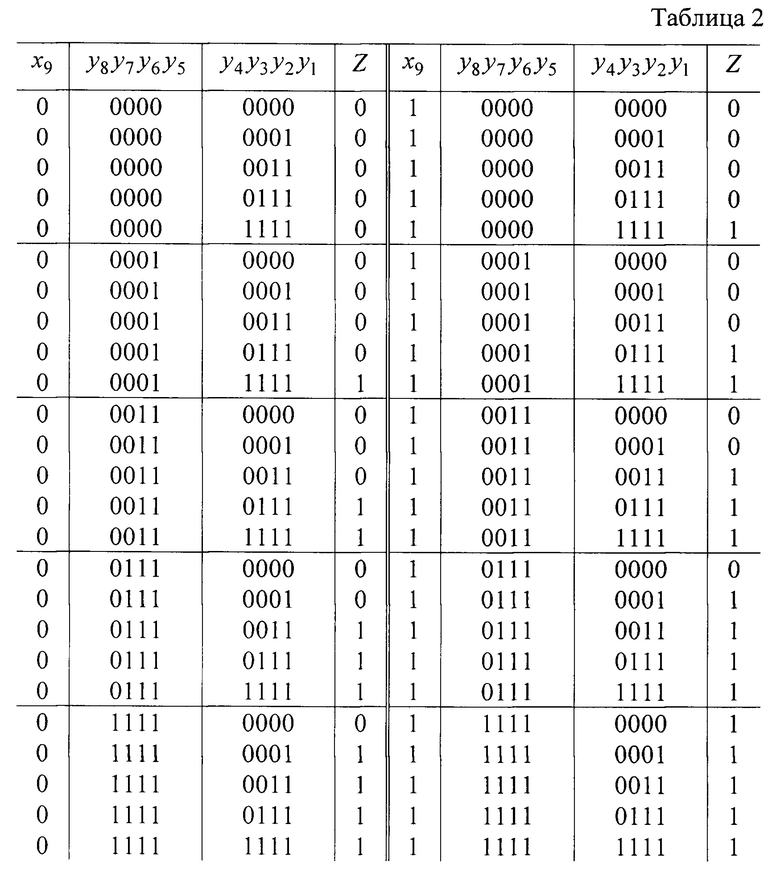

Работа предлагаемого мажоритарного модуля осуществляется следующим образом. На его первый, …, девятый входы подаются соответственно двоичные сигналы x1, …, x9 ∈ {0, l}. В представленных ниже табл. 1 и табл. 2 приведены соответственно значения внутренних сигналов y1+r, y2+r, y3-r, y4+r (r ∈ {0>4}) предлагаемого мажоритарного модуля, полученные для всех возможных наборов значений сигналов x1+r,x2+r,x3+r,x4+r, и значения его выходного сигнала Z, полученные для всех возможных наборов значений сигналов у1, …, у8, х9.

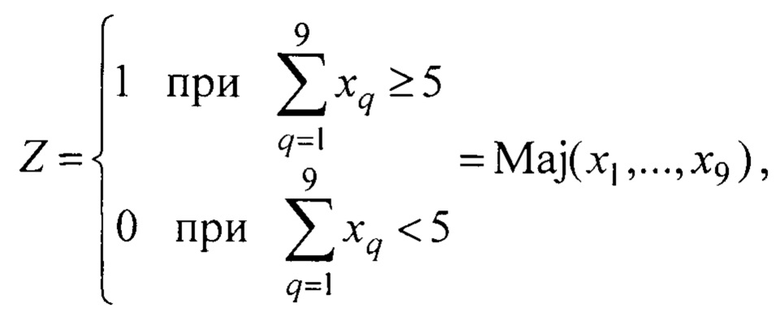

Согласно табл. 1, табл. 2 имеем

где Maj(x1, …, x9) есть мажоритарная функция девяти аргументов х1, …, х9.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый мажоритарный модуль реализует мажоритарную функцию девяти аргументов - входных двоичных сигналов и обладает меньшими по сравнению с прототипом аппаратурными затратами.

| название | год | авторы | номер документа |

|---|---|---|---|

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2021 |

|

RU2776923C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2023 |

|

RU2805141C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2022 |

|

RU2789750C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2023 |

|

RU2812683C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2021 |

|

RU2764709C1 |

| Мультиплексор | 1990 |

|

SU1780185A1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2018 |

|

RU2700552C1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2020 |

|

RU2757817C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2021 |

|

RU2775589C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2022 |

|

RU2791461C1 |

Изобретение относится к области вычислительной техники. Технический результат направлен на уменьшение аппаратных затрат при сохранении функциональных возможностей прототипа. Мажоритарный модуль, содержащий семнадцать элементов «2ИЛИ» и семнадцать элементов «2И», в котором первый, второй входы семнадцатого и первый, второй входы i-го  элементов «2И» соединены соответственно с выходами тринадцатого, семнадцатого и первым, вторым входами i-го элементов «2ИЛИ», первый, второй входы k-го

элементов «2И» соединены соответственно с выходами тринадцатого, семнадцатого и первым, вторым входами i-го элементов «2ИЛИ», первый, второй входы k-го  и первый, второй входы (k+6)-го элементов «2ИЛИ» подключены соответственно к выходам (k+2)-го, (k+4)-го элементов «2ИЛИ» и выходам (k+2)-го, (k+4)-го элементов «2И». 1 ил., 2 табл.

и первый, второй входы (k+6)-го элементов «2ИЛИ» подключены соответственно к выходам (k+2)-го, (k+4)-го элементов «2ИЛИ» и выходам (k+2)-го, (k+4)-го элементов «2И». 1 ил., 2 табл.

Мажоритарный модуль, содержащий семнадцать элементов «2ИЛИ» и семнадцать элементов «2И», отличающийся тем, что первый, второй входы семнадцатого и первый, второй входы i-го  элементов «2И» соединены соответственно с выходами тринадцатого, семнадцатого и первым, вторым входами i-го элементов «2ИЛИ», первый, второй входы k-го

элементов «2И» соединены соответственно с выходами тринадцатого, семнадцатого и первым, вторым входами i-го элементов «2ИЛИ», первый, второй входы k-го  и первый, второй входы (k+6)-го элементов «2ИЛИ» подключены соответственно к выходам (k+2)-го, (k+4)-го элементов «2ИЛИ» и выходам (k+2)-го, (k+4)-го элементов «2И», первый, второй входы четырнадцатого и первый вход (k+8)-го элементов «2ИЛИ» соединены соответственно с выходами седьмого, восьмого и выходом k-го элементов «2И», первый, второй входы четырнадцатого и второй вход (k+8)-го элементов «2И» подключены соответственно к выходам первого, второго и выходу (k+6)-го элементов «2ИЛИ», первый, второй входы одиннадцатого и первый, второй входы двенадцатого элементов «2ИЛИ» соединены соответственно с выходами девятого, десятого элементов «2ИЛИ» и выходами девятого, десятого элементов «2И», первый вход (k+14)-го элемента «2И» и выход (k+10)-го элемента «2ИЛИ» подключены соответственно к выходу (k+13)-го и второму входу (k+14)-го элементов «2И», второй вход (k+14)-го элемента «2ИЛИ» и выход (13-k)-го элемента «2И» соединены соответственно с выходом (k+13)-го и первым входом (k+14)-го элементов «2ИЛИ», первый, второй входы тринадцатого и первый вход семнадцатого элементов «2ИЛИ» подключены соответственно к выходам шестнадцатых элементов «2И», «2ИЛИ» и выходу тринадцатого элемента «2И», а первый, второй входы (k+2)-го, первый, второй входы (k+4)-го и второй вход семнадцатого элементов «2ИЛИ» подключены соответственно к (4×k-3)-му, (4×k-2)-му, (4×k-1)-му, (4×k)-му и девятому входам мажоритарного модуля, выходом которого является выход семнадцатого элемента «2И».

и первый, второй входы (k+6)-го элементов «2ИЛИ» подключены соответственно к выходам (k+2)-го, (k+4)-го элементов «2ИЛИ» и выходам (k+2)-го, (k+4)-го элементов «2И», первый, второй входы четырнадцатого и первый вход (k+8)-го элементов «2ИЛИ» соединены соответственно с выходами седьмого, восьмого и выходом k-го элементов «2И», первый, второй входы четырнадцатого и второй вход (k+8)-го элементов «2И» подключены соответственно к выходам первого, второго и выходу (k+6)-го элементов «2ИЛИ», первый, второй входы одиннадцатого и первый, второй входы двенадцатого элементов «2ИЛИ» соединены соответственно с выходами девятого, десятого элементов «2ИЛИ» и выходами девятого, десятого элементов «2И», первый вход (k+14)-го элемента «2И» и выход (k+10)-го элемента «2ИЛИ» подключены соответственно к выходу (k+13)-го и второму входу (k+14)-го элементов «2И», второй вход (k+14)-го элемента «2ИЛИ» и выход (13-k)-го элемента «2И» соединены соответственно с выходом (k+13)-го и первым входом (k+14)-го элементов «2ИЛИ», первый, второй входы тринадцатого и первый вход семнадцатого элементов «2ИЛИ» подключены соответственно к выходам шестнадцатых элементов «2И», «2ИЛИ» и выходу тринадцатого элемента «2И», а первый, второй входы (k+2)-го, первый, второй входы (k+4)-го и второй вход семнадцатого элементов «2ИЛИ» подключены соответственно к (4×k-3)-му, (4×k-2)-му, (4×k-1)-му, (4×k)-му и девятому входам мажоритарного модуля, выходом которого является выход семнадцатого элемента «2И».

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2018 |

|

RU2700554C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2018 |

|

RU2701461C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2015 |

|

RU2580801C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2005 |

|

RU2287897C1 |

| Способ и приспособление для нагревания хлебопекарных камер | 1923 |

|

SU2003A1 |

Авторы

Даты

2022-08-23—Публикация

2021-06-17—Подача