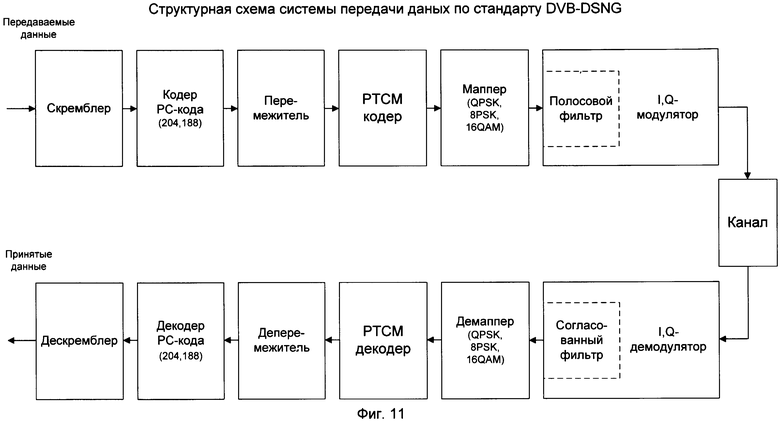

Изобретение относится к системам телекоммуникаций и может найти применение в приемниках цифровой информации для исправления ошибок, возникающих в спутниковых каналах передачи информации, например, в системе DVB-DSNG (Digital Video Broadcasting - Digital Satellite News Gathering) [1] или системе DVB-S (Digital Video Broadcasting - Satellite) [2].

Известно устройство декодирования РТСМ (Pragmatic Trellis Coded Modulation), предназначенное для работы в составе приемника цифровой информации, использующего сигнальные созвездия M-PSK [3]. Устройство содержит табличный преобразователь значений синфазной и квадратурной компонент сигнала в полярную систему координат, табличный вычислитель значений метрик ветвей для декодера Витерби, декодер Витерби, детектор интенсивности нормализации декодера Витерби, кодер сверточного кода, табличный формирователь значений секторов, буфер задержки, логику поворота секторов, блок оценки значений некодируемых бит, декодер разрешения фазовой неопределенности, дифференциальный декодер.

Фазовая неоднозначность I,Q-сигнала устраняется в устройстве [3] путем вращения значений секторов в случае обнаружения высокой интенсивности нормализации декодера Витерби и использования декодера разрешения фазовой неопределенности вместе с дифференциальным декодером. Наличие этих декодеров в устройстве обусловлено применяемым дифференциальным кодированием бит данных.

Недостатками устройства [3] являются:

- ограниченная область его применения. Устройство [3] предназначено для сигнальных созвездий M-PSK, но не поддерживает QAM (16QAM используется в системе DVB-DSNG);

- применение дифференциального кодирования приводит к размножению ошибок, что снижает помехоустойчивость приема информации из канала.

Известно устройство декодирования РТСМ, предназначенное для работы в составе приемника цифровой информации, использующего сигнальные созвездия M-PSK [4]. Устройство содержит блок оценки фазы I,Q-сигнала, два фазовращателя, блок задержки оценки фазы сигнала, выделитель группы символов сверточного кода, декодер сверточного кода, кодер сверточного кода, детектор секторов сигнального созвездия, контроллер кадровой синхронизации и три мультиплексора.

Контроллер кадровой синхронизации в известном устройстве разрешает фазовую неоднозначность I,Q-сигнала, анализируя кадровые синхронизирующие слова и поворачивая фазу в двух фазовращателях. Кадровые синхронизирующие слова должны при этом представляться как битами, закодированными сверточным кодом, так и некодируемыми битами.

Недостатком устройства является ограниченная область его применения. РТСМ-декодер [4] предназначен для сигнальных созвездий M-PSK, но так же, как и устройство [3], не поддерживает QAM. Кроме того, введенные для компенсации сдвига фазы I,Q-сигнала, блок оценки фазы I,Q-сигнала и фазовращатели манипулируют многоразрядными двоичными числами, что определяет относительную затратность аппаратных решений.

Наиболее близким по технической сущности к заявляемому изобретению является выбранное в качестве прототипа устройство, предназначенное для приема цифровой информации из спутникового канала системы DVB-DSNG [5]. Устройство содержит I,Q-демодулятор, перестраиваемый преобразователь фазы I,Q-сигнала, декодер внутреннего кода, использующий алгоритм Витерби, детектор заголовка транспортного потока, детектор поворота фазы, буфер задержки, декодер внешнего кода (кода Рида-Соломона).

Устройство-прототип разрешает фазовую неоднозначность сигнала на выходе I,Q-демодулятора путем вращения фазы сигнала на входе декодера внутреннего кода. Для определения необходимого угла поворота фазы анализируются заголовки пакетов транспортного потока (синхробайты) и сигнал отказа от декодирования декодера внешнего кода.

Недостатком прототипа является относительно высокая сложность реализации перестраиваемого преобразователя фазы, обусловленная необходимостью выполнения вычислений над многоразрядными двоичными числами, представляющими I и Q компоненты сигнала. Кроме того, включение преобразователя фазы перед декодером внутреннего кода приводит к увеличению временной задержки поступления данных в декодер внешнего кода при осуществлении поворота фазы.

Технической задачей изобретения является уменьшение аппаратной сложности устройства декодирования РТСМ (РТСМ-декодера) и вносимой им временной задержки в условиях возможной фазовой неопределенности I,Q-сигнала на выходе демодулятора.

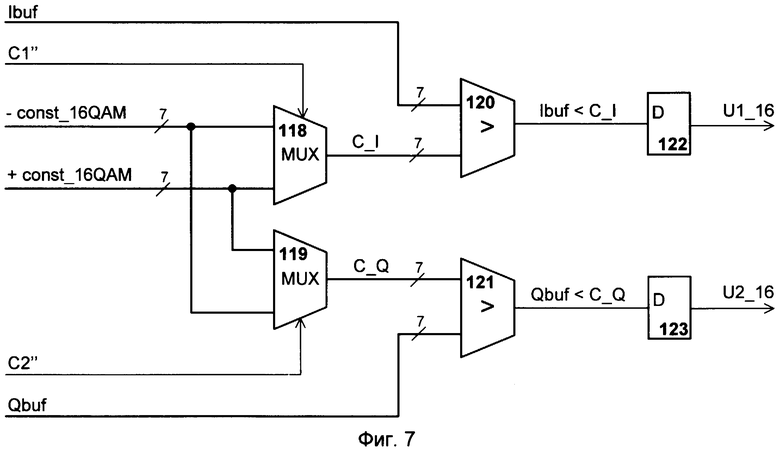

Поставленная техническая задача решается тем, что в известное устройство, содержащее буфер I,Q-компонент сигнала, декодер Витерби, блок кадровой синхронизации, причем первые входы, вторые входы, третий вход и четвертый вход буфера I,Q-компонент сигнала являются соответственно входами I, Q, С1 и С2 устройства декодирования РТСМ, согласно изобретению введены блок перестановки с инверсией мягких решений, блок кодирования и перфорации, блок перестановки с инверсией закодированных символов, первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, второй элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, блок синхронизации декодера Витерби, блок оценки некодированных бит в режимах 8PSK, блок оценки некодированных бит в режимах 16QAM, компенсатор фазового сдвига в режимах 8PSK, компенсатор фазового сдвига в режимах 16QAM, мультиплексор некодированных данных, блок сборки данных, причем первые и вторые входы блока перестановки с инверсией мягких решений являются соответственно входами soft_C1 и soft_C2 устройства декодирования РТСМ, первые и вторые выходы блока перестановки с инверсией мягких решений соединены соответственно с первыми и вторыми входами декодера Витерби, первый выход декодера Витерби соединен с первым входом блока кодирования и перфорации и с первым входом блока кадровой синхронизации, первый и второй выходы блока кодирования и перфорации соединены соответственно с первым и вторым входами блока перестановки с инверсией закодированных символов, первый выход блока перестановки с инверсией закодированных символов соединен со вторым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, с третьим входом блока оценки некодированных бит в режимах 8PSK, с третьим входом блока оценки некодированных бит в режимах 16QAM и с седьмым входом компенсатора фазового сдвига в режимах 8PSK, второй выход блока перестановки с инверсией закодированных символов соединен со вторым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, с четвертым входом блока оценки некодированных бит в режимах 8PSK, с четвертым входом блока оценки некодированных бит в режимах 16QAM и с шестым входом компенсатора фазового сдвига в режимах 8PSK, первые выходы буфера I,Q-компонент сигнала соединены с первыми входами блока оценки некодированных бит в режимах 8PSK и с первыми входами блока оценки некодированных бит в режимах 16QAM, вторые выходы буфера I,Q-компонент сигнала соединены со вторыми входами блока оценки некодированных бит в режимах 8PSK и со вторыми входами блока оценки некодированных бит в режимах 16QAM, третий выход буфера I,Q-компонент сигнала соединен с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, четвертый выход буфера I,Q-компонент сигнала соединен с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым входом блока синхронизации декодера Витерби, выход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен со вторым входом блока синхронизации декодера Витерби, первый выход блока синхронизации декодера Витерби соединен с третьим входом блока перестановки с инверсией мягких решений, с третьим входом блока перестановки с инверсией закодированных символов, с первым входом компенсатора фазового сдвига в режимах 8PSK и с первым входом компенсатора фазового сдвига в режимах 16QAM, второй выход блока синхронизации декодера Витерби соединен с третьим входом декодера Витерби, второй выход декодера Витерби соединен с третьим входом блока синхронизации декодера Витерби, третий выход блока синхронизации декодера Витерби является выходом no_vit_sync устройства декодирования РТСМ, четвертый выход блока синхронизации декодера Витерби соединен со вторым входом блока кадровой синхронизации и является выходом vit_sync_detect устройства декодирования РТСМ, пятый выход блока синхронизации декодера Витерби соединен со вторым входом блока кодирования и перфорации, третий выход блока кодирования и перфорации соединен с четвертым входом блока синхронизации декодера Витерби, первый выход блока кадровой синхронизации соединен с четвертым входом компенсатора фазового сдвига в режимах 8PSK и с четвертым входом компенсатора фазового сдвига в режимах 16QAM, второй выход блока кадровой синхронизации соединен с третьим входом блока сборки данных и является выходом frame_sync_detect устройства декодирования РТСМ, третьи выходы блока кадровой синхронизации соединены с четвертыми входами блока сборки данных, первый выход блока оценки некодированных бит в режимах 8PSK соединен со вторым входом компенсатора фазового сдвига в режимах 8PSK, второй выход блока оценки некодированных бит в режимах 8PSK соединен с третьим входом компенсатора фазового сдвига в режимах 8PSK, первый выход блока оценки некодированных бит в режимах 16QAM соединен со вторым входом компенсатора фазового сдвига в режимах 16QAM, второй выход блока оценки некодированных бит в режимах 16QAM соединен с третьим входом компенсатора фазового сдвига в режимах 16QAM, пятый вход компенсатора фазового сдвига в режимах 8PSK является входом ext_phase_shift устройства декодирования РТСМ, первый выход компенсатора фазового сдвига в режимах 8PSK соединен с первым входом мультиплексора некодированных данных, второй выход компенсатора фазового сдвига в режимах 8PSK соединен со вторым входом мультиплексора некодированных данных, первый выход компенсатора фазового сдвига в режимах 16QAM соединен с третьим входом мультиплексора некодированных данных, второй выход компенсатора фазового сдвига в режимах 16QAM соединен с четвертым входом мультиплексора некодированных данных, первый выход мультиплексора некодированных данных соединен с первым входом блока сборки данных, второй выход мультиплексора некодированных данных соединен со вторым входом блока сборки данных, первые выходы блока сборки данных являются выходами data_out устройства декодирования РТСМ, причем блок перестановки с инверсией мягких решений содержит первый вычитатель, первый мультиплексор, второй мультиплексор, первый буферный регистр, второй буферный регистр, причем управляющий вход первого мультиплексора соединен с управляющим входом второго мультиплексора и является третьим входом блока перестановки с инверсией мягких решений, первые входы данных первого мультиплексора соединены со входами вычитаемого первого вычитателя и являются первыми входами блока перестановки с инверсией мягких решений, вторые входы данных первого мультиплексора соединены с первыми входами данных второго мультиплексора и являются вторыми входами блока перестановки с инверсией мягких решений, входы уменьшаемого первого вычитателя соединены с шиной константы '15', выходы первого вычитателя соединены со вторыми входами данных второго мультиплексора, выходы первого мультиплексора соединены со входами данных первого буферного регистра, выходы второго мультиплексора соединены со входами данных второго буферного регистра, выходы первого буферного регистра являются первыми выходами блока перестановки с инверсией мягких решений, выходы второго буферного регистра являются вторыми выходами блока перестановки с инверсией мягких решений, причем блок перестановки с инверсией закодированных символов содержит первый инвертор, третий мультиплексор, четвертый мультиплексор, первый D-триггер, второй D-триггер, причем управляющий вход третьего мультиплексора соединен с управляющим входом четвертого мультиплексора и является третьим входом блока перестановки с инверсией закодированных символов, первый вход данных третьего мультиплексора соединен со входом первого инвертора и является вторым входом блока перестановки с инверсией закодированных символов, второй вход данных третьего мультиплексора соединен со вторым входом данных четвертого мультиплексора и является первым входом блока перестановки с инверсией закодированных символов, выход первого инвертора соединен с первым входом данных четвертого мультиплексора, выход третьего мультиплексора соединен с D-входом первого D-триггера, выход четвертого мультиплексора соединен с D-входом второго D-триггера, выход первого D-триггера является вторым выходом блока перестановки с инверсией закодированных символов, выход второго D-триггера является первым выходом блока перестановки с инверсией закодированных символов, причем блок синхронизации декодера Витерби содержит первый элемент И, второй элемент И, третий элемент И, четвертый элемент И, первый счетчик, первый RS-триггер, Т-триггер, пятый элемент И, первый элемент ИЛИ, первый компаратор, шестой элемент И, седьмой элемент И, третий элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, восьмой элемент И, девятый элемент И, десятый элемент И, одиннадцатый элемент И, второй счетчик, пятый мультиплексор, второй RS-триггер, второй компаратор, двенадцатый элемент И, третий счетчик, третий RS-триггер, четвертый RS-триггер, четвертый счетчик, тринадцатый элемент И, третий компаратор, пятый RS-триггер, причем нулевой разряд первых входов первого компаратора соединен с первым входом первого элемента И, первым, инверсным входом второго элемента И, первым входом первого элемента ИЛИ, с R-входом синхронного сброса Т-триггера, со вторым, инверсным входом седьмого элемента И и соединен с шиной 8PSK_5689 устройства декодирования РТСМ, разряды с первого по двенадцатый первых входов первого компаратора соединены с шиной константы единицы, второй вход первого элемента И соединен со вторым входом второго элемента И, с третьим входом пятого элемента И, со вторым входом третьего элемента И, с первым входом четвертого элемента И, со вторым входом девятого элемента И, со вторым входом десятого элемента И, со вторым входом одиннадцатого элемента И и соединен с шиной C2C1_valid устройства декодирования РТСМ, выход первого элемента И соединен со входом инкремента на единицу первого счетчика, выход второго элемента И соединен со входом инкремента на два первого счетчика, инверсный R-вход асинхронного сброса первого счетчика соединен с инверсным R-входом асинхронного сброса первого RS-триггера, с инверсным R-входом асинхронного сброса Т-триггера, с инверсным R-входом асинхронного сброса второго счетчика, с инверсным R-входом асинхронного сброса второго RS-триггера, с инверсным R-входом асинхронного сброса третьего счетчика, с инверсным R-входом асинхронного сброса третьего RS-триггера, с инверсным R-входом асинхронного сброса четвертого RS-триггера, с инверсным R-входом асинхронного сброса пятого RS-триггера, с инверсным R-входом асинхронного сброса четвертого счетчика и соединен с шиной сброса reset устройства декодирования РТСМ, выходы первого счетчика соединены со вторыми входами первого компаратора, пятый разряд выходов первого счетчика соединен с первым входом пятого элемента И, десятый разряд выходов первого счетчика соединен со вторым входом пятого элемента И, выход первого компаратора соединен с первым входом третьего элемента И, с четвертым входом четвертого элемента И, с третьим входом одиннадцатого элемента И, выход третьего элемента И соединен с R-входом синхронного сброса первого RS-триггера, выход пятого элемента И соединен с S-входом первого RS-триггера, выход четвертого элемента И соединен с Т-входом Т-триггера и со вторым входом шестого элемента И, выход Т-триггера соединен со вторым входом первого элемента ИЛИ и является первым выходом блока синхронизации декодера Витерби, выход первого элемента ИЛИ соединен с первым входом шестого элемента И, выход первого RS-триггера соединен с инверсным R-входом синхронного сброса второго счетчика, выход шестого элемента И соединен со входом инкремента на единицу третьего счетчика, со вторым входом двенадцатого элемента И, с S-входом третьего RS-триггера, с S-входом четвертого RS-триггера, первый вход седьмого элемента И является первым входом блока синхронизации декодера Витерби, выход седьмого элемента И соединен с первым входом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с первым входом восьмого элемента И, второй вход третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен со вторым входом восьмого элемента И и является вторым входом блока синхронизации декодера Витерби, выход третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым входом девятого элемента И, выход восьмого элемента И соединен с первым входом десятого элемента И, выход девятого элемента И соединен со входом инкремента на единицу второго счетчика, выход десятого элемента И соединен со входом инкремента на два второго счетчика, выходы второго счетчика соединены с первыми входами второго компаратора, первые входы, вторые входы, третьи входы, четвертые входы, пятые входы, шестые входы, седьмые входы, восьмые входы, девятые входы и десятые входы данных пятого мультиплексора соединены соответственно с шинами thres_QPSK12, thres_QPSK23, thres_QPSK34, thres_QPSK56, thres_QPSK78, thres_8PSK23, thres_8PSK56, thres_8PSK89, thres_16QAM34, thres_16QAM78 устройства декодирования РТСМ, управляющие входы пятого мультиплексора соединены с шиной выбора режима кодирования и модуляции mode устройства декодирования РТСМ, выходы пятого мультиплексора соединены со вторыми входами второго компаратора, выход второго компаратора соединен с первым входом одиннадцатого элемента И и со вторым, инверсным входом четвертого элемента И, выход одиннадцатого элемента И соединен с S-входом второго RS-триггера, выход второго RS-триггера соединен с третьим, инверсным входом четвертого элемента И и является четвертым выходом блока синхронизации декодера Витерби, первые входы третьего компаратора соединены с шиной n_last_state_cnt_sym устройства декодирования РТСМ, выходы третьего счетчика соединены со вторыми входами третьего компаратора, выход третьего компаратора соединен с R-входом синхронного сброса третьего счетчика и с первым входом двенадцатого элемента И, выход двенадцатого элемента И соединен с первым входом тринадцатого элемента И и со входом инкремента на единицу четвертого счетчика, R-вход третьего RS-триггера является третьим входом блока синхронизации декодера Витерби, выход третьего RS-триггера является вторым выходом блока синхронизации декодера Витерби, R-вход четвертого RS-триггера является четвертым входом блока синхронизации декодера Витерби, выход четвертого RS-триггера является пятым выходом блока синхронизации декодера Витерби, нулевой разряд выходов четвертого счетчика соединен со вторым входом тринадцатого элемента И, первый разряд выходов четвертого счетчика соединен с третьим входом тринадцатого элемента И, выход тринадцатого элемента И соединен с S-входом пятого RS-триггера, выход пятого RS-триггера является третьим выходом блока синхронизации декодера Витерби, причем блок кадровой синхронизации содержит первый регистр сдвига, селектор кода '47h', селектор кода 'B8h', второй элемент ИЛИ, четырнадцатый элемент И, пятнадцатый элемент И, шестнадцатый элемент И, семнадцатый элемент И, третий элемент ИЛИ, восемнадцатый элемент И, четвертый элемент ИЛИ, девятнадцатый элемент И, пятый элемент ИЛИ, двадцатый элемент И, шестой элемент ИЛИ, пятый счетчик, шестой счетчик, седьмой счетчик, восьмой счетчик, четвертый компаратор, первый дешифратор, селектор кода '7h', двадцать первый элемент И, блок инверторов, шестой RS-триггер, седьмой элемент ИЛИ, двадцать второй элемент И, двадцать третий элемент И, двадцать четвертый элемент И, двадцать пятый элемент И, восьмой элемент ИЛИ, первый шинный формирователь, второй шинный формирователь, третий шинный формирователь, четвертый шинный формирователь, пятый шинный формирователь, шестой шинный формирователь, седьмой шинный формирователь, шестой мультиплексор, девятый счетчик, сумматор, седьмой мультиплексор, девятый элемент ИЛИ, пятый компаратор, второй вычитатель, третий буферный регистр, восьмой мультиплексор, селектор нулевого кода, причем вход первого регистра сдвига является первым входом блока кадровой синхронизации, выходы первого регистра сдвига соединены со входами данных блока инверторов, со входами селектора кода '47h' и со входами селектора кода 'B8h', выход селектора кода '47h' соединен со вторым входом четырнадцатого элемента И и с первым, инверсным входом пятнадцатого элемента И, выход селектора кода 'B8h' соединен со вторым входом шестнадцатого элемента И и с первым, инверсным входом семнадцатого элемента И, первый вход четырнадцатого элемента И соединен с первым входом шестнадцатого элемента И, с инверсным R-входом синхронного сброса шестого RS-триггера, с инверсным R-входом синхронного сброса седьмого счетчика и является вторым входом блока кадровой синхронизации, выход четырнадцатого элемента И соединен со входом инкремента на единицу пятого счетчика, со вторым входом пятого элемента ИЛИ, с первым входом двадцатого элемента И и с первым входом шестого элемента ИЛИ, выход пятнадцатого элемента И соединен с первым входом третьего элемента ИЛИ, выход шестнадцатого элемента И соединен со вторым входом четвертого элемента ИЛИ, с первым входом девятнадцатого элемента И, со входом инкремента на единицу шестого счетчика и со вторым входом шестого элемента ИЛИ, выход семнадцатого элемента И соединен со вторым входом третьего элемента ИЛИ, выход третьего элемента ИЛИ соединен с первым входом четвертого элемента ИЛИ, с первым входом пятого элемента ИЛИ и со входом декремента на единицу седьмого счетчика, выход четвертого элемента ИЛИ соединен со входом декремента на единицу пятого счетчика, выход девятнадцатого элемента И соединен с R-входом синхронного сброса пятого счетчика, выход пятого элемента ИЛИ соединен со входом декремента на единицу шестого счетчика, выход двадцатого элемента И соединен с R-входом синхронного сброса шестого счетчика, выходы пятого счетчика соединены с первыми входами четвертого компаратора, выходы шестого счетчика соединены со вторыми входами четвертого компаратора, выход четвертого компаратора соединен с управляющим входом блока инверторов и является первым выходом блока кадровой синхронизации, выходы блока инверторов являются третьими выходами блока кадровой синхронизации, выход шестого элемента ИЛИ соединен со входом инкремента на единицу седьмого счетчика и с первым входом двадцать первого элемента И, выходы седьмого счетчика соединены со входами первого дешифратора, пятнадцатый разряд выходов первого дешифратора соединен со вторым входом двадцать первого элемента И, нулевой разряд выходов первого дешифратора соединен с третьим, инверсным входом пятнадцатого элемента И, с третьим, инверсным входом семнадцатого элемента И, с первым входом второго элемента ИЛИ, со вторым входом девятнадцатого элемента И, со вторым входом двадцатого элемента И, с инверсным входом инкремента на единицу восьмого счетчика, с R-входом синхронного сброса восьмого счетчика, с первым, инверсным входом двадцать пятого элемента И, с первым входом восьмого элемента ИЛИ, со вторым входом седьмого элемента ИЛИ, с управляющим входом седьмого мультиплексора и с первым входом девятого элемента ИЛИ, выход второго элемента ИЛИ соединен с третьим входом четырнадцатого элемента И и с третьим входом шестнадцатого элемента И, выход восемнадцатого элемента И соединен со вторым входом пятнадцатого элемента И, со вторым входом семнадцатого элемента И, со вторым входом второго элемента ИЛИ и с третьим входом двадцать первого элемента И, выход двадцать первого элемента И соединен с S-входом шестого RS-триггера и с шиной SB_pos_out устройства декодирования РТСМ, выход шестого RS-триггера соединен со вторым, инверсным входом восемнадцатого элемента И и является вторым выходом блока кадровой синхронизации, выходы восьмого счетчика соединены со входами селектора кода '7h', выход селектора кода '7h' соединен со вторым входом двадцать пятого элемента И, с первым входом двадцать второго элемента И и со вторым входом девятого элемента ИЛИ, управляющий вход шестого мультиплексора соединен с первым входом двадцать третьего элемента И, со вторым входом двадцать четвертого элемента И и с шиной 16QAM78 устройства декодирования РТСМ, первые входы данных шестого мультиплексора соединены с шиной константы '0', вторые входы данных шестого мультиплексора соединены с шиной константы '2', выходы шестого мультиплексора соединены с первыми входами пятого компаратора, выход двадцать пятого элемента И соединен со входом инкремента на единицу девятого счетчика, выход двадцать второго элемента И соединен со вторым входом восьмого элемента ИЛИ, выход восьмого элемента ИЛИ соединен с R-входом синхронного сброса девятого счетчика, выходы девятого счетчика соединены со вторыми входами пятого компаратора, выход пятого компаратора соединен с четвертым входом двадцать первого элемента И, со вторым входом двадцать второго элемента И и с первым входом седьмого элемента ИЛИ, выход седьмого элемента ИЛИ соединен со вторым, инверсным входом двадцать третьего элемента И и с первым входом двадцать четвертого элемента И, входы данных первого шинного формирователя соединены с шиной константы '2', управляющий вход первого шинного формирователя соединен с шиной 8PSK23 устройства декодирования РТСМ, входы данных второго шинного формирователя соединены с шиной константы '5', управляющий вход второго шинного формирователя соединен с шиной 8PSK56 устройства декодирования РТСМ, входы данных третьего шинного формирователя соединены с шиной константы '4', управляющий вход третьего шинного формирователя соединен с шиной 8PSK89 устройства декодирования РТСМ, входы данных четвертого шинного формирователя соединены с шиной константы '2', выход двадцать третьего элемента И соединен с управляющим входом четвертого шинного формирователя, входы данных пятого шинного формирователя соединены с шиной константы '3', выход двадцать четвертого элемента И соединен с управляющим входом пятого шинного формирователя, входы данных шестого шинного формирователя соединены с шиной константы '1', управляющий вход шестого шинного формирователя соединен с шиной QPSK устройства декодирования РТСМ, входы данных седьмого шинного формирователя соединены с шиной константы '3', управляющий вход седьмого шинного формирователя соединен с шиной 16QAM34 устройства декодирования РТСМ, выходы первого шинного формирователя соединены с выходами второго шинного формирователя, с выходами третьего шинного формирователя, с выходами четвертого шинного формирователя, с выходами пятого шинного формирователя, с выходами шестого шинного формирователя, с выходами седьмого шинного формирователя, с тремя младшими разрядами первых входов сумматора и с тремя младшими разрядами вторых входов данных седьмого мультиплексора, пять старших разрядов первых входов сумматора и пять старших разрядов вторых входов данных седьмого мультиплексора соединены с шиной константы '0', выходы сумматора соединены с восемью младшими разрядами входов уменьшаемого второго вычитателя и со вторыми входами данных восьмого мультиплексора, старший разряд входов уменьшаемого второго вычитателя соединен с шиной константы '0', входы вычитаемого второго вычитателя соединены с шиной константы '204', младшие разряды выходов второго вычитателя соединены с первыми входами данных восьмого мультиплексора, старший, знаковый разряд выходов второго вычитателя соединен с управляющим входом восьмого мультиплексора, выходы восьмого мультиплексора соединены с первыми входами данных седьмого мультиплексора, выходы седьмого мультиплексора соединены со входами данных третьего буферного регистра, выходы третьего буферного регистра соединены со вторыми входами сумматора и со входами селектора нулевого кода, выход девятого элемента ИЛИ соединен с управляющим входом третьего буферного регистра, выход селектора нулевого кода соединен с первым входом восемнадцатого элемента И, причем блок оценки некодированных бит в режимах 8PSK содержит второй инвертор, девятый мультиплексор, десятый мультиплексор, одиннадцатый мультиплексор, первый умножитель, второй умножитель, шестой компаратор, седьмой компаратор, двадцать шестой элемент И, двадцать седьмой элемент И, десятый элемент ИЛИ, двадцать восьмой элемент И, четвертый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, третий D-триггер, четвертый D-триггер, причем управляющий вход девятого мультиплексора соединен с первым, инверсным входом двадцать восьмого элемента И и с шиной 8PSK23 устройства декодирования РТСМ, первый вход двадцать шестого элемента И соединен с первым, инверсным входом двадцать седьмого элемента И, со входом второго инвертора, с нулевым разрядом вторых входов данных девятого мультиплексора, с управляющим входом одиннадцатого мультиплексора и является третьим входом блока оценки некодированных бит в режимах 8PSK, первый разряд вторых входов данных девятого мультиплексора является четвертым входом данных блока оценки некодированных бит в режимах 8PSK, нулевой разряд первых входов данных девятого мультиплексора соединен с шиной константы '0', выход второго инвертора соединен с первым разрядом первых входов данных девятого мультиплексора, выходы девятого мультиплексора соединены с управляющими входами десятого мультиплексора, первые входы данных десятого мультиплексора соединены с шиной константы K00 устройства декодирования РТСМ, вторые входы данных десятого мультиплексора соединены с первыми входами данных одиннадцатого мультиплексора и с шиной константы K01 устройства декодирования РТСМ, третьи входы данных десятого мультиплексора соединены с шиной константы K10 устройства декодирования РТСМ, четвертые входы данных десятого мультиплексора соединены со вторыми входами данных одиннадцатого мультиплексора и с шиной константы K11 устройства декодирования РТСМ, выходы десятого мультиплексора соединены с первыми входами первого умножителя, выходы одиннадцатого мультиплексора соединены со вторыми входами второго умножителя, вторые входы первого умножителя соединены с первыми входами второго умножителя и являются первыми входами блока оценки некодированных бит в режимах 8PSK, выходы первого умножителя соединены с первыми входами шестого компаратора, выходы второго умножителя соединены со вторыми входами седьмого компаратора, вторые входы шестого компаратора соединены с первыми входами седьмого компаратора и являются вторыми входами блока оценки некодированных бит в режимах 8PSK, выход шестого компаратора соединен со вторым входом четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход седьмого компаратора соединен со вторым входом двадцать шестого элемента И, со вторым, инверсным входом двадцать седьмого элемента И и с D-входом четвертого D-триггера, выход двадцать шестого элемента И соединен с первым входом десятого элемента ИЛИ, выход двадцать седьмого элемента И соединен со вторым входом десятого элемента ИЛИ, выход десятого элемента ИЛИ соединен со вторым входом двадцать восьмого элемента И, выход двадцать восьмого элемента И соединен с первым входом четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с D-входом третьего D-триггера, выход третьего D-триггера является первым выходом блока оценки некодированных бит в режимах 8PSK, выход четвертого D-триггера является вторым выходом блока оценки некодированных бит в режимах 8PSK, причем блок оценки некодированных бит в режимах 16QAM содержит двенадцатый мультиплексор, тринадцатый мультиплексор, восьмой компаратор, девятый компаратор, пятый D-триггер, шестой D-триггер, причем первые входы восьмого компаратора являются первыми входами блока оценки некодированных бит в режимах 16QAM, управляющий вход двенадцатого мультиплексора является третьим входом блока оценки некодированных бит в режимах 16QAM, первые входы данных двенадцатого мультиплексора соединены со вторыми входами данных тринадцатого мультиплексора и с шиной константы -const_16QAM устройства декодирования РТСМ, вторые входы данных двенадцатого мультиплексора соединены с первыми входами данных тринадцатого мультиплексора и с шиной +const_16QAM устройства декодирования РТСМ, управляющий вход тринадцатого мультиплексора является четвертым входом блока оценки некодированных бит в режимах 16QAM, вторые входы девятого компаратора являются вторыми входами блока оценки некодированных бит в режимах 16QAM, выходы двенадцатого мультиплексора соединены со вторыми входами восьмого компаратора, выходы тринадцатого мультиплексора соединены с первыми входами девятого компаратора, выход восьмого компаратора соединен с D-входом пятого D-триггера, выход девятого компаратора соединен с D-входом шестого D-триггера, выход пятого D-триггера является первым выходом блока оценки некодированных бит в режимах 16QAM, выход шестого D-триггера является вторым выходом блока оценки некодированных бит в режимах 16QAM, причем компенсатор фазового сдвига в режимах 8PSK содержит двадцать девятый элемент И, тридцатый элемент И, тридцать первый элемент И, пятый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, тридцать второй элемент И, тридцать третий элемент И, тридцать четвертый элемент И, одиннадцатый элемент ИЛИ, двенадцатый элемент ИЛИ, третий инвертор, четвертый инвертор, пятый инвертор, шестой инвертор, четырнадцатый мультиплексор, шестой элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, седьмой инвертор, восьмой инвертор, пятнадцатый мультиплексор, шестнадцатый мультиплексор, седьмой элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, тридцать пятый элемент И, тридцать шестой элемент И, тридцать седьмой элемент И, тридцать восьмой элемент И, тридцать девятый элемент И, сороковой элемент И, сорок первый элемент И, сорок второй элемент И, сорок третий элемент И, сорок четвертый элемент И, сорок пятый элемент И, сорок шестой элемент И, тринадцатый элемент ИЛИ, четырнадцатый элемент ИЛИ, пятнадцатый элемент ИЛИ, шестнадцатый элемент ИЛИ, девятый инвертор, десятый инвертор, семнадцатый мультиплексор, причем первый вход данных четырнадцатого мультиплексора соединен с первым, инверсным входом двадцать девятого элемента И, с первым входом тридцатого элемента И, с первым входом тридцать первого элемента И, с первым входом пятого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, с первым входом тридцать второго элемента И, с первым, инверсным входом тридцать третьего элемента И, с первым, инверсным входом тридцать четвертого элемента И, со входом третьего инвертора, с первым и пятым входами данных пятнадцатого мультиплексора, со входом седьмого инвертора, с первым входом шестого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, со вторым входом седьмого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, со вторым, инверсным входом тридцать пятого элемента И, со вторым входом тридцать седьмого элемента И, со вторым входом тридцать восьмого элемента И, со вторым, инверсным входом сорокового элемента И, со вторым, инверсным входом сорок первого элемента И, со вторым входом сорок третьего элемента И, со вторым входом сорок четвертого элемента И, со вторым, инверсным входом сорок шестого элемента И и является вторым входом компенсатора фазового сдвига в режимах 8PSK,

второй, инверсный вход двадцать девятого элемента И соединен со вторым входом тридцатого элемента И, с третьим, инверсным входом тридцать второго элемента И, со вторым входом тридцать четвертого элемента И, со вторым входом шестого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, с третьим, инверсным входом тридцать пятого элемента И, со вторым входом тридцать шестого элемента И, с третьим входом тридцать восьмого элемента И, со вторым, инверсным входом тридцать девятого элемента И, с третьим, инверсным входом сорок первого элемента И, со вторым входом сорок второго элемента И, с третьим входом сорок четвертого элемента И, со вторым, инверсным входом сорок пятого элемента И и является седьмым входом компенсатора фазового сдвига в режимах 8PSK, третий, инверсный вход двадцать девятого элемента И соединен со вторым входом тридцать первого элемента И, со вторым входом пятого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, со вторым входом тридцать второго элемента И, со вторым, инверсным входом тридцать третьего элемента И и является шестым входом компенсатора фазового сдвига в режимах 8PSK,

выход двадцать девятого элемента И соединен с первым входом одиннадцатого элемента ИЛИ, выход тридцатого элемента И соединен со вторым входом одиннадцатого элемента ИЛИ, выход тридцать первого элемента И соединен с третьим входом одиннадцатого элемента ИЛИ, выход одиннадцатого элемента ИЛИ соединен со вторым входом данных четырнадцатого мультиплексора и со входом четвертого инвертора, инверсный выход пятого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с третьим входом данных четырнадцатого мультиплексора и со входом пятого инвертора, выход тридцать второго элемента И соединен с первым входом двенадцатого элемента ИЛИ, выход тридцать третьего элемента И соединен со вторым входом двенадцатого элемента ИЛИ, выход тридцать четвертого элемента И соединен с третьим входом двенадцатого элемента ИЛИ, выход двенадцатого элемента ИЛИ соединен с четвертым входом данных четырнадцатого мультиплексора и со входом шестого инвертора, выход третьего инвертора соединен с пятым входом данных четырнадцатого мультиплексора, выход четвертого инвертора соединен с шестым входом данных четырнадцатого мультиплексора, выход пятого инвертора соединен с седьмым входом данных четырнадцатого мультиплексора, выход шестого инвертора соединен с восьмым входом данных четырнадцатого мультиплексора, второй разряд управляющих входов четырнадцатого мультиплексора соединен с первым разрядом управляющих входов пятнадцатого мультиплексора, с первым разрядом управляющих входов семнадцатого мультиплексора и является нулевым разрядом пятых входов компенсатора фазового сдвига в режимах 8PSK, первый разряд управляющих входов четырнадцатого мультиплексора соединен с нулевым разрядом управляющих входов пятнадцатого мультиплексора, с нулевым разрядом управляющих входов семнадцатого мультиплексора и является четвертым входом компенсатора фазового сдвига в режимах 8PSK, нулевой разряд управляющих входов четырнадцатого мультиплексора является первым входом компенсатора фазового сдвига в режимах 8PSK, выход четырнадцатого мультиплексора соединен с первым входом данных шестнадцатого мультиплексора, второй разряд управляющих входов пятнадцатого мультиплексора соединен со вторым разрядом управляющих входов семнадцатого мультиплексора и является первым разрядом пятых входов компенсатора фазового сдвига в режимах 8PSK, выход седьмого инвертора соединен с третьим и седьмым входами данных пятнадцатого мультиплексора, выход шестого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен со входом восьмого инвертора, с четвертым и восьмым входами данных пятнадцатого мультиплексора, выход восьмого инвертора соединен со вторым и шестым входами данных пятнадцатого мультиплексора, выход пятнадцатого мультиплексора соединен со вторым входом данных шестнадцатого мультиплексора, управляющий вход шестнадцатого мультиплексора соединен с шиной 8PSK23 устройства декодирования РТСМ, выход шестнадцатого мультиплексора является первым выходом компенсатора фазового сдвига в режимах 8PSK, первый вход данных семнадцатого мультиплексора соединен с первым входом седьмого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, со входом десятого инвертора, с первым, инверсным входом тридцать пятого элемента И, с первым входом тридцать шестого элемента И, с первым входом тридцать седьмого элемента И, с первым входом тридцать восьмого элемента И, с первым, инверсным входом тридцать девятого элемента И, с первым, инверсным входом сорокового элемента И, с первым входом сорок первого элемента И, с первым, инверсным входом сорок второго элемента И, с первым, инверсным входом сорок третьего элемента И, с первым, инверсным входом сорок четвертого элемента И, с первым входом сорок пятого элемента И, с первым входом сорок шестого элемента И и является третьим входом компенсатора фазового сдвига в режимах 8PSK, выход седьмого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен со входом девятого инвертора и с седьмым входом данных семнадцатого мультиплексора, выход девятого инвертора соединен с третьим входом данных семнадцатого мультиплексора, выход десятого инвертора соединен с пятым входом данных семнадцатого мультиплексора, выход тридцать пятого элемента И соединен с первым входом тринадцатого элемента ИЛИ, выход тридцать шестого элемента И соединен со вторым входом тринадцатого элемента ИЛИ, выход тридцать седьмого элемента И соединен с третьим входом тринадцатого элемента ИЛИ, выход тринадцатого элемента ИЛИ соединен со вторым входом данных семнадцатого мультиплексора, выход тридцать восьмого элемента И соединен с первым входом четырнадцатого элемента ИЛИ, выход тридцать девятого элемента И соединен со вторым входом четырнадцатого элемента ИЛИ, выход сорокового элемента И соединен с третьим входом четырнадцатого элемента ИЛИ, выход четырнадцатого элемента ИЛИ соединен с четвертым входом данных семнадцатого мультиплексора, выход сорок первого элемента И соединен с первым входом пятнадцатого элемента ИЛИ, выход сорок второго элемента И соединен со вторым входом пятнадцатого элемента ИЛИ, выход сорок третьего элемента И соединен с третьим входом пятнадцатого элемента ИЛИ, выход пятнадцатого элемента ИЛИ соединен с шестым входом данных семнадцатого мультиплексора, выход сорок четвертого элемента И соединен с первым входом шестнадцатого элемента ИЛИ, выход сорок пятого элемента И соединен со вторым входом шестнадцатого элемента ИЛИ, выход сорок шестого элемента И соединен с третьим входом шестнадцатого элемента ИЛИ, выход шестнадцатого элемента ИЛИ соединен с восьмым входом данных семнадцатого мультиплексора, выход семнадцатого мультиплексора является вторым выходом компенсатора фазового сдвига в режимах 8PSK, причем компенсатор фазового сдвига в режимах 16QAM содержит одиннадцатый инвертор, двенадцатый инвертор, восемнадцатый мультиплексор, девятнадцатый мультиплексор, причем первый вход данных восемнадцатого мультиплексора соединен со входом одиннадцатого инвертора, с четвертым входом данных девятнадцатого мультиплексора и является вторым входом компенсатора фазового сдвига в режимах 16QAM, второй вход данных восемнадцатого мультиплексора соединен со входом двенадцатого инвертора, с первым входом данных девятнадцатого мультиплексора и является третьим входом компенсатора фазового сдвига в режимах 16QAM, выход одиннадцатого инвертора соединен с третьим входом данных восемнадцатого мультиплексора и со вторым входом данных девятнадцатого мультиплексора, выход двенадцатого инвертора соединен с четвертым входом данных восемнадцатого мультиплексора и с третьим входом данных девятнадцатого мультиплексора, нулевой разряд управляющих входов восемнадцатого мультиплексора соединен с нулевым разрядом управляющих входов девятнадцатого мультиплексора и является первым входом компенсатора фазового сдвига в режимах 16QAM, первый разряд управляющих входов восемнадцатого мультиплексора соединен с первым разрядом управляющих входов девятнадцатого мультиплексора и является четвертым входом компенсатора фазового сдвига в режимах 16QAM, выход восемнадцатого мультиплексора является первым выходом компенсатора фазового сдвига в режимах 16QAM, выход девятнадцатого мультиплексора является вторым выходом компенсатора фазового сдвига в режимах 16QAM, причем блок сборки данных содержит второй регистр сдвига, четвертый буферный регистр, пятый буферный регистр, буфер задержки кодированных символов, буфер задержки некодированных символов, двадцатый мультиплексор, десятый счетчик, второй дешифратор, десятый компаратор, сорок седьмой элемент И, семнадцатый элемент ИЛИ, причем входы данных четвертого буферного регистра являются четвертыми входами блока сборки данных, выходы четвертого буферного регистра соединены со входами буфера задержки кодированных символов, выходы буфера задержки кодированных символов соединены с первыми входами данных двадцатого мультиплексора, первый вход второго регистра сдвига является первым входом блока сборки данных, второй вход второго регистра сдвига является вторым входом блока сборки данных, вход выбора величины сдвига второго регистра сдвига соединен с шиной 8PSK23 устройства декодирования РТСМ, выходы второго регистра сдвига соединены со входами данных пятого буферного регистра, выходы пятого буферного регистра соединены со входами буфера задержки некодированных символов, выходы буфера задержки некодированных символов соединены со вторыми входами данных двадцатого мультиплексора, выходы двадцатого мультиплексора являются выходами блока сборки данных, первый вход сорок седьмого элемента И соединен с шиной 16QAM78 устройства декодирования РТСМ, инверсный R-вход асинхронного сброса десятого счетчика соединен с шиной сброса reset устройства декодирования РТСМ, выходы десятого счетчика соединены со входами второго дешифратора и с первыми входами десятого компаратора, нулевой разряд выходов второго дешифратора соединен с первым входом семнадцатого элемента ИЛИ, третий разряд выходов второго дешифратора соединен со вторым входом сорок седьмого элемента И, выход сорок седьмого элемента И соединен со вторым входом семнадцатого элемента ИЛИ, пятый разряд выходов второго дешифратора соединен с третьим входом семнадцатого элемента ИЛИ, выход семнадцатого элемента ИЛИ соединен с управляющим входом двадцатого мультиплексора, вторые входы десятого компаратора соединены с шиной n_last_state_cnt_A_L устройства декодирования РТСМ, выход десятого компаратора соединен с R-входом синхронного сброса десятого счетчика.

Взаимодействие введенных функциональных блоков позволяет использовать предлагаемое устройство в составе приемников систем DVB-DSNG или DVB-S, поскольку устройство поддерживает все режимы кодирования и модуляции, определенные в стандарте DVB-DSNG (QPSK, 8PSK, 16QAM), которые, в свою очередь, включают в себя все режимы стандарта DVB-S. Введение компенсаторов фазового сдвига для разрешения фазовой неоднозначности сигнала на выходе I,Q-демодулятора после декодера Витерби позволяет значительно снизить аппаратную сложность устройства, поскольку при этом исключаются операции с многоразрядными числами до декодера Витерби. Это также уменьшает временную задержку выдачи данных устройством после установления кадровой синхронизации.

Сущность изобретения заключается в следующем. Разрешение фазовой неоднозначности I,Q-сигнала на выходе I,Q-демодулятора приемника осуществляется в предлагаемом устройстве в процессе его синхронизации с использованием свойств внутреннего (сверточного) кода, последовательности синхробайт и свойств внешнего (блочного) кода Рида-Соломона. Компенсация возможного фазового сдвига I,Q-сигнала осуществляется распределенно различными блоками устройства. Фазовый сдвиг для бит данных, закодированных сверточным кодом, компенсируется в блоке перестановки с инверсией мягких решений и блоке кадровой синхронизации. Компенсация фазового сдвига для бит данных, не кодированных сверточным кодом, осуществляется компенсатором фазового сдвига в режимах 8PSK или компенсатором фазового сдвига в режимах 16QAM с использованием результатов работы декодера Витерби, блока синхронизации декодера Витерби и блока кадровой синхронизации.

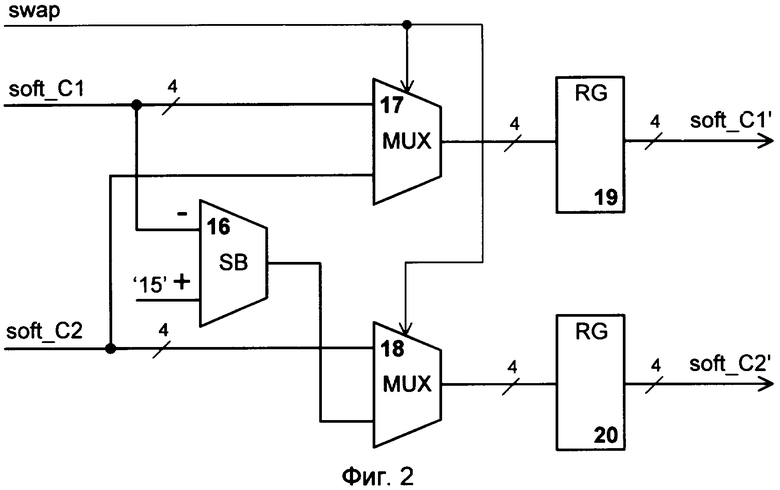

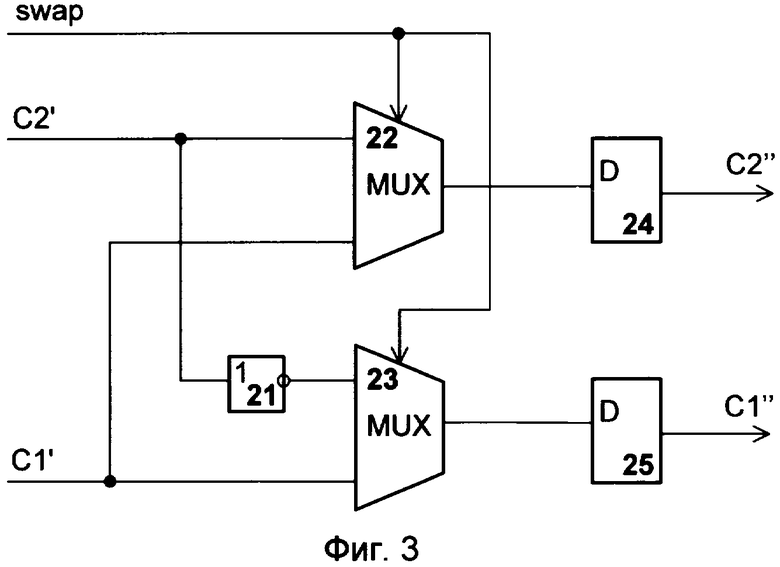

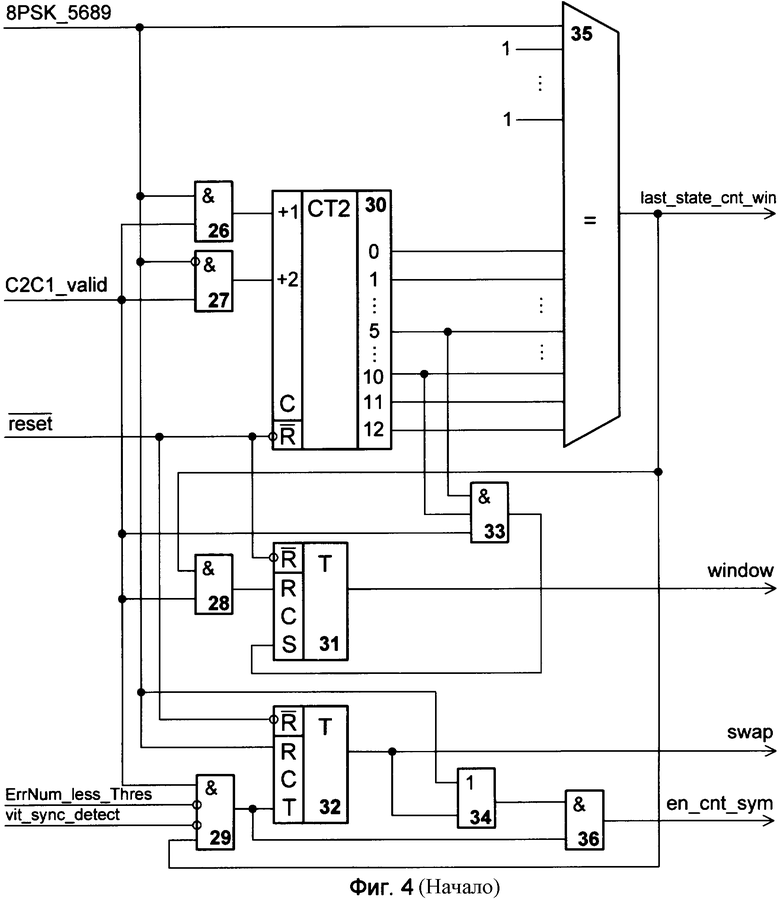

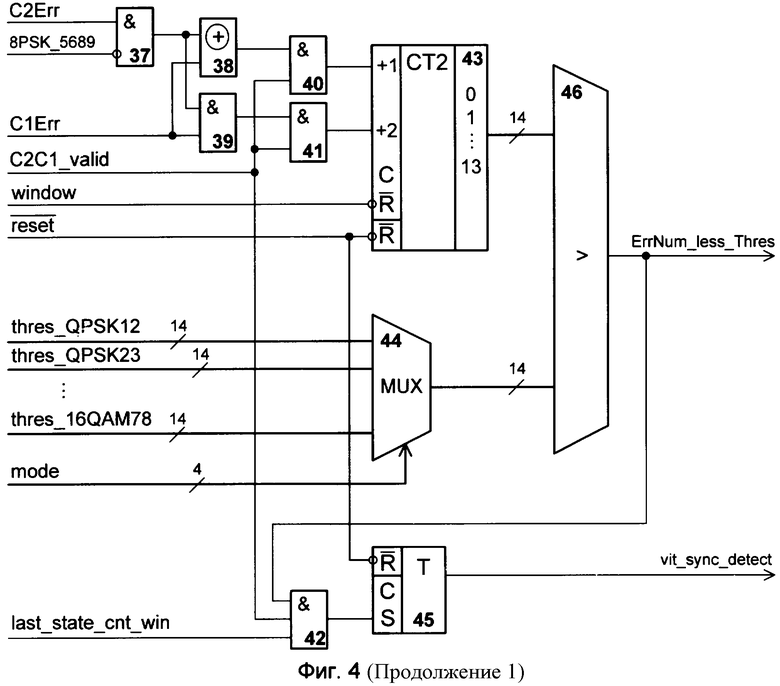

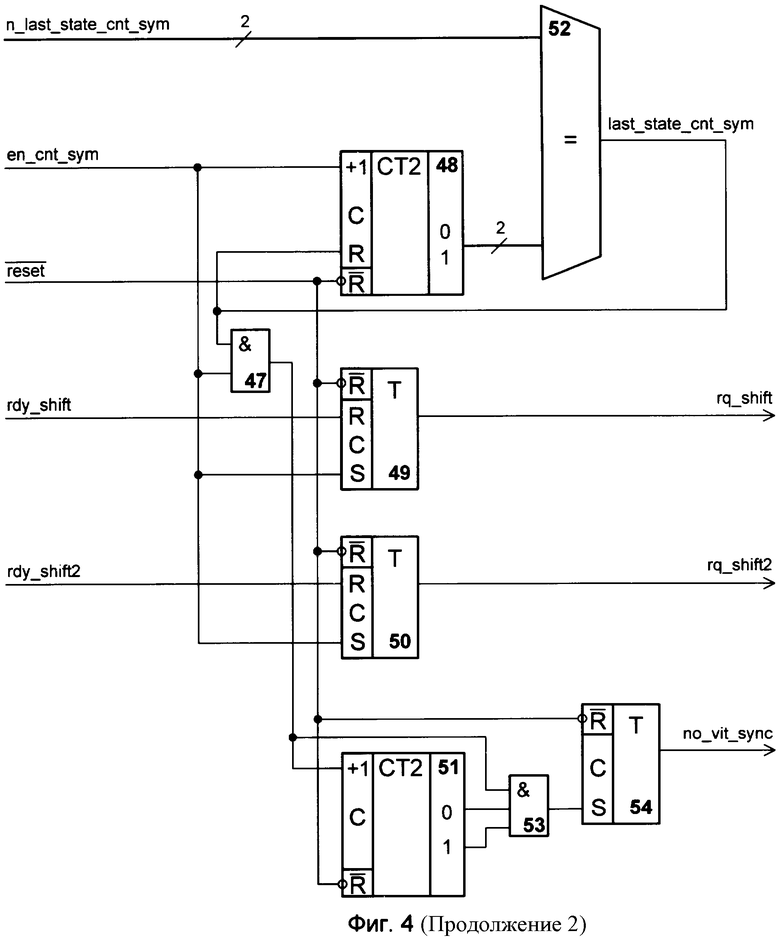

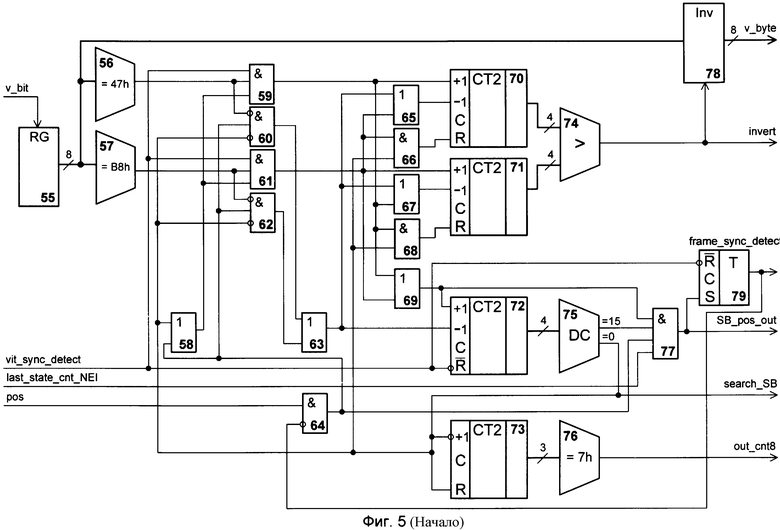

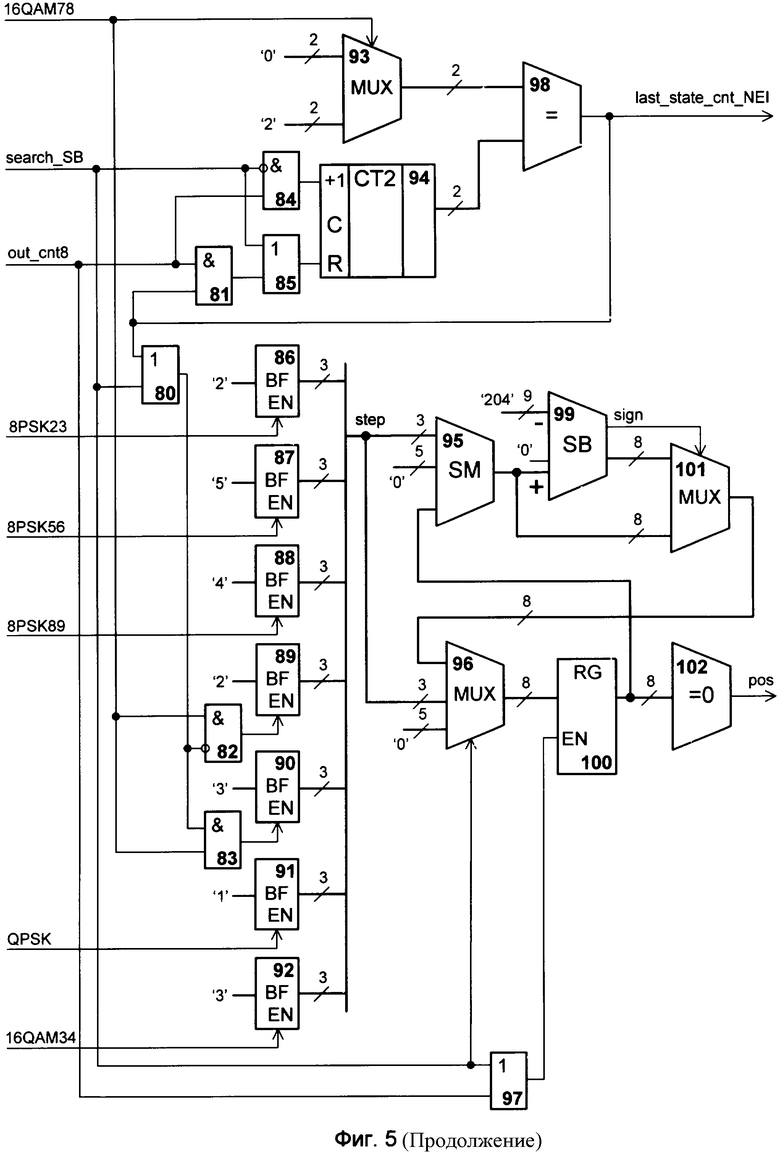

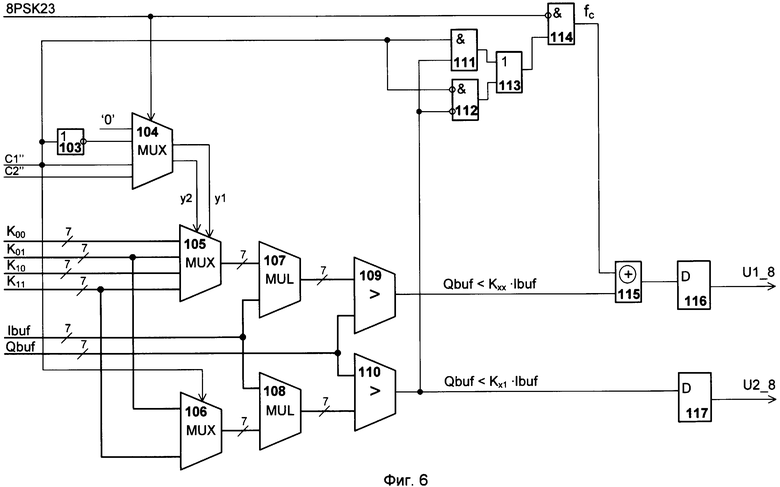

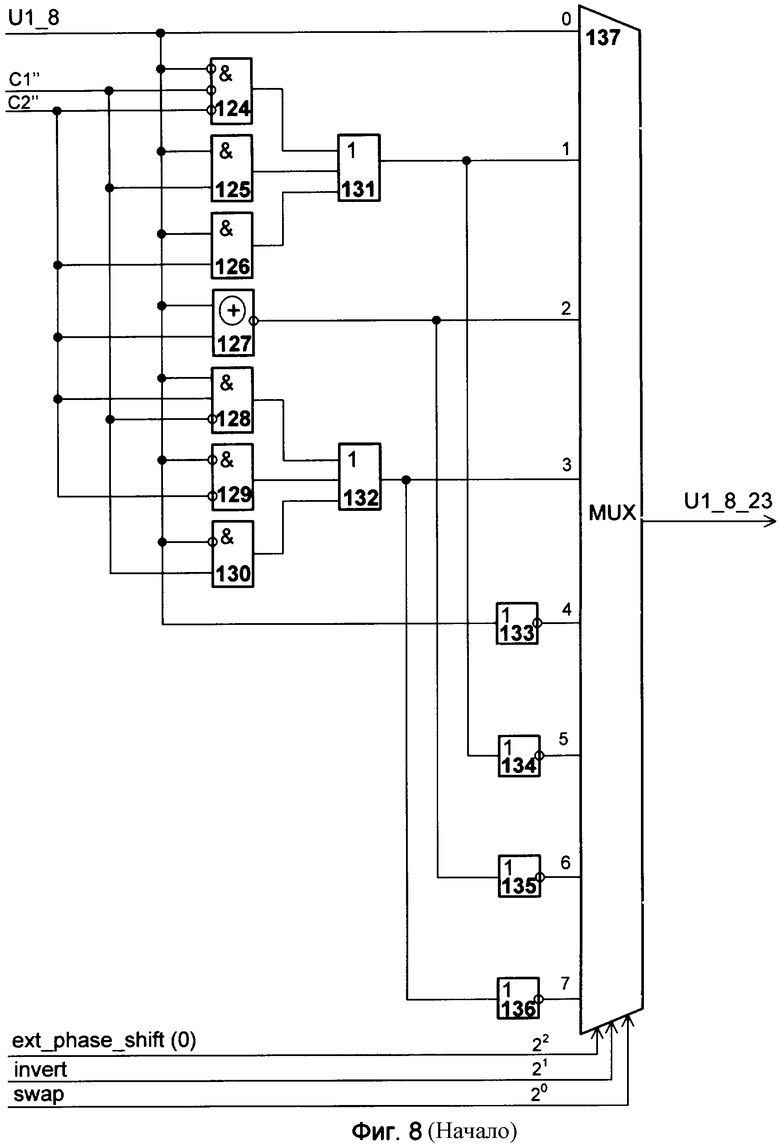

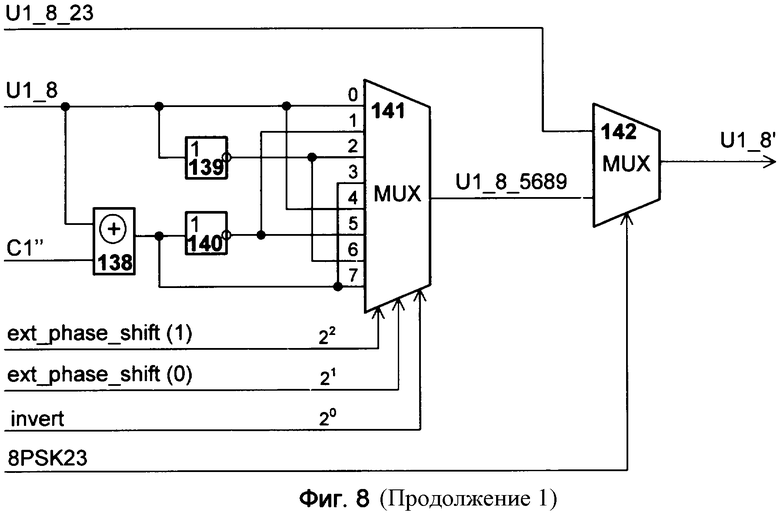

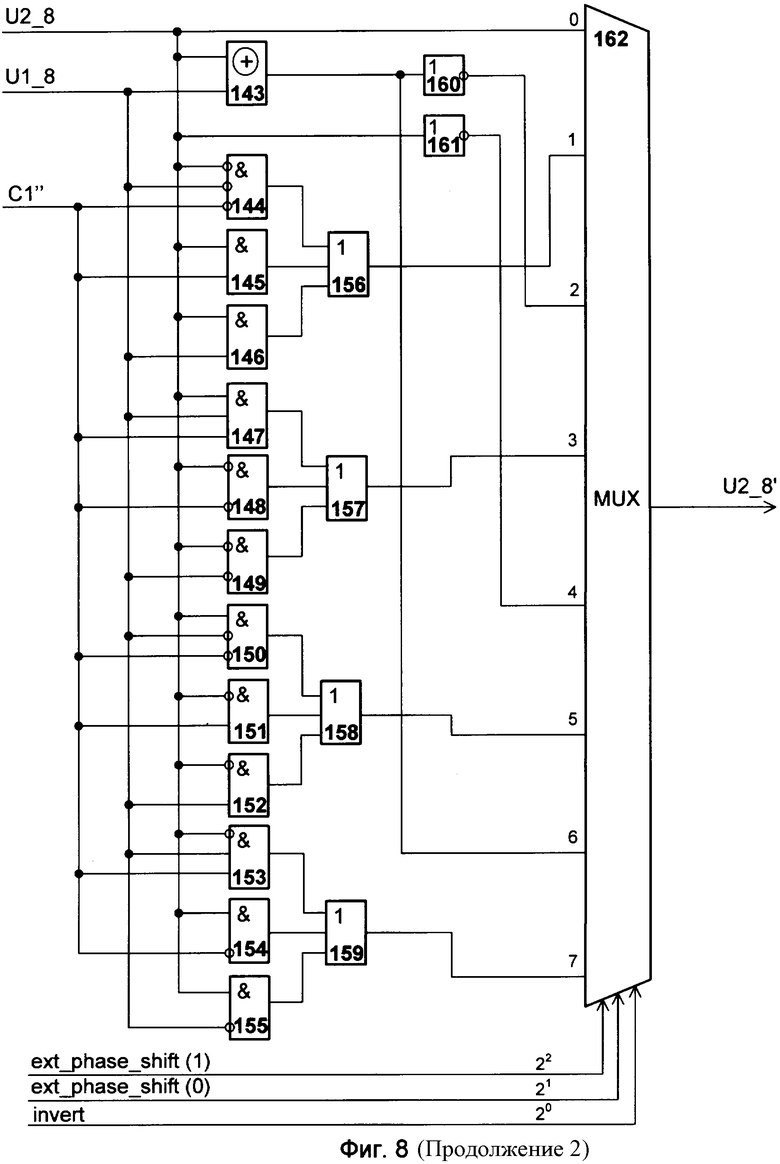

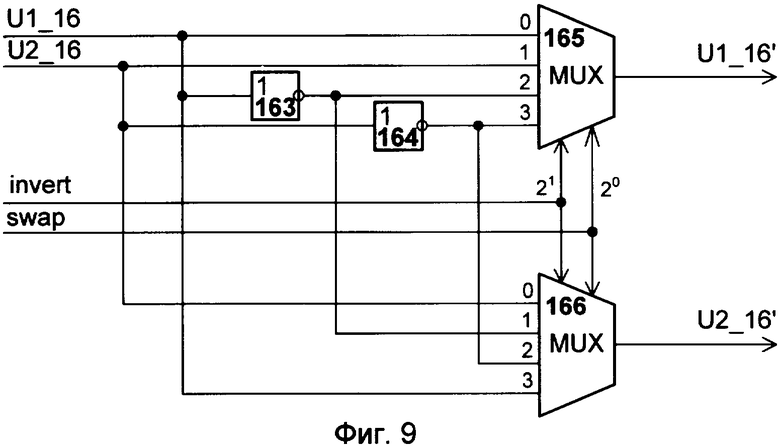

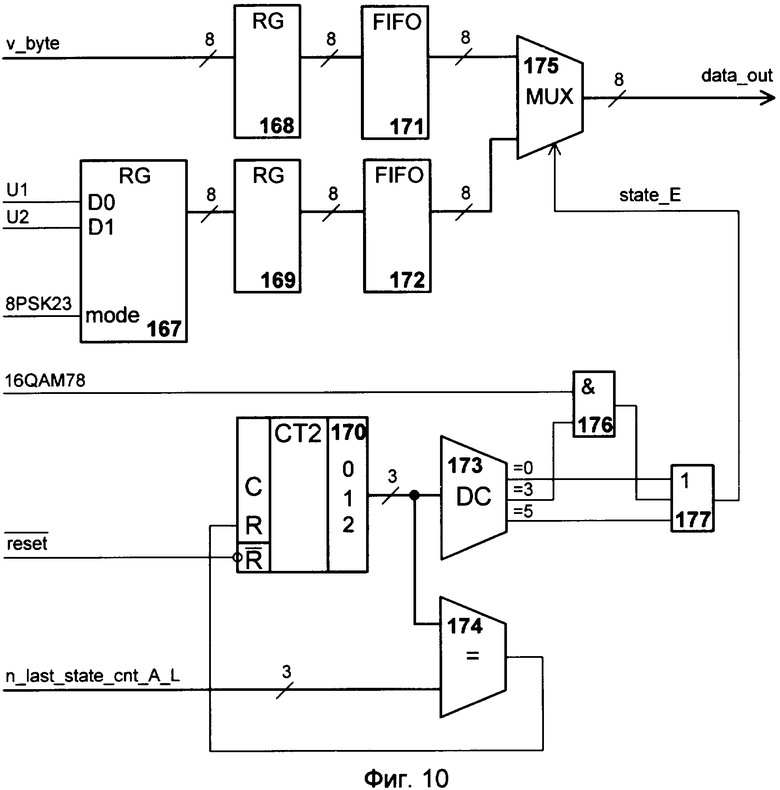

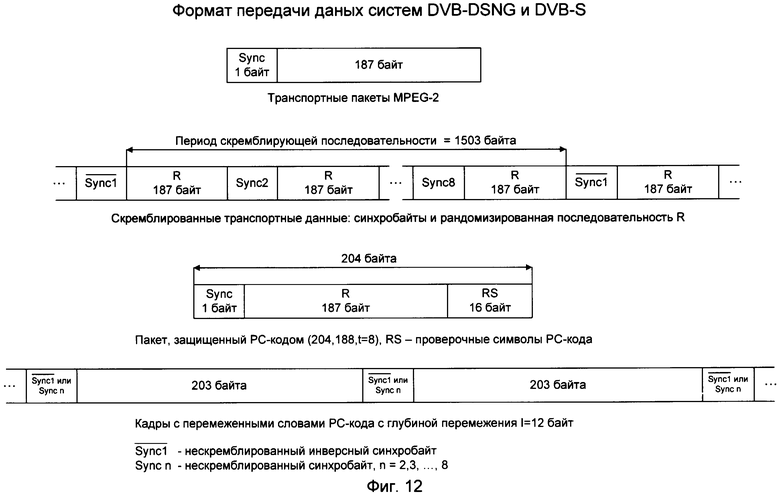

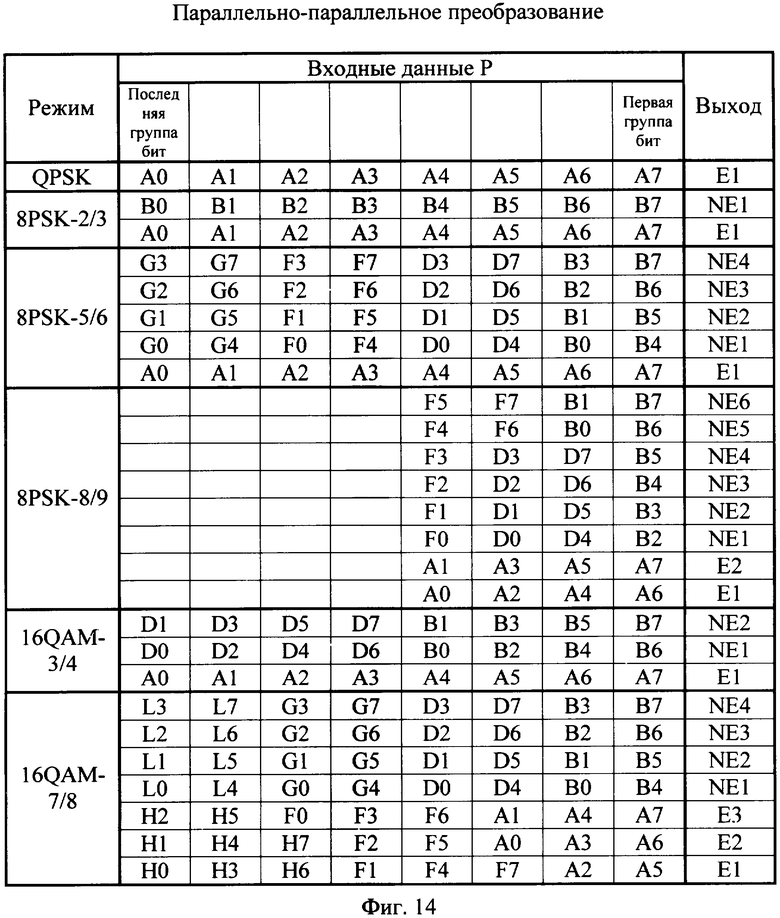

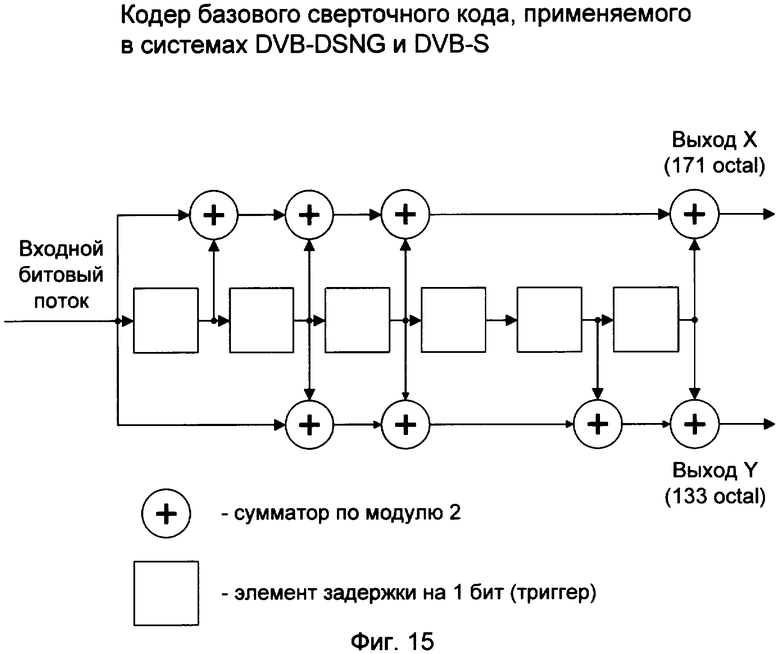

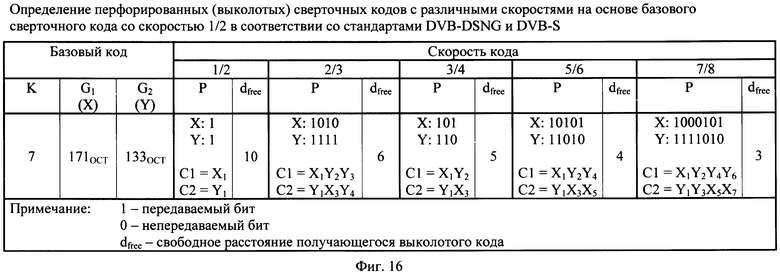

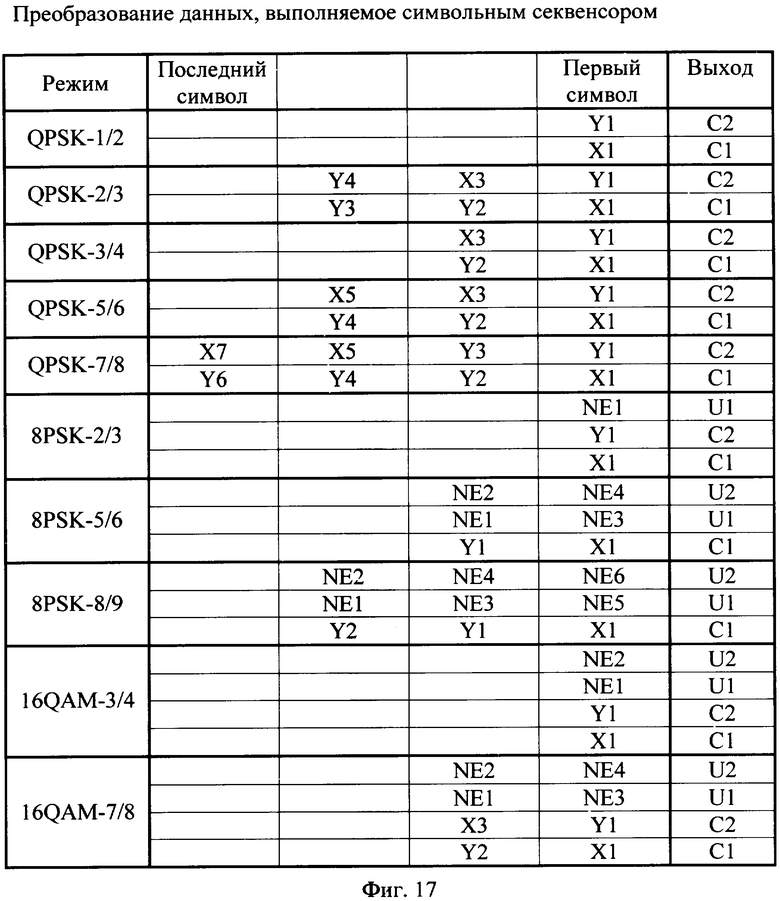

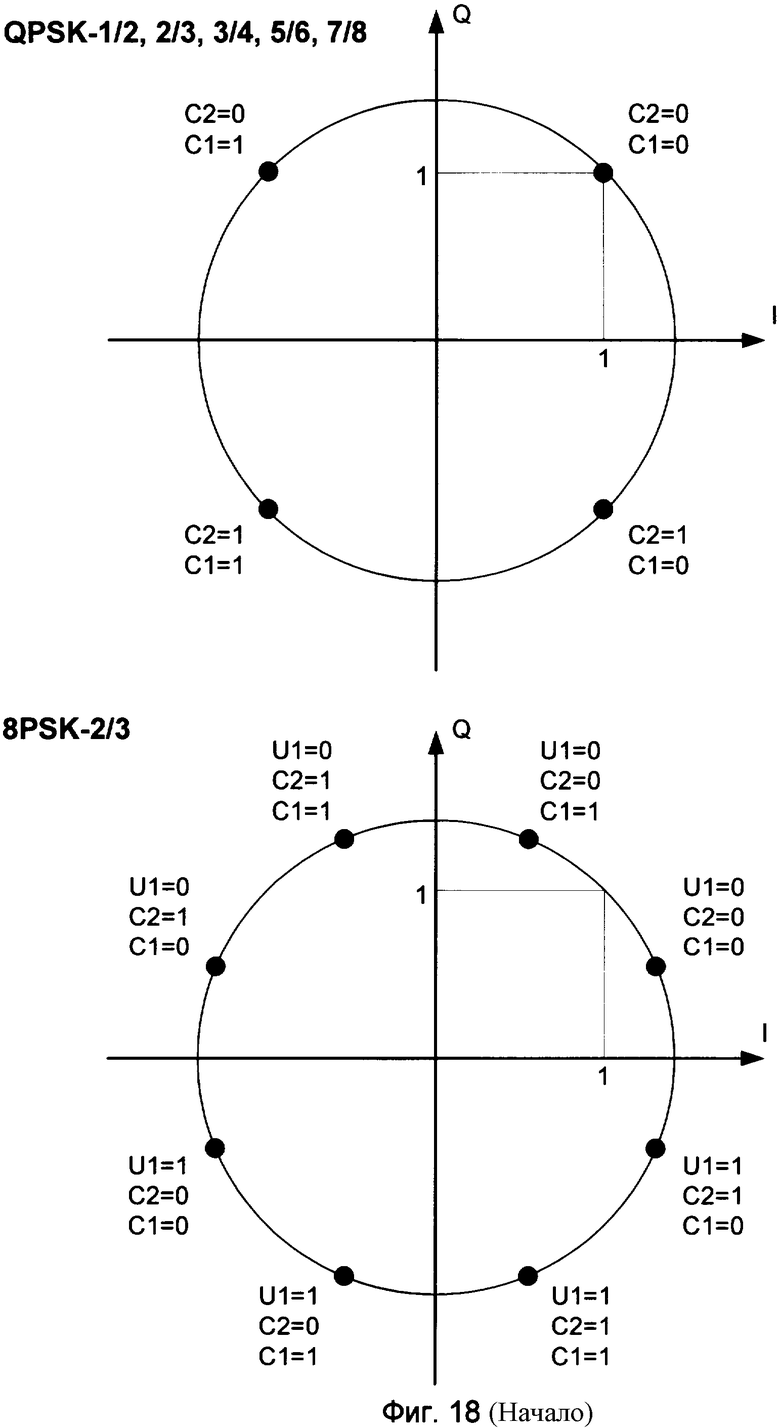

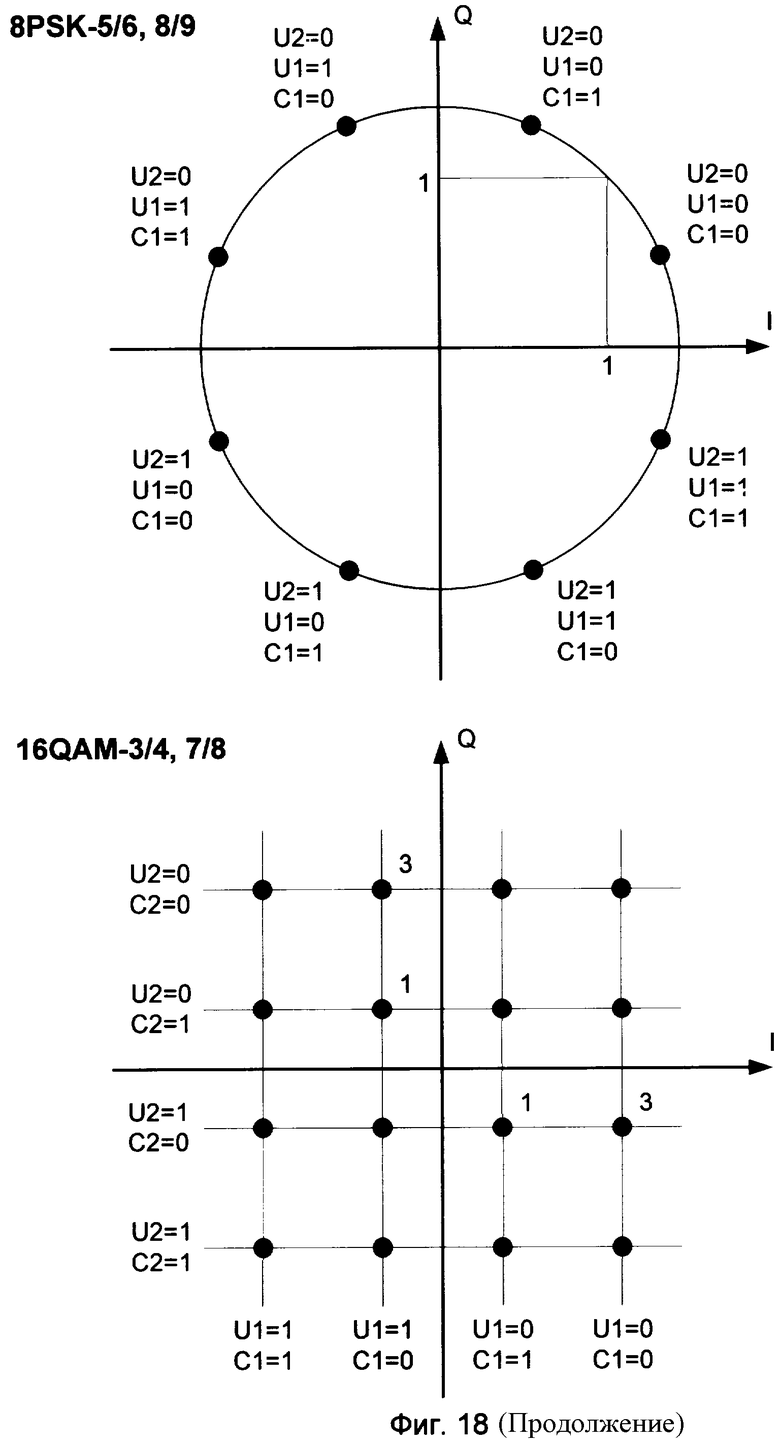

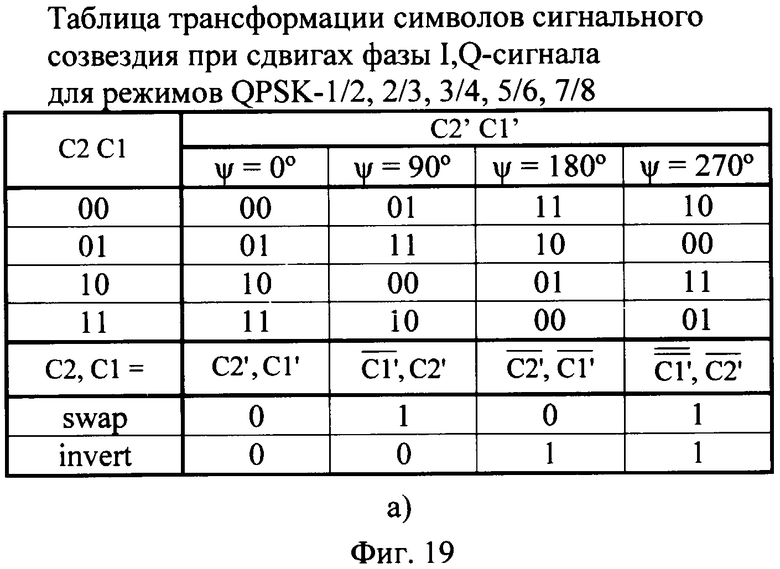

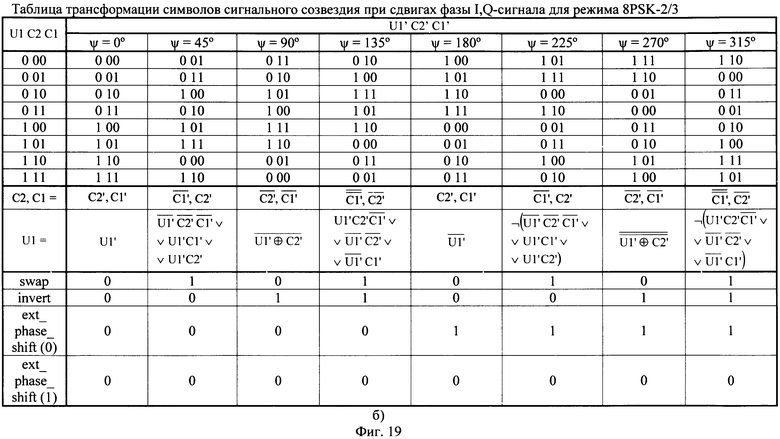

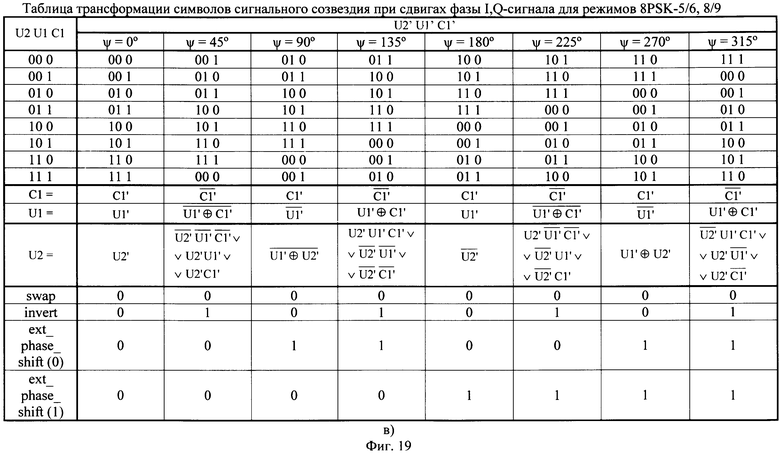

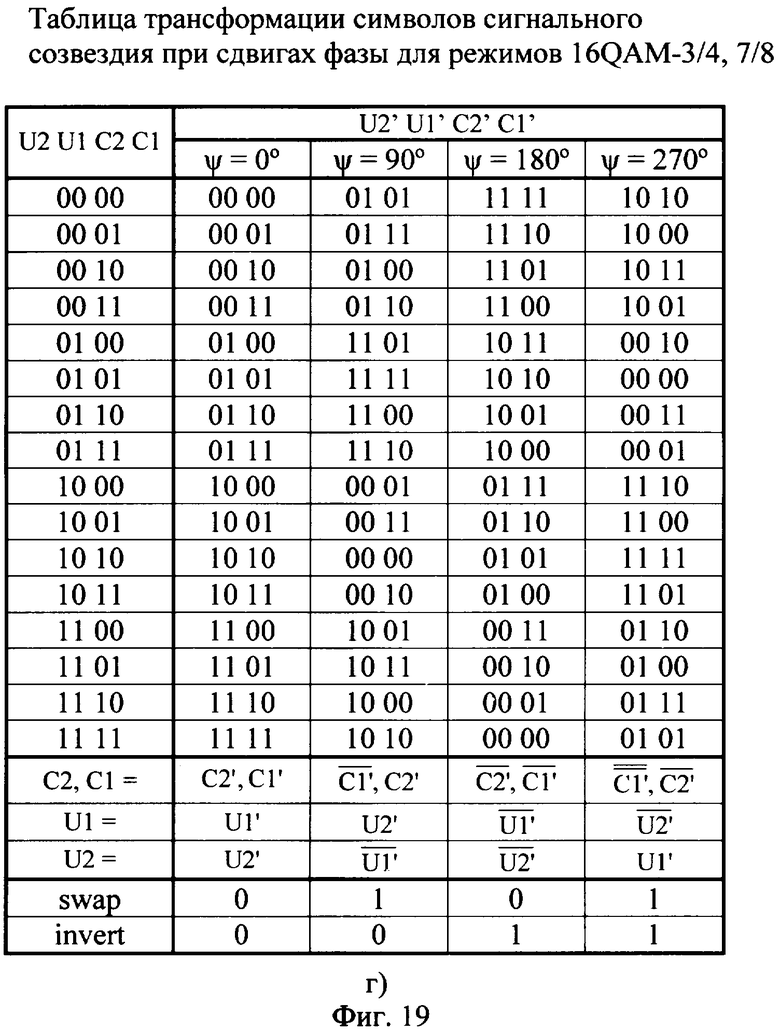

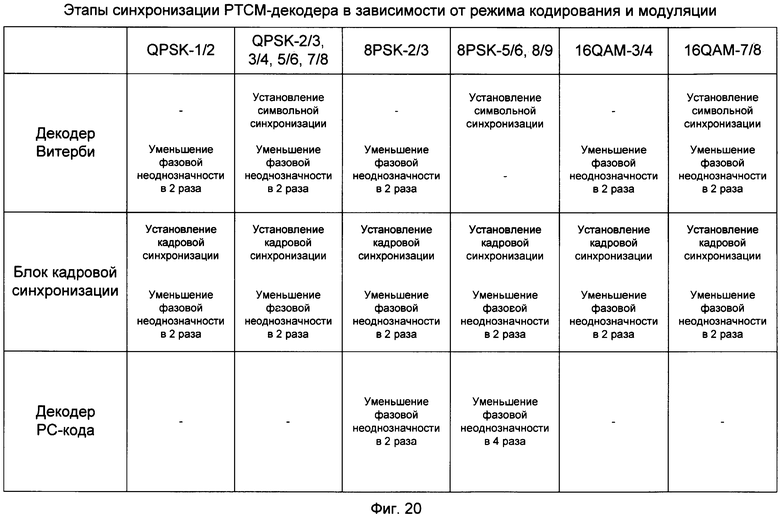

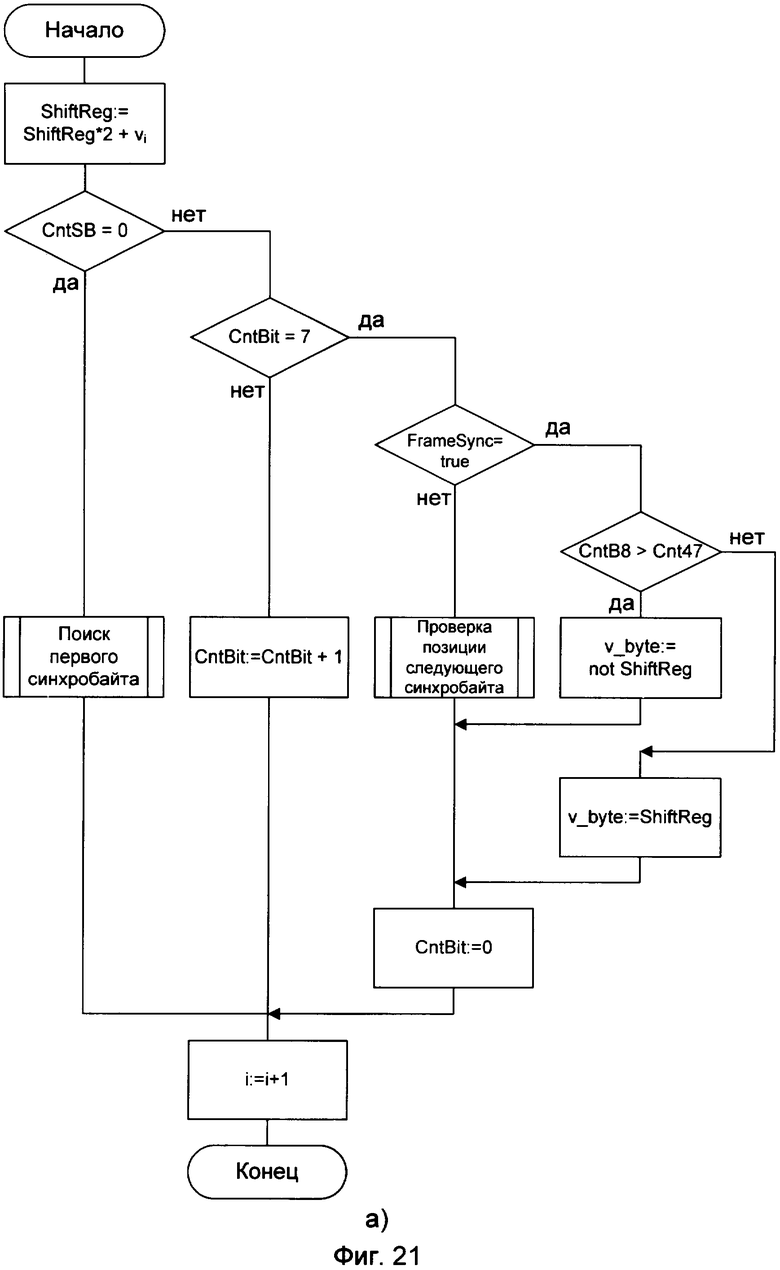

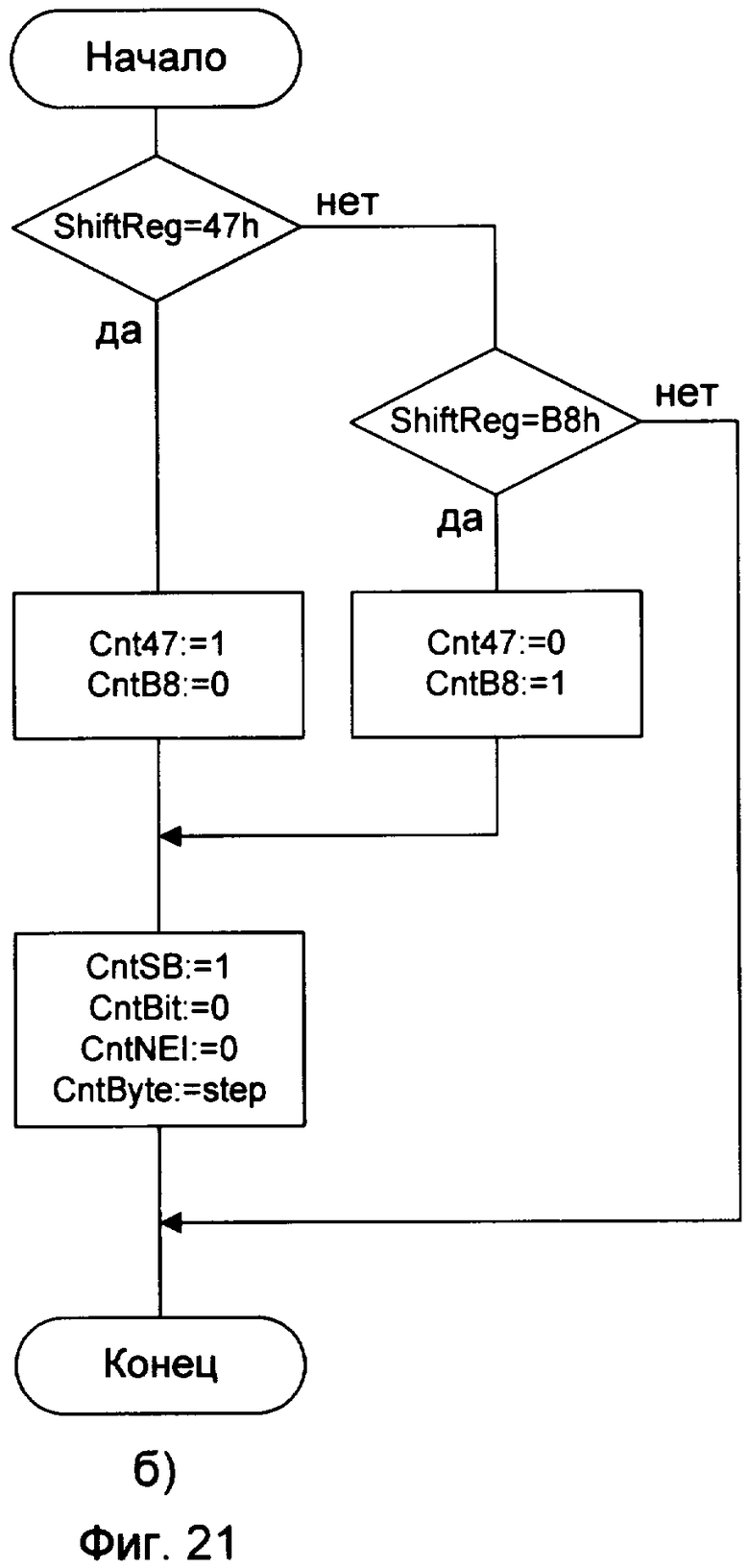

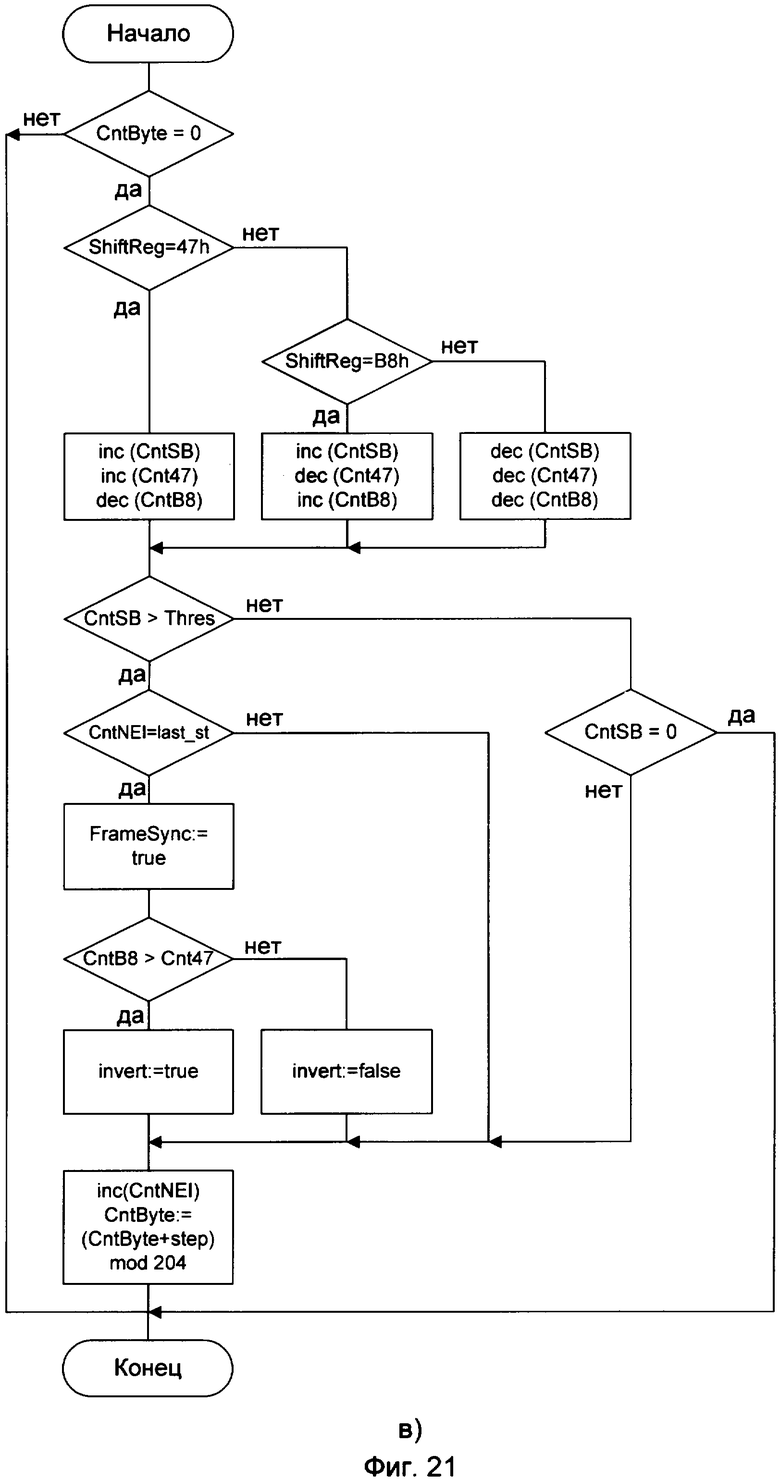

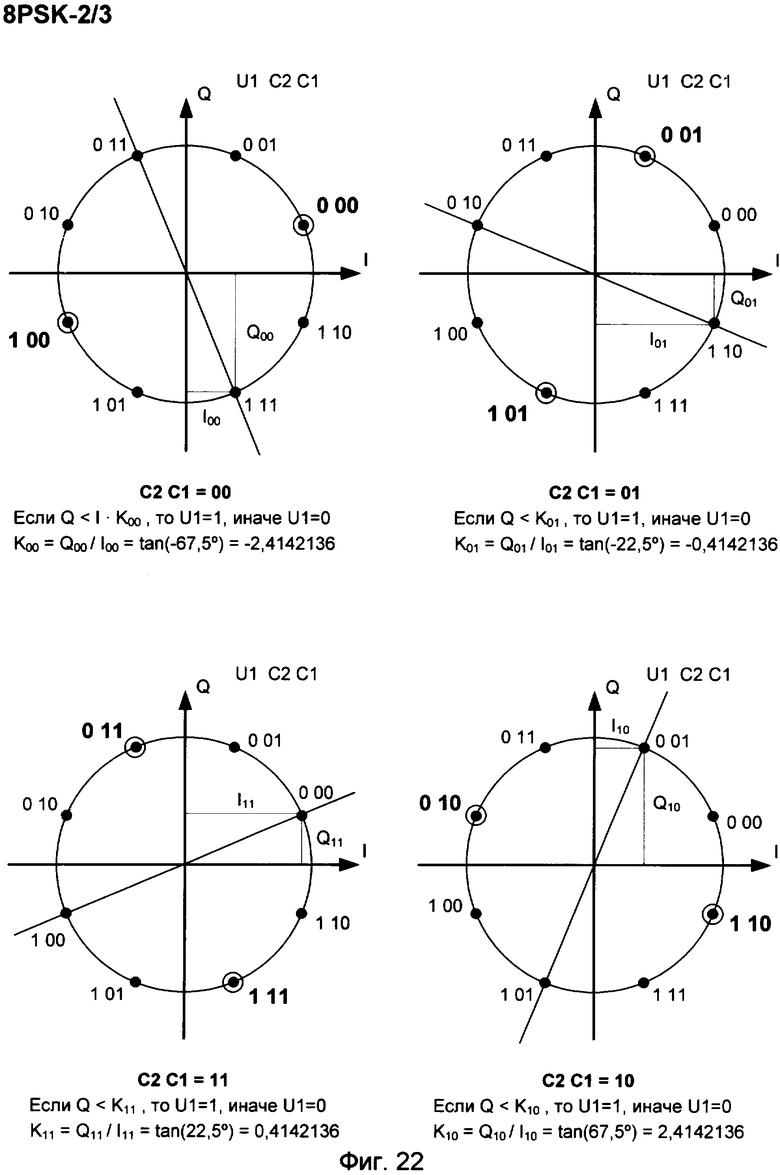

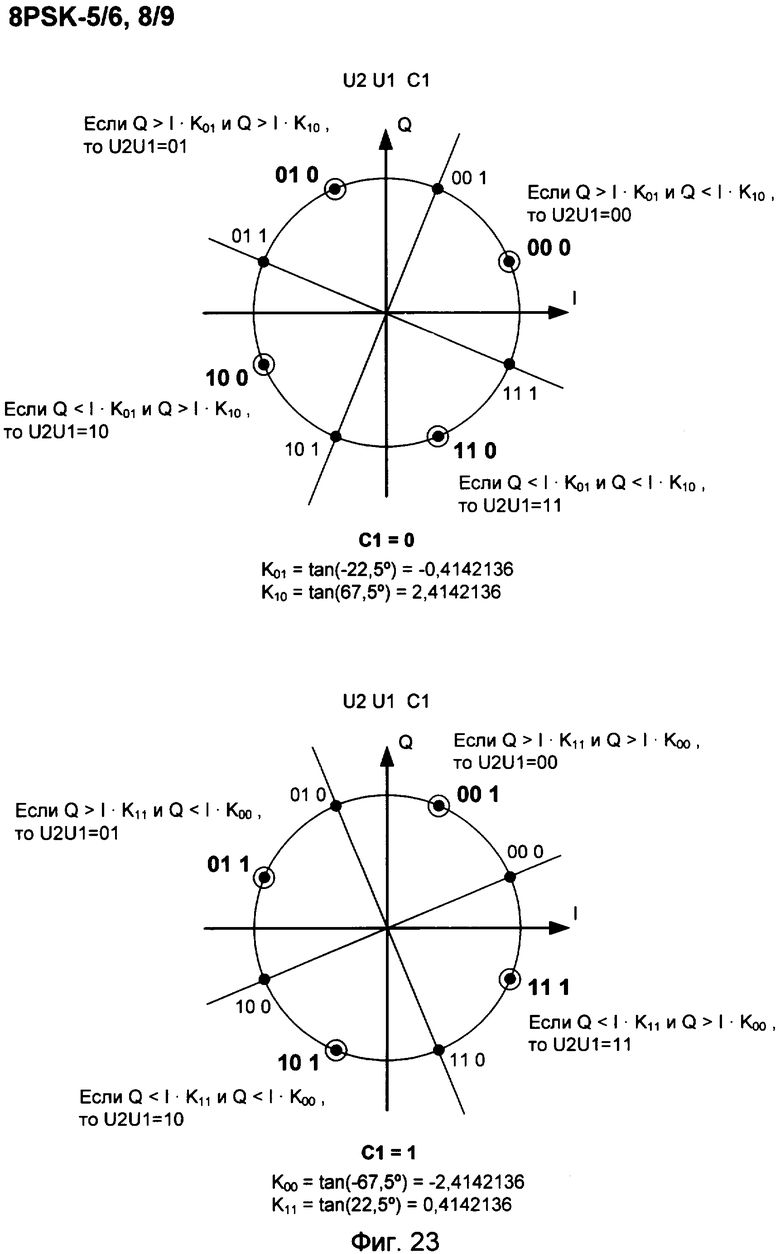

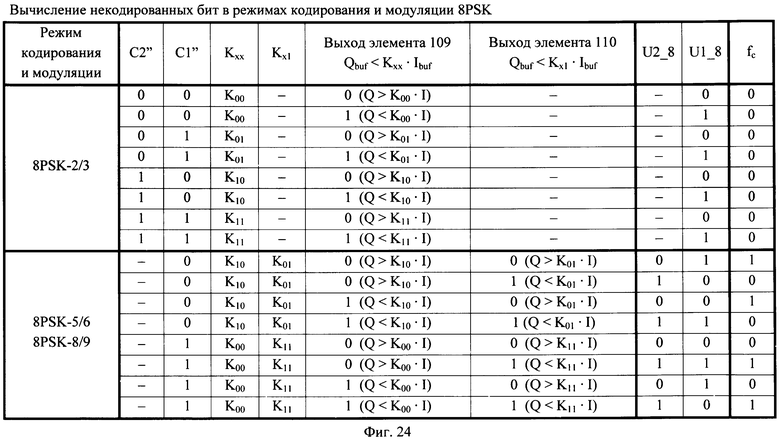

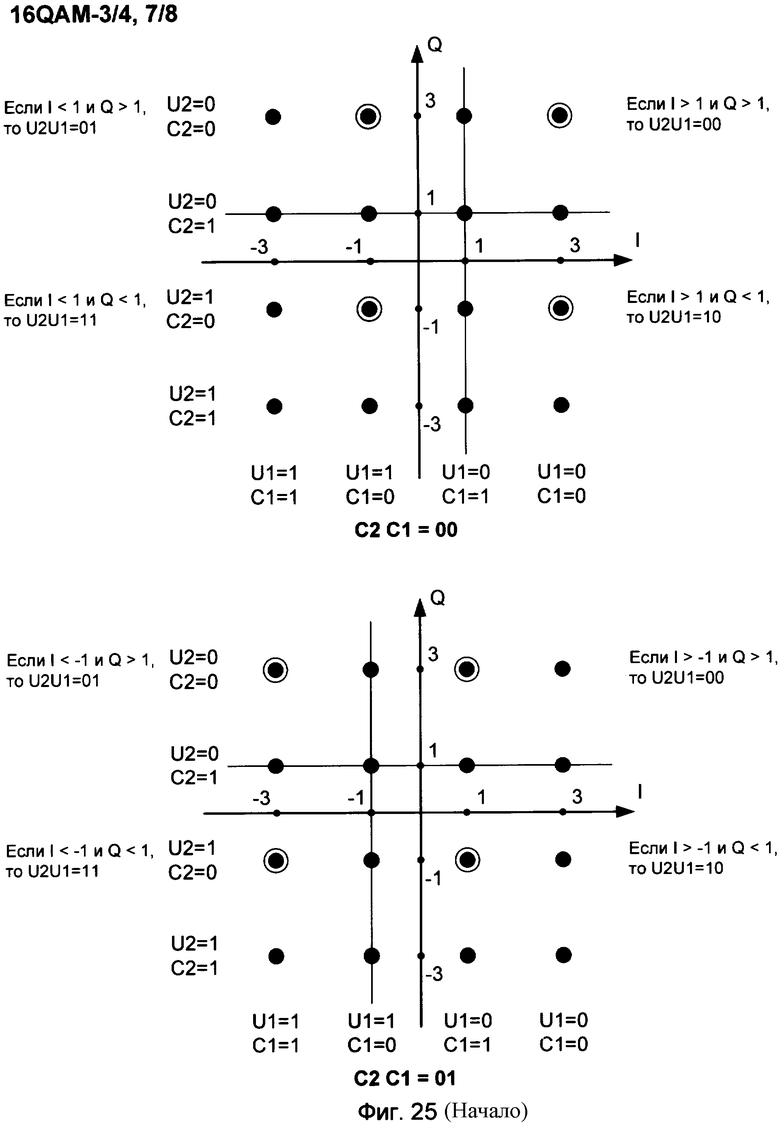

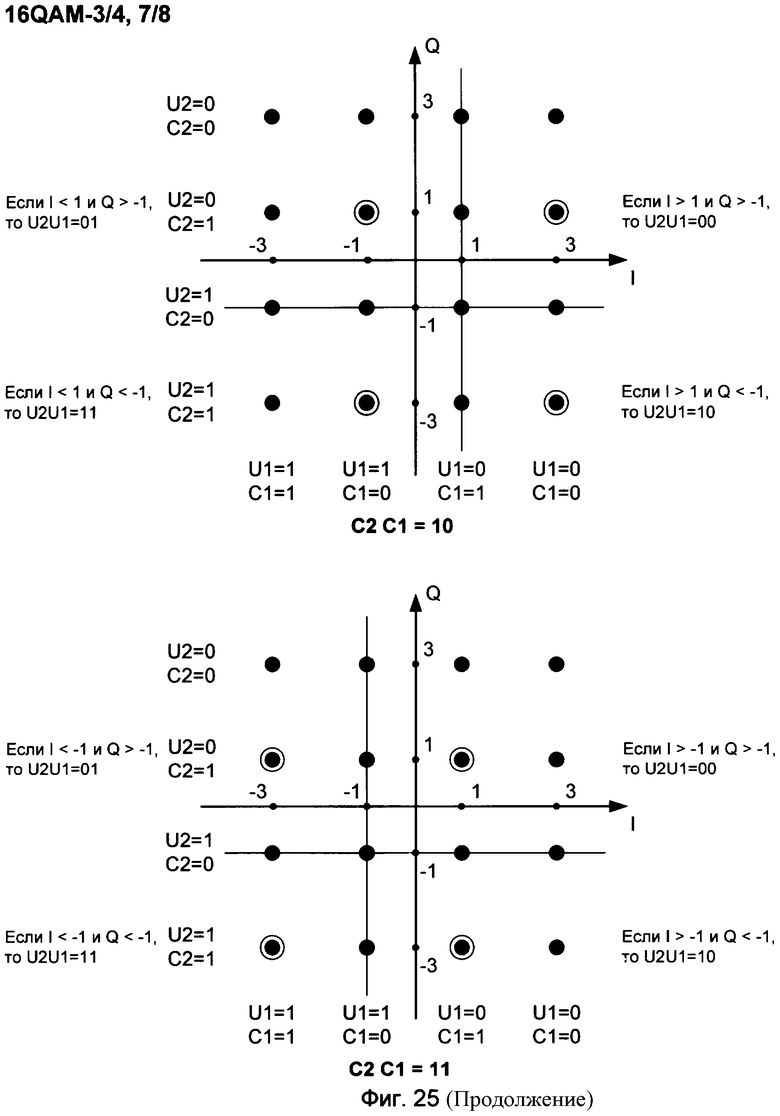

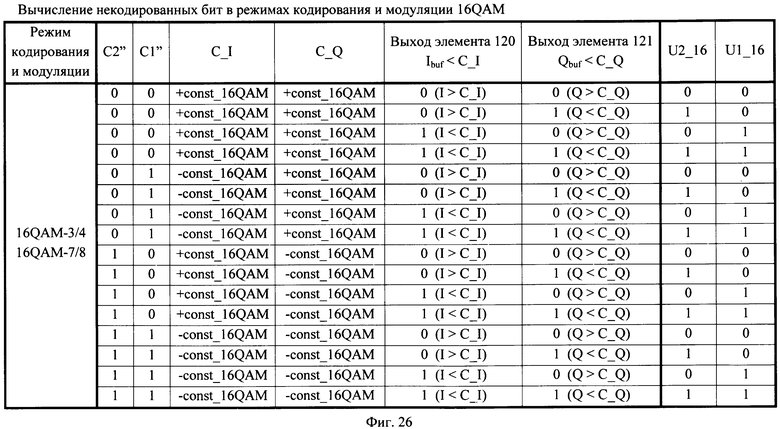

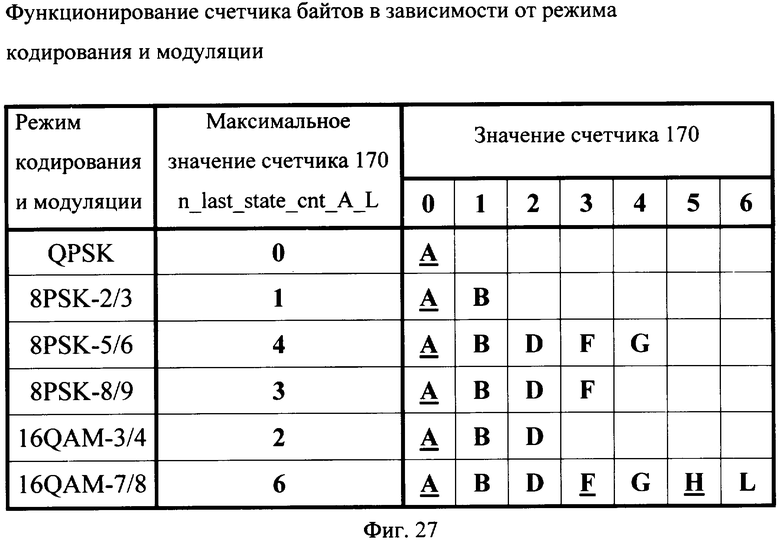

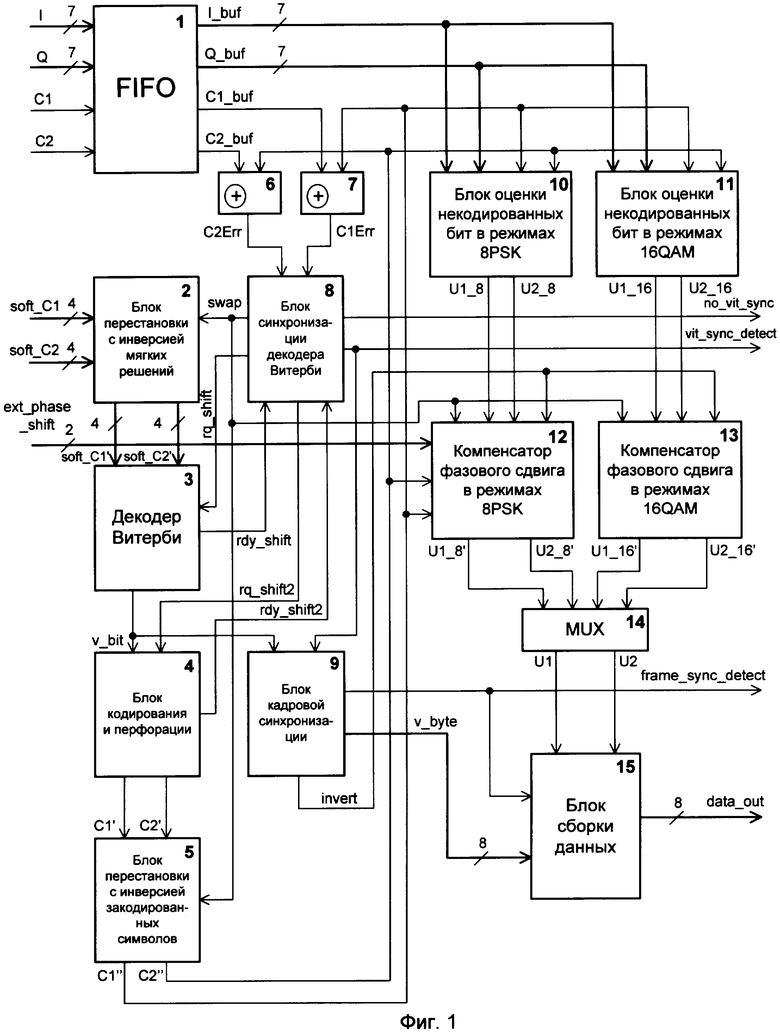

На фиг.1 приведена функциональная схема устройства декодирования РТСМ. На фиг.2 приведена функциональная схема блока перестановки с инверсией мягких решений. На фиг.3 приведена функциональная схема блока перестановки с инверсией закодированных символов. На фиг.4 приведена функциональная схема блока синхронизации декодера Витерби. На фиг.5 приведена функциональная схема блока кадровой синхронизации. На фиг.6 приведена функциональная схема блока оценки некодированных бит в режимах 8PSK. На фиг.7 приведена функциональная схема блока оценки некодированных бит в режимах 16QAM. На фиг.8 приведена функциональная схема компенсатора фазового сдвига в режимах 8PSK. На фиг.9 приведена функциональная схема компенсатора фазового сдвига в режимах 16QAM. На фиг.10 приведена функциональная схема блока сборки данных. На фиг.11 приведена структурная схема системы передачи данных по стандарту DVB-DSNG. На фиг.12 приведен формат передачи данных систем DVB-DSNG и DVB-S. На фиг.13 приведена структурная схема РТСМ-кодера системы DVB-DSNG. На фиг.14 приведена таблица, поясняющая принцип работы параллельно-параллельного преобразователя. На фиг.15 приведена функциональная схема кодера базового сверточного кода, применяемого в системах DVB-DSNG и DVB-S. На фиг.16 приведена таблица, определяющая перфорированные (выколотые) сверточные коды с различными скоростями, получаемые из базового сверточного кода со скоростью 1/2 в соответствии со стандартами DVB-DSNG и DVB-S. На фиг.17 приведена таблица, поясняющая принцип преобразования данных символьным секвенсором. На фиг.18 приведены сигнальные созвездия для различных режимов кодирования и модуляции, применяемых в системе DVB-DSNG. На фиг.19 приведены таблицы трансформации символов сигнального созвездия при сдвигах фазы I,Q-сигнала для различных режимов кодирования и модуляции. На фиг.20 приведено содержание этапов синхронизации РТСМ-декодера в зависимости от режима кодирования и модуляции. На фиг.21 приведена блок-схема алгоритма установления кадровой синхронизации. На фиг.22 приведены решающие правила для восстановления некодированных бит в режиме 8PSK-2/3. На фиг.23 приведены решающие правила для режимов 8PSK-5/6,8/9. На фиг.24 приведена таблица, поясняющая вычисление некодированных бит в режимах кодирования и модуляции 8PSK. На фиг.25 приведены решающие правила для режимов 16QAM-3/4, 7/8. На фиг.26 приведена таблица, поясняющая вычисление некодированных бит в режимах кодирования и модуляции 16QAM. На фиг.27 приведена таблица, поясняющая функционирование счетчика байтов блока сборки данных в зависимости от режима кодирования и модуляции.

В описании устройства и на чертежах используются следующие обозначения:

ETSI - European Telecommunications Standards Institute (Европейский институт стандартизации в электросвязи);

DVB-S - Digital Video Broadcasting - Satellite (аббревиатура, принятая в стандартах ETSI для обозначения системы спутникового цифрового видео (телевизионного) вещания);

DVB-DSNG - Digital Video Broadcasting - Digital Satellite News Gathering (аббревиатура, принятая в стандартах ETSI для обозначения спутниковой системы сбора новостей с цифровой передачей);

РТСМ - Pragmatic Trellis Coded Modulation (практическая решетчатая кодовая модуляция);

M-PSK - M-ary Phase Shift Keying (М-фазная манипуляция);

QPSK - Quaternary Phase Shift Keying (четырехфазная манипуляция);

8PSK - Eight Phase Shift Keying (восьмифазная манипуляция);

QAM - Quadrature Amplitude Modulation (квадратурная амплитудная модуляция);

16QAM-Sixteen Quadrature Amplitude Modulation (16-точечная квадратурная амплитудная модуляция);

СК - сверточный код;

1CBPS - 1 Coded Bit Per Symbol (один закодированный бит на символ);

2CBPS - 2 Coded Bits Per Symbol (два закодированных бита на символ);

PC-код - код Рида-Соломона;

FIFO - буферная память для задержки данных (например, набор регистров, последовательно соединенных m-разрядными шинами);

Т-триггер (RS-триггер, D-триггер, Т-триггер);

RG - буферный регистр, регистр сдвига;

MUX - мультиплексор;

SM - сумматор;

SB - вычитатель;

СТ2 - двоичный счетчик;

BF - шинный формирователь;

MUL - умножитель;

DC - дешифратор.

Устройство декодирования РТСМ (фиг.1) содержит буфер I,Q-компонент сигнала (1), блок перестановки с инверсией мягких решений (2), декодер Витерби (3), блок кодирования и перфорации (4), блок перестановки с инверсией закодированных символов (5), первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ (6), второй элемент ИСКЛЮЧАЮЩЕЕ ИЛИ (7), блок синхронизации декодера Витерби (8), блок кадровой синхронизации (9), блок оценки некодированных бит в режимах 8PSK (10), блок оценки некодированных бит в режимах 16QAM (11), компенсатор фазового сдвига в режимах 8PSK (12), компенсатор фазового сдвига в режимах 16QAM (13), мультиплексор некодированных данных (14), блок сборки данных (15).

На входы буфера компонент I,Q-сигнала (1) подаются соответственно следующие входные данные: семиразрядная I-компонента I,Q-сигнала, семиразрядная Q-компонента I,Q-сигнала, одноразрядные "жесткие" решения С1 и С2. На первые и вторые входы блока перестановки с инверсией мягких решений (2) подаются соответственно следующие входные данные: четырехразрядные "мягкие" решения soft_C1 и soft_C2.

Первые и вторые выходы блока перестановки с инверсией мягких решений (2) соединены соответственно с первыми и вторыми входами декодера Витерби (3). Первый выход декодера Витерби (3) соединен с первым входом блока кодирования и перфорации (4) и с первым входом блока кадровой синхронизации (9). Первый и второй выходы блока кодирования и перфорации (4) соединены соответственно с первым и вторым входами блока перестановки с инверсией закодированных символов (5). Первый выход блока перестановки с инверсией закодированных символов (5) соединен со вторым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ (7), с третьим входом блока оценки некодированных бит в режимах 8PSK (10), с третьим входом блока оценки некодированных бит в режимах 16QAM (11) и с седьмым входом компенсатора фазового сдвига в режимах 8PSK (12).

Второй выход блока перестановки с инверсией закодированных символов (5) соединен со вторым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ (6), с четвертым входом блока оценки некодированных бит в режимах 8PSK (10), с четвертым входом блока оценки некодированных бит в режимах 16QAM (11) и с шестым входом компенсатора фазового сдвига в режимах 8PSK (12).

Первые выходы буфера I,Q-компонент сигнала (1) соединены с первыми входами блока оценки некодированных бит в режимах 8PSK (10) и с первыми входами блока оценки некодированных бит в режимах 16QAM (11). Вторые выходы буфера I,Q-компонент сигнала (1) соединены со вторыми входами блока оценки некодированных бит в режимах 8PSK (10) и со вторыми входами блока оценки некодированных бит в режимах 16QAM (11). Третий выход буфера I,Q-компонент сигнала (1) соединен с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ (7). Четвертый выход буфера I,Q-компонент сигнала (1) соединен с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ (6). Выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ (6) соединен с первым входом блока синхронизации декодера Витерби (8), выход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ (7) соединен со вторым входом блока синхронизации декодера Витерби (8).

Первый выход блока синхронизации декодера Витерби (8) соединен с третьим входом блока перестановки с инверсией мягких решений (2), с третьим входом блока перестановки с инверсией закодированных символов (5), с первым входом компенсатора фазового сдвига в режимах 8PSK (12) и с первым входом компенсатора фазового сдвига в режимах 16QAM (13). Второй выход блока синхронизации декодера Витерби (8) соединен с третьим входом декодера Витерби (3). Второй выход декодера Витерби (3) соединен с третьим входом блока синхронизации декодера Витерби (8). Третий выход блока синхронизации декодера Витерби (8) является выходом no_vit_sync

устройства декодирования РТСМ. Четвертый выход блока синхронизации декодера Витерби (8) соединен со вторым входом блока кадровой синхронизации (9) и является выходом vit_sync_detect устройства декодирования РТСМ. Пятый выход блока синхронизации декодера Витерби (8) соединен со вторым входом блока кодирования и перфорации (4). Третий выход блока кодирования и перфорации (4) соединен с четвертым входом блока синхронизации декодера Витерби (8).

Первый выход блока кадровой синхронизации (9) соединен с четвертым входом компенсатора фазового сдвига в режимах 8PSK (12) и с четвертым входом компенсатора фазового сдвига в режимах 16QAM (13). Второй выход блока кадровой синхронизации (9) соединен с третьим входом блока сборки данных (15) и является выходом frame_sync_detect устройства декодирования РТСМ. Третьи выходы блока кадровой синхронизации (9) соединены с четвертыми входами блока сборки данных (15). Первый выход блока оценки некодированных бит в режимах 8PSK (10) соединен со вторым входом компенсатора фазового сдвига в режимах 8PSK (12). Второй выход блока оценки некодированных бит в режимах 8PSK (10) соединен с третьим входом компенсатора фазового сдвига в режимах 8PSK (12). Первый выход блока оценки некодированных бит в режимах 16QAM (11) соединен со вторым входом компенсатора фазового сдвига в режимах 16QAM (13). Второй выход блока оценки некодированных бит в режимах 16QAM (11) соединен с третьим входом компенсатора фазового сдвига в режимах 16QAM (13). Пятый вход компенсатора фазового сдвига в режимах 8PSK (12) является входом ext_phase_shift устройства декодирования РТСМ.

Первый выход компенсатора фазового сдвига в режимах 8PSK (12) соединен с первым входом мультиплексора некодированных данных (14). Второй выход компенсатора фазового сдвига в режимах 8PSK (12) соединен со вторым входом мультиплексора некодированных данных (14). Первый выход компенсатора фазового сдвига в режимах 16QAM (13) соединен с третьим входом мультиплексора некодированных данных (14). Второй выход компенсатора фазового сдвига в режимах 16QAM (13) соединен с четвертым входом мультиплексора некодированных данных (14). Первый выход мультиплексора некодированных данных (14) соединен с первым входом блока сборки данных (15), второй выход мультиплексора некодированных данных (14) соединен со вторым входом блока сборки данных (15). Первые выходы блока сборки данных (15) являются выходами data_out устройства декодирования РТСМ.

Блок перестановки с инверсией мягких решений (2) (фиг.2) содержит первый вычитатель (16), первый мультиплексор (17), второй мультиплексор (18), первый буферный регистр (19), второй буферный регистр (20). Управляющий вход первого мультиплексора (17) соединен с управляющим входом второго мультиплексора (18) и является третьим входом блока перестановки с инверсией мягких решений (2). Первые входы данных первого мультиплексора (17) соединены со входами вычитаемого первого вычитателя (16) и являются первыми входами блока перестановки с инверсией мягких решений (2). Вторые входы данных первого мультиплексора (17) соединены с первыми входами данных второго мультиплексора (18) и являются вторыми входами блока перестановки с инверсией мягких решений (2). Входы уменьшаемого первого вычитателя (16) соединены с шиной константы '15'. Выходы первого вычитателя (16) соединены со вторыми входами данных второго мультиплексора (18). Выходы первого мультиплексора (17) соединены со входами данных первого буферного регистра (19). Выходы второго мультиплексора (18) соединены со входами данных второго буферного регистра (20). Выходы первого буферного регистра (19) являются первыми выходами блока перестановки с инверсией мягких решений (2). Выходы второго буферного регистра (20) являются вторыми выходами блока перестановки с инверсией мягких решений (2).

Блок перестановки с инверсией закодированных символов (5) (фиг.3) содержит первый инвертор (21), третий мультиплексор (22), четвертый мультиплексор (23), первый D-триггер (24), второй D-триггер (25). Управляющий вход третьего мультиплексора (22) соединен с управляющим входом четвертого мультиплексора (23) и является третьим входом блока перестановки с инверсией закодированных символов (5). Первый вход данных третьего мультиплексора (22) соединен со входом первого инвертора (21) и является вторым входом блока перестановки с инверсией закодированных символов (5). Второй вход данных третьего мультиплексора (22) соединен со вторым входом данных четвертого мультиплексора (23) и является первым входом блока перестановки с инверсией закодированных символов (5). Выход первого инвертора (21) соединен с первым входом данных четвертого мультиплексора (23). Выход третьего мультиплексора (22) соединен с D-входом первого D-триггера (24). Выход четвертого мультиплексора (23) соединен с D-входом второго D-триггера (25). Выход первого D-триггера (24) является вторым выходом блока перестановки с инверсией закодированных символов (5). Выход второго D-триггера (25) является первым выходом блока перестановки с инверсией закодированных символов (5).

Блок синхронизации декодера Витерби (8) (фиг.4) содержит первый элемент И (26), второй элемент И (27), третий элемент И (28), четвертый элемент И (29), первый счетчик (30), первый RS-триггер (31), Т-триггер (32), пятый элемент И (33), первый элемент ИЛИ (34), первый компаратор (35), шестой элемент И (36), седьмой элемент И (37), третий элемент ИСКЛЮЧАЮЩЕЕ ИЛИ (38), восьмой элемент И (39), девятый элемент И (40), десятый элемент И (41), одиннадцатый элемент И (42), второй счетчик (43), пятый мультиплексор (44), второй RS-триггер (45), второй компаратор (46), двенадцатый элемент И (47), третий счетчик (48), третий RS-триггер (49), четвертый RS-триггер (50), четвертый счетчик (51), третий компаратор (52), тринадцатый элемент И (53), пятый RS-триггер (54).

Нулевой разряд первых входов первого компаратора (35) соединен с первым входом первого элемента И (26), первым, инверсным входом второго элемента И (27), первым входом первого элемента ИЛИ (34), с R-входом синхронного сброса Т-триггера (32), со вторым, инверсным входом седьмого элемента И (37) и соединен с шиной 8PSK_5689 устройства декодирования РТСМ. Разряды с первого по двенадцатый первых входов первого компаратора (35) соединены с шиной константы единицы, второй вход первого элемента И (26) соединен со вторым входом второго элемента И (27), с третьим входом пятого элемента И (33), со вторым входом третьего элемента И (28), с первым входом четвертого элемента И (29), со вторым входом девятого элемента И (40), со вторым входом десятого элемента И (41), со вторым входом одиннадцатого элемента И (42) и соединен с шиной C2C1_valid устройства декодирования РТСМ.

Выход первого элемента И (26) соединен со входом инкремента на единицу первого счетчика (30), выход второго элемента И (27) соединен со входом инкремента на два первого счетчика (30), инверсный R-вход асинхронного сброса первого счетчика (30) соединен с инверсным R-входом асинхронного сброса первого RS-триггера (31), с инверсным R-входом асинхронного сброса Т-триггера (32), с инверсным R-входом асинхронного сброса второго счетчика (43), с инверсным R-входом асинхронного сброса второго RS-триггера (45), с инверсным R-входом асинхронного сброса третьего счетчика (48), с инверсным R-входом асинхронного сброса третьего RS-триггера (49), с инверсным R-входом асинхронного сброса четвертого RS-триггера (50), с инверсным R-входом асинхронного сброса пятого RS-триггера (54), с инверсным R-входом асинхронного сброса четвертого счетчика (51) и соединен с шиной сброса reset устройства декодирования РТСМ. Выходы первого счетчика (30) соединены со вторыми входами первого компаратора (35), пятый разряд выходов первого счетчика (30) соединен с первым входом пятого элемента И (33), десятый разряд выходов первого счетчика (30) соединен со вторым входом пятого элемента И (33). Выход первого компаратора (35) соединен с первым входом третьего элемента И (28), с четвертым входом четвертого элемента И (29), с третьим входом одиннадцатого элемента И (42). Выход третьего элемента И (28) соединен с R-входом синхронного сброса первого RS-триггера (31), выход пятого элемента И (33) соединен с S-входом первого RS-триггера (31), выход четвертого элемента И (29) соединен с Т-входом Т-триггера (32) и со вторым входом шестого элемента И (36). Выход Т-триггера (32) соединен со вторым входом первого элемента ИЛИ (34) и является первым выходом блока синхронизации декодера Витерби (8). Выход первого элемента ИЛИ (34) соединен с первым входом шестого элемента И (36). Выход первого RS-триггера (31) соединен с инверсным R-входом синхронного сброса второго счетчика (43). Выход шестого элемента И (36) соединен со входом инкремента на единицу третьего счетчика (48), со вторым входом двенадцатого элемента И (47), с S-входом третьего RS-триггера (49), с S-входом четвертого RS-триггера (50), первый вход седьмого элемента И (37) является первым входом блока синхронизации декодера Витерби (8). Выход седьмого элемента И (37) соединен с первым входом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ (38) и с первым входом восьмого элемента И (39). Второй вход третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ (38) соединен со вторым входом восьмого элемента И (39) и является вторым входом блока синхронизации декодера Витерби (8).

Выход третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ (38) соединен с первым входом девятого элемента И (40). Выход восьмого элемента И (39) соединен с первым входом десятого элемента И (41). Выход девятого элемента И (40) соединен со входом инкремента на единицу второго счетчика (43). Выход десятого элемента И (41) соединен со входом инкремента на два второго счетчика (43). Выходы второго счетчика (43) соединены с первыми входами второго компаратора (46).

Первые входы, вторые входы, третьи входы, четвертые входы, пятые входы, шестые входы, седьмые входы, восьмые входы, девятые входы и десятые входы данных пятого мультиплексора (44) соединены соответственно с шинами thres_QPSK12, thres_QPSK23, thres_QPSK34, thres_QPSK56, thres_QPSK78, thres_8PSK23, thres_8PSK56, thres_8PSK89, thres_16QAM34, thres_16QAM78 устройства декодирования РТСМ. Управляющие входы пятого мультиплексора (44) соединены с шиной выбора режима кодирования и модуляции mode устройства декодирования РТСМ. Выходы пятого мультиплексора (44) соединены со вторыми входами второго компаратора (46). Выход второго компаратора (46) соединен с первым входом одиннадцатого элемента И (42) и со вторым, инверсным входом четвертого элемента И (29). Выход одиннадцатого элемента И (42) соединен с S-входом второго RS-триггера (45). Выход второго RS-триггера (45) соединен с третьим, инверсным входом четвертого элемента И (29) и является четвертым выходом блока синхронизации декодера Витерби (8). Первые входы третьего компаратора (52) соединены с шиной n_last_state_cnt_sym устройства декодирования РТСМ.

Выходы третьего счетчика (48) соединены со вторыми входами третьего компаратора (52). Выход третьего компаратора (52) соединен с R-входом синхронного сброса третьего счетчика (48) и с первым входом двенадцатого элемента И (47). Выход двенадцатого элемента И (47) соединен с первым входом тринадцатого элемента И (53) и со входом инкремента на единицу четвертого счетчика (51). R-вход третьего RS-триггера (49) является третьим входом блока синхронизации декодера Витерби (8). Выход третьего RS-триггера (49) является вторым выходом блока синхронизации декодера Витерби (8). R-вход четвертого RS-триггера (50) является четвертым входом блока синхронизации декодера Витерби (8). Выход четвертого RS-триггера (50) является пятым выходом блока синхронизации декодера Витерби (8). Нулевой разряд выходов четвертого счетчика (51) соединен со вторым входом тринадцатого элемента И (53), первый разряд выходов четвертого счетчика (51) соединен с третьим входом тринадцатого элемента И (53). Выход тринадцатого элемента И (53) соединен с S-входом пятого RS-триггера (54). Выход пятого RS-триггера (54) является третьим выходом блока синхронизации декодера Витерби (8).

Блок кадровой синхронизации (9) (фиг.5) содержит первый регистр сдвига (55), селектор кода '47h' (56), селектор кода 'B8h' (57), второй элемент ИЛИ (58), четырнадцатый элемент И (59), пятнадцатый элемент И (60), шестнадцатый элемент И (61), семнадцатый элемент И (62), третий элемент ИЛИ (63), восемнадцатый элемент И (64), четвертый элемент ИЛИ (65), девятнадцатый элемент И (66), пятый элемент ИЛИ (67), двадцатый элемент И (68), шестой элемент ИЛИ (69), пятый счетчик (70), шестой счетчик (71), седьмой счетчик (72), восьмой счетчик (73), четвертый компаратор (74), первый дешифратор (75), селектор кода '7h' (76), двадцать первый элемент И (77), блок инверторов (78), шестой RS-триггер (79), седьмой элемент ИЛИ (80), двадцать второй элемент И (81), двадцать третий элемент И (82), двадцать четвертый элемент И (83), двадцать пятый элемент И (84), восьмой элемент ИЛИ (85), первый шинный формирователь (86), второй шинный формирователь (87), третий шинный формирователь (88), четвертый шинный формирователь (89), пятый шинный формирователь (90), шестой шинный формирователь (91), седьмой шинный формирователь (92), шестой мультиплексор (93), девятый счетчик (94), сумматор (95), седьмой мультиплексор (96), девятый элемент ИЛИ (97), пятый компаратор (98), второй вычитатель (99), третий буферный регистр (100), восьмой мультиплексор (101), селектор нулевого кода (102).

Вход первого регистра сдвига (55) является первым входом блока кадровой синхронизации (9). Выходы первого регистра сдвига (55) соединены со входами данных блока инверторов (78), со входами селектора кода '47h' (56) и со входами селектора кода 'B8h' (57). Выход селектора кода '47h' (56) соединен со вторым входом четырнадцатого элемента И (59) и с первым, инверсным входом пятнадцатого элемента И (60). Выход селектора кода 'B8h' (57) соединен со вторым входом шестнадцатого элемента И (61) и с первым, инверсным входом семнадцатого элемента И (62). Первый вход четырнадцатого элемента И (59) соединен с первым входом шестнадцатого элемента И (61), с инверсным R-входом синхронного сброса шестого RS-триггера (79), с инверсным R-входом синхронного сброса седьмого счетчика (72) и является вторым входом блока кадровой синхронизации (9). Выход четырнадцатого элемента И (59) соединен со входом инкремента на единицу пятого счетчика (70), со вторым входом пятого элемента ИЛИ (67), с первым входом двадцатого элемента И (68) и с первым входом шестого элемента ИЛИ (69). Выход пятнадцатого элемента И (60) соединен с первым входом третьего элемента ИЛИ (63). Выход шестнадцатого элемента И (61) соединен со вторым входом четвертого элемента ИЛИ (65), с первым входом девятнадцатого элемента И (66), со входом инкремента на единицу шестого счетчика (71) и со вторым входом шестого элемента ИЛИ (69). Выход семнадцатого элемента И (62) соединен со вторым входом третьего элемента ИЛИ (63). Выход третьего элемента ИЛИ (63) соединен с первым входом четвертого элемента ИЛИ (65), с первым входом пятого элемента ИЛИ (67) и со входом декремента на единицу седьмого счетчика (72). Выход четвертого элемента ИЛИ (65) соединен со входом декремента на единицу пятого счетчика (70). Выход девятнадцатого элемента И (66) соединен с R-входом синхронного сброса пятого счетчика (70). Выход пятого элемента ИЛИ (67) соединен со входом декремента на единицу шестого счетчика (71). Выход двадцатого элемента И (68) соединен с R-входом синхронного сброса шестого счетчика (71). Выходы пятого счетчика (70) соединены с первыми входами четвертого компаратора (74). Выходы шестого счетчика (71) соединены со вторыми входами четвертого компаратора (74). Выход четвертого компаратора (74) соединен с управляющим входом блока инверторов (78) и является первым выходом блока кадровой синхронизации (9). Выходы блока инверторов (78) являются третьими выходами блока кадровой синхронизации (9). Выход шестого элемента ИЛИ (69) соединен со входом инкремента на единицу седьмого счетчика (72) и с первым входом двадцать первого элемента И (77).

Выходы седьмого счетчика (72) соединены со входами первого дешифратора (75). Пятнадцатый разряд выходов первого дешифратора (75) соединен со вторым входом двадцать первого элемента И (77). Нулевой разряд выходов первого дешифратора (75) соединен с третьим, инверсным входом пятнадцатого элемента И (60), с третьим, инверсным входом семнадцатого элемента И (62), с первым входом второго элемента ИЛИ (58), со вторым входом девятнадцатого элемента И (66), со вторым входом двадцатого элемента И (68), с инверсным входом инкремента на единицу восьмого счетчика (73), с R-входом синхронного сброса восьмого счетчика (73), с первым, инверсным входом двадцать пятого элемента И (84), с первым входом восьмого элемента ИЛИ (85), со вторым входом седьмого элемента ИЛИ (80), с управляющим входом седьмого мультиплексора (96) и с первым входом девятого элемента ИЛИ (97). Выход второго элемента ИЛИ (58) соединен с третьим входом четырнадцатого элемента И (59) и с третьим входом шестнадцатого элемента И (61). Выход восемнадцатого элемента И (64) соединен со вторым входом пятнадцатого элемента И (60), со вторым входом семнадцатого элемента И (62), со вторым входом второго элемента ИЛИ (58) и с третьим входом двадцать первого элемента И (77). Выход двадцать первого элемента И (77) соединен с S-входом шестого RS-триггера (79) и с шиной SB_pos_out устройства декодирования РТСМ.

Выход шестого RS-триггера (79) соединен со вторым, инверсным входом восемнадцатого элемента И (64) и является вторым выходом блока кадровой синхронизации (9). Выходы восьмого счетчика (73) соединены со входами селектора кода '7h' (76). Выход селектора кода '7h' (76) соединен со вторым входом двадцать пятого элемента И (84), с первым входом двадцать второго элемента И (81) и со вторым входом девятого элемента ИЛИ (97). Управляющий вход шестого мультиплексора (93) соединен с первым входом двадцать третьего элемента И (82), со вторым входом двадцать четвертого элемента И (83) и с шиной 16QAM78 устройства декодирования РТСМ.

Первые входы данных шестого мультиплексора (93) соединены с шиной константы '0', вторые входы данных шестого мультиплексора (93) соединены с шиной константы '2'. Выходы шестого мультиплексора (93) соединены с первыми входами пятого компаратора (98). Выход двадцать пятого элемента И (84) соединен со входом инкремента на единицу девятого счетчика (94). Выход двадцать второго элемента И (81) соединен со вторым входом восьмого элемента ИЛИ (85). Выход восьмого элемента ИЛИ (85) соединен с R-входом синхронного сброса девятого счетчика (94). Выходы девятого счетчика (94) соединены со вторыми входами пятого компаратора (98). Выход пятого компаратора (98) соединен с четвертым входом двадцать первого элемента И (77), со вторым входом двадцать второго элемента И (81) и с первым входом седьмого элемента ИЛИ (80). Выход седьмого элемента ИЛИ (80) соединен со вторым, инверсным входом двадцать третьего элемента И (82) и с первым входом двадцать четвертого элемента И (83).

Входы данных первого шинного формирователя (86) соединены с шиной константы '2'. Управляющий вход первого шинного формирователя (86) соединен с шиной 8PSK23 устройства декодирования РТСМ. Входы данных второго шинного формирователя (87) соединены с шиной константы '5'. Управляющий вход второго шинного формирователя (87) соединен с шиной 8PSK56 устройства декодирования РТСМ. Входы данных третьего шинного формирователя (88) соединены с шиной константы '4'. Управляющий вход третьего шинного формирователя (88) соединен с шиной 8PSK89 устройства декодирования РТСМ. Входы данных четвертого шинного формирователя (89) соединены с шиной константы '2'. Выход двадцать третьего элемента И (82) соединен с управляющим входом четвертого шинного формирователя (89). Входы данных пятого шинного формирователя (90) соединены с шиной константы '3'. Выход двадцать четвертого элемента И (83) соединен с управляющим входом пятого шинного формирователя (90). Входы данных шестого шинного формирователя (91) соединены с шиной константы '1'. Управляющий вход шестого шинного формирователя (91) соединен с шиной QPSK устройства декодирования РТСМ. Входы данных седьмого шинного формирователя (92) соединены с шиной константы '3'. Управляющий вход седьмого шинного формирователя (92) соединен с шиной 16QAM34 устройства декодирования РТСМ. Выходы первого шинного формирователя (86) соединены с выходами второго шинного формирователя (87), с выходами третьего шинного формирователя (88), с выходами четвертого шинного формирователя (89), с выходами пятого шинного формирователя (90), с выходами шестого шинного формирователя (91), с выходами седьмого шинного формирователя (92), с тремя младшими разрядами первых входов сумматора (95) и с тремя младшими разрядами вторых входов данных седьмого мультиплексора (96). Пять старших разрядов первых входов сумматора (95) и пять старших разрядов вторых входов данных седьмого мультиплексора (96) соединены с шиной константы '0'. Выходы сумматора (95) соединены с восемью младшими разрядами входов уменьшаемого второго вычитателя (99) и со вторыми входами данных восьмого мультиплексора (101). Старший разряд входов уменьшаемого второго вычитателя (99) соединен с шиной константы '0'. Входы вычитаемого второго вычитателя (99) соединены с шиной константы '204'. Младшие разряды выходов второго вычитателя (99) соединены с первыми входами данных восьмого мультиплексора (101). Старший, знаковый разряд выходов второго вычитателя (99) соединен с управляющим входом восьмого мультиплексора (101). Выходы восьмого мультиплексора (101) соединены с первыми входами данных седьмого мультиплексора (96). Выходы седьмого мультиплексора (96) соединены со входами данных третьего буферного регистра (100). Выходы третьего буферного регистра (100) соединены со вторыми входами сумматора (95) и со входами селектора нулевого кода (102). Выход девятого элемента ИЛИ (97) соединен с управляющим входом третьего буферного регистра (100). Выход селектора нулевого кода (102) соединен с первым входом восемнадцатого элемента И (64).

Блок оценки некодированных бит в режимах 8PSK (10) (фиг.6) содержит второй инвертор (103), девятый мультиплексор (104), десятый мультиплексор (105), одиннадцатый мультиплексор (106), первый умножитель (107), второй умножитель (108), шестой компаратор (109), седьмой компаратор (110), двадцать шестой элемент И (111), двадцать седьмой элемент И (112), десятый элемент ИЛИ (113), двадцать восьмой элемент И (114), четвертый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ (115), третий D-триггер (116), четвертый D-триггер (117).

Управляющий вход девятого мультиплексора (104) соединен с первым, инверсным входом двадцать восьмого элемента И (114) и с шиной 8PSK23 устройства декодирования РТСМ. Первый вход двадцать шестого элемента И (111) соединен с первым, инверсным входом двадцать седьмого элемента И (112), со входом второго инвертора (103), с нулевым разрядом вторых входов данных девятого мультиплексора (104), с управляющим входом одиннадцатого мультиплексора (106) и является третьим входом блока оценки некодированных бит в режимах 8PSK (10).

Первый разряд вторых входов данных девятого мультиплексора (104) является четвертым входом данных блока оценки некодированных бит в режимах 8PSK (10). Нулевой разряд первых входов данных девятого мультиплексора (104) соединен с шиной константы '0'. Выход второго инвертора (103) соединен с первым разрядом первых входов данных девятого мультиплексора (104). Выходы девятого мультиплексора (104) соединены с управляющими входами десятого мультиплексора (105).

Первые входы данных десятого мультиплексора (105) соединены с шиной константы К00 устройства декодирования РТСМ. Вторые входы данных десятого мультиплексора (105) соединены с первыми входами данных одиннадцатого мультиплексора (106) и с шиной константы K01 устройства декодирования РТСМ. Третьи входы данных десятого мультиплексора (105) соединены с шиной константы К10 устройства декодирования РТСМ. Четвертые входы данных десятого мультиплексора (105) соединены со вторыми входами данных одиннадцатого мультиплексора (106) и с шиной константы К11 устройства декодирования РТСМ. Выходы десятого мультиплексора (105) соединены с первыми входами первого умножителя (107). Выходы одиннадцатого мультиплексора (106) соединены со вторыми входами второго умножителя (108). Вторые входы первого умножителя (107) соединены с первыми входами второго умножителя (108) и являются первыми входами блока оценки некодированных бит в режимах 8PSK (10). Выходы первого умножителя (107) соединены с первыми входами шестого компаратора (109). Выходы второго умножителя (108) соединены со вторыми входами седьмого компаратора (110). Вторые входы шестого компаратора (109) соединены с первыми входами седьмого компаратора (110) и являются вторыми входами блока оценки некодированных бит в режимах 8PSK (10).