Изобретение относится к технике электрических измерений и может быть использовано при построении высокоточных цифровых приборов.

Известны кодирующие преобразователи, предназначенные для точного измерения переменного напряжения и состоящие из управляющего устройства, электронного ключа, генератора импульсов, источника компенсирующего напряжения, счетчика импульсов, дешифратора, регистрирующего устройства, нуль-органа, управляемого делителя и программирующего блока. В данном кодирующем преобразователе для преобразования переменного напряжения в постоянное применен преобразователь средних значений. Постоянное напряжение Ux измеряется следующим образом. При поступлении пускового импульса от управляющего устройства открывается электронный ключ и к источнику компенсирующего напряжения поступают колебания от генератора импульсов, которые одновременно фиксируются счетчиком импульсов. Источник компенсирующего напряжения вырабатывает компенсирующее напряжение U, изменяющееся на A Lk с приходом каждого импульса от генератора импульсов. Процесс измерения сводится к подсчету счетчиком импульсов числа импульсов, прошедших через электронный ключ за определенное время, которое фиксируется нуль-органом. При срабатывании нуль-органа, когда входное напряжение Ux, поступающее на нуль-орган через управляемый делитель, станет равным компенсирующему напряжению UK, ключ запирается, генерирование A UK и счет импульсов прекращается, показания счетчика импульсов после дешифрации передаются на регистрирующее устройство.

Недостатком данного кодирующего преобразователя является низкая точность измерения среднеквадратических значений переменного сигнала (3-5)%, поскольку применяемый в устройстве преобразователь переменного напряжения в постоянное не предназначен для преобразования сигналов произвольной формы.

ы

si

Наиболее близким к предлагаемому является кодирующий преобразователь, состоящий из последовательно соединенных декадных преобразователей, выходы которых через устройство обработки подключены к цифровому индикатору, компаратора, блока определения диапазона, блока управления, счетчика циклов, формирователей узких и широких импульсов, схем И, ИЛИ и счетчиков. Измеряемое напряжение поступает на вход компаратора и через схему И на последовательно соединенные декадные преобразователи. На второй вход схемы И в зависимости от частоты входного сигнала поступают или узкие, или широкие импульсы, сформированные формирователями узких и широких импульсов, В компараторе после дифференцирования входного сигнала выделяется последовательность импульсов, соответствующая моментам перехода через ноль входного напряжения. По этой последовательности импульсов блок определения диапазона определяет частоту входного сигнала. Дальнейшая работа устройства зависит от частоты входного сигна- ла. Если частота входного сигнала находится в области нижних частот, формирователь широких импульсов вырабатывает импульсы определенной длительности, которые поступают на запуск декадных преоб- разователей. Кроме того, эти сигналы стробируют входной сигнал, поступающий на измерительный вход декадных преобразователей. Так как время преобразования декадных преобразователей меньше широкого строб-импульса, то за время его действия измеряется мгновенное значение входного сигнала,

Количество измерений мгновенных значений входного сигнала за его период зависит от частоты входного сигнала (при постоянном интервале At между сигналами запуска декадных преобразователей). В связи с этим в устройстве обработки, где производятся функциональные преобразования, необходимые для вычисления сред- неквадратического значения напряжения, вводится количество измерений мгновенных значений входного сигнала, проведенных за его период. Подсчет количества измерений производится счетчиком циклов.

При работе в области верхних частот в связи с тем, что декадные преобразователи не успевают закодировать мгновенное значение входного сигнала за время действия узкого строб-импульса, кодирование производится поэтапно. В первый период входного напряжения кодируется первый десятичный разряд этого напряжения, во второй период - второй разряд входного

напряжения и т.д. Выбор режима работы (поэтапное кодирование) при работе в области верхних частот осуществляется блоком определения диапазона.

Недостатком данного кодирующего

преобразователя является низкая точность измерения среднеквадратических значений переменных сигналов, порядка 1-2%. Это обусловлено тем, что измерение мгновен0 ных значений переменного сигнала (выборок) происходит на одном пределе измерения. Уровень сигналов (выборок) за период действия переменного сигнала изменяется в широком динамическом диапа5 зоне. Измеряемые сигналы (выборки) отличаются друг от друга по уровню на несколько порядков, причем число измерений, где уровень сигналов имеет один порядок с максимальным мгновенным значением вы0 борки, составляет примерно 70% от общего числа измерений за период действия входного сигнала на выбранном пределе измерения. Это приводит к тому, что погрешность преобразователя при измере5 нии среднеквадратических значений переменных сигналов, получаемых путем функциональных преобразований, составляет 1 -2 %.

Цель изобретения - повышение точно0 сти кодирующего преобразователя.

Поставленная цель достигается тем, что в кодирующий преобразователь, содержащий компаратор, вход которого является входом преобразователя, первый дешифра5 тор, выход которого подключен к входу индикатора и первый аналого-цифровой преобразователь, дополнительно введены генератор импульсов, второй, третий и четвертый дешифраторы, делители, счетчики,

0 регистры, триггер, вычитатель, сумматор, квадратор, блок деления, блок извлечения корны, второй аналого-цифровой преобразователь, программно-временной блок и формирователь интервала выборок, выход

5 компаратора и выход формирователя интервала выборок соединены соответственно с первым и вторым входами программно-временного блока, первый и второй выходы которого соединены с первыми входами

0 соответственно блока извлечения корня и первого блока элементов И, третий и четвертый выходы программно-временного блока соединены соответственно с первым и вторым входами блока деления, выход которого

5 соединен с вторым входом первого блока элементов И, выходы которого соединены с вторыми входами блока извлечения корня, пятый выход программно-временного блока соединен с первым входом первого регистра, выходы которого соединены непосредственно с первыми входами второго блока элементов И, входами второго дешифратора и через цифро-аналоговый преобразователь с первым входом вычитателя, выход которого соединен с первым входом перво- го аналого-цифрового преобразователя, выходы которого соединены с вторыми входами второго блока элементов И, шестой выход программно-временного блока соединен с вторым входом первого аналоге- цифрового преобразователя, первым входом второго аналого-цифрового преобразователя и входом триггера, выход которого соединен с первым входом первого счетчика, выходы которого соединены с первыми входами третьего блока элементов И, выходы которого соединены с третьими входами блока деления, седьмой и восьмой выходы программно-временного блока соединены соответственно с первым входом первого дешифратора и вторым входом третьего блока элементов И, девятый выход программно-временного блока соединен с первым входом четвертого блока элементов И, выходы которого соединены с четверты- ми входами блока деления, десятый и одиннадцатый выходы программно-временного блока соединены соответственно с первым и вторым входами сумматора, выходы которого соединены с вторыми входами четвер- того блока элементов И, двенадцатый выход программно-временного блока соединен с первым входом пятого блока элементов И, выходы которого соединены с первыми входами третьего дешифратора, выходы кото- рого соединены с соответствующими третьими входами сумматора, тринадцатый и четырнадцатый выходы программно-временного блока соединены соответственно с первым и вторым входами квадратора, вы- ходы которого соединены с вторыми входами пятого блока элементов И, пятнадцатый выход программно-временного блока соединен с третьим входом второго блока элементов И, выходы которого соединены с третьими входами квадратора, шестнадцатый, семнадцатый и восемнадцатый выходы программно-временного блока соединены соответственно с вторым входом первого счетчика, первым и вторым входами второго счетчика, выход которого соединен с первым входом четвертого дешифратора, выход которого соединен с первым входом второго регистра, выход которого соединен с первым входом формирователя интервала выборок, девятнадцатый, двадцатый, двадцать первый и двадцать второй выходы программно-временного блока соединены соответственно с вторым входом четвертого дешифратора, вторым входом второго регистра, вторым входом формирователя интервала выборок и третьим входом блока извлечения корня, выходы которого соединены с вторыми входами первого дешифратора, выход генератора импульсов соединен с входом первого делителя, первый, второй и третий выходы которого соединены соответственно с третьим входом второго счетчика, третьими входами формирователя интервала выборок и третьим входом первого аналого-цифрового преобразователя и вторым входом второго аналого-цифрового преобразователя, выходы второго дешифратора соединены с вторыми входами третьего дешифратора и первыми входами второго де лителя, второй вход которого подключен входу преобразователя, выход соединен с вторым входом вычитателя и с третьим входом второго аналого-цифрового преобразователя, выход которого соединен со вторыми входами первого регистра.

Повышение точности кодирующего преобразователя до 0,1-0,2% обусловлено тем, что измерение мгновенных значений выборок, изменяющихся в широком динамическом диапазоне производится на разных пределах, С этой целью сначала производится определение предела измерения кодирующего преобразователя, а затем измерение входного сигнала на выбранном пределе измерения.

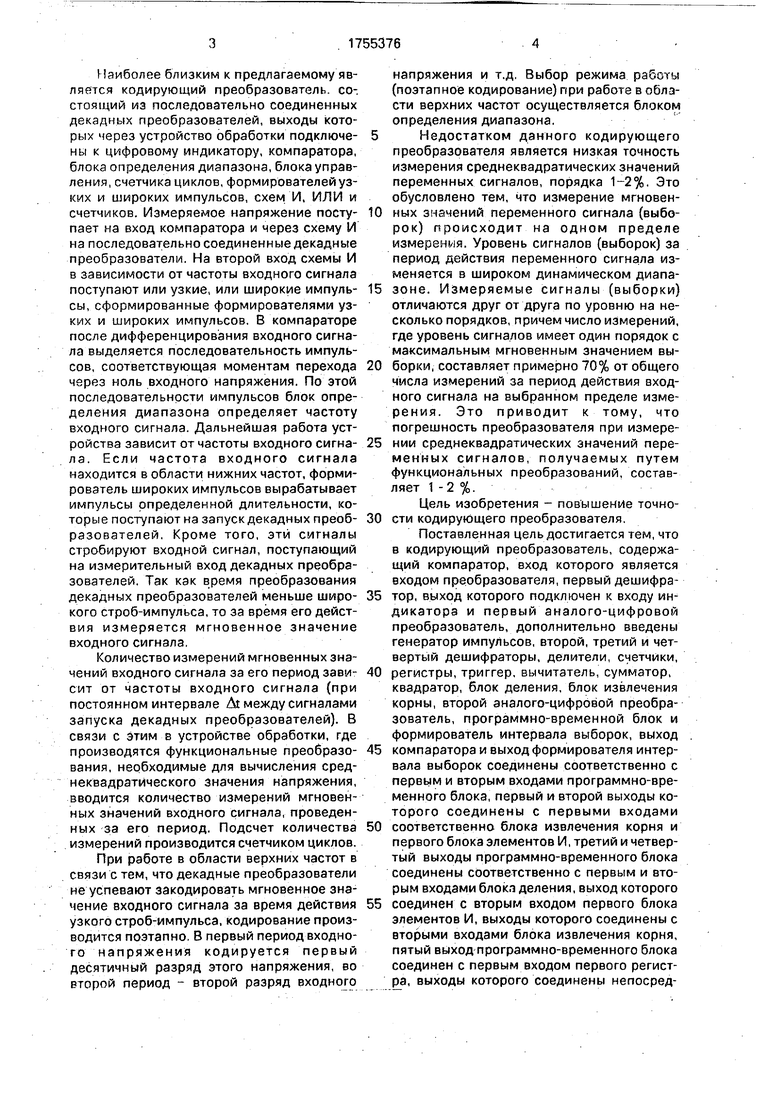

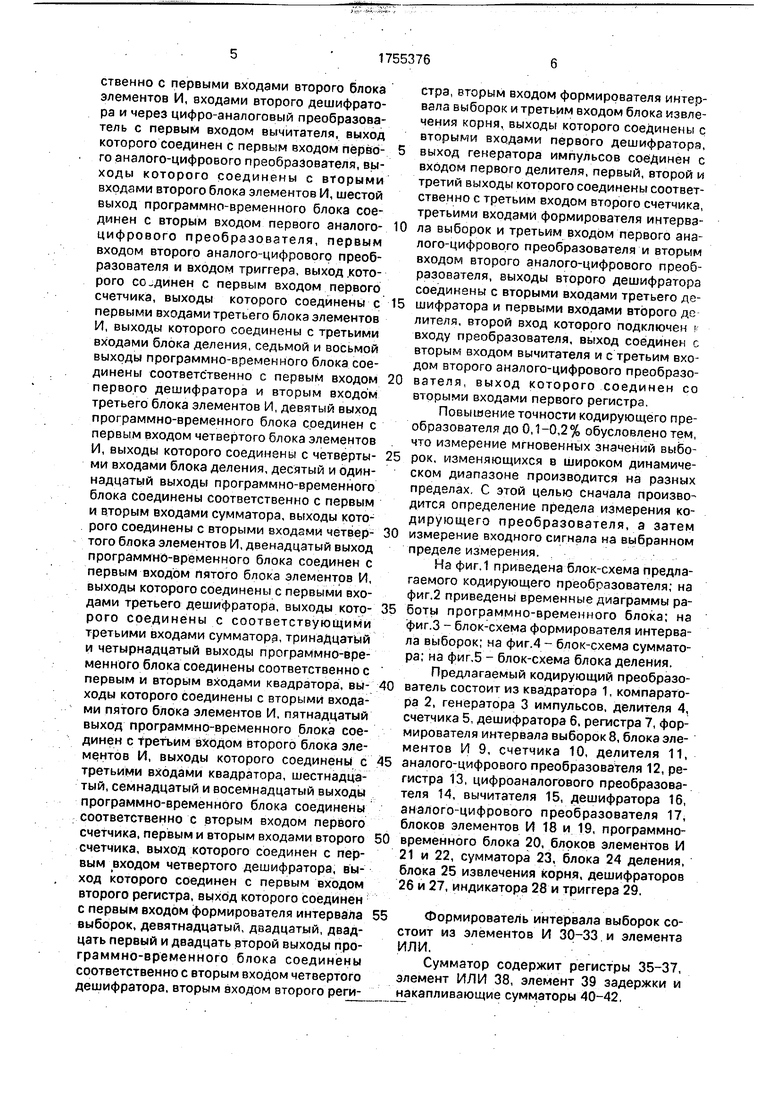

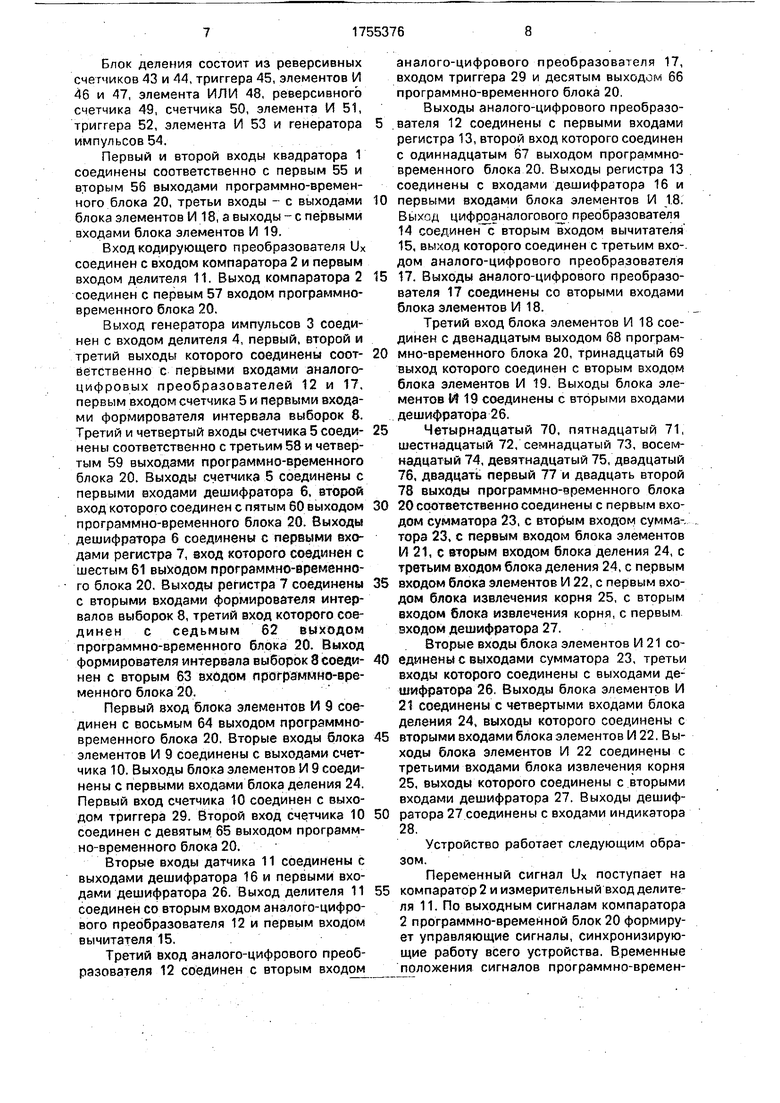

На фиг.1 приведена блок-схема предлагаемого кодирующего преобразователя; на фиг.2 приведены временные диаграммы работы программно-временного блока; на фиг.З - блок-схема формирователя интервала выборок; на фиг.4 - блок-схема сумматора; на фиг,5 - блок-схема блока деления.

Предлагаемый кодирующий преобразователь состоит из квадратора 1, компаратора 2, генератора 3 импульсов, делителя 4, счетчика 5, дешифратора б, регистра 7, формирователя интервала выборок 8, блока элементов И 9, счетчика 10, делителя 11, аналого-цифрового преобразователя 12, регистра 13, цифроаналогового преобразователя 14, вычитателя 15, дешифратора 16, аналого-цифрового преобразователя 17, блоков элементов И 18 и 19, программно- временного блока 20, блоков элементов И 21 и 22, сумматора 23, блока 24 деления, блока 25 извлечения корня, дешифраторов 26 и 27, индикатора 28 и триггера 29.

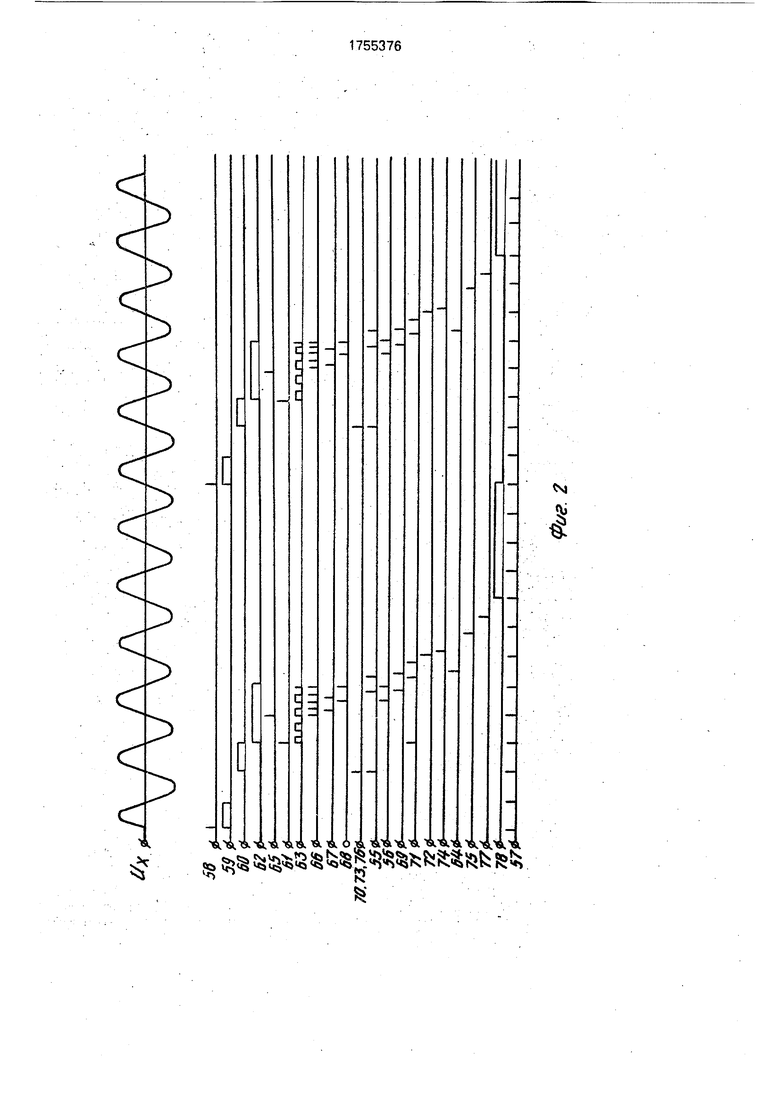

Формирователь интервала выборок состоит из элементов И 30-33 и элемента ИЛИ.

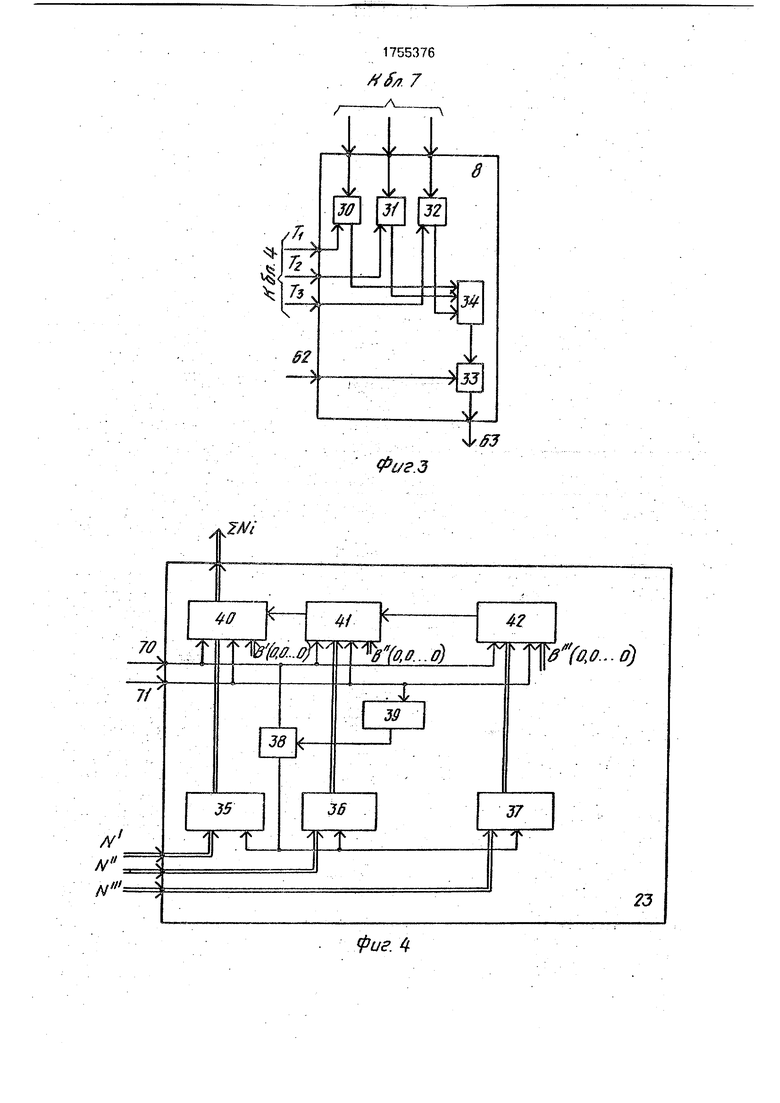

Сумматор содержит регистры 35-37, элемент ИЛИ 38, элемент 39 задержки и накапливающие сумматоры 40-42,

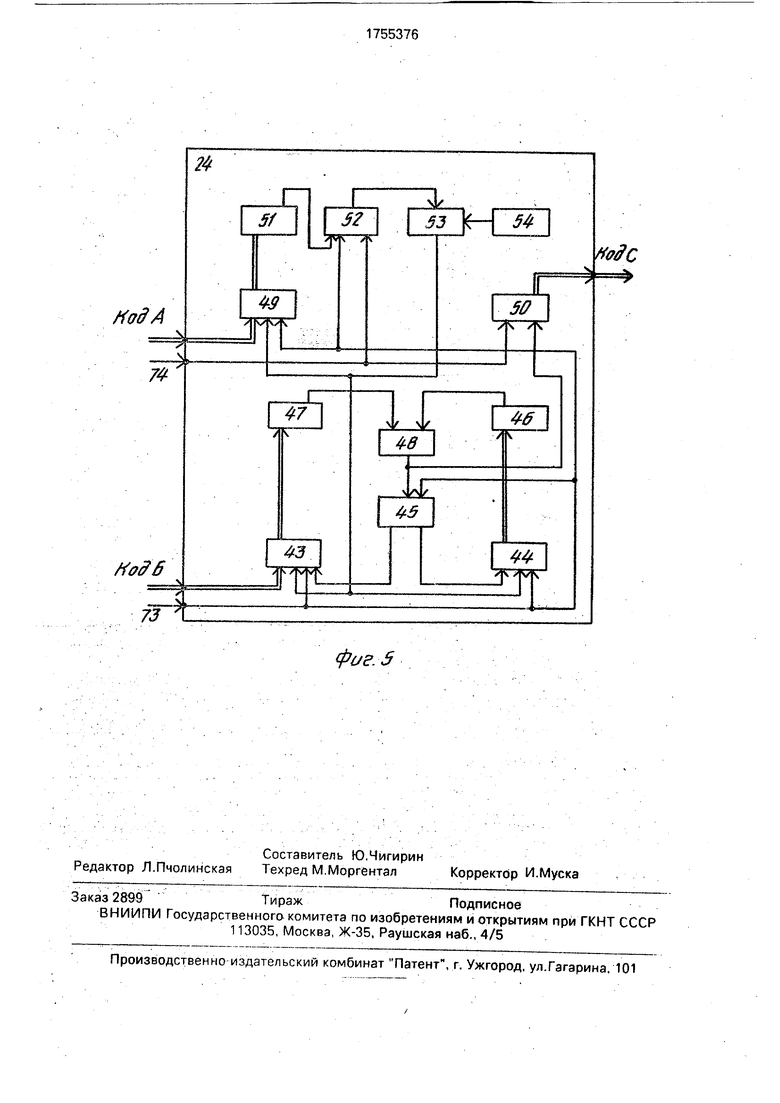

Блок деления состоит из реверсивных счетчиков 43 и 44, триггера 45, элементов И 46 и 47, элемента ИЛИ 48, реверсивного счетчика 49, счетчика 50, элемента И 51, триггера 52, элемента И 53 и генератора импульсов 54.

Первый и второй входы квадратора 1 соединены соответственно с первым 55 и вторым 56 выходами программно-временного блока 20, третьи входы - с выходами блока элементов И 18, а выходы - с первыми входами блока элементов И 19.

Вход кодирующего преобразователя Ux соединен с входом компаратора 2 и первым входом делителя 11. Выход компаратора 2 соединен с первым 57 входом программно- временного блока 20.

Выход генератора импульсов 3 соединен с входом делителя 4, первый, второй и третий выходы которого соединены соот- ветственно с первыми входами аналого- цифровых преобразователей 12 и 17, первым входом счетчика 5 и первыми входами формирователя интервала выборок 8. Третий и четвертый входы счетчика 5 соеди- нены соответственно с третьим 58 и четвертым 59 выходами программно-временного блока 20. Выходы счетчика 5 соединены с первыми входами дешифратора б, второй вход которого соединен с пятым 60 выходом программно-временного блока 20. Выходы дешифратора 6 соединены с первыми входами регистра 7, вход которого соединен с шестым 61 выходом программно-временного блока 20. Выходы регистра 7 соединены с вторыми входами формирователя интервалов выборок 8, третий вход которого соединен с седьмым 62 выходом программно-временного блока 20. Выход формирователя интервала выборок 8 соеди- нен с вторым 63 входом программно-временного блока 20.

Первый вход блока элементов И 9 соединен с восьмым 64 выходом программно- временного блока 20. Вторые входы блока элементов И 9 соединены с выходами счетчика 10. Выходы блока элементов И 9 соединены с первыми входами блока деления 24, Первый вход счетчика 10 соединен с выходом триггера 29. Второй вход счетчика 10 соединен с девятым 65 выходом программно-временного блока 20.

Вторые входы датчика 11 соединены с выходами дешифратора 16 и первыми входами дешифратора 26. Выход делителя 11 соединен со вторым входом аналого-цифрового преобразователя 12 и первым входом вычитателя 15.

Третий вход аналого-цифрового преобразователя 12 соединен с вторым входом

аналого-цифрового преобразователя 17, входом триггера 29 и десятым выходом 66 программно-временного блока 20.

Выходы аналого-цифрового преобразователя 12 соединены с первыми входами регистра 13, второй вход которого соединен с одиннадцатым 67 выходом программно- временного блока 20. Выходы регистра 13 соединены с входами дешифратора 16 и первыми входами блока элементов И 18. Выход цифроаналоговогр преобразователя 14 соединен с вторым входом вычитателя 15, выход которого соединен с третьим входом аналого-цифрового преобразователя 17. Выходы аналого-цифрового преобразователя 17 соединены со вторыми входами блока элементов И 18.

Третий вход блока элементов И 18 соединен с двенадцатым выходом 68 программно-временного блока 20, тринадцатый 69 выход которого соединен с вторым входом блока элементов И 19. Выходы блока элементов и 19 соединены с вторыми входами дешифратора 26.

Четырнадцатый 70, пятнадцатый 71, шестнадцатый 72, семнадцатый 73, восемнадцатый 74, девятнадцатый 75, двадцатый 76, двадцать первый 77 и двадцать второй 78 выходы программно-временного блока

20соответственно соединены с первым входом сумматора 23, с вторым входом сумматора 23, с первым входом блока элементов И 21, с вторым входом блока деления 24, с третьим входом блока деления 24, с первым входом блока элементов И 22, с первым входом блока извлечения корня 25, с вторым входом блока извлечения корня, с первым входом дешифратора 27.

Вторые входы блока элементов И 21 соединены с выходами сумматора 23, третьи входы которого соединены с выходами дешифратора 26. Выходы блока элементов И

21соединены с четвертыми входами блока деления 24, выходы которого соединены с вторыми входами блока элементов И 22. Выходы блока элементов И 22 соединены с третьими входами блока извлечения корня 25, выходы которого соединены с вторыми входами дешифратора 27. Выходы дешифратора 27 соединены с входами индикатора 28.

Устройство работает следующим образом.

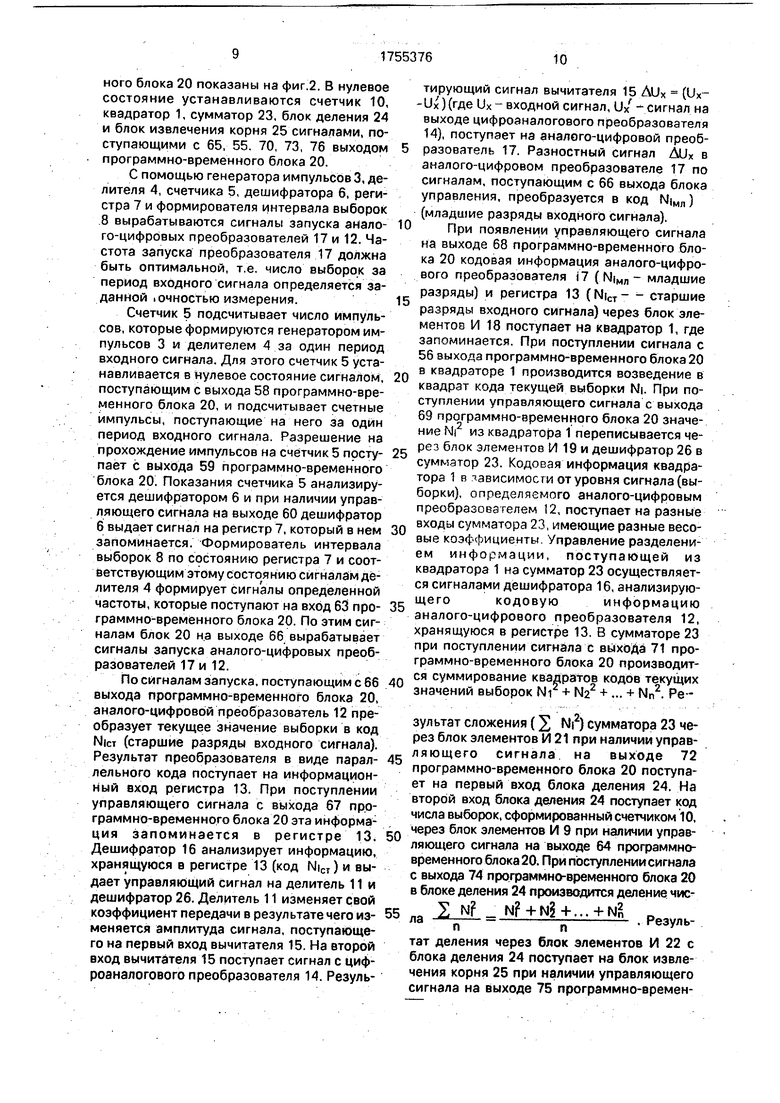

Переменный сигнал Ux поступает на компаратор 2 и измерительный вход делителя 11. По выходным сигналам компаратора 2 программно-временной блок 20 формирует управляющие сигналы, синхронизирующие работу всего устройства. Временные положения сигналов программно-временного блока 20 показаны на фиг.2. В нулевое состояние устанавливаются счетчик 10, квадратор 1, сумматор 23, блок деления 24 и блок извлечения корня 25 сигналами, поступающими с 65, 55. 70, 73, 76 выходом программно-временного блока 20.

С помощью генератора импульсов 3, делителя 4, счетчика 5, дешифратора 6, регистра 7 и формирователя интервала выборок 8 вырабатываются сигналы запуска аналого-цифровых преобразователей 17 и 12. Частота запуска преобразователя 17 должна быть оптимальной, т.е. число выборок за период входного сигнала определяется заданной |0чностью измерения.

Счетчик 5 подсчитывает число импульсов, которые формируются генератором импульсов 3 и делителем 4 за один период входного сигнала. Для этого счетчик 5 устанавливается в нулевое состояние сигналом, поступающим с выхода 58 программно-временного блока 20, и подсчитывает счетные импульсы, поступающие на него за один период входного сигнала. Разрешение на прохождение импульсов на счетчик 5 поступает с выхода 59 программно-временного блока 20. Показания счетчика 5 анализируется дешифратором б и при наличии управляющего сигнала на выходе 60 дешифратор 6 выдает сигнал на регистр 7, который в нем запоминается. Формирователь интервала выборок 8 по состоянию регистра 7 и соответствующим этому состоянию сигналам делителя 4 формирует сигналы определенной частоты, которые поступают на вход 63 программно-временного блока 20. По этим сигналам блок 20 на выходе 66 вырабатывает сигналы запуска аналого-цифровых преобразователей 17 и 12.

По сигналам запуска, поступающим с 66 выхода программно-временного блока 20, аналого-цифровой преобразователь 12 преобразует текущее значение выборки в код NICT (старшие разряды входного сигнала). Результат преобразователя в виде параллельного кода поступает на информационный вход регистра 13. При поступлении управляющего сигнала с выхода 67 программно-временного блока 20 эта информация запоминается в регистре 13. Дешифратор 16 анализирует информацию, хранящуюся в регистре 13 (код NICT) и выдает управляющий сигнал на делитель 11 и дешифратор 26. Делитель 11 изменяет свой коэффициент передачи в результате чего изменяется амплитуда сигнала, поступающего на первый вход вычитателя 15. На второй вход вычитателя 15 поступает сигнал с циф- роаналогового преобразователя 14. Результирующий сигнал вычитателя 15 AUX (Ux- -Ux) (где Ux - входной сигнал, Ux - сигнал на выходе цифроаналогового преобразователя 14), поступает на аналого-цифровой преобразователь 17. Разностный сигнал AUx в аналого-цифровом преобразователе 17 по сигналам, поступающим с 66 выхода блока управления, преобразуется в код NIM/I) (младшие разряды входного сигнала).

При появлении управляющего сигнала на выходе 68 программно-временного блока 20 кодовая информация аналого-цифрового преобразователя (7 ( М|мл - младшие

разряды) и регистра 13 (NiCTстаршие

разряды входного сигнала) через блок элементов И 18 поступает на квадратор 1, где запоминается. При поступлении сигнала с 56 выхода программно-временного блока 20 в квадраторе 1 производится возведение в квадрат кода текущей выборки NI. При поступлении управляющего сигнала с выхода 69 программно-временного блока 20 значение Nj2 из квадратора 1 переписывается через блок элементов И 19 и дешифратор 26 в сумматор 23. Кодовая информация квадратора 1 в тзвисимости от уровня сигнала (выборки), определяемого аналого-цифровым преобразователем 2, поступает на разные входы сумматора 23, имеющие разные весовые коэффициенты Управление разделением информации, поступающей из квадратора 1 на сумматор 23 осуществляется сигналами дешифратора 16, анализирующегокодовуюинформациюаналого-цифрового преобразователя 12, хранящуюся в регистре 13. В сумматоре 23 при поступлении сигнала с выхода 71 программно-временного блока 20 производит- П ся суммирование квадратов кодов текущих значений выборок Nr + №2 +... + Nn2. Ре0

5

0

5

0

5

зультат сложения (2) Ni2) сумматора 23 через блок элементов И 21 при наличии управ- ляющего сигнала на выходе 72 программно-временного блока 20 поступает на первый вход блока деления 24. На второй вход блока деления 24 поступает код числа выборок, сформированный счетчиком 10, через блок элементов И 9 при наличии управляющего сигнала на выходе 64 программно- временного блока 20. При поступлении сигнала с выхода 74 программно-временного блока 20 в блоке деления 24 производится деление чисУ N N -г N§ +... + N2, , ла . Результат деления через блок элементов И 22 с блока деления 24 поступает на блок извлечения корня 25 при наличии управляющего сигнала на выходе 75 программно-времен5

0

5

ного блока 20. При поступлении управляющего сигнала с выхода 77 программно-временного блока 20 в блоке извлечения корня 25 производится извлечение корня из кодоV Nf + N2 +... + Мй вой информации.

Результат функциональных преобразований, пропорциональный среднеквадратиче- скому значению переменных сигналов, дешифрируется дешифратором 27 и при наличии управляющего сигнала на выходе 78 программно-временного блока 20 считывается индикатором 28.

Формула изобретения Кодирующий преобразователь, содержащий компаратор, вход которого является входом преобразователя, первый дешифратор, выход которого подключен к входу индикатора, и первый аналого-цифровой преобразователь, отличающийся тем, что, с целью повышения точности преобразователя, в него введены генератор импульсов, второй, третий и четвертый дешифраторы, делители, счетчики, регистры, триггер, вычитатель, сумматор, квадратор, блок извлечения корня, блоки элементов И, блок деления, цифроаналоговый преобразователь, второй аналого-цифровой преобразователь, программно-временной блок и формирователь интервала выборок, выход компаратора и выход формирователя интервала выборок соединены соответственно с первым и вторым входами программно-временного блока, первый и второй выходы которого соединены с первыми входами соответственно блока извлечения корня и первого блока элементов И, третий и четвертый выходы программно-временного блока соединены соответственно с первым и вторым входами блока деления, выход которого соединен с вторым входом первого блока элементов И, выход которого соединен с вторыми входами блока извлечения корня, пятый выход программно-временного блока соединен с первым входом первого регистра, выходы которого соединены непосредственно с первыми входами второго блока элементов И и входами второго дешифратора и через цифроаналоговый преобразователь - с первым входом вычитателя, выход которого соединен с первым входом первого аналого-цифрового преобразователя, выходы которого соединены с вторыми входами второго блока элементов И, шестой выход программно-временного блока dbe- динен с вторым входом первого аналого- цифрового преобразователя, первым входом второго аналого-цифрового преобразователя и входом триггера, выход кото-рого соединен с первым входом первого счетчика, выходы которого соединены с первыми входами третьего блока элементов И, выходы которого соединены с третьими входами блока деления, седьмой и восьмой выходы программно-временного блока соединены соответственно с первым входом первого дешифратора и вторым входом третьего блока элементов И, девятый выход

0 программно-временного блока соединен с первым входом четвертого блока элементов И, выходы которого соединены с четвертыми входами блока деления, десятый и одиннадцатый выходы программно-временного

5 блока соединены соответственно с первым и вторым входами сумматора, выходы которого соединены с вторыми входами четвер- того блока элементов И, двенадцатый выход программно-временного блока соединен с

0 первым входом пятого блока элементов И, выходы которого соединены с первыми входами третьего дешифратора, выходы которого соединены с соответствующими третьими входами сумматора, тринадцатый

5 и четырнадцатый выходы программно-временного блока соединены соответственно с первым и вторым входами квадратора, выходы которого соединены с вторыми входа- ми пятого блока элементов И, пятнадцатый

0 выход программно-временного блока соединен с третьим входом второго блока элементов И, выходы которого соединены с/ третьими входами квадратора, шестнадцатый, семнадцатый и восемнадцатый выходы

5 программно-временного блока соединены соответственно с вторым входом первого счетчика, первым и вторым входами второго счетчика, выход которого соединен с первым входом четвертого дешифратора, выход

0 которого соединен с первым входом второго регистра, выход которого соединен с первым входом формирователя интервала выборок, девятнадцатый, двадцатый, двадцать первый и двадцать второй выходы програм5 мно-временного блока соединены соответственно с вторым входом четвертого дешифратора, вторым входом второго регистра, вторым входом формирователя интервала выборок и третьим входом блока

0 извлечения корня, выходы которого соединены с вторыми входами первого дешифратора, выход генератора импульсов соединен с входом первого делителя, первый, вторые и третий выходы которого сое5 динены соответственно с третьим входом второго счетчика, третьими входами формирователя интервалов выборок и третьим входом первого аналого-цифрового преобразователя и вторым входом второго аналого-цифрового преобразователя, выходы

второго дешифратора соединены с вторыми входами третьего дешифратора и первыми входами второго делителя, второй вход которого подключен к входу преобразователя, выход соединен с вторым входом вычитателй ti с третьим входом второго аналого-цкф- рового преобразователя, первый и второй выходы которого соединены соответственно с третьим входом вычитателя и вторыми входами первого регистра.

Ј

$ $ 15% & :йй%йЬ Sift

N S

фиг. 5

| название | год | авторы | номер документа |

|---|---|---|---|

| РАДИОВЫСОТОМЕР | 2001 |

|

RU2212684C1 |

| Устройство для формирования случайных процессов с заданным спектром | 1981 |

|

SU1027723A1 |

| Способ измерения мгновенных значений частоты электрического сигнала и устройство для его осуществления | 1987 |

|

SU1503022A1 |

| Устройство для измерения фазовых сдвигов | 1984 |

|

SU1226341A1 |

| Устройство для контроля качества канала связи с шумоподобными сигналами | 1989 |

|

SU1628210A1 |

| Устройство для сжатия информации | 1982 |

|

SU1056249A1 |

| Устройство для сжатия информации | 1983 |

|

SU1142855A1 |

| СЧЕТЧИК РЕСУРСА СИЛОВОГО ТРАНСФОРМАТОРА | 2008 |

|

RU2384879C1 |

| Автоматический цифровой измеритель коэффициента гармоник | 1980 |

|

SU911363A1 |

| Устройство для воспроизведения аналогового сигнала | 1988 |

|

SU1524175A1 |

Изобретение относится к технике электрических измерений и может быть использовано при построении высокоточных ц ровых приборов, предназначенных для измерения среднеквадратических значений переменных сигналов произвольной формы, изменяющихся в широком частотном диапазоне. Высокая точность кодирующего преобразователя достигается за счет преобразования мгновенных значений (выборок) переменного сигнала на разных диапазонах измерения цифрового прибора на выбранном интервале измерения. 5 ил.

| Преобразователь напряжение-код | 1976 |

|

SU938387A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-08-15—Публикация

1989-11-23—Подача