Изобретение относится к области электротехники, а именно к средствам функциональной диагностики электроагрегатов (ЭА) с двигателями внутреннего сгорания и может быть использовано в составе систем диагностирования технического состояния передвижных электрических станций для оценки установившегося отклонения частоты.

Известны методы оценки показателей качества электрической энергии по частоте, включая установившегося отклонения частоты посредством стендовых испытаний /1, 2/.

Недостаток этих методов состоит в наличии человеческого фактора, низкой степени автоматизации и потребности в нагрузочных устройствах для их проведения.

Наиболее близким по технической сущности к изобретению является измеритель отклонения частоты от заданного значения содержащий шину исследуемого сигнала, формирователь импульсов, генератор импульсов, два логических элемента И, RS-триггер, реверсивный счетчик, задатчик, регистр памяти, два логических элемента НЕ, первый, второй и третий формирователь коротких импульсов, выход которого подключен к сбросовому входу RS-триггера, два логических элемента ИЛИ, распределитель импульсов и шину установки /3/.

Данное устройство дает оценку отклонения частоты от заданного значения в установившемся и переходном режиме, не различая их. Однако оно не определяет факт соответствия установившегося отклонения частоты требованиям стандарта.

Цель изобретения - расширение функциональных возможностей.

Цель изобретения достигается тем, что двузонное устройство допускового контроля установившегося отклонения частоты, содержащее первый и второй логический элемент И, первый и второй логический элемент ИЛИ, генератор импульсов стабильной частоты, распределитель импульсов, RS-триггер, первый счетчик, первый задающий регистр, первый регистр памяти, логический элемент НЕ, первый, второй и третий формирователь коротких импульсов, шину ПУСК, формирователь-ограничитель, к входу которого подключен диод, а к выходу - вход первого формирователя коротких импульсов и входу логического элемента НЕ, связанного выходом со входом второго формирователя коротких импульсов, снабжено четвертым формирователем коротких импульсов, вторым счетчиком импульсов, с первого по пятый электронными ключами, третьим логическим элементом И, с первого по пятый числовым компаратором, со второго по пятый регистром памяти, вычитателем, индикатором, вторым и третьим задающим регистром, третьим и четвертым логическим элементом ИЛИ, делителем импульсов, первым и вторым элементом задержки, датчиком трехфазной активной мощности с цифровым выходом, вход которого связан с пусковым органом, подключенным выходом к диоду и зажимам генератора, а разряды информационного выхода подключены к соответствующим разрядам первого входа третьего числового компаратора и входам второго и третьего регистра памяти, разряды выхода которых соответственно связаны с разрядами первого и второго входа второго числового компаратора, выход РАВНО которого соединен с третьим входом третьего логического элемента И, выход которого подключен к единичному входу RS-триггера, а второй вход - к выходу МЕНЬШЕ пятого числового компаратора разряды первого входа которого подключены к соответствующим разрядам выхода четвертого и пятого электронного ключа к разрядам входа которых соответственно подключены разряды выхода второго и третьего задающего регистра, а управляющий вход пятого ключа связан с выходом БОЛЬШЕ третьего числового компаратора, выходы РАВНО и МЕНЬШЕ которого подключены к управляющему входу четвертого ключа, а разряды второго входа - с соответствующими разрядами выхода первого задающего регистра, причем разряды второго входа пятого числового компаратора соединены с соответствующими разрядами выхода вычитателя, разряды первого входа которого связаны с соответствующими разрядами выхода пятого регистра памяти и второго входа четвертого числового компаратора, выход БОЛЬШЕ которого подключен к входу четвертого формирователя коротких импульсов, подключенного выходом к входу записи пятого регистра памяти, разряды входа которого связаны с соответствующими разрядами выхода первого регистра памяти, первых входов четвертого и первого числового компаратора, разряды второго входа которого связаны с соответствующими разрядами выхода четвертого регистра памяти и второго входа вычитателя, а выход МЕНЬШЕ - с входом третьего формирователя коротких импульсов, подключенного выходом ко второму входу четвертого логического элемента ИЛИ, выход которого соединен с входом записи четвертого регистра памяти, разряды входа которого связаны с соответствующими разрядами выходи первого регистра памяти и выхода третьего электронного ключа, разряды входа которого подключены к шине единичного уровня, а управляющий вход связан с: шиной ПУСК; первым входом первого, второго и четвертого логического элемента ИЛИ; сбросовыми входами второго, третьего и пятого регистра памяти, сбросовым входом RS-триггера, прямой выход которого подключен к входу индикатора, кроме того, первый вход третьего логического элемента И соединен с выходом третьего логического элемента ИЛИ и входам записи первого регистра памяти, разряды входа которого связаны с соответствующими разрядами выхода первого и второго электронного ключа, разряды входов которых подключены соответственно к разрядам выхода первого и второго счетчика, сбросовый вход которого подключен к выходу второго логического элемента ИЛИ, соединенного вторым входом с выходом второго элемента задержки, вход которого связан с выходом второго формирователя, входом управления первого электронного ключа и первым входом третьего логического элемента ИЛИ, второй вход которого соединен с выходом первого формирователя коротких импульсов, управляющим входом второго электронного ключа и входом первого элемента задержки, выход которого подключен ко второму входу первого логического элемента ИЛИ, связанного выходом со сбросовым входом первого счетчика, счетный вход которого подключен к выходу первого логического элемента И, связанного вторым входом с выходом ограничителя-формирователя, а первым входом - с выходом генератора импульсов стабильной частоты и первым входом второго логического элемента И, второй вход которого соединен с выходом логического элемента НЕ, а выход - со счетным входом второго счетчика, кроме того, выход генератора импульсов стабильной частоты подключен к входу делителя импульсов, соединенного выходом с входом распределителя импульсов, первый выход которого соединен с входом записи второго регистра памяти, а второй выход - с входом записи третьего регистра памяти.

Датчик мощности, третий числовой компаратор и их связи производят зонирование нагрузки ЭА. Второй и третий регистры памяти, второй числовой компаратор, третий логический элемент И и их связи идентифицируют установившийся режим работы ЭА. Третий электронный ключ, четвертый регистр памяти, четвертый логический элемент ИЛИ и их связи совместно с первым числовым компаратором и третьим формирователем коротких импульсов формируют код наименьшей частоты. Пятый регистр памяти, четвертый числовой компаратор, четвертый формирователем коротких импульсов и их связи обеспечивают формирование кода наибольшей частоты. Второй и третий задающие регистры обеспечивают выдачу кода нормы установившегося отклонения частоты в зависимости от величины нагрузки ЭА. Вычитатель, пятый числовой компаратор индикатор и их связи обеспечивают фиксацию факта отклонения частоты за установленные стандартом пределы.

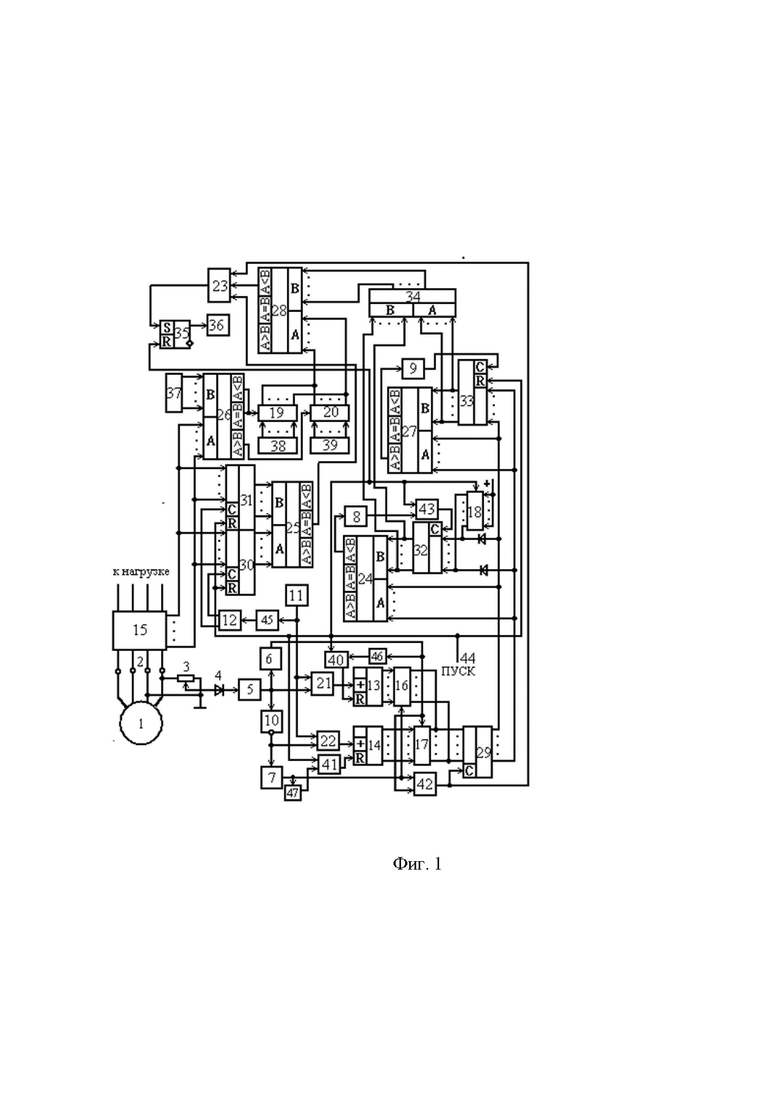

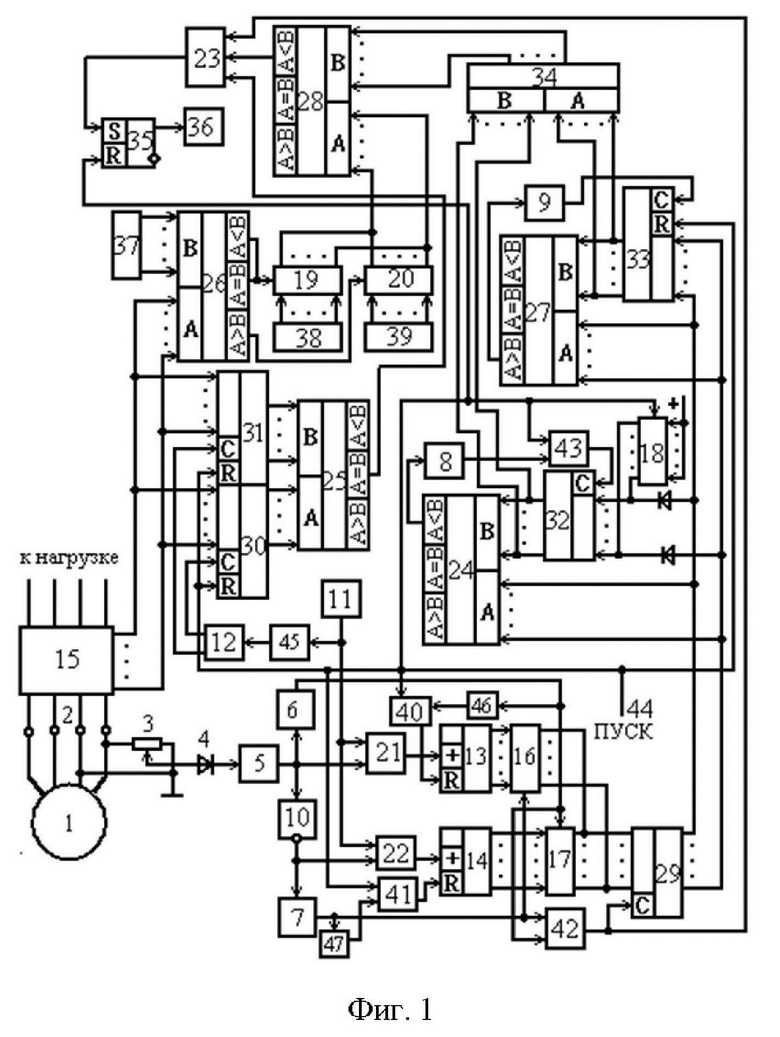

На фиг.1 представлена схема устройства, на фиг. 2 - регуляторная характеристика электроагрегата.

Схема устройства (фиг. 1) содержит генератор 1, зажимы для подключения 2, пусковой орган 3, диод 4, ограничитель-формирователь 5, первый 6, второй 7, третий 8 и четвертый 9 формирователь коротких импульсов, логический элемент НЕ 10, генератор 11 импульсов стабильной частоты, распределитель импульсов 12, первый 13 и второй 14 счетчик импульсов, датчик 15 трехфазной активной мощности с цифровым выходом, первый 16, второй 17, третий 18, четвертый 19 и пятый 20 электронный ключ, первый 21, второй 22 и третий 23 логический элемент И, первый 24, второй 25, третий 26, четвертый 27 и пятый 28 числовой компаратор, первый 29, второй 30, третий 31, четвертый 32 и пятый 33 регистр памяти, вычитаталь 34, RS-триггер 35, индикатор 36, первый 37, второй 38 и третий 39 задающий регистр, первый 40, второй 41, третий 42 и четвертый 43 логический элемент ИЛИ, шину ПУСК 44, делитель 45 импульсов, первый 46 и второй 47 элемент задержки.

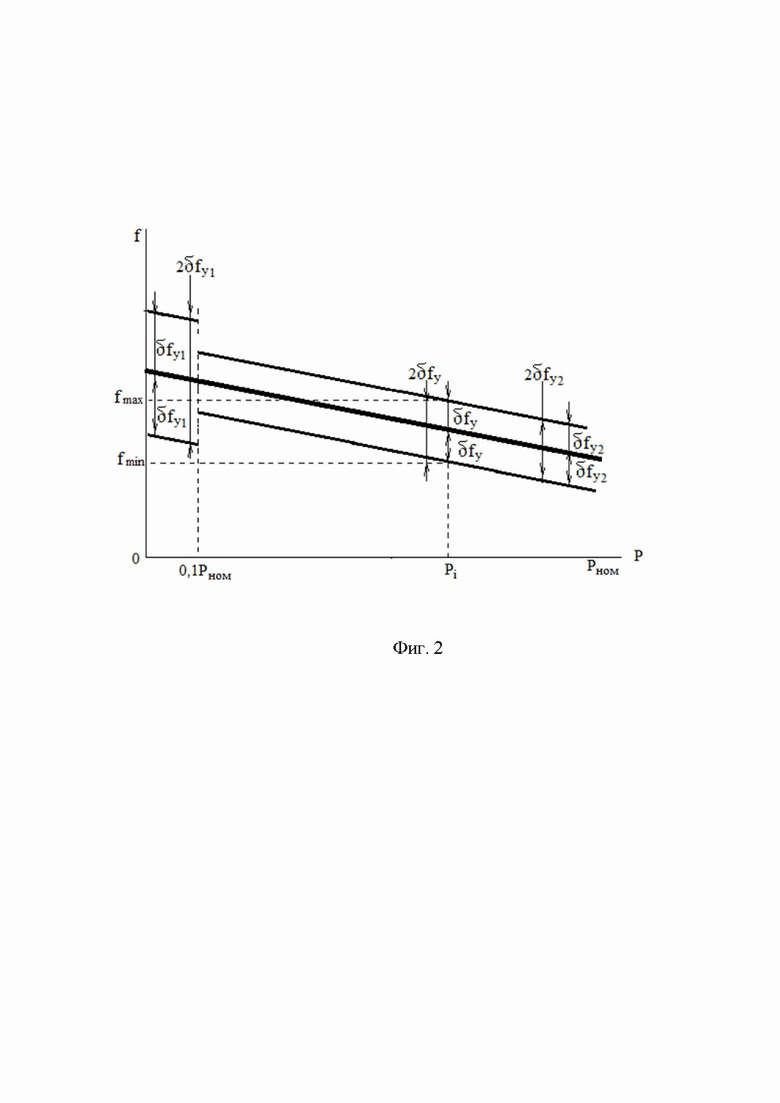

В задающий регистр 37 записан код пороговой мощности соответствующий 10% номинальной мощности Рном. В задающий регистр 38 записан код нормы установившегося отклонения частоты δfу1 (фиг. 2) для зоны мощностей от 0 до 10% номинальной мощности Рном, а в регистр 39 - код нормы установившегося отклонения частоты δfу2 для зоны мощностей более 10% номинальной мощности Рном,

Устройство работает следующим образом. Подачей сигнала на шину 44 ПУСК устройство переводится в исходное состояние. При этом сбрасываются счетчики 13 и 14, обнуляются регистры памяти 30, 31 и 33, RS-триггер 35 переводится в состояние, когда сигнал присутствует на инверсном выходе, в регистр памяти 32 заносится единичный код через электронный ключ 18.

При работе генератора 1 на нагрузку на выходе датчика мощности 15 появляется код мощности, который поступает на входы регистров памяти 30 и 31. С выхода генератора импульсов 11 через делитель 45 импульсы поступают на вход распределителя импульсов 12 откуда поочередно поступают на входы записи регистров 30 и 31. В регистры 30 и 31 записываются коды мощности в текущий и предыдущий моменты времени с выхода датчика 15. Если приращение мощности отсутствует коды на выходах регистров 30 и 31 равны. Эти коды поступают на первый и второй входы компаратора 25 и появляется сигнал на выходе РАВНО, что является признаком установившегося режима нагрузки. Сигнал с выхода РАВНО компаратора 25 подготавливает логический элемент И 23 по третьему входу.

Одновременно производится анализ изменения частоты. С пускового органа 3 через диод 4 на вход ограничителя-формирователя 5 подается положительная полуволна напряжения генератора 1, и на выходе ограничителя-формирователя 5 появляется импульс, длительность которого равна полупериоду напряжения генератора 1. Этот импульс подготавливает элемент И 21 по второму входу. На счетный вход счетчика 13 через первый вход элемента И 21 начинают поступать импульсы с выхода генератора импульсов 11. На выходе счетчика 13 формируется код частоты генератора 1.

С приходом отрицательной полуволны напряжения генератора 1, сигнал на выходе ограничителя-формирователя 5 исчезает, а на выходе инвертора 10 появляется. По фронту этого сигнала формирователь 7 коротких импульсов выдает импульс, который открывает электронный ключ 16, подающий код частоты с выхода счетчика 13 на вход регистра памяти 29. Импульсом с выхода формирователя 7, проходящим через элемент ИЛИ 42, в регистр 29 заносится код частоты, сформированный за положительную полуволну напряжения. Одновременно сигналом с выхода инвертора 10 подготавливается по второму входу элемент И 22, и через него начинают поступать импульсы с выхода генератора 11 на счетный вход счетчика 14, на выходе которого формируется код частоты до момента появления сигнала на выходе ограничителя-формирователя 5. В этот момент сигналом с выхода формирователя 6 открывается ключ 17 и в регистр 29 записывается новый код частоты. Тем же сигналом, проходящим через элемент задержки 46 и элемент ИЛИ 40, обнуляется счетчик 13, который начинает счет импульсов , поступающих с выхода генератора 11 через элемент И 21 формируя очередной код частоты. Далее процесс повторяется циклично и через каждую половину периода в регистр 29 записывается новый код текущей частоты.

С выхода регистра памяти 29 код частоты поступает на вход регистра 33 и первый вход числового компаратора 27. Регистр 33 ранее был обнулен, поэтому на втором входе компаратора 27 присутствует нулевой код. Появляется сигнал на выходе БОЛЬШЕ компаратора 27, по фронту которого формирователь 9 выдает импульс, которым в регистр 33 записывается текущий код частоты с выхода регистра 29. При увеличении текущей частоты код на первом входе компаратора 27 становится больше кода на его втором входе, появляется сигнал на выходе БОЛЬШЕ компаратора 27, что приводит к записи нового кода большей частоты. Появление каждого большего кода на выходе регистра 29 сопровождается его записью в регистр 33. В результате на выходе регистра 33 формируется код наибольшей частоты fmax за период наблюдения. В тоже время код текущей частоты с выхода регистра 29 поступает на первый вход компаратора 24 и вход регистра памяти 32, в который ранее был записан единичный код, поданный на второй вход компаратора 24. Код на первом входе компаратора 24 меньше кода присутствующего на втором входе, поэтому появляется сигнал на выходе МЕНЬШЕ. По фронту этого сигнала формирователь 8 выдает импульс, который проходит через элемент ИЛИ 40 и записывает в регистр 32 код текущей частоты с выхода регистра 29. В последующем при каждом снижении частоты её код с выхода регистра 29 переписывается в регистр 32. В результате в регистре 32 формируется код наименьшей частоты fmin за период наблюдения, который поступает на второй вход вычитателя 34, на первый вход которого поступает код наибольшей частоты fmax с выхода регистра 33. На выходе вычитателя 34 появляется код разности частот (fmax - fmin), который подается на второй вход числового компаратора 28 для сравнения с нормой установившегося отклонения частоты, код которой поступает на первый вход компаратора 28.

Норма установлена стандартом в зависимости от нагрузки генератора 1. С выхода датчика 15 код мощности поступает на первый вход числового компаратора 26. Если нагрузка меньше 10% от номинальной мощности, то появляется сигнал на выходе МЕНЬШЕ компаратора 26, которым открывается электронный ключ 19, и к входу компаратора 28 подключается задающий регистр 38. Если нагрузка генератора превышает 10% от номинальной мощности, то появляется сигнал на выходе БОЛЬШЕ компаратора 26, который включает электронный ключ 20, подключая к входу компаратора 28 задающий регистр 39.

Если код текущей разности частот на втором входе компаратора 28, отражающий размах колебаний частоты, превышает код нормы, поданный на первый вход компаратора 28, то появляется сигнал на выходе БОЛЬШЕ компаратора 28, подготавливающий элемент И 23 по второму входу. В момент завершения процесса формирования кода текущей частоты, когда появляется импульс на выходе элемента ИЛИ 42, элемент И 23 открывается и сигналом с его выхода RS-триггер 35 переводится единичное состояние, включая индикатор 36, указывающий на необходимость подстройки регулятора частоты.

Если код разность частот (fmax - fmin) на выходе вычитателя 34, не превышает кода нормы, то сигнал на выходе компаратора 28 отсутствует, элемент И 23 закрыт по второму входу, поддерживая запрет на включение индикатора 36.

Таким образом, устройство позволяет без проведения стендовых испытаний в процессе работы электроагрегата оценивать соответствие норме установившееся отклонении частоты с учетом величины нагрузки.

Источники информации

1. Сугаков В. Г., Хватов О.С. Основы автоматического регулирования выходных электрических параметров автономных источников электрической энергии. Часть 1. Автоматическое регулирование частоты автономных источников электрической энергии: Учебное пособие. Кстово, НВВИКУ, 2008.

2. Сугаков В. Г., Хватов О.С. Системы автоматического регулирования параметров судовых электростанций. Часть 1. Автоматическое регулирование частоты судовых источников электрической энергии. Учебное пособие для студентов (курсантов) специальности 180404. Н. Новгород, Издательство ФГОУ «ВГАВТ», 2010.

3. Авторское свидетельство СССР №1679404, кл. G01R 23/00, 1991.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ ПЕРЕХОДНОГО ОТКЛОНЕНИЯ ЧАСТОТЫ ДВУНАПРАВЛЕННОЕ | 2024 |

|

RU2819573C1 |

| ДВУНАПРАВЛЕННОЕ УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ ВРЕМЕНИ ВОССТАНОВЛЕНИЯ ЧАСТОТЫ | 2023 |

|

RU2817045C1 |

| УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ УСТАНОВИВШЕГОСЯ ОТКЛОНЕНИЯ ЧАСТОТЫ | 2022 |

|

RU2795501C1 |

| УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ ВРЕМЕНИ ВОССТАНОВЛЕНИЯ ЧАСТОТЫ ДВУНАПРАВЛЕННОЕ | 2024 |

|

RU2820839C1 |

| УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ ВРЕМЕНИ ВОССТАНОВЛЕНИЯ ЧАСТОТЫ | 2020 |

|

RU2787747C2 |

| ТРЕХФАЗНЫЙ БЕСТРАНСФОРМАТОРНЫЙ НЕПОСРЕДСТВЕННЫЙ ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ | 2020 |

|

RU2758443C1 |

| ДВУНАПРАВЛЕННОЕ УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ ПЕРЕХОДНОГО ОТКЛОНЕНИЯ ЧАСТОТЫ | 2024 |

|

RU2826860C1 |

| НЕПОСРЕДСТВЕННЫЙ ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ БЕСТРАНСФОРМАТОРНЫЙ | 2022 |

|

RU2787121C1 |

| УСТРОЙСТВО КОРРЕКЦИИ ФОРМЫ КРИВОЙ НАПРЯЖЕНИЯ | 2014 |

|

RU2580944C1 |

| БЕСТРАНСФОРМАТОРНЫЙ НЕПОСРЕДСТВЕННЫЙ ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ | 2018 |

|

RU2691968C1 |

Изобретение относится к области электротехники, а именно к средствам функциональной диагностики электроагрегатов (ЭА) с двигателями внутреннего сгорания и может быть использовано в составе систем диагностирования технического состояния передвижных электрических станций для оценки установившегося отклонения частоты. Технический результат: расширение функциональных возможностей. Сущность: устройство содержит генератор 1, зажимы для подключения 2, пусковой орган 3, диод 4, ограничитель-формирователь 5, первый 6, второй 7, третий 8 и четвертый 9 формирователи коротких импульсов, логический элемент НЕ 10, генератор 11 импульсов стабильной частоты, распределитель импульсов 12, первый 13 и второй 14 счетчик импульсов, датчик 15 трехфазной активной мощности с цифровым выходом, первый 16, второй 17, третий 18, четвертый 19 и пятый 20 электронные ключи, первый 21, второй 22 и третий 23 логические элементы И, первый 24, второй 25, третий 26, четвертый 27 и пятый 28 числовые компараторы, первый 29, второй 30, третий 31, четвертый 32 и пятый 33 регистры памяти, вычитатель 34, RS-триггер 35, индикатор 36, первый 37, второй 38 и третий 39 задающие регистры, первый 40, второй 41, третий 42 и четвертый 43 логические элементы ИЛИ, шину ПУСК 44, делитель 45 импульсов, первый 46 и второй 47 элементы задержки. Устройство позволяет в процессе работы электроагрегата осуществлять непрерывный контроль установившегося отклонения частоты, определяя соответствие нормативным требованиям с учетом нагрузки. 2 ил.

Устройство допускового контроля установившегося отклонения частоты, содержащее первый и второй логический элемент И, первый и второй логический элемент ИЛИ, генератор импульсов стабильной частоты, распределитель импульсов, RS-триггер, первый счетчик, первый задающий регистр, первый регистр памяти, логический элемент НЕ, первый, второй и третий формирователь коротких импульсов, шину ПУСК, формирователь-ограничитель, к входу которого подключен диод, а к выходу – вход первого формирователя коротких импульсов и входу логического элемента НЕ, связанного выходом с входом второго формирователя коротких импульсов, отличающееся тем, что с целью расширения функциональных возможностей снабжено четвертым формирователем коротких импульсов, вторым счетчиком импульсов, с первого по пятый электронными ключами, третьим логическим элементом И, с первого по пятый числовым компаратором, со второго по пятый регистром памяти, вычитателем, индикатором, вторым и третьим задающим регистром, третьим и четвертым логическим элементом ИЛИ, делителем импульсов, первым и вторым элементом задержки, датчиком трехфазной активной мощности с цифровым выходом, вход которого связан с пусковым органом, подключенным выходом к диоду и зажимам генератора, а разряды информационного выхода подключены к соответствующим разрядам первого входа третьего числового компаратора и входам второго и третьего регистра памяти, разряды выхода которых соответственно связаны с разрядами первого и второго входа второго числового компаратора, выход РАВНО которого соединен с третьим входом третьего логического элемента И, выход которого подключен к единичному входу RS-триггера, а второй вход – к выходу МЕНЬШЕ пятого числового компаратора, разряды первого входа которого подключены к соответствующим разрядам выхода четвертого и пятого электронного ключа, к разрядам входа которых соответственно подключены разряды выхода второго и третьего задающего регистра, а управляющий вход пятого ключа связан с выходом БОЛЬШЕ третьего числового компаратора, выходы РАВНО и МЕНЬШЕ которого подключены к управляющему входу четвертого ключа, а разряды второго входа – с соответствующими разрядами выхода первого задающего регистра, причем разряды второго входа пятого числового компаратора соединены с соответствующими разрядами выхода вычитателя, разряды первого входа которого связаны с соответствующими разрядами выхода пятого регистра памяти и второго входа четвертого числового компаратора, выход БОЛЬШЕ которого подключен к входу четвертого формирователя коротких импульсов, подключенного выходом к входу записи пятого регистра памяти, разряды входа которого связаны с соответствующими разрядами выхода первого регистра памяти, первых входов четвертого и первого числового компаратора, разряды второго входа которого связаны с соответствующими разрядами выхода четвертого регистра памяти и второго входа вычитателя, а выход МЕНЬШЕ – с входом третьего формирователя коротких импульсов, подключенного выходом к второму входу четвертого логического элемента ИЛИ, выход которого соединен с входом записи четвертого регистра памяти, разряды входа которого связаны с соответствующими разрядами выходи первого регистра памяти и выхода третьего электронного ключа, разряды входа которого подключены к шине единичного уровня, а управляющий вход связан с: шиной ПУСК; первым входом первого, второго и четвертого логического элемента ИЛИ; сбросовыми входами второго, третьего и пятого регистра памяти, сбросовым входом RS-триггера, прямой выход которого подключен к входу индикатора, кроме того, первый вход третьего логического элемента И соединен с выходом третьего логического элемента ИЛИ и входом записи первого регистра памяти, разряды входа которого связаны с соответствующими разрядами выхода первого и второго электронного ключа, разряды входов которых подключены соответственно к разрядам выхода первого и второго счетчика, сбросовый вход которого подключен к выходу второго логического элемента ИЛИ, соединенного вторым входом с выходом второго элемента задержки, вход которого связан с выходом второго формирователя, входом управления первого электронного ключа и первым входом третьего логического элемента ИЛИ, второй вход которого соединен с выходом первого формирователя коротких импульсов, управляющим входом второго электронного ключа и входом первого элемента задержки, выход которого подключен к второму входу первого логического элемента ИЛИ, связанного выходом со сбросовым входом первого счетчика, счетный вход которого подключен к выходу первого логического элемента И, связанного вторым входом с выходом ограничителя-формирователя, а первым входом – с выходом генератора импульсов стабильной частоты и первым входом второго логического элемента И, второй вход которого соединен с выходом логического элемента НЕ, а выход – со счетным входом второго счетчика, кроме того, выход генератора импульсов стабильной частоты подключен к входу делителя импульсов, соединенного выходом с входом распределителя импульсов, первый выход которого соединен с входом записи второго регистра памяти, а второй выход – с входом записи третьего регистра памяти.

| Способ измерения отклонений частоты от номинального значения и устройство для его осуществления | 1986 |

|

SU1347032A1 |

| Устройство для контроля частоты вращения рабочих органов машин | 1987 |

|

SU1540704A1 |

| Измеритель девиации частоты | 1976 |

|

SU575578A1 |

| Устройство для измерения отклонения частоты электрических сигналов от номинального значения | 1985 |

|

SU1270715A1 |

| JPS 54099557 U, 13.07.1979 | |||

| Стенд для испытания движения жидкости и газа в проницаемых материалах | 1983 |

|

SU1125511A1 |

| Измеритель отклонений частоты от заданного значения | 1989 |

|

SU1679404A1 |

Авторы

Даты

2023-07-10—Публикация

2023-04-10—Подача