Изобретение относится к области электротехники, а именно к средствам функциональной диагностики электроагрегатов (ЭА) с двигателями внутреннего сгорания и может быть использовано в составе систем диагностирования технического состояния передвижных электрических станций.

Известны методы оценки показателей качества электрической энергии по частоте, включая переходное отклонение частоты при набросе нагрузки посредством стендовых испытаний /1, 2/.

Недостаток этих методов состоит в наличии человеческого фактора, низкой степени автоматизации и потребности нагрузочных устройств для их проведения.

Наиболее близким по технической сущности к изобретению является устройство допускового контроля переходного отклонения частоты, содержащее первый и второй числовые компараторы к разрядам второго входа которых подключены соответствующие разряды выходов соответственно первого и второго задающих регистров, шину ПУСК, связанную со сбросовыми входами второго и первого и первого RS-триггера, прямой выход которого соединен с входом индикатора, пусковой орган, подключенный к зажимам генератора, к выходу которого через диод подключен вход ограничителя-формирователя, выход которого соединен со вторым входом первого логического элемента И, связанного первым входом с выходом генератора стабильных импульсов, а выходом – со счетным входом счетчика импульсов, кроме того выход ограничителя-формирователя связан со входом инвертора соединенного выходом с входом формирователя коротких импульсов, выход которого подключен к входу первого элемента задержки и первому входу второго логического элемента И, а выход БОЛЬШЕ третьего числового компаратора связан со вторым входом второго логического элемента И, выход МЕНЬШЕ – со вторым входом третьего логического элемента И, выход которого подключен к единичному входу первого RS-триггера, первый вход – к выходу первого формирователя коротких импульсов, третий вход – к выходу БОЛЬШЕ второго числового компаратора, а четвертый вход – к единичному входу второго RS-триггера и выходу РАВНО первого числового компаратора, разряды первого входа которого подключены к соответствующим разрядам выхода первого вычитателя, разряды первого входа которого связаны с соответствующими разрядами выхода третьего регистра памяти, а соответствующие разряды второго входа – с соответствующими разрядами входа третьего регистра памяти, входа адреса блока памяти и выхода второго регистра памяти, разряды входа которого соединены с соответствующими разрядами выхода датчика трехфазной активной мощности с цифровым выходом, а вход записи подключен к выходу второго элемента задержки, вход которого связан с выходом делителя импульсов, соединенного входом с выходом генератора стабильных импульсов, и входом записи третьего регистра памяти, сбросовый вход которого связан с шиной ПУСК, сбросовым входом первого и второго регистра памяти и первым входом второго логического элемента ИЛИ, связанного вторым входом с выходом первого элемента задержки, а выходом – со сбросовым входом счетчика импульсов, разряды выхода которого связаны с соответствующими разрядами входа первого регистра памяти, с – соответствующими разрядами второго входа третьего числового компаратора и соответствующими разрядами выхода электронного ключа, подключенного разрядами входа к шине высокого уровня, а управляющим входом – к выходу второго формирователя коротких импульсов, вход которого соединен прямым выходом второго RS-триггера и третьим входом первого логического элемента И, кроме того выход второго формирователя коротких импульсов подключен к первому входу первого логического элемента ИЛИ, второй вход которого подключен к выходу второго логического элемента ИЛИ, а выход – к сбросовому входу третьего регистра памяти, разряды выхода которого связаны с соответствующими разрядами первого входа третьего числового компаратора и разрядами входа вычитаемого второго вычитателя, разряды выхода которого подключены к соответствующим разрядам первого входа второго числового компаратора, а разряды входа уменьшаемого – к соответствующим разрядам выхода блока памяти /3/.

Недостатком этого устройства является то, что оно контролирует переходное отклонение частоты лишь при набросе нагрузки.

Цель изобретения – расширение функциональных возможностей.

Цель изобретения достигается тем, что двунаправленное устройство допускового контроля переходного отклонения частоты, содержащее второй и первый числовые компараторы, к разрядам второго входа которого подключены соответствующие разряды выхода задающего регистра, шину ПУСК, связанную со сбросовыми входами второго и первого RS-триггера, прямой выход которого соединен с входом индикатора, пусковой орган, подключенный к зажимам генератора, к выходу которого через диод подключен вход ограничителя-формирователя, выход которого соединен со вторым входом первого логического элемента И, связанного первым входом с выходом генератора стабильных импульсов, а выходом – со счетным входом счетчика импульсов, кроме того выход ограничителя-формирователя связан со входом инвертора соединенного выходом с входом первого формирователя коротких импульсов, выход которого подключен к входу первого элемента задержки и первому входу второго логического элемента И, а выход БОЛЬШЕ третьего числового компаратора связан со вторым входом второго логического элемента И, выход МЕНЬШЕ – со вторым входом третьего логического элемента И, выход которого подключен к единичному входу первого RS-триггера, первый вход – к выходу первого формирователя коротких импульсов, третий вход – к выходу БОЛЬШЕ второго числового компаратора, а четвертый вход – к единичному входу второго RS-триггера и выходу РАВНО первого числового компаратора, разряды первого входа которого подключены к соответствующим разрядам выхода первого вычитателя, разряды второго входа которого связаны с соответствующими разрядами выхода третьего регистра памяти, а соответствующие разряды первого входа – с соответствующими разрядами входа третьего регистра памяти, входа адреса второго блока памяти и выхода второго регистра памяти, разряды входа которого соединены с соответствующими разрядами выхода датчика трехфазной активной мощности с цифровым выходом, а вход записи подключен к выходу второго элемента задержки, вход которого связан с выходом делителя импульсов, соединенного входом с выходом генератора стабильных импульсов, и входом записи третьего регистра памяти, сбросовый вход которого связан с шиной ПУСК, сбросовым входом первого и второго регистра памяти и первым входом второго логического элемента ИЛИ, связанного вторым входом с выходом первого элемента задержки, а выходом – со сбросовым входом счетчика импульсов, разряды выхода которого связаны с соответствующими разрядами входа первого регистра памяти, с – соответствующими разрядами второго входа третьего числового компаратора и соответствующими разрядами выхода электронного ключа, подключенного разрядами входа к шине высокого уровня, а управляющим входом – к выходу второго формирователя коротких импульсов, вход которого соединен прямым выходом второго RS-триггера и третьим входом первого логического элемента И, кроме того выход второго формирователя коротких импульсов подключен к первому входу первого логического элемента ИЛИ, второй вход которого подключен к выходу второго логического элемента И, а выход – к сбросовому входу третьего регистра памяти, разряды выхода которого связаны с соответствующими разрядами первого входа третьего числового компаратора и разрядами первого входа второго вычитателя, разряды выхода которого подключены к соответствующим разрядам первого входа второго числового компаратора, а разряды второго входа – к соответствующим разрядам выхода второго блока памяти, снабжено первым блоком памяти, четвертым числовым компаратором, четвертым регистром памяти, третьим RS-триггером, вторым и третьим электронным ключом и третьим логическим элементом ИЛИ, связанным выходом с вторым входом третьего логического элемента И, первым входом – с выходом МЕНЬШЕ третьего числового компаратора, а вторым входом – с выходом БОЛЬШЕ четвертого числового компаратора, выход МЕНЬШЕ которого подключен к входу записи четвертого регистра памяти, связанного сбросовым входом с шиной ПУСК, разрядами входа – с соответствующими разрядами счетчика и второго входа четвертого числового компаратора, разряды первого входа которого подключены к соответствующим разрядам выхода четвертого регистра памяти и второго электронного ключа, связанного разрядами выхода с соответствующими разрядами первого входа второго вычитателя и входа третьего электронного ключа, соединенного разрядами входа с соответствующими разрядами выхода первого регистра памяти, а управляющим входом – с инверсным выходом третьего RS-триггера, единичный вход которого подключен к выходу признака положительной разности первого вычитателя, который связан выходом признака отрицательной разности с сбросовым входом третьего RS-триггера, разрядами выхода разности – с соответствующими разрядами первого входа первого числового компаратора, разрядами входа вычитаемого – с соответствующими разрядами выхода второго регистра памяти, а разрядами выхода уменьшаемого – с соответствующими разрядами выхода третьего регистра памяти, кроме того прямой и инверсный выходы третьего RS-триггера подключены к входу адреса первого блока памяти, а управляющий вход второго электронного ключа связан с прямым выходом третьего RS-триггера.

Связи второго вычитателя, третий RS-триггер и его связи определяют характер изменения нагрузки (сброс, наброс). Четвертый числовой компаратор, четвертый регистр памяти и их связи формируют код максимальной частоты при сбросе нагрузки. Первый блок памяти, второй и третий электронные ключи, третий логический элемент ИЛИ и их связи анализируют переходное отклонение частоты при сбросе и набросе нагрузки и обеспечивают индикацию факта выхода частоты за пределы допустимого.

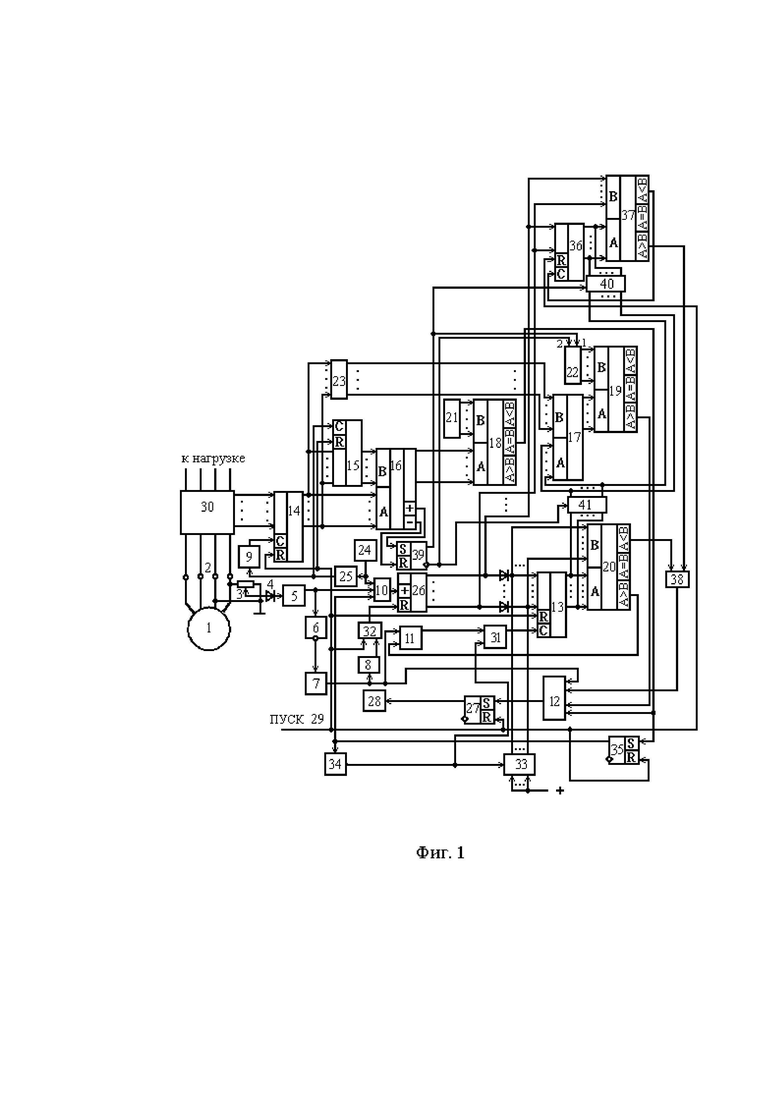

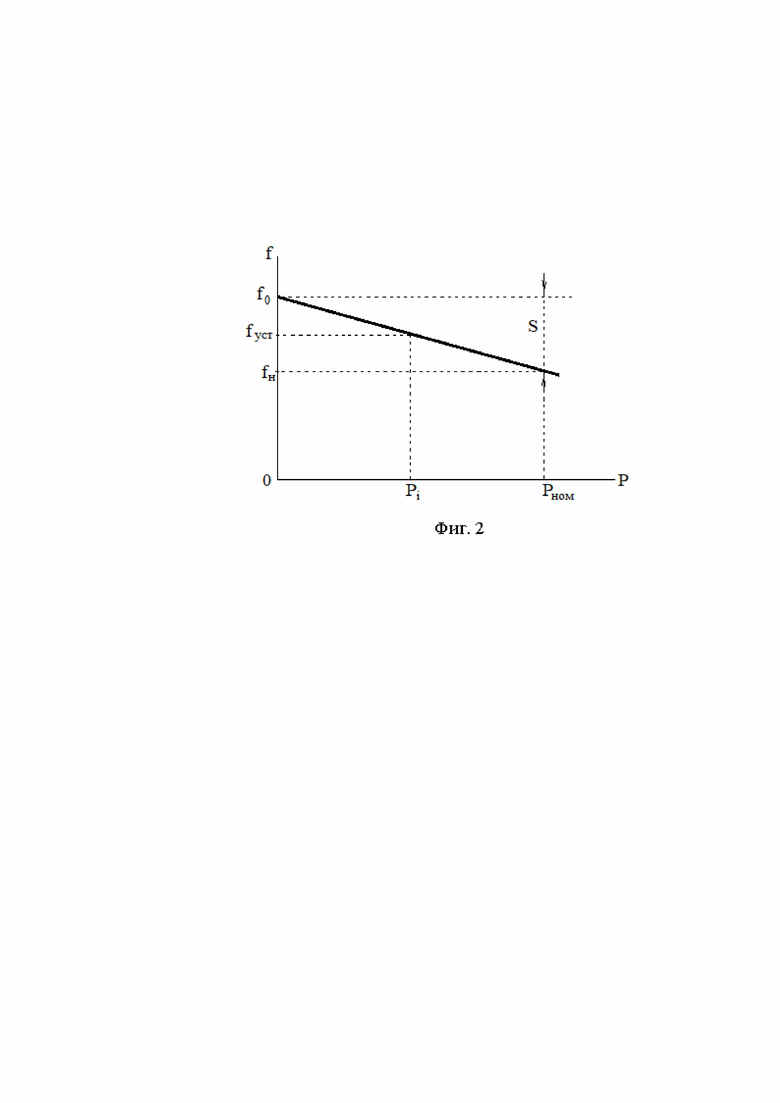

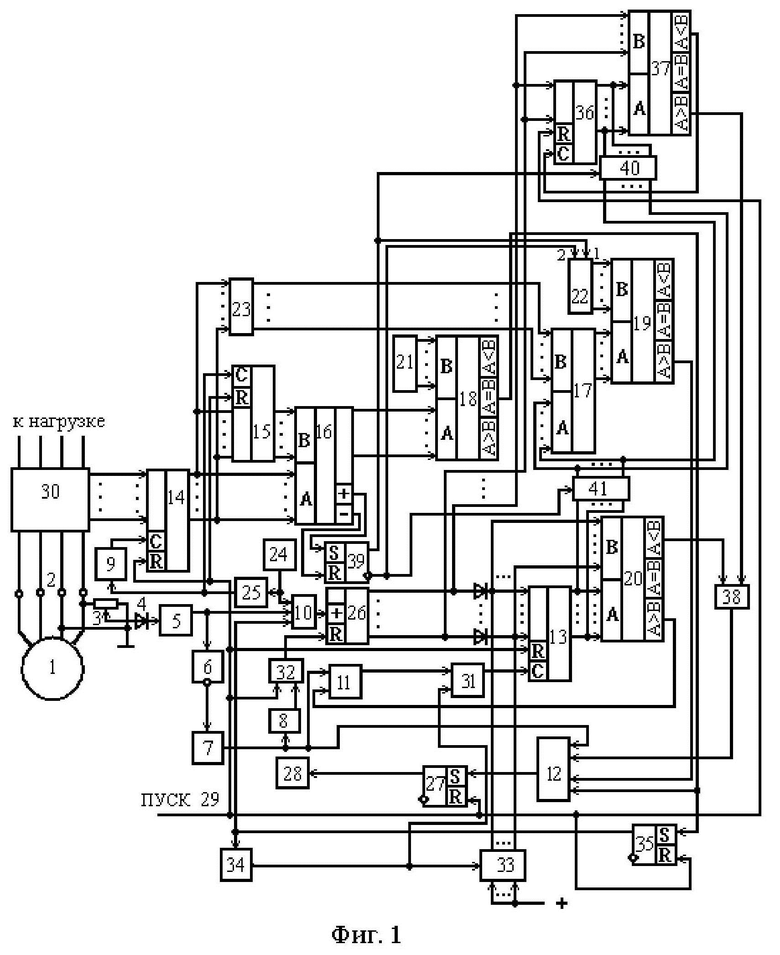

На фиг. 1 представлена схема устройства допускового контроля переходного отклонения частоты двунаправленного, на фиг. 2 – зависимость частоты fэi от нагрузки Pi генератора (регуляторная характеристика электроагрегата).

Схема устройства (фиг. 1) содержит генератор 1, зажимы для подключения 2, пусковой орган 3, диод 4, ограничитель-формирователь 5, инвертор 6, формирователь коротких импульсов 7, первый 8 и второй 9 элементы задержки, первый 10, второй 11 и третий 12 логические элементы И, первый 13, второй 14 и третий 15 регистры памяти, первый 16 и второй 17 вычитатели, первый 18, второй 19 и третий 20 числовые компараторы, первый 21 задающий регистр, первый 22 и второй 23 , блоки памяти, генератор 24 импульсов стабильной частоты, делитель 25 импульсов, счетчик импульсов 26, первый RS-триггер 27, первый индикатор 28, шину ПУСК 29, датчик 30 трехфазной активной мощности с цифровым выходом, первый 31 и второй 32 логические элементы ИЛИ, электронный ключ 33, второй формирователь 34 коротких импульсов, второй RS-триггер 35, четвертый регистр памяти 36, четвертый числовой компаратор 37, третий логический ИЛИ 38, третий RS-триггер 39, второй 40 и третий 41 электронный ключи.

В ячейки блока памяти 22 по адресу «10» записан код допустимого отклонения частоты при сбросе нагрузки, а по адресу «01» записан код допустимого отклонения частоты при набросе заданной ступени нагрузки.

В ячейки блока 23 памяти занесены коды эталонной частоты fуст в зависимости от мощности Pi нагрузки генератора (фиг. 2), которые соответствуют выражению для относительной эталонной частоты fэi

fуст = f0 - λS, о.е.,

где f0 – относительная частота на холостом ходу генератора, о. е.

f0 =f а0 / fном;

f а 0 – абсолютная частота на холостом ходу генератора, Гц;

f ном – абсолютная номинальная частота генератора, Гц;

λ – относительная активная мощность нагрузки генератора, о.е.

λ = Pi / Pном;

Pi – текущая активная мощность нагрузки генератора, кВт;

Pном – номинальная активная мощность нагрузки генератора, кВт;

S – наклон (статизм) регуляторной характеристики электроагрегата, о.е

S =(f а0 - f аН )/ fном;

f а Н – абсолютная частота при номинальной нагрузке генератора, Гц.

Устройство работает следующим образом. В регистр 21 заносится код контролируемой ступени наброса нагрузки (стандартные величины 25%, 50% или 100% от номинальной мощности). Подается сигнал на шину ПУСК 29, которым обнуляются регистры памяти 13, 14, 15,36 и счетчик 26, а RS-триггеры 27 и 35 переводятся в состояние, когда сигнал на прямом выходе отсутствует.

Анализ изменения нагрузки осуществляется по коду мощности на выходе датчика 30. После появления сигнала на шине ПУСК 29 на выходах регистров памяти 14 и 15 присутствует нулевой код. При появлении первого импульса на выходе делителя 25 в регистр 15 переписывается нулевой код, а в регистр 14 с выдержкой времени, заданной элементом задержки 9, записывается код мощности с выхода датчика 30. При втором и последующих импульсах с выхода делителя 25 в регистр 15 происходит перезапись кода мощности в предыдущий момент времени с выхода регистра 14, а в регистр 14 записывается код мощности в текущий (последующий) момент времени с выхода датчика 30. В результате на выходе регистра 15 постоянно присутствует код мощности в предыдущий момент времени, который подается вход уменьшаемого вычитателя 16, а на выходе регистра 14 постоянно устанавливается код мощности в последующий момент времени, который поступает на вход вычитаемого вычитателя 16. На выходе разности вычитателя 16 в течение всей работы электроагрегата присутствует код величины изменения мощности нагрузки, который поступает на первый вход компаратора 18.

Одновременно анализируется характер изменения мощности. При сбросе нагрузки код на входе уменьшаемого больше кода на входе вычитаемого вычитателя 16. Поэтому появляется сигнал на выходе признака положительной разности, который переводит RS-триггер 39 в единичное состояние. При набросе нагрузки появляется сигнал на выходе признака отрицательной разности вычитателя 16, который переводит RS-триггер 39 в нулевое состояние.

Если в процессе работы электроагрегата величина наброса нагрузки соответствует контролируемой, то код на первом входе компаратора 18 совпадает с кодом на выходе задающего регистра 21, поданным на второй вход компаратора 18. При этом появляется сигнал на выходе РАВНО компаратора 18, который подготавливает логический элемент 27 по четвертому входу, а RS-триггер 35 переводится в единичное состояние. Сигналом с прямого выхода RS-триггера 35 логический элемент И 10 подготавливается по третьему входу. Одновременно по фронту сигнала с прямого выхода RS-триггера 35 формирователь коротких импульсов 34 выдает импульс, кратковременно открывающий электронный ключ 33, с выхода которого в регистр памяти 13 записывается единичный код импульсом проходящим через логический элемент ИЛИ 31.

С пускового органа 3 через диод 4 на вход ограничителя-формирователя 5 подается положительная полуволна напряжения генератора 1, и на выходе ограничителя-формирователя 5 появляется импульс, длительность которого равна полупериоду напряжения генератора 1. Этот импульс подготавливает элемент И 10 по второму входу. На счетный вход счетчика 26 через первый вход элемента И 10 начинают поступать импульсы с выхода генератора импульсов 24. На выходе счетчика 26 формируется код частоты генератора 1. Этот код, поступающий на второй вход компаратора 20, меньше единичного кода поданного на первый вход компаратора 20, поэтому появляется сигнал на выходе БОЛЬШЕ компаратора 20, подготавливающий логический элемент И 11 по второму входу.

С приходом отрицательной полуволны напряжения генератора 1, сигнал на выходе ограничителя-формирователя 5 исчезает, а на выходе инвертора 6 появляется. По фронту этого сигнала формирователь 7 коротких импульсов выдает импульс, проходящий через логические элементы И 11 и ИЛИ 31 на вход записи регистра памяти 13, в который производится запись кода частоты с выхода счетчика 26. Затем счетчик 26 обнуляется импульсом, поступающим с выхода элемента задержки 8, через логический элемент ИЛИ 32 на сбросовый вход, подготавливая счетчик 26 к очередному измерению частоты. При набросе нагрузки в начальный период частота снижается. Поэтому очередной код частоты на выходе счетчика 26 оказывается меньше предыдущего кода, записанного в регистр памяти 13. Эти коды сравниваются компаратором 20, и на его выходе БОЛЬШЕ вновь появляется сигнал, разрешающий перезапись в регистр памяти 13 нового меньшего значения частоты с выхода счетчика 26. Процесс перезаписи кода частоты в регистр 13 происходит до момента записи кода минимальной частоты f мин, после чего частота начинает увеличиваться и сформированные коды частот на выходе счетчика 26 оказываются больше кода записанного в регистр 13. Появляется сигнал на выходе МЕНЬШЕ компаратора 20, который проходит через логический элемент ИЛИ 38 и подготавливает логический элемент И 12 по второму входу.

Код мощности с выхода регистра памяти 14 подается на вход адреса блока 23 памяти и на его выходе появляется код установившейся частоты f уст для данной нагрузки генератора 1, который поступает на второй вход вычитателя 17. На первый вход вычитателя 17, через электронный ключ 41, включенный сигналом с инверсного выхода RS-триггера 39, подан код минимальной частоты f мин с выхода регистра 13. На выходе вычитателя 17 появляется код переходного отклонения частоты для заданной ступени нагрузки δ f пер = f уст - f мин. С выхода вычитателя 17 код поступает на первый вход компаратора 19. С выходов RS-триггера 39 на вход адреса блока памяти 22 поступает код «10», поэтому на втором входе которого присутствует код допустимого переходного отклонения частоты для заданной ступени наброса нагрузки.

Если переходное отклонение частоты превышает допустимую величину, то появляется сигнал на выходе БОЛЬШЕ компаратора 19, который подготавливает логический элемент И 12 по третьему входу. При появлении отрицательной полуволны напряжения генератора 1, когда возникает импульс на выходе формирователя коротких импульсов 7, через логический элемент И 12 проходит импульс на единичный вход RS-триггера 27. Появляется сигнал на прямом выходе RS-триггера 27, который включает индикатор 28, указывающий на необходимость подрегулировки регулятора частоты.

Если переходное отклонение частоты не превышает допустимую величину, то сигнал на выходе БОЛЬШЕ компаратора 19 не появляется, поддерживая запрет на открытие логического элемента И 12 и включение индикатора 28.

При сбросе нагрузки последующий код мощности, поступающий с выхода регистра 14, меньше предыдущего кода, поступающего с выхода регистра15. Поэтому появляется сигнал на выходе признака положительной разности вычитателя 16, которым RS-триггера 39 переводится в единичное состояние. На вход адреса блока памяти 22 с выходов RS-триггера 39 поступает код «01» и на его выходе появляется код допустимого отклонения частоты при сбросе нагрузки.

Код текущей частоты с выхода счетчика 26 поступает на второй вход компаратора 37, на первый вход которого подан нулевой код с выхода регистра 36, который был обнулен сигналом с шины ПУСК 29. Появляется сигнал на выходе МЕНЬШЕ компаратора 37, который производит запись в регистр 36 код текущей частоты. При сбросе нагрузки частота в начальный период возрастает и в регистр 36 происходит перезапись новых больших кодов. Процесс перезаписи продолжается до момента записи кода максимальной частоты fmax, после чего появляется сигнал на выходе БОЛЬШЕ компаратора 37, который проходит через логический элемент ИЛИ 38 и подготавливает логический элемент И 12 по второму входу. Код максимальной частоты fmax с выхода регистра 36, через электронный ключ 40, включенный сигналом с прямого выхода RS-триггера 39, поступает на первый вход вычитателя 17. На второй вход вычитателя 17 подан код установившейся частоты, с выхода блока памяти 23. На выходе вычитателя 17 появляется код отклонения частоты при сбросе нагрузки δ f пер = fmax -f уст, который подается на первый вход компаратора 19, где сравнивается с нормативной величиной отклонения частоты, код которой поступает на второй вход компаратора 19 с выхода блока памяти 22.

Если отклонение частоты превышает нормативную величину, то появляется сигнал на выходе БОЛЬШЕ компаратора 19, который подготавливает логический элемент И 12 по третьему входу. В момент появления отрицательной полуволны напряжения генератора 1 формируется импульс на выходе формирователя коротких импульсов 7, который проходит через логический элемент И 12 на единичный вход RS-триггера 27. Сигналом с прямого выхода RS-триггера 27 включается индикатор 28, указывающий на запредельное отклонение частоты при сбросе нагрузки.

Таким образом, устройство позволяет в процессе работы электроагрегата оценивать переходное отклонение частоты при набросе и сбросе фиксированной ступени нагрузки без проведения стендовых испытаний.

Источники информации

1. Сугаков В. Г., Хватов О.С. Основы автоматического регулирования выходных электрических параметров автономных источников электрической энергии. Часть 1. Автоматическое регулирование частоты автономных источников электрической энергии: Учебное пособие. Кстово, НВВИКУ, 2008.

2. Сугаков В. Г., Хватов О.С. Системы автоматического регулирования параметров судовых электростанций. Часть 1. Автоматическое регулирование частоты судовых источников электрической энергии. Учебное пособие для студентов (курсантов) специальности 180404. Н. Новгород, Издательство ФГОУ «ВГАВТ», 2010.

3. Патент на изобретение RU № 2793860, МПК G 01 R 31/00, 2023.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ ПЕРЕХОДНОГО ОТКЛОНЕНИЯ ЧАСТОТЫ ДВУНАПРАВЛЕННОЕ | 2024 |

|

RU2819573C1 |

| УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ ВРЕМЕНИ ВОССТАНОВЛЕНИЯ ЧАСТОТЫ ДВУНАПРАВЛЕННОЕ | 2024 |

|

RU2820839C1 |

| УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ ПЕРЕХОДНОГО ОТКЛОНЕНИЯ ЧАСТОТЫ | 2022 |

|

RU2793860C1 |

| ДВУНАПРАВЛЕННОЕ УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ ВРЕМЕНИ ВОССТАНОВЛЕНИЯ ЧАСТОТЫ | 2023 |

|

RU2817045C1 |

| УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ ВРЕМЕНИ ВОССТАНОВЛЕНИЯ ЧАСТОТЫ | 2020 |

|

RU2787747C2 |

| СИСТЕМА РЕГУЛИРОВАНИЯ ВОЗБУЖДЕНИЯ СИНХРОННОГО ГЕНЕРАТОРА С ВНЕШНЕЙ ФОРСИРОВКОЙ | 2019 |

|

RU2723989C1 |

| СИСТЕМА ВОЗБУЖДЕНИЯ СИНХРОННОГО ГЕНЕРАТОРА | 2024 |

|

RU2822126C1 |

| СИСТЕМА ВОЗБУЖДЕНИЯ СИНХРОННОГО ГЕНЕРАТОРА С УПРАВЛЯЕМОЙ ДВУНАПРАВЛЕННОЙ ВНЕШНЕЙ ФОРСИРОВКОЙ | 2021 |

|

RU2781107C1 |

| СИСТЕМА ВОЗБУЖДЕНИЯ СИНХРОННОГО ГЕНЕРАТОРА С ВНЕШНЕЙ ДВУНАПРАВЛЕННОЙ ФОРСИРОВКОЙ | 2019 |

|

RU2725137C1 |

| УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ УСТАНОВИВШЕГОСЯ ОТКЛОНЕНИЯ ЧАСТОТЫ | 2022 |

|

RU2795501C1 |

Изобретение относится к области электротехники, а именно к средствам функциональной диагностики электроагрегатов (ЭА) с двигателями внутреннего сгорания, и может быть использовано в составе систем диагностирования технического состояния передвижных электрических станций. Двунаправленное устройство допускового контроля переходного отклонения частоты содержит генератор 1, зажимы для подключения 2, пусковой орган 3, диод 4, ограничитель-формирователь 5, инвертор 6, формирователь коротких импульсов 7, первый 8 и второй 9 элементы задержки, первый 10, второй 11 и третий 12 логические элементы И, первый 13, второй 14 и третий 15 регистры памяти, первый 16 и второй 17 вычитатели, первый 18, второй 19 и третий 20 числовые компараторы, первый 21 задающий регистр, первый 22 и второй 23 блоки памяти, генератор 24 импульсов стабильной частоты, делитель 25 импульсов, счетчик импульсов 26, первый RS-триггер 27, первый индикатор 28, шину ПУСК 29, датчик 30 трехфазной активной мощности с цифровым выходом, первый 31 и второй 32 логические элементы ИЛИ, электронный ключ 33, второй формирователь 34 коротких импульсов, второй RS-триггер 35, четвертый регистр памяти 36, четвертый числовой компаратор 37, третий логический ИЛИ 38, третий RS-триггер 39, второй 40 и третий 41 электронные ключи. Технический результат – расширение функциональных возможностей. 2 ил.

Двунаправленное устройство допускового контроля переходного отклонения частоты, содержащее второй и первый числовые компараторы, к разрядам второго входа которых подключены соответствующие разряды выхода задающего регистра, шину ПУСК, связанную со сбросовыми входами второго и первого RS-триггера, прямой выход которого соединен с входом индикатора, пусковой орган, подключенный к зажимам генератора, к выходу которого через диод подключен вход ограничителя-формирователя, выход которого соединен со вторым входом первого логического элемента И, связанного первым входом с выходом генератора стабильных импульсов, а выходом – со счетным входом счетчика импульсов, кроме того, выход ограничителя-формирователя связан со входом инвертора, соединенного выходом с входом первого формирователя коротких импульсов, выход которого подключен к входу первого элемента задержки и первому входу второго логического элемента И, а выход БОЛЬШЕ третьего числового компаратора связан со вторым входом второго логического элемента И, выход МЕНЬШЕ – со вторым входом третьего логического элемента И, выход которого подключен к единичному входу первого RS-триггера, первый вход – к выходу первого формирователя коротких импульсов, третий вход – к выходу БОЛЬШЕ второго числового компаратора, а четвертый вход – к единичному входу второго RS-триггера и выходу РАВНО первого числового компаратора, разряды первого входа которого подключены к соответствующим разрядам выхода первого вычитателя, разряды второго входа которого связаны с соответствующими разрядами выхода третьего регистра памяти, а соответствующие разряды первого входа – с соответствующими разрядами входа третьего регистра памяти, входа адреса второго блока памяти и выхода второго регистра памяти, разряды входа которого соединены с соответствующими разрядами выхода датчика трехфазной активной мощности с цифровым выходом, а вход записи подключен к выходу второго элемента задержки, вход которого связан с выходом делителя импульсов, соединенного входом с выходом генератора стабильных импульсов, и входом записи третьего регистра памяти, сбросовый вход которого связан с шиной ПУСК, сбросовым входом первого и второго регистра памяти и первым входом второго логического элемента ИЛИ, связанного вторым входом с выходом первого элемента задержки, а выходом – со сбросовым входом счетчика импульсов, разряды выхода которого связаны с соответствующими разрядами входа первого регистра памяти, с соответствующими разрядами второго входа третьего числового компаратора и соответствующими разрядами выхода электронного ключа, подключенного разрядами входа к шине высокого уровня, а управляющим входом – к выходу второго формирователя коротких импульсов, вход которого соединен прямым выходом второго RS-триггера и третьим входом первого логического элемента И, кроме того, выход второго формирователя коротких импульсов подключен к первому входу первого логического элемента ИЛИ, второй вход которого подключен к выходу второго логического элемента И, а выход – к сбросовому входу третьего регистра памяти, разряды выхода которого связаны с соответствующими разрядами первого входа третьего числового компаратора и разрядами первого входа второго вычитателя, разряды выхода которого подключены к соответствующим разрядам первого входа второго числового компаратора, а разряды второго входа – к соответствующим разрядам выхода второго блока памяти, отличающееся тем, что с целью расширения функциональных возможностей снабжено первым блоком памяти, четвертым числовым компаратором, четвертым регистром памяти, третьим RS-триггером, вторым и третьим электронными ключами и третьим логическим элементом ИЛИ, связанным выходом с вторым входом третьего логического элемента И, первым входом – с выходом МЕНЬШЕ третьего числового компаратора, а вторым входом – с выходом БОЛЬШЕ четвертого числового компаратора, выход МЕНЬШЕ которого подключен к входу записи четвертого регистра памяти, связанного сбросовым входом с шиной ПУСК, разрядами входа – с соответствующими разрядами счетчика и второго входа четвертого числового компаратора, разряды первого входа которого подключены к соответствующим разрядам выхода четвертого регистра памяти и второго электронного ключа, связанного разрядами выхода с соответствующими разрядами первого входа второго вычитателя и входа третьего электронного ключа, соединенного разрядами входа с соответствующими разрядами выхода первого регистра памяти, а управляющим входом – с инверсным выходом третьего RS-триггера, единичный вход которого подключен к выходу признака положительной разности первого вычитателя, который связан выходом признака отрицательной разности с сбросовым входом третьего RS-триггера, разрядами выхода разности – с соответствующими разрядами первого входа первого числового компаратора, разрядами входа вычитаемого – с соответствующими разрядами выхода второго регистра памяти, а разрядами выхода уменьшаемого – с соответствующими разрядами выхода третьего регистра памяти, кроме того, прямой и инверсный выходы третьего RS-триггера подключены к входу адреса первого блока памяти, а управляющий вход второго электронного ключа связан с прямым выходом третьего RS-триггера.

| ДВУНАПРАВЛЕННОЕ УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ ВРЕМЕНИ ВОССТАНОВЛЕНИЯ ЧАСТОТЫ | 2023 |

|

RU2817045C1 |

| УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ ВРЕМЕНИ ВОССТАНОВЛЕНИЯ ЧАСТОТЫ | 2020 |

|

RU2787747C2 |

| Сугаков В.Г., Корсаков С.М | |||

| ТЕХНИЧЕСКИЕ СРЕДСТВА ДОПУСКОВОГО КОНТРОЛЯ ЧАСТОТЫ ДЛЯ ПОВЫШЕНИЯ ЭНЕРГОЭФФЕКТИВНОСТИ ТЕПЛОВОЗОВ | |||

| Актуальные проблемы современного транспорта | |||

| Способ восстановления спиралей из вольфрамовой проволоки для электрических ламп накаливания, наполненных газом | 1924 |

|

SU2020A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| С | |||

| Аппарат, предназначенный для летания | 0 |

|

SU76A1 |

| УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ ПЕРЕХОДНОГО ОТКЛОНЕНИЯ ЧАСТОТЫ | 2022 |

|

RU2793860C1 |

| УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ УСТАНОВИВШЕГОСЯ ОТКЛОНЕНИЯ ЧАСТОТЫ | 2022 |

|

RU2795501C1 |

| ДВУЗОННОЕ УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ УСТАНОВИВШЕГОСЯ ОТКЛОНЕНИЯ ЧАСТОТЫ | 2023 |

|

RU2799658C1 |

| Сугаков В.Г., Ягжов И.И | |||

Авторы

Даты

2024-09-17—Публикация

2024-05-13—Подача