Изобретение относится к области электротехники, а именно к средствам функциональной диагностики электроагрегатов с двигателями внутреннего сгорания и может быть использовано в составе систем диагностирования технического состояния передвижных электрических станций для оценки времени восстановления частоты при набросе и сбросе нагрузки.

Известны методы оценки показателей качества электрической энергии по частоте, включая время восстановления частоты при набросе и сбросе нагрузки посредством стендовых испытаний /1, 2/.

Эти методы требуют специальных стендов с нагрузкой и приборами.

Известны устройства для контроля генераторов /3, 4/, которые обеспечивают не высокую достоверность.

Наиболее близким по технической сущности к изобретению является устройство допускового контроля времени восстановления частоты, содержащее с первого по четвертый логические элементы И, логический элемент ИЛИ, первый и второй RS-триггер, прямой выход которого подключен к входу индикатора, генератор с зажимами, на напряжение которого подключен блок масштабирования, выход которого через диод соединен с входом ограничителя-формирователя, связанного выходом с входом инвертора, первый и второй формирователи коротких импульсов, первый, второй и третий счетчики импульсов, первый и второй электронные ключи, первый, второй и третий регистры памяти, первый, второй и третий числовые компараторы, вычитатель, первый и второй задающие регистры, первый блок памяти, шину ПУСК, генератор импульсов стабильной частоты, делитель импульсов, элемент задержки и датчик трехфазной активной мощности с цифровым выходом, который подключен последовательно к зажимам генератора, а разрядами информационного выхода - к соответствующим разрядам информационного входа второго регистра памяти, разряды выхода которого связаны с соответствующими разрядами входа адреса первого блока памяти, информационного входа третьего регистра памяти и входа уменьшаемого вычитателя, разряды входа вычитаемого которого соединены с соответствующими разрядами выхода третьего регистра памяти, а разряды выхода - с соответствующими разрядами первого входа второго числового компаратора, разряды второго входа которого подключены к соответствующим разрядам выхода первого задающего регистра, а выход РАВНО - к единичному входу первого RS-триггера, прямой выход которого соединен с первым входом третьего логического элемента И, выход которого подключен к счетному входу третьего счетчика, разряды выхода которого связаны с соответствующими разрядами первого входа третьего числового компаратора, подключенного разрядами второго входа к соответствующим разрядам выхода второго задающего регистра, а выходом БОЛЬШЕ - к первому входу четвертого логического элемента И, выход которого соединен с единичным входом второго RS-триггера, а второй вход - с выходом МЕНЬШЕ первого числового компаратора, разряды первого входа которого связаны с соответствующими разрядами выхода первого регистра памяти, разряды информационного входа которого подключены к соответствующим разрядам выходов первого и второго электронного ключа, разряды входов которых связаны с соответствующими разрядами выходов соответственно первого и второго счетчика, счетные входы которых подключены соответственно к выходам первого и второго логического элемента И, первые входы которых соединены с выходом генератора импульсов стабильной частоты, выход которого также подключен к второму входу третьего логического элемента И и входу делителя импульсов, выход которого подключен к входу записи третьего регистра памяти и входу элемента задержки, выход которого соединен с входом записи второго регистра памяти, сбросовый вход которого связан со сбросовыми входами третьего регистра памяти, первого и второго RS-триггеров, третьего счетчика и шиной ПУСК, кроме того выход ограничителя формирователя соединен со вторым входом первого логического элемента И и входом первого формирователя коротких импульсов, выход которого подключен к сбросовому входу первого счетчика, управляющему входу второго электронного ключа и второму входу логического элемента ИЛИ, выход которого соединен с входом записи первого регистра памяти, а первый вход связан с управляющим входом первого электронного ключа, сбросовым входом второго счетчика и выходом второго формирователя коротких импульсов, соединенного входом с выходом инвертора и вторым входом второго логического элемента И151.

Данное устройство позволяет оценить времени восстановления частоты при набросенагрузки в процессеработы электроагрегата. Недостатком его является невозможность контроля времени восстановления частоты при сбросе нагрузки.

Цель изобретения - расширение функциональных возможностей.

Цель изобретения достигается тем, что двунаправленное устройство допускового контроля времени восстановления частоты, содержащее с первого по четвертый логические элементы И, логический элемент ИЛИ, первый и второй RS-триггер, прямой выход которого подключен к входу индикатора, генератор с зажимами, на напряжение которого подключен блок масштабирования, выход которого через диод соединен с входом ограничителя-формирователя, связанного выходом с входом инвертора, первый и второй формирователи коротких импульсов, первый, второй и третий счетчики импульсов, первый и второй электронные ключи, первый, второй и третий регистры памяти, первый, второй и третий числовые компараторы, вычитатель, первый и второй задающие регистры, первый блок памяти, шину ПУСК, генератор импульсов стабильной частоты, делитель импульсов, элемент задержки и датчик трехфазной активной мощности с цифровым выходом, который подключен последовательно к зажимам генератора, а разрядами информационного выхода - к соответствующим разрядам информационного входа второго регистра памяти, разряды выхода которого связаны с соответствующими разрядами входа адреса первого блока памяти, информационного входа третьего регистра памяти и входа уменьшаемого вычитателя, разряды входа вычитаемого которого соединены с соответствующими разрядами выхода третьего регистра памяти, а разряды выхода - с соответствующими разрядами первого входа второго числового компаратора, разряды второго входа которого подключены к соответствующим разрядам выхода первого задающего регистра, а выход РАВНО - к единичному входу первого RS-триггера, прямой выход которого соединен с первым входом третьего логического элемента И, выход которого подключен к счетному входу третьего счетчика, разряды выхода которого связаны с соответствующими разрядами первого входа третьего числового компаратора, подключенного разрядами второго входа к соответствующим разрядам выхода второго задающего регистра, а выходом БОЛЬШЕ - к первому входу четвертого логического элемента И, выход которого соединен с единичным входом второго RS-триггера, а второй вход - с выходом МЕНЬШЕ первого числового компаратора, разряды первого входа которого связаны с соответствующими разрядами выхода первого регистра памяти, разряды информационного входа которого подключены к соответствующим разрядам выходов первого и второго электронного ключа, разряды входов которых связаны с соответствующими разрядами выходов соответственно первого и второго счетчика, счетные входы которых подключены соответственно к выходам первого и второго логического элемента И, первые входы которых соединены с выходом генератора импульсов стабильной частоты, выход которого также подключен к второму входу третьего логического элемента И и входу делителя импульсов, выход которого подключен к входу записи третьего регистра памяти и входу элемента задержки, выход которого соединен с входом записи второго регистра памяти, сбросовый вход которого связан со сбросовыми входами третьего регистра памяти, первого и второго RS-триггеров, третьего счетчика и шиной ПУСК, кроме того выход ограничителя формирователя соединен со вторым входом первого логического элемента И и входом первого формирователя коротких импульсов, выход которого подключен к сбросовому входу первого счетчика, управляющему входу второго электронного ключа и второму входу логического элемента ИЛИ, выход которого соединен с входом записи первого регистра памяти, а первый вход связан с управляющим входом первого электронного ключа, сбросовым входом второго счетчика и выходом второго формирователя коротких импульсов, соединенного входом с выходом инвертора и вторым входом второго логического элемента И отличающееся тем, что снабжено третьим и четвертым электронными ключами, третьим RS-триггером, вторым блоком памяти, вторым индикатором и пятым логическим элементом И, первый вход которого подключен к выходу БОЛЬШЕ третьего компаратора, а второй вход - к выходу БОЛЬШЕ первого компаратора, разряды второго входа которого связаны с соответствующими разрядами выходов третьего и четвертого электронных ключей, разряды входов которых соединены соответственно с разрядами выходов первого и второго блока памяти, разряды входа адреса которого подключены к соответствующим разрядам выхода второго регистра памяти, кроме того выход пятого логического элемента И подключен к единичному входу третьего RS-триггера, сбросовый вход которого соединен с шиной ПУСК, а прямой выход - с входом второго индикатора, причем управляющий вход третьего электронного ключа соединен с выходом признака отрицательной разности вычитателя, а управляющий вход четвертого электронного ключа - с выходом признака положительной разности вычитателя.

Второй блок памяти обеспечивает хранения кода эталонной частоты для случая сброса нагрузки. Третий и четвертый электронные ключи и их связи обеспечивают подачу кодов эталонной частоты для сравнения при набросе и сбросе нагрузки. Пятый логический элемент И, третий RS-триггер и второй индикатор и их связи обеспечивают индикацию факта выхода времени восстановления частоты при сбросе нагрузки за пределы допустимой зоны.

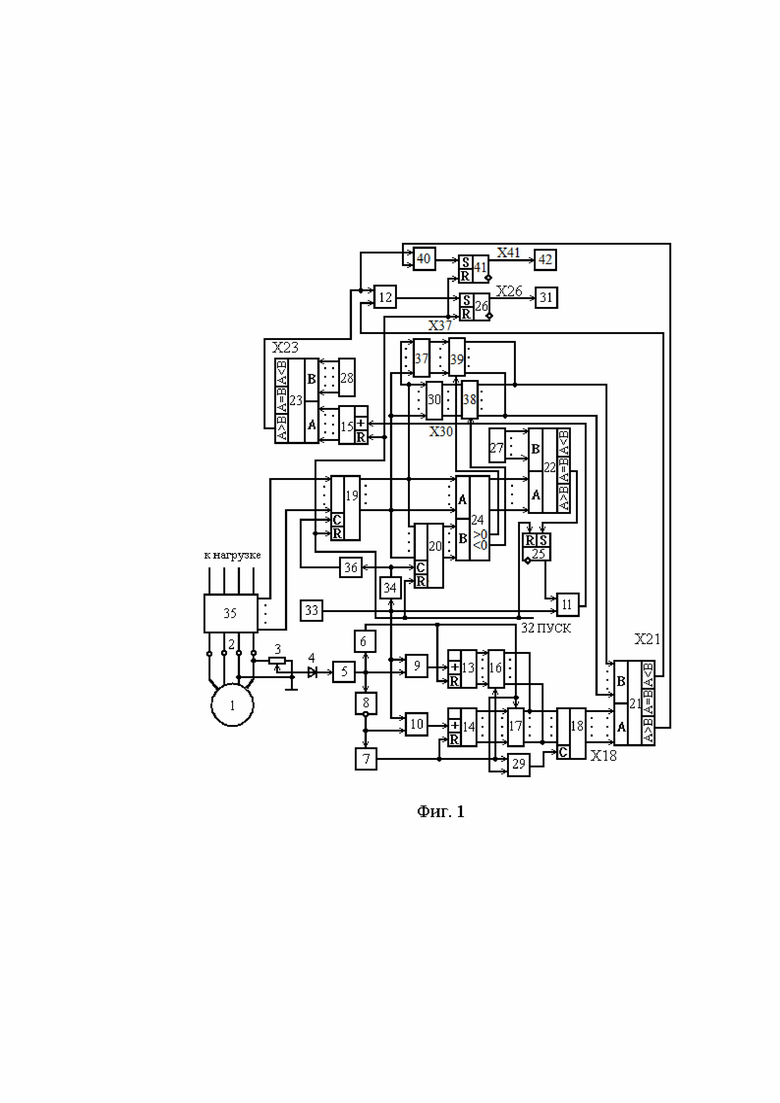

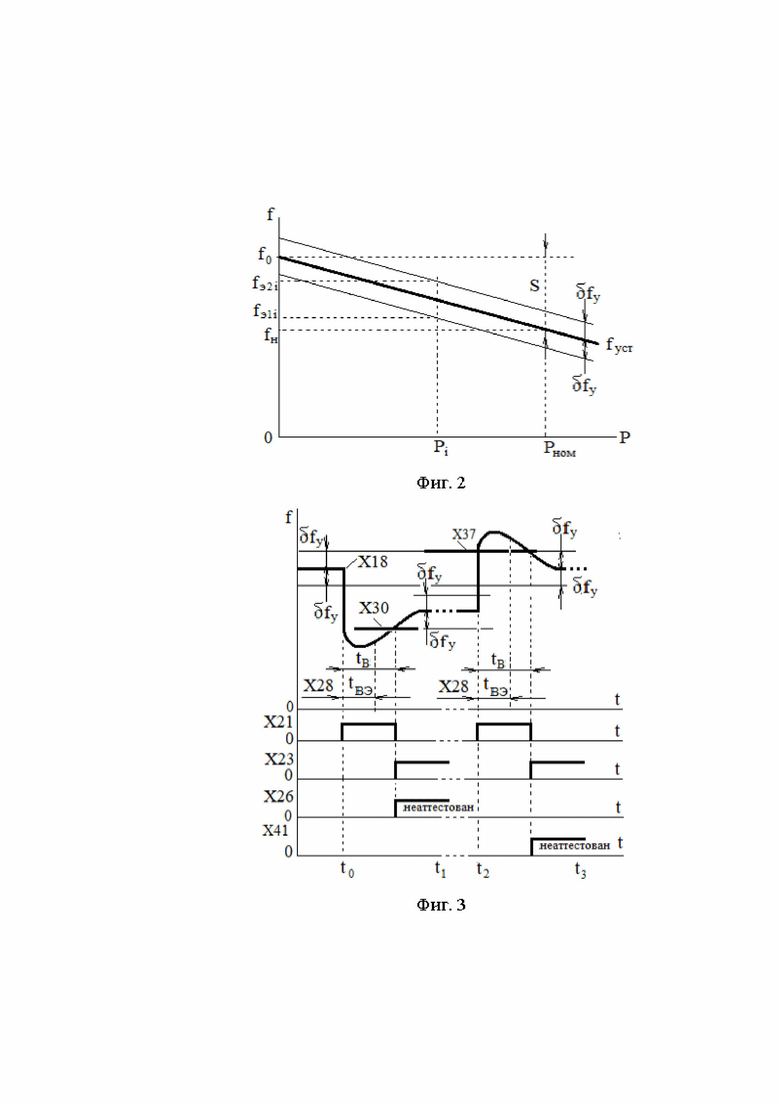

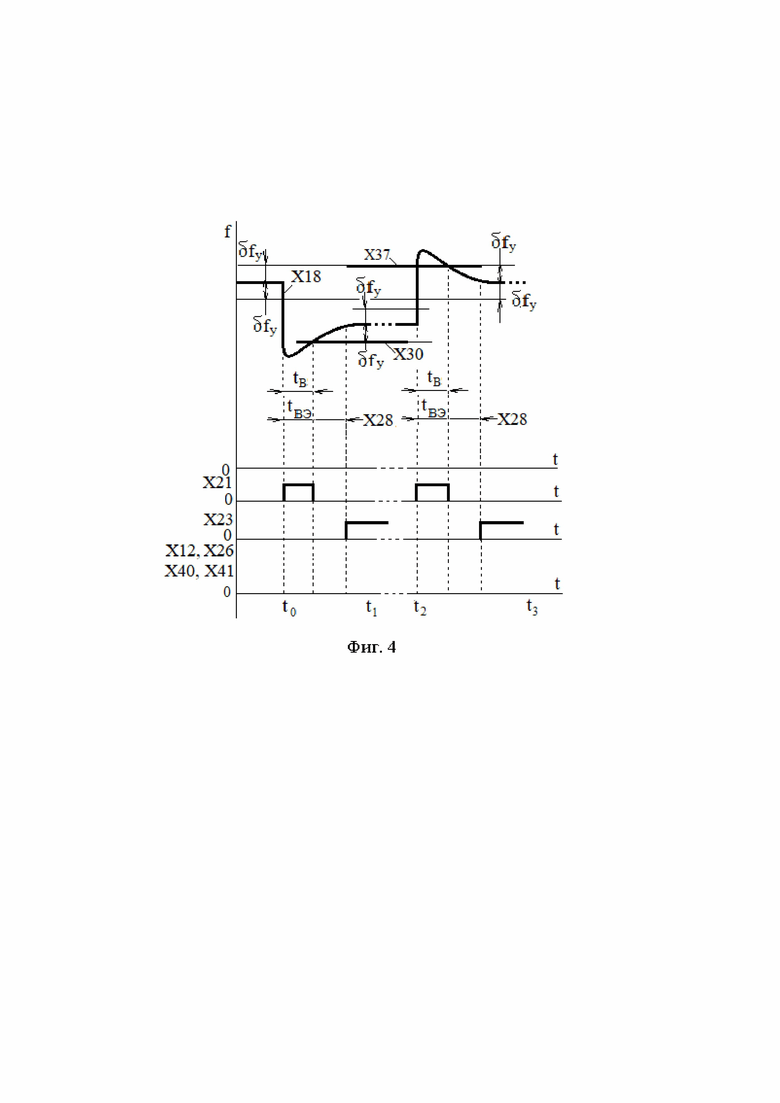

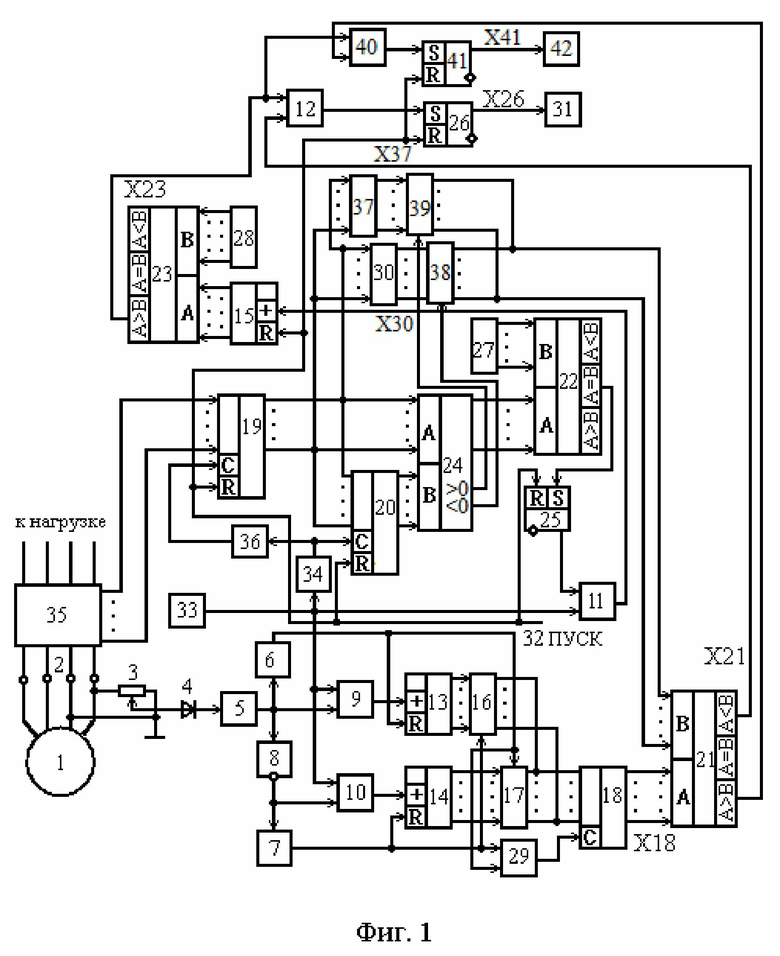

На фиг. 1 представлена схема двунаправленного устройства допусково-го контроля времени восстановления частоты, на фиг. 2 - зависимость частоты  от нагрузки Р, генератора (регуляторная характеристика электроагрегата), на фиг. 3 - эпюры сигналов на основных элементах схемы при неблагоприятном исходе контроля, на фиг. 4 - эпюры сигналов на основных элементах схемы при благоприятном исходе контроля.

от нагрузки Р, генератора (регуляторная характеристика электроагрегата), на фиг. 3 - эпюры сигналов на основных элементах схемы при неблагоприятном исходе контроля, на фиг. 4 - эпюры сигналов на основных элементах схемы при благоприятном исходе контроля.

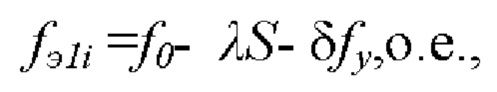

Схема устройства (фиг. 1) содержит генератор 1, зажимы для подключения 2, блок масштабирования 3, диод 4, ограничитель-формирователь 5, первый 6 и второй 7 формирователи коротких импульсов, инвертор 8, первый 9, второй 10, третий 11 и четвертый 12 логические элементы И, первый 13, второй 14 и третий 15 счетчики импульсов, первый 16 и второй 17 электронные ключи, первый 18, второй 19 и третий 20 регистры памяти, первый 21, второй 22 и третий 23 числовые компараторы, вычитатель 24, первый 25 и второй 26 RS-триггеры, первый 27 и второй 28 задающие регистры, логический элемент ИЛИ 29, первый блок памяти 30, индикатор 31, шина ПУСК 32, генератор 33 импульсов стабильной частоты, делитель 34 импульсов, датчик 35 трехфазной активной мощности с цифровым выходом, элемент задержки 36, второй блок памяти 37, третий 38 и четвертый 39 электронный ключ, пятый логический элемент И 40, третий RS-триггер 41и второй индикатор 42. В ячейки блока 30 памяти занесены коды эталонной частоты  в зависимости от мощности Pi нагрузки генератора (фиг. 2) которые соответствуют выражению для относительной эталонной частоты

в зависимости от мощности Pi нагрузки генератора (фиг. 2) которые соответствуют выражению для относительной эталонной частоты

где  - относительная частота на холостом ходу генератора, о. е.

- относительная частота на холостом ходу генератора, о. е.

- абсолютная частота на холостом ходу генератора, Гц;

- абсолютная частота на холостом ходу генератора, Гц;

- абсолютная номинальная частота генератора, Гц;

- абсолютная номинальная частота генератора, Гц;

λ - относительная активная мощность нагрузки генератора, о.е.

Pi - текущая активная мощность нагрузки генератора, кВт;

Рном - номинальная активная мощность нагрузки генератора, кВт;

S- наклон (статизм)регуляторной характеристики электроагрегата;

- установившееся отклонение частоты при неизменной нагрузке (допустимая нестабильность частоты) о.е.

- установившееся отклонение частоты при неизменной нагрузке (допустимая нестабильность частоты) о.е.

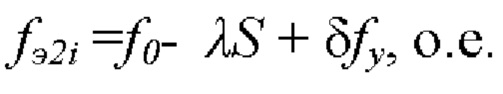

В ячейки блока 37 памяти занесены коды эталонной частоты  в зависимости от мощности Pi нагрузки генератора (фиг. 2), которые соответствуют выражению для относительной эталонной частоты

в зависимости от мощности Pi нагрузки генератора (фиг. 2), которые соответствуют выражению для относительной эталонной частоты

Устройство работает следующим образом. В регистр 27 заносится код контролируемой ступени наброса нагрузки (стандартные величины 25%, 50%) или 100%) от номинальной мощности). В регистр 28 записывается код нормативного времени восстановления частоты для принятой ступени наброса (зависит от класса точности регулятора частоты). Подается сигнал на шину ПУСК 32, которым обнуляются счетчик 15 и регистры памяти 19 и 20, a RS-триггеры 25, 26 и 41 переводятся в состояние когда сигнал на прямом выходе отсутствует.

С момента возбуждения генератора 1 на зажимах 2 присутствует напряжение, которое подается на блок масштабирования 3. С блока масштабирования 3 через диод 4 на вход ограничителя-формирователя 5 подается положительная полуволна напряжения генератора 1, и на выходе ограничителя-формирователя 5 появляется импульс, длительность которого равна полупериоду напряжения генератора. Этот импульс подготавливает элемент И 9 по второму входу. На счетный вход счетчика 13 через первый вход элемента И 9 начинают поступать импульсы с выхода генератора импульсов 33. На выходе счетчика 13 формируется код частоты генератора 1 за положительную полуволну.

При появлении отрицательной полуволны напряжения генератора 1 сигнал на выходе ограничителя-формирователя 5 исчезает, и появляется сигнал на выходе инвертора 8, который подготавливает элемент И 10 по второму входу. По его фронту импульса с выхода инвертора 8 формирователь коротких импульсов 7 выдает импульс. Этот импульс обнуляет счетчик 14 и кратковременно открывает ключ 16, который подключает выход счетчика 13 к входу регистра 18. Этот же импульс с выхода формирователя 7 поступает через элемент ИЛИ 29 на вход записи регистра 18, в который записывается код текущей частоты с выхода счетчика 13. На выходе регистра 18 появляется код текущей частоты генератора 1. Одновременно начинается формирование очередного кода частоты за отрицательный полупериод. Через первый вход элемента И 10 импульсы генератора 33 поступают счетный вход счетчика 14, на выходе которого формируется очередной код частоты. Его формирование завершается с появлением следующей положительной полуволны напряжения, когда вновь появляется сигнал на выходе ограничителя-формирователя 5, который подготавливает элемент И 9 по второму входу. По фронту этого же сигнала формирователь коротких импульсов 6 выдает импульс, которым кратковременно открывается ключ 17 и импульсом через элемент ИЛИ 29 записывается в регистр памяти 18 код частоты с выхода счетчика 14. Далее процесс формирования кода частоты генератора 1 повторяется, а на выходе регистра памяти 18 постоянно присутствует код текущей частоты.

Вместе с тем осуществляется анализ изменения нагрузки по коду мощности на выходе датчика 35. После появления сигнала на шине ПУСК 32 на выходах регистров памяти 19 и 20 присутствует нулевой код. При появлении первого импульса на выходе делителя 34 в регистр 20 переписывается нулевой код, а в регистр 19 с выдержкой времени, заданной элементом задержки 36, код мощности. При втором и последующих импульсах с выхода делителя 34 в регистр 20 осуществляется перезапись кода мощности в предыдущий момент времени с выхода регистра 19, а в регистр 20 записывается код мощности в текущий момент времени с выхода датчика 35. В результате на выходе регистра 20 постоянно присутствует код мощности в предыдущий момент времени, который подается на вход уменьшаемого вычитателя 24, а на выходе регистра 19 постоянно устанавливается код мощности в последующий момент, который поступает на вход вычитаемого вычитателя 24. На выходе вычитателя 24 в течение всей работы электроагрегата присутствует код величины изменения мощности нагрузки, который поступает на первый вход компаратора 22.

Если в процессе работы электроагрегата величина изменения нагрузки соответствует контролируемой, то код на первом входе компаратора 22 совпадает с кодом на выходе задающего регистра 27, по данным на второй вход компаратора 22. При этом появляется сигнал на выходе РАВНО компаратора 22, который переводит RS-триггер 25 в единичное состояние. Сигнал с прямого выхода RS-триггера 25 подготавливает элемент И 11 по первому входу и через его на счетный вход счетчика 15 начинают поступать импульсы с выхода генератора 33, формируя на выходе счетчика 15 код времени переходного процесса, который поступает на первый вход числового компаратора 23. Когда это время превышает нормативное временя, код которого установлен на выходе задатчика 28 и подан на второй вход компаратора 23, появляется сигнал Х23 на выходе БОЛЬШЕ компаратора 23 (фиг. 3). Этот сигнал Х23 подготавливает элементы И 12 и 40 по первому входу. На входы адреса блоков памяти 30 и 37 поступает код текущего значения мощности и на их выходах появляются соответственно коды Х30 и Х37 (фиг. 3) нормативной частоты, соответствующей данной мощности с учетом наклона регуляторной характеристики и допустимой нестабильности частоты.

Если происходит наброс нагрузки (фиг. 3 интервал времени t0 - t1), то код мощности в предыдущий момент времени, поступающий с регистра 20 на вход уменьшаемого вычитателя 24, меньше кода мощности в последующий момент времени, поступающий с выхода регистра 19 на вход вычитаемого вычитателя 24. Поэтому появляется сигнал на выходе признака отрицательной разности вычитателя 24, который открывает электронный ключ 38, и подает на второй вход компаратора 21 с выхода блока памяти 30 код Х30 нормативной частоты  Если текущая частота, код XI8 которой подан с выхода регистра 18 на первый вход компаратора 21, меньше кода Х30 нормативной частоты, появляется сигнал на выходе МЕНЬШЕ компаратора 21, который проходит через элемент И 12 и переводит RS-триггер 26 в единичное состояние. Сигнал Х26 с прямого выхода RS-триггера 26 подается на индикатор 31, который указывает на несоответствие времени восстановления при набросе нагрузки требованиям стандарта.

Если текущая частота, код XI8 которой подан с выхода регистра 18 на первый вход компаратора 21, меньше кода Х30 нормативной частоты, появляется сигнал на выходе МЕНЬШЕ компаратора 21, который проходит через элемент И 12 и переводит RS-триггер 26 в единичное состояние. Сигнал Х26 с прямого выхода RS-триггера 26 подается на индикатор 31, который указывает на несоответствие времени восстановления при набросе нагрузки требованиям стандарта.

Если происходит сброс нагрузки (фиг. 3 интервал времени t2 - t3), то код мощности в предыдущий момент времени, поступающий с регистра 20 на вход уменьшаемого вычитателя 24, больше кода мощности в последующий момент времени, поступающий с выхода регистра 19 на вход вычитаемого вычитателя 24. Поэтому появляется сигнал на выходе признака положительной разности вычитателя 24, который открывает электронный ключ 39, и подает на второй вход компаратора 21 с выхода блока памяти 37 код Х37 нормативной частоты  Если по истечении нормативного времени после сброса нагрузки частота не вошла в зону допустимой нестабильности то, код XI8 текущей частоты поступающий с выхода регистра 18 на первый вход компаратора 21, больше кода Х37 нормативной частоты. Поэтому появляется сигнал на выходе БОЛЬШЕ компаратора 21, который проходит через элемент И 40 и переводит RS-триггер 41 в единичное состояние. Сигнал Х41 с прямого выхода RS-триггера 41 подаетсяна индикатор 42, который указывает на несоответствие времени восстановления при сбросе нагрузки требованиям стандарта и необходимость проведения подрегулировки регулятора частоты.

Если по истечении нормативного времени после сброса нагрузки частота не вошла в зону допустимой нестабильности то, код XI8 текущей частоты поступающий с выхода регистра 18 на первый вход компаратора 21, больше кода Х37 нормативной частоты. Поэтому появляется сигнал на выходе БОЛЬШЕ компаратора 21, который проходит через элемент И 40 и переводит RS-триггер 41 в единичное состояние. Сигнал Х41 с прямого выхода RS-триггера 41 подаетсяна индикатор 42, который указывает на несоответствие времени восстановления при сбросе нагрузки требованиям стандарта и необходимость проведения подрегулировки регулятора частоты.

Если время восстановления частоты tB меньше нормативного времени tBЭ (фиг. 4), то к моменту появления сигнала Х23 на выходе числового компаратора 23 сигнал Х21 на выходе числового компаратора 21 исчезает закрывая элемент И12 (при набросе нагрузки) или элемент И 40 (при сбросе нагрузки) по второму входу, препятствуя изменению состояния соответственно RS-триггера 26 или 41. Индикаторы 31 и 42 не указывают на необходимость подстройки регулятора частоты.

Таким образом, устройство позволяет в процессе работы электроагрегата оценивать время восстановления частоты при фиксированной ступени наброса или сброса нагрузки без проведения стендовых испытаний.

Источники информации

1. Сугаков В.Г., Хватов О.С. Основы автоматического регулирования выходных электрических параметров автономных источников электрической энергии. Часть 1. Автоматическое регулирование частоты автономных источников электрической энергии: Учебное пособие. Кстово, НВВИКУ, 2008.

2. Сугаков В.Г., Хватов О.С. Системы автоматического регулирования параметров судовых электростанций. Часть 1. Автоматическое регулирование частоты судовых источников электрической энергии. Учебное пособие для студентов (курсантов) специальности 180404. Н. Новгород, Издательство ФГОУ «ВГАВТ», 2010.

3. Авторское свидетельство СССР №632022, кл. H02Н 3/44, 1977.

4. Авторское свидетельство СССР №1260885, кл. G01R 31/34, 1985.

5. Устройство доггускового контроля времени восстановления частоты Описание к патенту на изобретение№2787747, кл. G01R 31/34, 2023.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДВУНАПРАВЛЕННОЕ УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ ПЕРЕХОДНОГО ОТКЛОНЕНИЯ ЧАСТОТЫ | 2024 |

|

RU2826860C1 |

| УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ ВРЕМЕНИ ВОССТАНОВЛЕНИЯ ЧАСТОТЫ ДВУНАПРАВЛЕННОЕ | 2024 |

|

RU2820839C1 |

| УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ ПЕРЕХОДНОГО ОТКЛОНЕНИЯ ЧАСТОТЫ ДВУНАПРАВЛЕННОЕ | 2024 |

|

RU2819573C1 |

| УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ ПЕРЕХОДНОГО ОТКЛОНЕНИЯ ЧАСТОТЫ | 2022 |

|

RU2793860C1 |

| УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ ВРЕМЕНИ ВОССТАНОВЛЕНИЯ ЧАСТОТЫ | 2020 |

|

RU2787747C2 |

| СИСТЕМА ВОЗБУЖДЕНИЯ СИНХРОННОГО ГЕНЕРАТОРА | 2024 |

|

RU2822126C1 |

| СИСТЕМА РЕГУЛИРОВАНИЯ ВОЗБУЖДЕНИЯ СИНХРОННОГО ГЕНЕРАТОРА С ВНЕШНЕЙ ФОРСИРОВКОЙ | 2019 |

|

RU2723989C1 |

| СИСТЕМА ВОЗБУЖДЕНИЯ СИНХРОННОГО ГЕНЕРАТОРА С УПРАВЛЯЕМОЙ ДВУНАПРАВЛЕННОЙ ВНЕШНЕЙ ФОРСИРОВКОЙ | 2021 |

|

RU2781107C1 |

| СИСТЕМА ВОЗБУЖДЕНИЯ СИНХРОННОГО ГЕНЕРАТОРА С ВНЕШНЕЙ ДВУНАПРАВЛЕННОЙ ФОРСИРОВКОЙ | 2019 |

|

RU2725137C1 |

| ДВУЗОННОЕ УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ УСТАНОВИВШЕГОСЯ ОТКЛОНЕНИЯ ЧАСТОТЫ | 2023 |

|

RU2799658C1 |

Изобретение относится к области электротехники и может быть использовано в составе систем диагностирования технического состояния передвижных электрических станций для оценки времени восстановления частоты при набросе нагрузки. Устройство содержит генератор 1, зажимы для подключения 2, блок масштабирования 3, диод 4, ограничитель-формирователь 5, первый 6 и второй 7 формирователи коротких импульсов, инвертор 8, первый 9, второй 10, третий 11 и четвертый 12 логические элементы И, первый 13, второй 14 и третий 15 счетчики импульсов, первый 16 и второй 17 электронные ключи, первый 18, второй 19 и третий 20 регистры памяти, первый 21, второй 22 и третий 23 числовые компараторы, вычитатель 24, первый 25 и второй 26 RS-триггеры, первый 27 и второй 28 задающие регистры, логический элемент ИЛИ 29, первый блок памяти 30, индикатор 31, шина ПУСК 32, генератор 33 импульсов стабильной частоты, делитель 34 импульсов, датчик 35 трехфазной активной мощности с цифровым выходом, элемент задержки 36, второй блок памяти 37, третий 38 и четвертый 39 электронный ключ, пятый логический элемент И 40, третий RS-триггер 41 и второй индикатор 42. Устройство позволяет в процессе работы электроагрегата оценивать время восстановления частоты при фиксированной ступени наброса или сброса нагрузки без проведения стендовых испытаний. Технический результат - расширение функциональных возможностей. 4 ил.

Двунаправленное устройство допускового контроля времени восстановления частоты, содержащее с первого по четвертый логические элементы И, логический элемент ИЛИ, первый и второй RS-триггер, прямой выход которого подключен к входу индикатора, генератор с зажимами, на напряжение которого подключен блок масштабирования, выход которого через диод соединен с входом ограничителя-формирователя, связанного выходом с входом инвертора, первый и второй формирователи коротких импульсов, первый, второй и третий счетчики импульсов, первый и второй электронные ключи, первый, второй и третий регистры памяти, первый, второй и третий числовые компараторы, вычитатель, первый и второй задающие регистры, первый блок памяти, шину ПУСК, генератор импульсов стабильной частоты, делитель импульсов, элемент задержки и датчик трехфазной активной мощности с цифровым выходом, который подключен последовательно к зажимам генератора, а разрядами информационного выхода – к соответствующим разрядам информационного входа второго регистра памяти, разряды выхода которого связаны с соответствующими разрядами входа адреса первого блока памяти, информационного входа третьего регистра памяти и входа уменьшаемого вычитателя, разряды входа вычитаемого которого соединены с соответствующими разрядами выхода третьего регистра памяти, а разряды выхода – с соответствующими разрядами первого входа второго числового компаратора, разряды второго входа которого подключены к соответствующим разрядам выхода первого задающего регистра, а выход РАВНО – к единичному входу первого RS-триггера, прямой выход которого соединен с первым входом третьего логического элемента И, выход которого подключен к счетному входу третьего счетчика, разряды выхода которого связаны с соответствующими разрядами первого входа третьего числового компаратора, подключенного разрядами второго входа к соответствующим разрядам выхода второго задающего регистра, а выходом БОЛЬШЕ – к первому входу четвертого логического элемента И, выход которого соединен с единичным входом второго RS-триггера, а второй вход – с выходом МЕНЬШЕ первого числового компаратора, разряды первого входа которого связаны с соответствующими разрядами выхода первого регистра памяти, разряды информационного входа которого подключены к соответствующим разрядам выходов первого и второго электронного ключа, разряды входов которых связаны с соответствующими разрядами выходов соответственно первого и второго счетчика, счетные входы которых подключены соответственно к выходам первого и второго логического элемента И, первые входы которых соединены с выходом генератора импульсов стабильной частоты, выход которого также подключен к второму входу третьего логического элемента И и входу делителя импульсов, выход которого подключен к входу записи третьего регистра памяти и входу элемента задержки, выход которого соединен с входом записи второго регистра памяти, сбросовый вход которого связан со сбросовыми входами третьего регистра памяти, первого и второго RS-триггеров, третьего счетчика и шиной ПУСК, кроме того выход ограничителя формирователя соединен со вторым входом первого логического элемента И и входом первого формирователя коротких импульсов, выход которого подключен к сбросовому входу первого счетчика, управляющему входу второго электронного ключа и второму входу логического элемента ИЛИ, выход которого соединен с входом записи первого регистра памяти, а первый вход связан с управляющим входом первого электронного ключа, сбросовым входом второго счетчика и выходом второго формирователя коротких импульсов, соединенного входом с выходом инвертора и вторым входом второго логического элемента И, отличающееся тем, что снабжено третьим и четвертым электронными ключами, третьим RS-триггером, вторым блоком памяти, вторым индикатором и пятым логическим элементом И, первый вход которого подключен к выходу БОЛЬШЕ третьего компаратора, а второй вход – к выходу БОЛЬШЕ первого компаратора, разряды второго входа которого связаны с соответствующими разрядами выходов третьего и четвертого электронных ключей, разряды входов которых соединены соответственно с разрядами выходов первого и второго блока памяти, разряды входа адреса которого подключены к соответствующим разрядам выхода второго регистра памяти, кроме того выход пятого логического элемента И подключен к единичному входу третьего RS-триггера, сбросовый вход которого соединен с шиной ПУСК, а прямой выход – с входом второго индикатора, причем управляющий вход третьего электронного ключа соединен с выходом признака отрицательной разности вычитателя, а управляющий вход четвертого электронного ключа – с выходом признака положительной разности вычитателя.

| УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ ВРЕМЕНИ ВОССТАНОВЛЕНИЯ ЧАСТОТЫ | 2020 |

|

RU2787747C2 |

| Устройство для измерения времени выбега электрической машины | 1985 |

|

SU1260885A1 |

| Устройство для определения времени выбега электрической машины | 1982 |

|

SU1092668A1 |

| Устройство для определения времени выбега электрической машины | 1984 |

|

SU1183929A1 |

| Реле скорости изменения частоты | 1977 |

|

SU632022A1 |

| CN 102109575 B, 11.02.2015. | |||

Авторы

Даты

2024-04-09—Публикация

2023-11-17—Подача