Область техники

Изобретение относится к электронной технике и может использоваться при разработке микросхем приемных трактов. В связи с ростом динамического диапазона приемных трактов и увеличением значения цифровой обработки сигнала возросла потребность в схемах индикации уровня сигнала на входе приемного устройства (Received Signal Strength Indication - RSSI). Данные о величине входного сигнала позволяют избежать перегрузки и используются для цифрового управления всем устройством, что позволяет обеспечивать требуемый диапазон величин входных сигналов.

В качестве примера применения подобных устройств можно привести работу сотовых телефонов на разном расстоянии от базовой станции сотовой связи. При приближении к базовой станции необходимо уменьшать усиление во входных каскадах во избежание «забитая» приемного тракта и наоборот требуется максимальное усиление при значительном удалении от базовой станции. Аналогичная ситуация возникает и в радиолокационных устройствах, а также везде, где приходится иметь дело с сигналами широкого динамического диапазона. Предлагаемое изобретение имеет своей целью устранение дополнительных настроек и регулировок в траках RSSI, которые существуют в настоящее время.

Предшествующий уровень техники

Из уровня техники известны технические решения, обеспечивающие построение трактов RSSI. Ряд зарубежных фирм серийно выпускает подобные устройства, построенные на основе логарифмирующих трактов по методу последовательного детектирования, наилучшие результаты достигнуты известной фирмой Analog Devices, США. За последние десятилетия этой фирмой разработан целый ряд подобных устройств, имеющих близкую структуру и отличающихся частотным и динамическим диапазонами (AD640 и последующие) [1], которые выполнены большей частью по биполярной технологии, в последние годы по SiGe процессу.

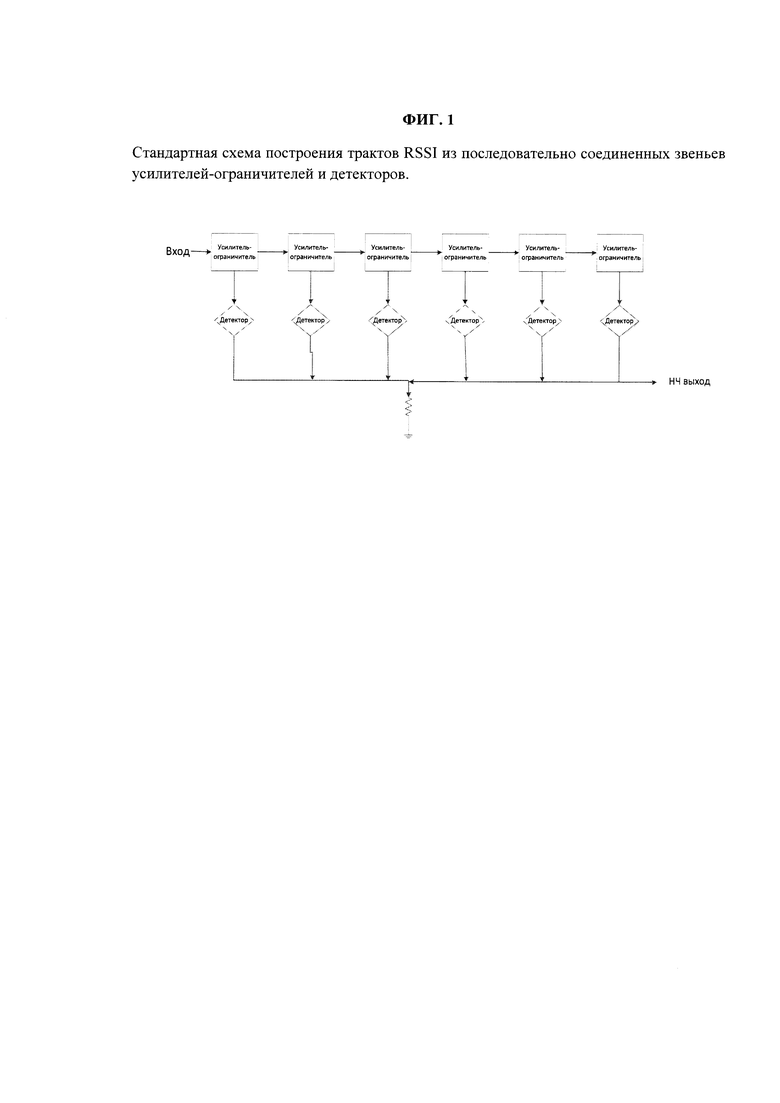

Основой данного класса схем является тракт логарифмирующей обработки сигнала. Упрощенная блок-схема логарифмирующего тракта по методу последовательного детектирования, представлена на ФИГ. 1. Следует отметить, что современные тракты в интегральном исполнении выполняются на основе дифференциальных каскадов.

Основой тракта является последовательное соединение нескольких звеньев состоящих из усилителя-ограничителя (УО) и детектора на смещенном дифференциальном каскаде. Сигнал со всех детекторов суммируется на общей нагрузке и при правильно выбранном коэффициенте передачи и пороге УО обеспечивает логарифмическую зависимость между уровнем мощности входного сигнала и выходным напряжением.

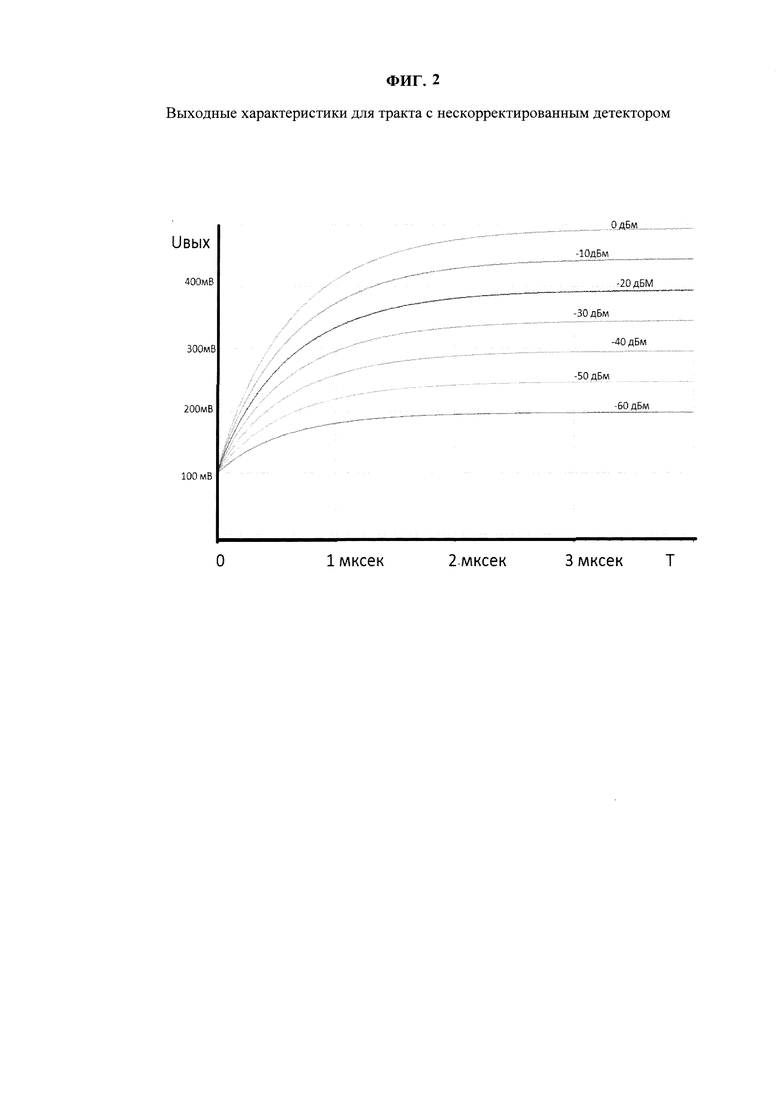

Известные зарубежные аналоги данного типа требуют наличия ряда дополнительных выводов для подстройки и подключения внешних регулируемых резисторов и блокирующих конденсаторов большой емкости. Важным вопросом является наличие «пьедестала» [1] при работе детектора, выполненного по известной схеме на смещенном дифференциальном каскаде. Данный «пьедестал» является суммой падения напряжения на выходном резисторе от малых токов детекторов всех каскадов при нулевом сигнале на входе. На ФИГ. 2 представлены графики выходного напряжения логарифмирующего тракта последовательного детектирования для разных уровней входного сигнала. Видно, что при сколь угодно малом сигнале на выходе существует «пьедестал» равный в данном случае 100 мВ. Это напряжение, соответствующее отсутствию сигнала на входе может меняться в определенных пределах из-за технологического разброса и не позволяет гальванически подключать аналого-цифровой преобразователь (АЦП), а также требует для его устранения дополнительной калибровки, путем подстройки через внешний источник постоянного тока и резистор, как рекомендуется во всех описаниях известных зарубежных микросхем данного типа [1].

Раскрытие изобретения

Задачей настоящего изобретения является исключение внешних элементов подстройки для полупроводниковых микросхем трактов индикации уровня сигнала на входе приемного устройства.

Техническим результатом, на достижение которого направлено заявленное изобретение, является устранение описанного эффекта наличия «пьедестала» -произвольного напряжения на выходе микросхем трактов индикации уровня сигнала при отсутствии входного сигнала.

Описание способа достижения результата

Сущность изобретения поясняется чертежами.

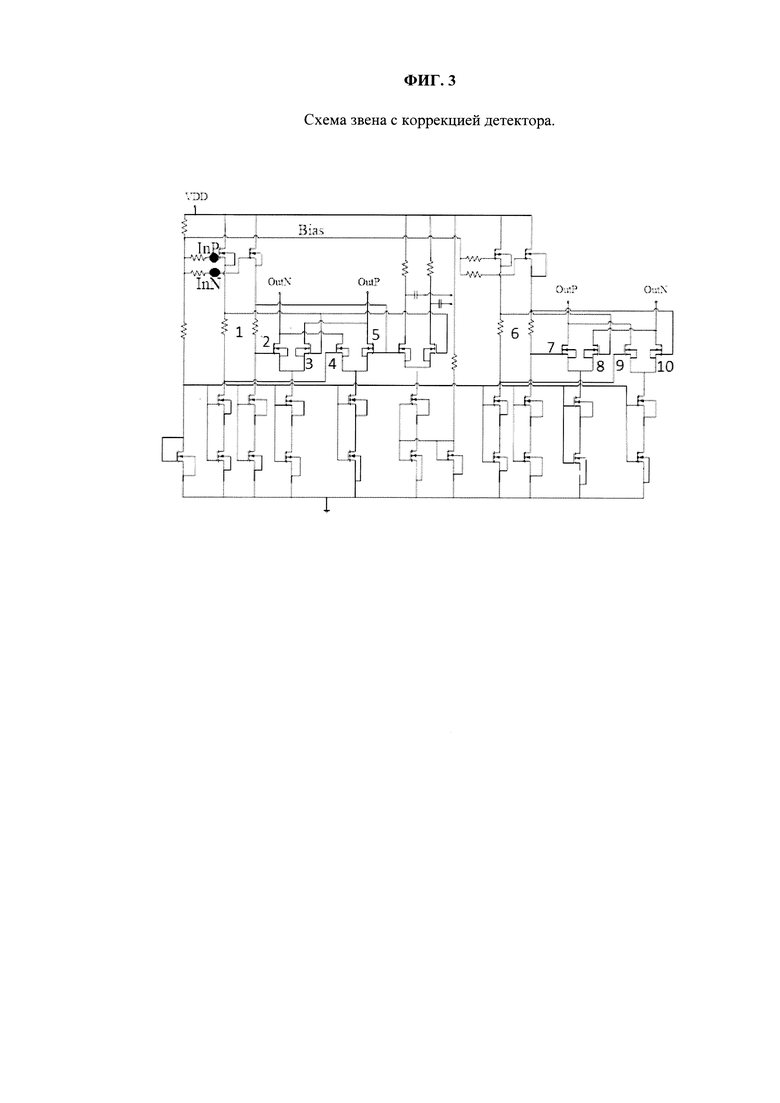

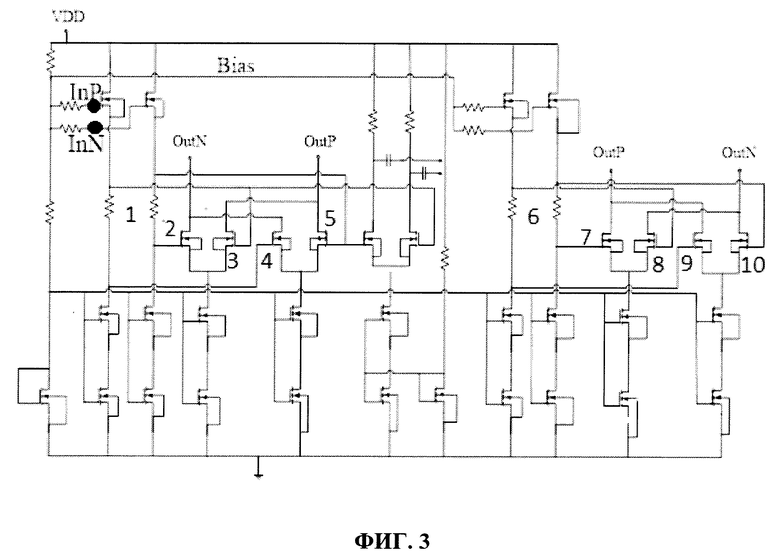

На ФИГ. 3 представлено новое решение звена с коррекцией разбаланса детектора по постоянному току. Звено состоит из детектора на смещенном дифференциальном каскаде, выполненном по известному схемотехническому решению и дополнительного компенсирующего детектора. Указанный технический результат достигается тем, что в качестве корректирующего устройства, разбаланса смещенного детектора, выполненного в известном исполнении на резисторах смещения 1 и транзисторах 2-5 и на который подается сигнал через входы InP, InN, используется дополнительный детектор также расположенный на кристалле идентичный основному, выполненный на резисторах смещения 6 и транзисторах 7-10, но без подачи на него сигнала, а его статический ток на выходах OutP, OutN в противофазе складывается с током основного детектора.

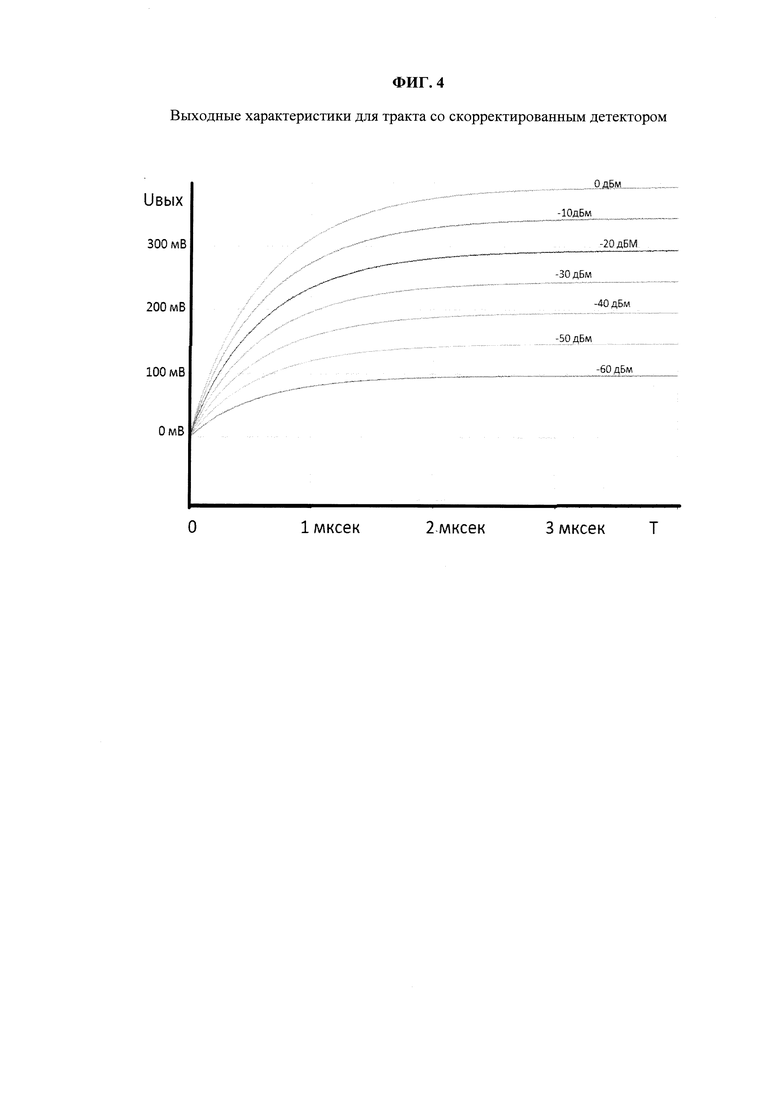

Статические выходные токи основного и дополнительного детекторов складываясь на общем резисторе нагрузки всех звеньев, ФИГ. 1, при дифференциальном включении создают равные потенциалы на инвертированном и неинвертированном выходе. Таким образом, обеспечивается нулевое смещение на выходе детектора при отсутствии входного сигнала. За счет выбора режима детектора с малым потреблением общее увеличение тока потребления оказывается несущественным. На ФИГ. 4 представлены выходные характеристики тракта с коррекцией детектора. Все графики начинаются из нулевой точки, схема пригодна для гальванического соединения с блоком АЦП и не требует дополнительных подстроек.

Источники информации:

1. Datasheet Analog Devices AD640; Datasheet Analog Devices AD641; Datasheet Analog Devices AD8306; Datasheet Analog Devices AD8307; Datasheet Analog Devices AD8309; Datasheet Analog Devices AD8318.

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель-ограничитель с корректировкой разбаланса в схемах идентификации уровня сигнала | 2022 |

|

RU2806698C1 |

| Операционный усилитель с промежуточным двухтактным «перегнутым» каскодом на комплементарных полевых транзисторах | 2024 |

|

RU2837569C1 |

| ШИРОКОПОЛОСНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2010 |

|

RU2419196C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ | 2009 |

|

RU2416148C1 |

| УПРАВЛЯЕМЫЙ УСИЛИТЕЛЬ | 2010 |

|

RU2421883C1 |

| Устройство передачи данных с гальванической развязкой посредством импульсного трансформатора | 2019 |

|

RU2714224C1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ НЕЭЛЕКТРИЧЕСКОЙ ВЕЛИЧИНЫ В ЭЛЕКТРИЧЕСКИЙ СИГНАЛ | 1995 |

|

RU2087857C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2006 |

|

RU2319290C1 |

| Двухтактный усилитель мощности | 2024 |

|

RU2832230C1 |

| СКАНИРУЮЩЕЕ УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПРОСТРАНСТВЕННОГО РАСПРЕДЕЛЕНИЯ МОЩНОСТИ ЭКСПОЗИЦИОННОЙ ДОЗЫ ГАММА-ИЗЛУЧЕНИЯ В АКТИВНОЙ ЗОНЕ ОСТАНОВЛЕННЫХ УРАН-ГРАФИТОВЫХ РЕАКТОРОВ | 2003 |

|

RU2248010C2 |

Изобретение относится к электротехнике. Технический результат - устранение произвольного напряжения на выходе микросхем трактов индикации уровня сигнала при отсутствии входного сигнала. Для этого предложен детектор сигналов с коррекцией, включающий двухполупериодный детектор, выполненный на двух дифференциальных парах, состоящих из транзисторов и резисторов смещения, а также корректирующий детектор, состоящий из транзисторов и резисторов смещения. Причем детектор сигналов и корректирующий детектор выполнены на кристалле с высокой степенью идентичности. Таким образом, малый статический ток от детектора сигналов складывается с большим током от корректирующего детектора, и наоборот, большой статический ток от детектора сигналов складывается с малым током от корректирующего детектора, что приводит к равенству потенциалов на выходах OutN и OutP, т.е. к нулевому дифференциальному напряжению при нулевом сигнале на входе. 4 ил.

Детектор сигналов с коррекцией, включающий двухполупериодный детектор, выполненный на двух дифференциальных парах, состоящих из первого транзистора (2), второго транзистора (3), третьего транзистора (4), четвертого транзистора (5) и резисторов смещения (1), подключенных между затворами транзисторов (2), (5) и (3), (4) соответственно, а также корректирущий детектор, состоящий из пятого транзистора (7), шестого транзистора (8), седьмого транзистора (9), восьмого транзистора (10) и двух резисторов смещения (6), подключенных между затворами транзисторов (7), (10) и (8), (9) соответственно, причем детектор сигналов и корректирующий детектор выполнены на одном кристалле с высокой степенью идентичности, стоки первого (2) и третьего (4) транзисторов соединены со стоками шестого (8) и восьмого (10) транзисторов, а стоки второго (3) и четвертого (5) транзисторов соединены со стоками пятого (7) и седьмого (9) так, что малый статический ток от детектора сигналов, включающего первый-четвертый (2-5) транзисторы, складывается с большим статическим током от корректирующего детектора, включающего пятый-восьмой (7-10) транзисторы, и наоборот, большой статический ток от детектора сигналов, включающего первый-четвертый (2-5) транзисторы, складывается с малым током от корректирующего детектора, включающего пятый-восьмой (7-10) транзисторы, что приводит к равенству потенциалов на выходах OutN и OutP и к нулевому дифференциальному напряжению на выходе при нулевом сигнале на входе.

| WO 1995013655 A1, 18.05.1995 | |||

| Детектор абсолютной величины входного сигнала | 1985 |

|

SU1337991A1 |

| ПИКОВЫЙ ДЕТЕКТОР С ДИФФЕРЕНЦИАЛЬНЫМ ВХОДОМ | 2018 |

|

RU2700327C1 |

| Амплитудный детектор | 1978 |

|

SU718884A1 |

Авторы

Даты

2023-09-11—Публикация

2022-08-05—Подача