Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов в структуре аналоговых микросхем различного функционального назначения (например, в быстродействующих дифференциальных операционных усилителях (ОУ), работающих с двумя сигналами, имеющими синфазную составляющую).

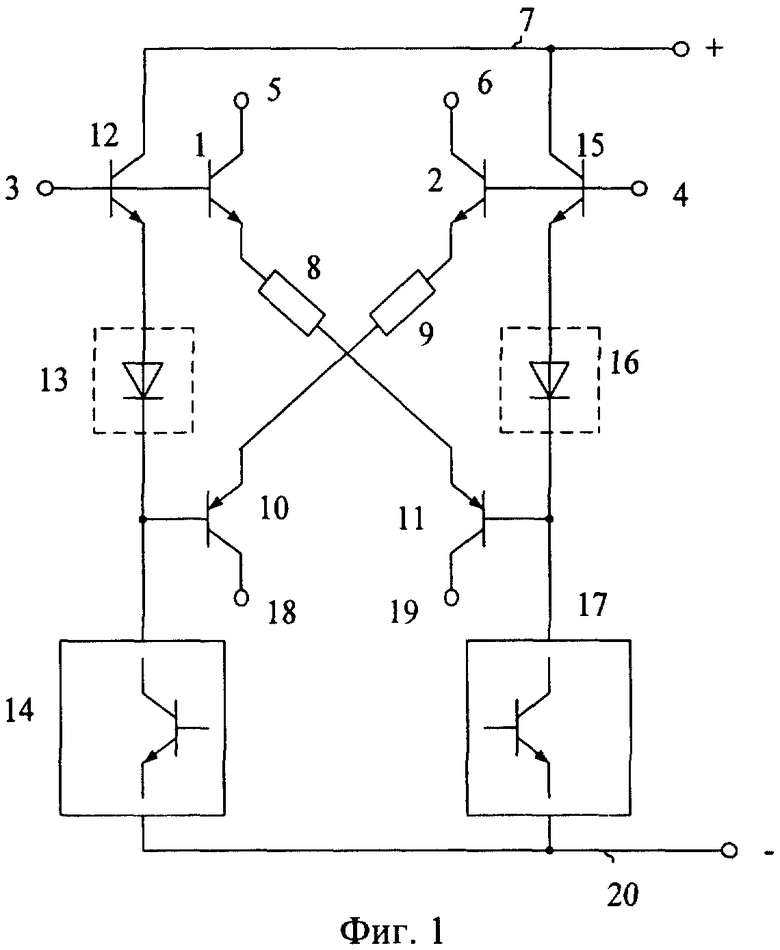

Известны схемы дифференциальных входных каскадов (ДВК) быстродействующих операционных усилителей (ОУ), обеспечивающих большие уровни выходного тока при изменении входного дифференциального сигнала в широких пределах (фиг.1). Такие ВК, имеющие мостовую структуру, стали основой построения практически всех быстродействующих операционных усилителей как зарубежного, так и отечественного производства (НА2700, К154УД1, К154УД4 и т.д.). На модификации схемы фиг.1 выдано более 20 патентов для ведущих микроэлектронных фирм (Texas Instruments, Micron Technology, National Semiconductor, Burr Brows, Intel, Analog Devices, Ericsson, ST Microelectronics [1-22 и др.].

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель, описанный в патенте США №6.696.888, содержащий первый (1) и второй (2) входные транзисторы, базы которых соединены со входами 3 и 4 входного каскада, коллекторы связаны с выходами 5 и 6 входного каскада, согласованными с шиной первого источника питания 7, а эмиттеры через первый 8 и второй 9 согласующие резисторы соединены с соответствующими эмиттерами первого 10 и второго 11 выходных транзисторов, первый вход 3 входного каскада соединен с базой третьего входного транзистора 12, эмиттер которого через первую цепь смещения потенциала 13 связан с базой первого 10 входного транзистора и первым источником опорного тока 14, второй вход 4 входного каскада соединен с базой четвертого 15 входного транзистора, эмиттер которого через вторую цепь смещения потенциала 16 связан с базой второго выходного транзистора 11 и вторым источником опорного тока 17, причем коллекторы первого 10 и второго 11 выходных транзисторов соединены с выходами входного каскада 18 и 19, согласованными с шиной второго источника питания 20.

Существенный недостаток известного дифференциального входного каскада состоит в том, что он имеет недостаточно высокое ослабление синфазных сигналов на высоких частотах (f>1 МГц), что существенно снижает точность быстродействующих аналоговых интерфейсов на его основе. Кроме этого, во входном каскаде-прототипе наблюдается ограничение выходного тока на уровне Iн.max, который существенно зависит от коэффициента усиления по току базы применяемых р-n-р транзисторов. Увеличение Iн.max при сохранении на неизменном уровне энергопотребления ДВК - важная схемотехническая задача.

Основная цель предлагаемого изобретения состоит в повышении коэффициента ослабления входного синфазного сигнала (Кос.сф) в диапазоне высоких частот. Дополнительная цель - увеличение максимального выходного тока Iн.max без ухудшения энергетических показателей в статическом режиме.

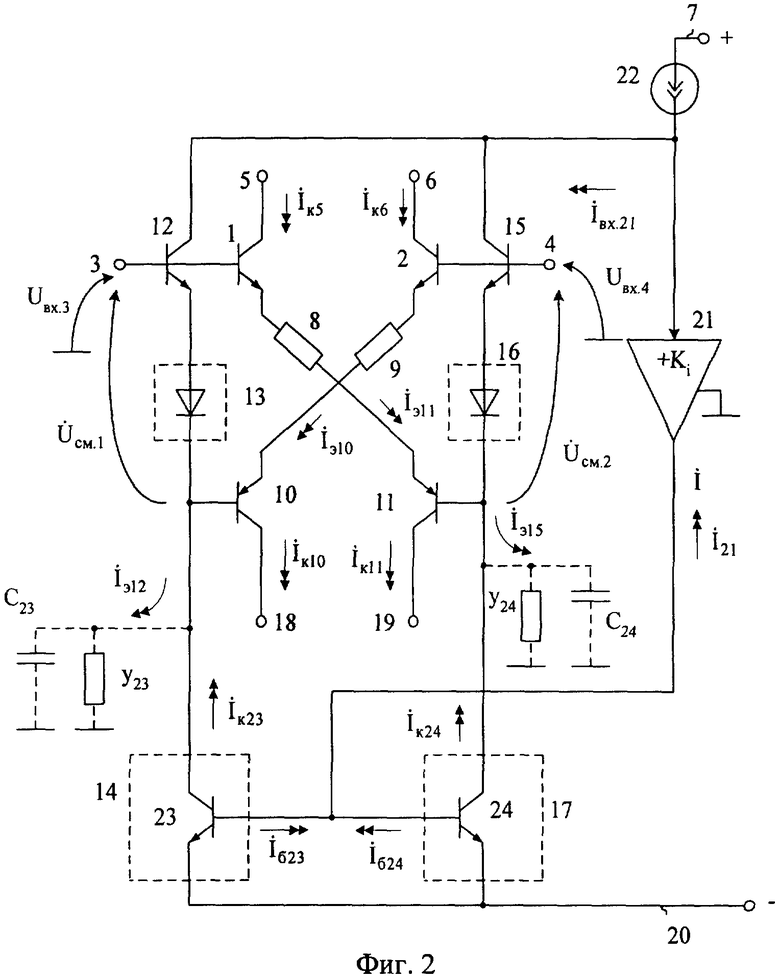

Поставленная цель достигается тем, что в дифференциальном входном каскаде быстродействующего операционного усилителя фиг.1, содержащем первый (1) и второй (2) входные транзисторы, базы которых соединены со входами 3 и 4 входного каскада, коллекторы связаны с выходами 5 и 6 входного каскада, согласованными с шиной первого источника питания 7, а эмиттеры через первый 8 и второй 9 согласующие резисторы соединены с соответствующими эмиттерами первого 10 и второго 11 выходных транзисторов, первый вход 3 входного каскада соединен с базой третьего входного транзистора 12, эмиттер которого через первую цепь смещения потенциала 13 связан с базой первого 10 входного транзистора и первым источником опорного тока 14, второй вход 4 входного каскада соединен с базой четвертого 15 входного транзистора, эмиттер которого через вторую цепь смещения потенциала 16 связан с базой второго выходного транзистора 11 и вторым источником опорного тока 17, причем коллекторы первого 10 и второго 11 выходных транзисторов соединены с выходами входного каскада 18 и 19, согласованными с шиной второго источника питания 20, предусмотрены новые элементы и связи - коллекторы третьего 12 и четвертого 15 входных транзисторов подключены ко входу дополнительного усилителя тока 21 и дополнительному источнику опорного тока 22, причем первый 14 и второй 17 источники опорного тока выполнены на первом 23 и втором 24 вспомогательных транзисторах при их включении по схеме с общим эмиттером, базы этих транзисторов 23 и 24 объединены и подключены к выходу дополнительного усилителя тока 21.

Схема заявляемого устройства, соответствующая п.1 формулы изобретения, приведена на фиг.2.

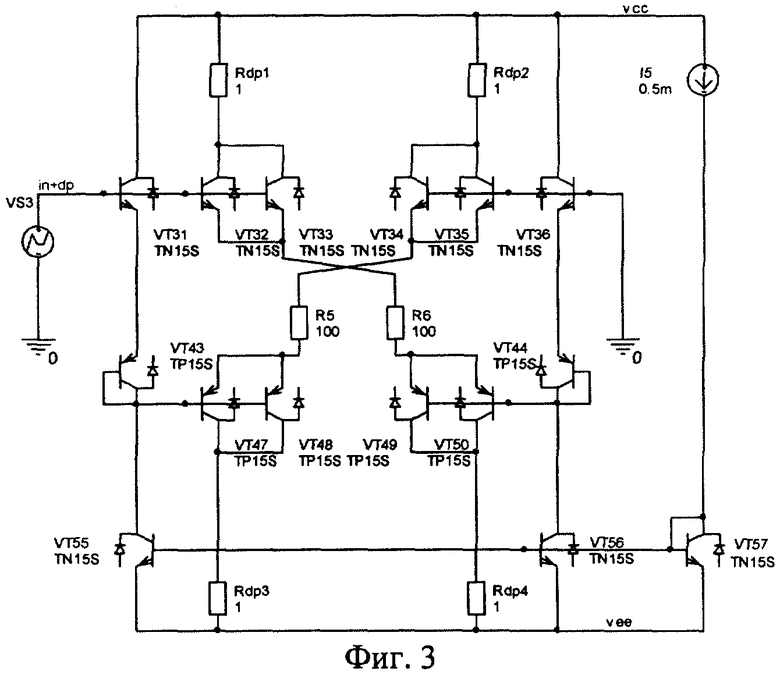

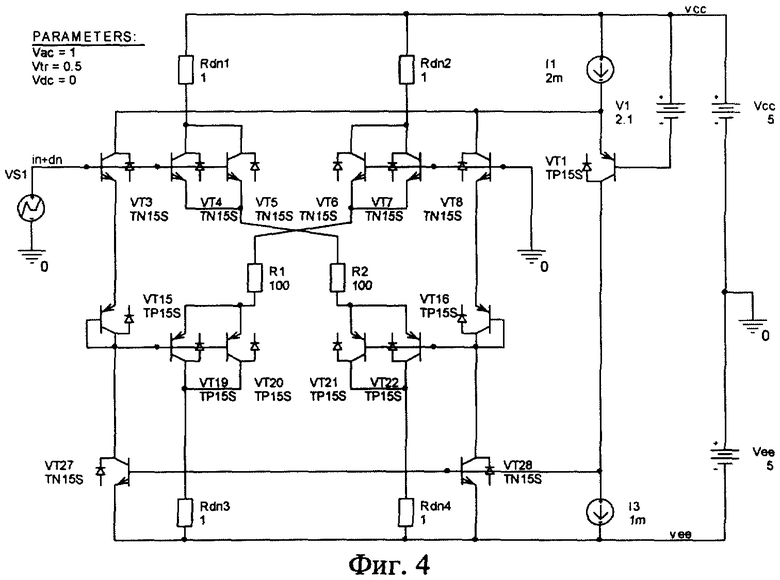

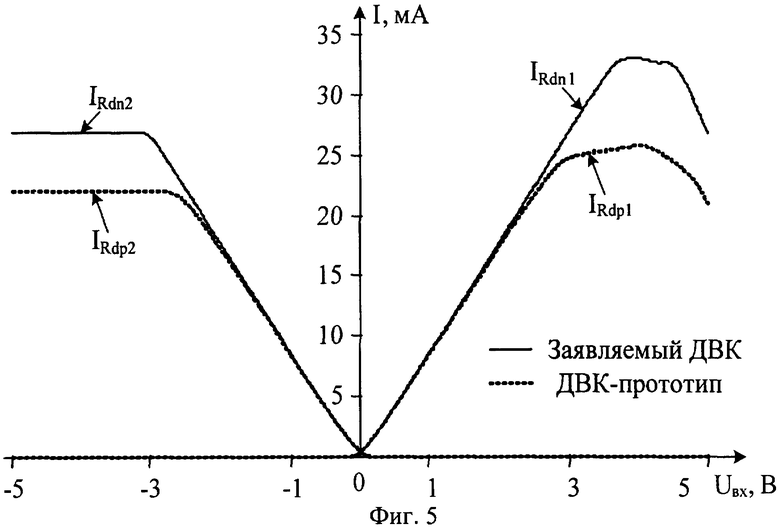

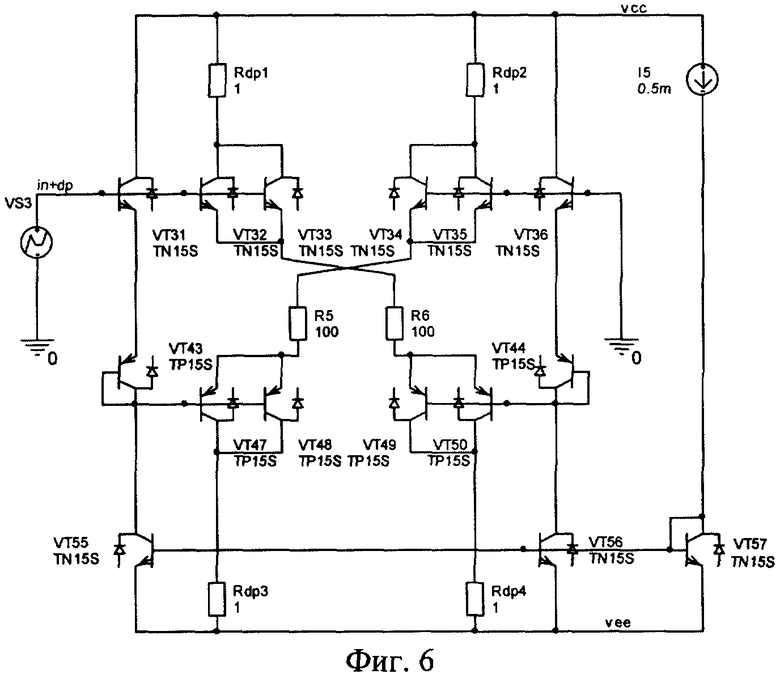

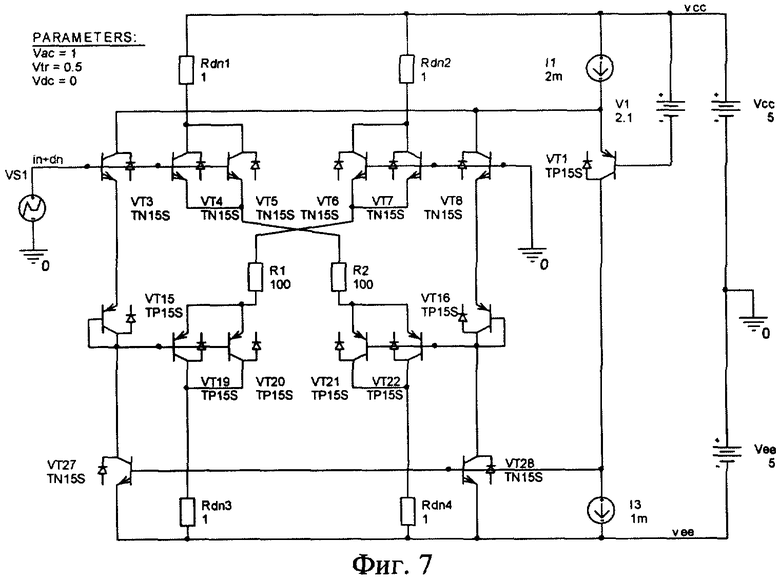

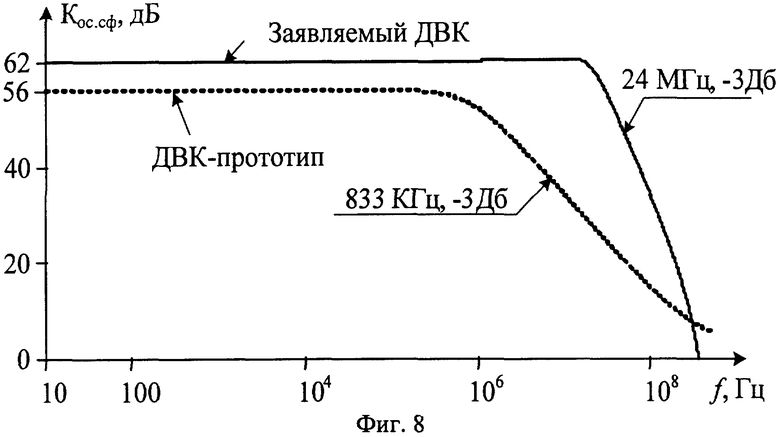

На фиг.3 и 4 представлены соответственно схема ДВК-прототипа (фиг.3) и заявляемого устройства (фиг.4) в среде PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар». На фиг.4 также показан частный вариант выполнения дополнительного усилителя тока 21. На фиг.5 показаны проходные характеристики входных каскадов фиг.3 и 4. На фиг.6 и 7 изображены схемы известного (фиг.6) и заявляемого (фиг.7) ДВК в среде PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар», которые исследовались авторами при определении их коэффициента ослабления входного синфазного сигнала. Соответствующие сравнительные характеристики Кос.сф в частотном диапазоне данных ДВК показаны на фиг.8, из которых, в частности, следует, что заявляемый ДВК имеет в 28 раз лучшие значения частоты fc, на которой Кос.сф уменьшается на -3 дБ от своего низкочастотного значения.

Дифференциальный входной каскад быстродействующего операционного усилителя фиг.2 содержит первый (1) и второй (2) входные транзисторы, базы которых соединены со входами 3 и 4 входного каскада, коллекторы связаны с выходами 5 и 6 входного каскада, согласованными с шиной первого источника питания 7, а эмиттеры через первый 8 и второй 9 согласующие резисторы соединены с соответствующими эмиттерами первого 10 и второго 11 выходных транзисторов, первый вход 3 входного каскада соединен с базой третьего входного транзистора 12, эмиттер которого через первую цепь смещения потенциала 13 связан с базой первого 10 входного транзистора и первым источником опорного тока 14, второй вход 4 входного каскада соединен с базой четвертого 15 входного транзистора, эмиттер которого через вторую цепь смещения потенциала 16 связан с базой второго выходного транзистора 11 и вторым источником опорного тока 17, причем коллекторы первого 10 и второго 11 выходных транзисторов соединены с выходами входного каскада 18 и 19, согласованными с шиной второго источника питания 20. Коллекторы третьего 12 и четвертого 15 входных транзисторов подключены ко входу дополнительного усилителя тока 21 и дополнительному источнику опорного тока 22, причем первый 14 и второй 17 источники опорного тока выполнены на первом 23 и втором 24 вспомогательных транзисторах при их включении по схеме с общим эмиттером, базы этих транзисторов 23 и 24 объединены и подключены к выходу дополнительного усилителя тока 21. В частном случае дополнительный усилитель тока 21 может быть выполнен на дополнительном транзисторе при его включении по схеме с общей базой (фиг.4).

Рассмотрим работу заявляемого ДВК на примере анализа схемы фиг.2.

Основная причина существенного ухудшения Кос.сф ДВК фиг.1 - 2 на высоких частотах - наличие у транзисторов источников опорного тока 14 и 17 емкостей на подложку C23, С24, которые включены параллельно их выходным проводимостям у23, у24, связанным с эффектом Эрли. Причем для базовых микронных технологий С23≈С24=Сп=2÷3 пФ.

С повышением частоты сигнала увеличивается емкостная составляющая тока эмиттеров транзисторов 12 и 15, обусловленная наличием на входах ДВК 3 и 4 синфазного сигнала Uc=Uвх.3=Uвх.4:

где ω - частота синфазного сигнала на входах ДВК 3 и 4.

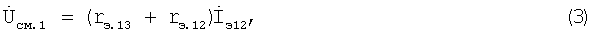

Приращения токов Iэ12, Iэ15 создают на элементах 12, 13 и 15, 16 некоторые переменные напряжения

где rэ.13, rэ.12, rэ.16, rэ.15 - дифференциальные сопротивления эмиттерных переходов транзисторов 12 и 15 и цепей смещения 13, 16.

Эти переменные напряжения оказываются приложенными между базами транзисторов 2 и 10, 1 и 11, что увеличивает токи эмиттеров транзисторов 10 и 11 Iэ10 и Iэ11.

где  ,

,  - эквивалентные сопротивления эмиттерных цепей транзисторов 2 и 10, 1 и 11.

- эквивалентные сопротивления эмиттерных цепей транзисторов 2 и 10, 1 и 11.

Данные токи  ,

,  передаются в коллекторные цепи на выходы 5 и 6, 18 и 19. Они являются основной причиной ухудшения Кос.сф ДВК на высоких частотах.

передаются в коллекторные цепи на выходы 5 и 6, 18 и 19. Они являются основной причиной ухудшения Кос.сф ДВК на высоких частотах.

В заявляемом устройстве токи  и

и  передаются с единичным коэффициентом в коллекторную цепь транзисторов 12 и 15, а затем на вход и, далее, на выход дополнительного усилителя тока 21:

передаются с единичным коэффициентом в коллекторную цепь транзисторов 12 и 15, а затем на вход и, далее, на выход дополнительного усилителя тока 21:

где Кi>>1 - коэффициент усиления по току дополнительного усилителя 21.

Причем выходной ток  дополнительного усилителя 21 равен сумме токов баз транзисторов 23 и 24:

дополнительного усилителя 21 равен сумме токов баз транзисторов 23 и 24:

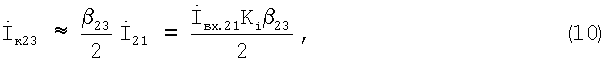

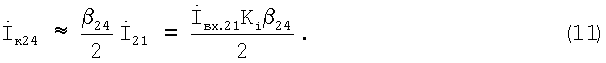

В свою очередь приращения токов  и

и  связаны с коллекторными токами транзисторов 23, 24 через коэффициент усиления по току базы β23=β24

связаны с коллекторными токами транзисторов 23, 24 через коэффициент усиления по току базы β23=β24

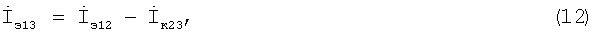

Таким образом, в заявляемой схеме создаются две составляющие коллекторных токов  , которые (в определенном частотном диапазоне) почти полностью компенсируют емкостные токи через С23 и C24. Как следствие, эффективные значения напряжений

, которые (в определенном частотном диапазоне) почти полностью компенсируют емкостные токи через С23 и C24. Как следствие, эффективные значения напряжений  (3),

(3),  (4) уменьшаются, что приводит к уменьшению токов

(4) уменьшаются, что приводит к уменьшению токов  и

и  и, как следствие, к повышению Кос.сф. Действительно, из (1)÷(10) следует, что в заявляемом ДВК эффективные значения токов через элементы 13, 12 и 16, 15 уменьшаются и, как следствие, уменьшаются и токи

и, как следствие, к повышению Кос.сф. Действительно, из (1)÷(10) следует, что в заявляемом ДВК эффективные значения токов через элементы 13, 12 и 16, 15 уменьшаются и, как следствие, уменьшаются и токи  и

и  , влияющие на Кос.сф

, влияющие на Кос.сф

То есть в схеме фиг.2 эффективные значения емкостей

Формулы (18), (19) справедливы до диапазона частот, в котором β23=β24 и Кi>1 существенно не ухудшаются от своих низкочастотных значений.

Практически для каждого из выходов 5, 6, 18, 19 в отдельности ослабление синфазных сигналов ДВК не ухудшается от своих низкочастотных значений до частот 20-25 МГц.

Полученные выше выводы подтверждаются результатами (фиг.8) моделирования предлагаемых схем в среде PSpice с использованием моделей интегральных транзисторов ФГУП НПП «Пульсар» (г.Москва) - заявляемый ДВК имеет более широкий частотный диапазон по ослаблению синфазных сигналов, а также характеризуется более высокими уровнями максимального выходного тока (фиг.5). Последний эффект объясняется влиянием на проходные характеристики ДВК нелинейной отрицательной обратной связи.

Следует заметить, что использование дифференциальных выходов ДВК 5 и 6 или 18 и 19, а также традиционное суммирование токовых выходов 6 и 19, 5 и 18 с помощью типовых токовых зеркал [23], позволяет значительно увеличить абсолютные значения Кос.сф.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №5.150.074.

2. Патент США №6.437.645.

3. Патент США №3.668.538.

4. Патент США №5.343.164.

5. Патент США №6.600.343.

6. Патент США №6.486.736.

7. Патентная заявка US 2001/0020869 A1.

8. Патент США №5.374.897.

9. Патент США №4.851.768.

10. Патент США №3.178.647.

11. Патент США №5.656.969.

12. Патент США №6.411.132.

13. Патент США №4.757.273.

14. Патент США №6.249.153.

15. Патент США №6.259.280.

16. Патент США №6.696.888.

17. Патент США №6.281.752.

18. Патент США №5.122.759.

19. Патент США №5.515.005.

20. Патент Англии №2.179.814.

21. Патент США №6.351.186.

22. А.св. СССР №1045349.

23. Матавкин В.В. Быстродействующие операционные усилители [Текст] / В.В.Матавкин. - М.: Радио и связь, 1989. - Рис.4.16, рис.5.18, рис.6.9.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2319295C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2005 |

|

RU2292632C1 |

| ДВУХТАКТНЫЙ КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2321161C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2320078C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С РАСШИРЕННЫМ ДИАПАЗОНОМ ИЗМЕНЕНИЯ ВХОДНОГО СИНФАЗНОГО СИГНАЛА | 2012 |

|

RU2474953C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2319291C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ ВХОДНОГО СИНФАЗНОГО СИГНАЛА | 2011 |

|

RU2458455C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2005 |

|

RU2292633C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2011 |

|

RU2444117C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2321159C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов в структуре аналоговых микросхем различного функционального назначения (например, в быстродействующих дифференциальных операционных усилителях (ОУ), работающих с двумя сигналами, имеющими синфазную составляющую). Дифференциальный входной каскад (ДВК) содержит входные транзисторы (Т) (1) и (2), базы которых соединены со входами (3) и (4) ДВК, коллекторы связаны с выходами (5) и (6) ДВК, согласованными с шиной первого источника питания (ИП) (7), а эмиттеры через первый (8) и второй (9) согласующие резисторы соединены с соответствующими эмиттерами выходных Т (10) и (11). Вход (3) ДВК соединен с базой входного Т (12), эмиттер которого через первую цепь смещения потенциала (13) связан с базой входного Т (10) и первым источником опорного тока (ИОТ) (14). Вход (4) ДВК соединен с базой входного Т (15), эмиттер которого через вторую цепь смещения потенциала (16) связан с базой выходного Т (11) и вторым ИОТ (17), причем коллекторы выходных Т (10) и (11) соединены с выходами ДВК (18) и (19), согласованными с шиной второго ИП (20). Для повышения коэффициента ослабления входного синфазного сигнала коллекторы входных Т (12) и (15) подключены ко входу усилителя тока (УТ) (21) и ИОТ (22), причем ИОТ (14) и (17) выполнены на Т (23) и (24) при их включении по схеме с общим эмиттером, а базы этих Т (23) и (24) объединены и подключены к выходу УТ (21). 1 з.п. ф-лы, 8 ил.

| US 6696888 В2, 24.02.2004 | |||

| Дифференциальный усилитель | 1988 |

|

SU1608784A2 |

| Дифференциальный усилитель (его варианты) | 1981 |

|

SU1045349A1 |

| СПОСОБ ПРОИЗВОДСТВА ВЕТЧИНЫ, УПАКОВАННОЙ ПОД ВАКУУМОМ В ТЕРМОУСАДОЧНУЮ ПЛЕНКУ | 1999 |

|

RU2179814C2 |

| СПОСОБ ОРГАНИЗАЦИИ ТОПОЧНОГО ПРОЦЕССА—Б i^TCu:^.;....:• ^^^; -JiJHTKa -^|'сМ:ИЧ^г--;Л!::.5A;:aiJi:A | 0 |

|

SU173370A1 |

Авторы

Даты

2008-03-10—Публикация

2006-07-26—Подача