Предлагаемое изобретение относится к области микроэлектроники и может быть использовано в качестве устройства преобразования аналоговых сигналов датчиков физических величин, в т.ч. работающих при повышенных температурах.

В аналоговой микроэлекторонике находят широкое применение схемы операционных и трансимпедансных усилителей, у которых промежуточный каскад выполнен в виде так назывемого двухтактного «перенутого» каскода [1-4]. Данное схемотехническое решение и его модификации запатентованы ведущими микроэлектронными фирмами США, Японии, Китая, Южной Кореи и др. [5-15].

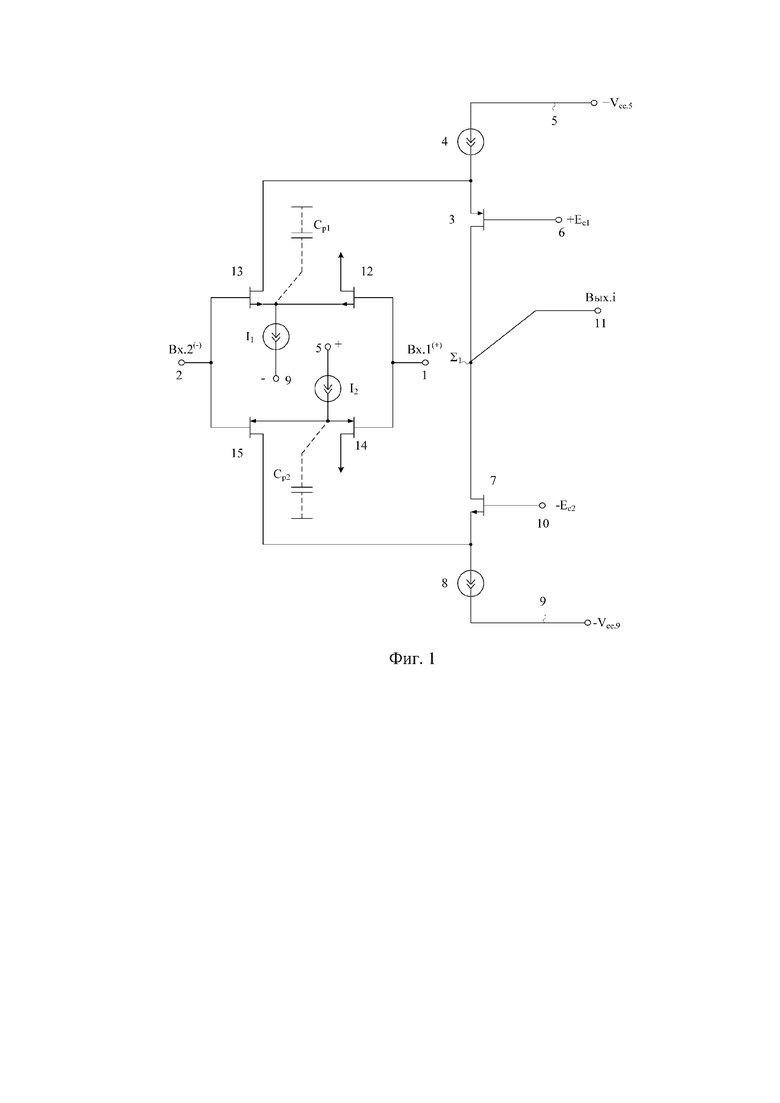

Ближайшим прототипом заявляемого устройства является операционный усилитель по патенту US 6.696.894, fig. 1, fig. 2, 2004 г. фирмы Analog Devices (США). Он содержит первый 1 неинвертирующий и второй 2 инвертирующий входы устройства, первый 3 выходной полевой транзистор промежуточного каскада, исток которого через первый 4 источник опорного тока соединен с первой 5 шиной источника питания, а затвор связан с первым 6 источником напряжения смещения, второй 7 выходной полевой транзистор промежуточного каскада, исток которого через второй 8 источник опорного тока соединен со второй 9 шиной источника питания, а затвор связан со вторым 10 источником напряжения смещения, причем стоки первого 3 и второго 7 выходных полевых транзисторов промежуточного каскада соединены друг с другом и подключены к токовому выходу устройства 11, первый 12, второй 13, третий 14 и четвертый 15 входные полевые транзисторы входного дифференциального каскада.

Существенный недостаток известного ОУ на чертеже фиг. 1 состоит в том, что передача входных переменных напряжений к токовому выходу устройства 11 для дифференциальных и синфазных сигналов на первом 1 и втором 2 входах устройства зависят от паразитных емкостей Ср1, Ср2, которые определяются выходными емкостями источников опорного тока I1 и I2. Следует также отметить, что разница токов ΔI1.2=I1-I2 в ОУ фиг. 1 оказывает отрицательное влияние на систематическую составляющую напряжения смещения нуля (Uсм) ОУ-прототипа.

Основная задача предлагаемого изобретения состоит в уменьшении влияния паразитных емкостей источников опорного тока I1, I2, устанавливающих статических режим входного дифференциального каскада, и их неидентичности на статические и динамические параметры ОУ с двухтактным «перегнутым» каскодом.

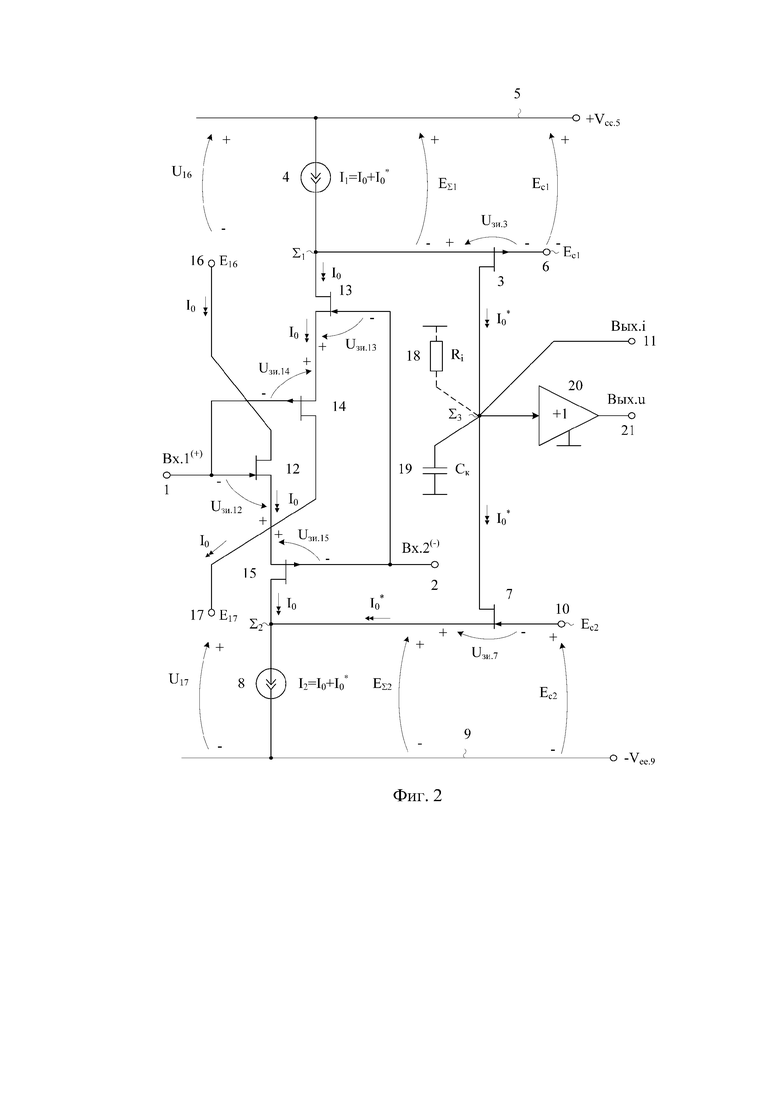

Поставленная задача достигается тем, что в операционном усилителе с промежуточным двухтактным «перегнутым» каскодом на комплементарных полевых транзисторах, содержащем первый 1 неинвертирующий и второй 2 инвертирующий входы устройства, первый 3 выходной полевой транзистор промежуточного каскада, исток которого через первый 4 источник опорного тока соединен с первой 5 шиной источника питания, а затвор связан с первым 6 источником напряжения смещения, второй 7 выходной полевой транзистор промежуточного каскада, исток которого через второй 8 источник опорного тока соединен со второй 9 шиной источника питания, а затвор связан со вторым 10 источником напряжения смещения, причем стоки первого 3 и второго 7 выходных полевых транзисторов промежуточного каскада соединены друг с другом и подключены к токовому выходу устройства 11, первый 12, второй 13, третий 14 и четвертый 15 входные полевые транзисторы входного дифференциального каскада, предусмотрены новые элементы и связи - затвор первого 12 входного полевого транзистора соединен с первым 1 неинвертирующим входом устройства, его исток соединен с истоком четвертого 15 входного полевого транзистора, затвор третьего 14 входного полевого транзистора подключен к первому 1 неинвертирующему входу устройства, а его исток соединен с истоком второго 13 входного полевого транзистора, причем сток второго 13 входного полевого транзистора соединен с истоком первого 3 выходного полевого транзистора промежуточного каскада, сток четвертого 15 входного полевого транзистора соединен с истоком второго 7 выходного полевого транзистора промежуточного каскада, а затворы второго 13 и четвертого 15 входных полевых транзисторов соединены со вторым 2 инвертирующим входом устройства, при этом сток первого 12 входного полевого транзистора подключен к третьему 16 источнику напряжения смещения, сток третьего 14 входного полевого транзистора подключен к четвертому 17 источнику напряжения смещения.

Кроме этого, в соответствии с п. 2 формулы изобретения операционный усилитель на чертеже фиг. 2 с промежуточным двухтактным «перегнутым» каскодом на комплементарных полевых транзисторах, отличается тем, что токовый выход 11 устройства соединен со входом дополнительного буферного усилителя 20, выход которого 21 является потенциальным выходом устройства.

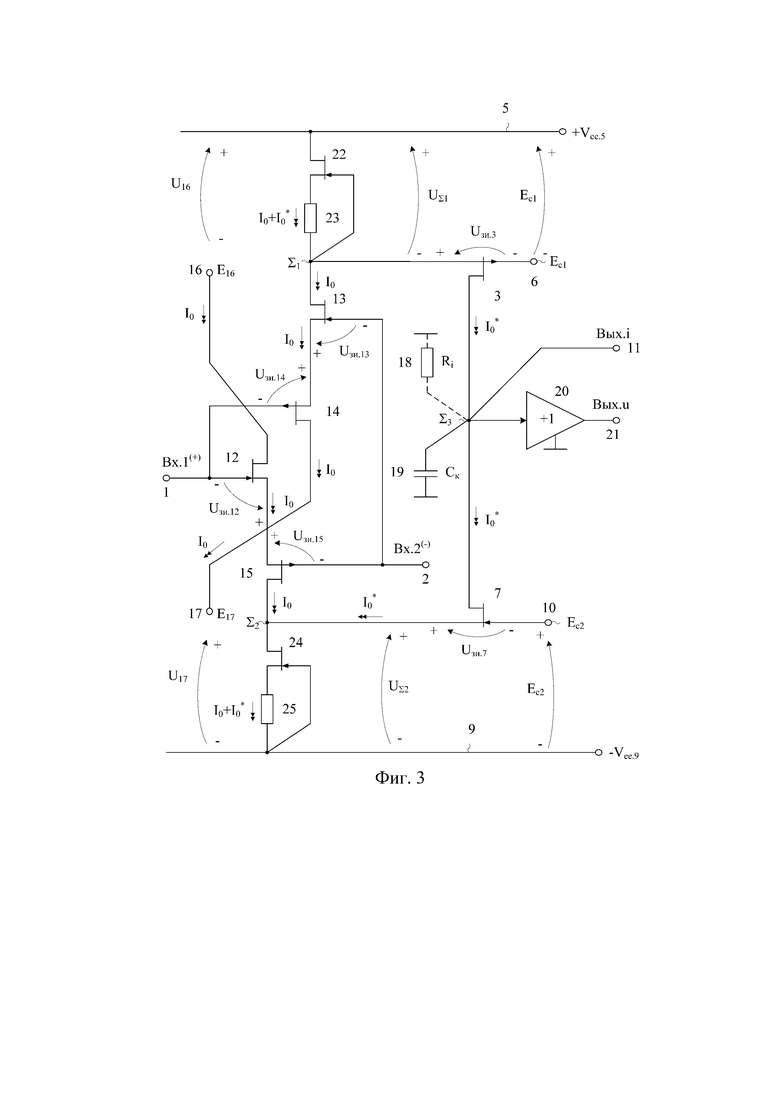

В соответствии с п. 3 формулы изобретения, операционный усилитель с промежуточным двухтактным «перегнутым» каскодом на комплементарных полевых транзисторах фиг. 3, отличается тем, что первый 4 источник опорного тока выполнен на первом 22 дополнительном полевом транзисторе, исток которого связан с затвором через первый 23 вспомогательный резистор, а сток согласован с первой 5 шиной источника питания, а второй 8 источник опорного тока выполнен на втором 24 дополнительном полевом транзисторе, затвор которого связан с истоком через второй 25 вспомогательный резистор и согласован со второй 9 шиной источника питания.

В соответствии с п. 4 формулы изобретения, операционный усилитель с промежуточным двухтактным «перегнутым» каскодом на комплементарных полевых транзисторах по п. 1 и п. 3, отличается тем, что в качестве полевых транзисторов используются полевые транзисторы с управляющим p-n переходом.

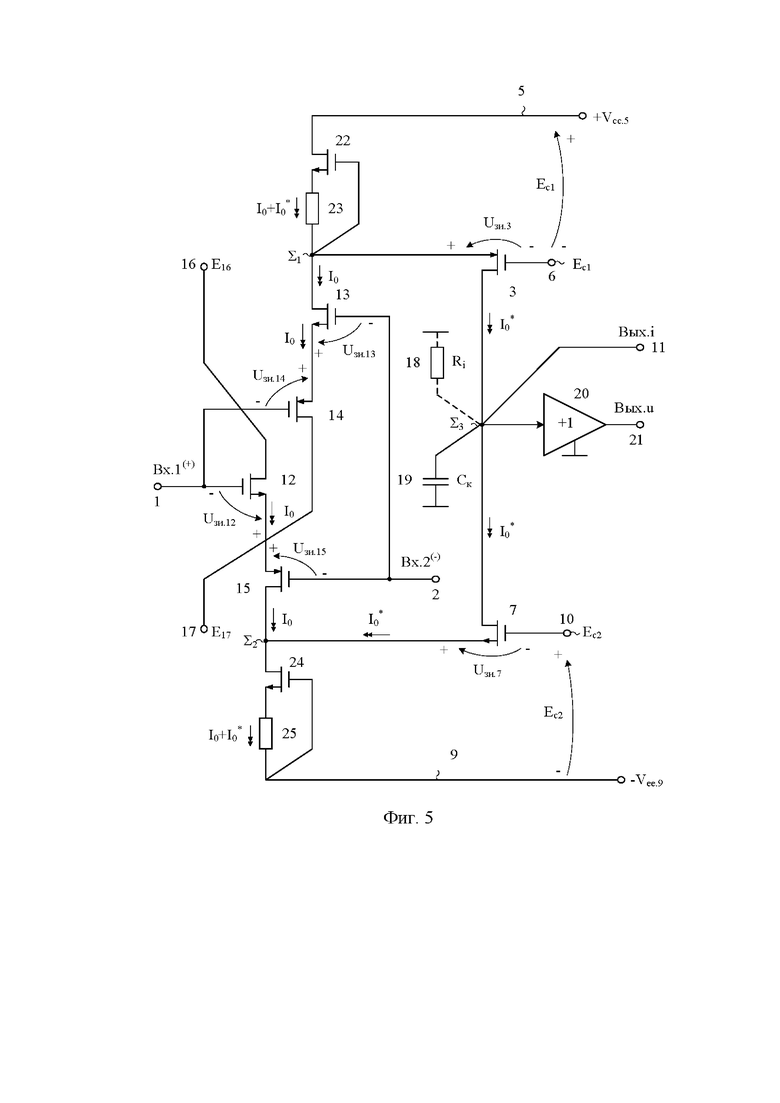

В соответствии с п. 5 формулы изобретения, операционный усилитель с промежуточным двухтактным «перегнутым» каскодом на комплементарных полевых транзисторах фиг. 5, отличается тем, что в качестве полевых транзисторов используются КМОП транзисторы со встроенным каналом.

На фиг. 1 приведена схема операционного усилителя - прототипа по патенту фирмы Analog Devices (США).

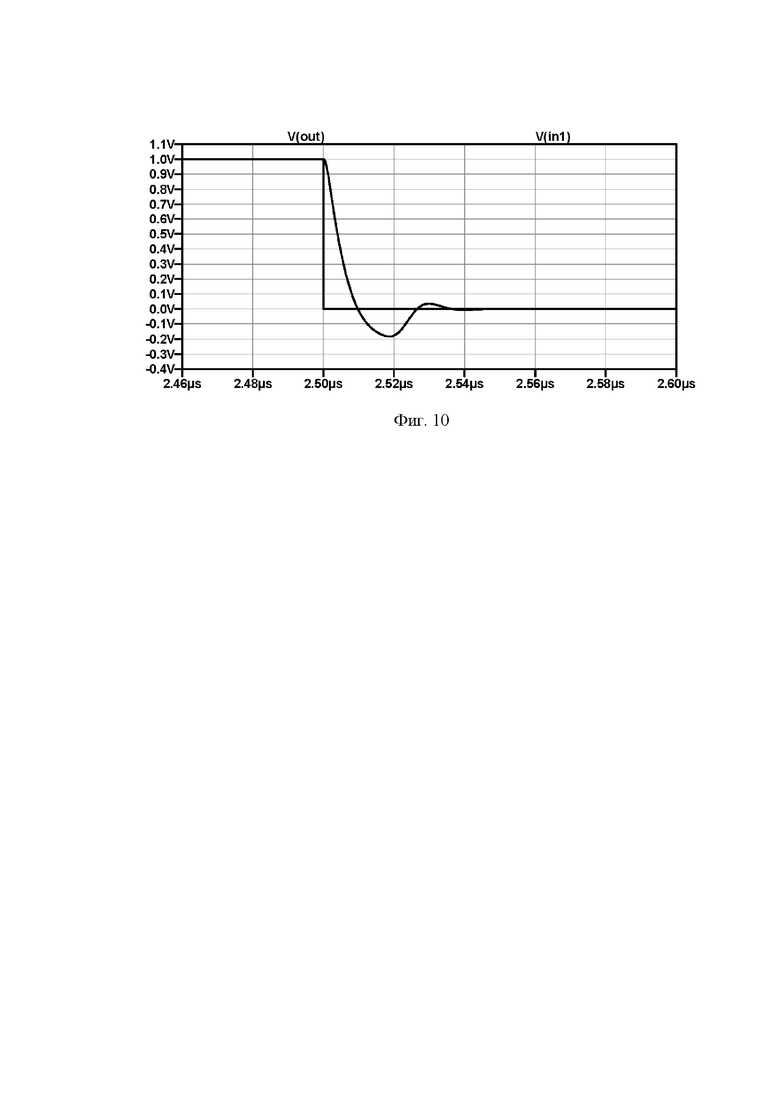

На фиг. 2 показана схема заявляемого операционного усилителя в соответствии с п. 1 и п.2 формулы изобретения.

На фиг. 3 представлена схема заявляемого операционного усилителя в соответствии с п. 3 формулы изобретения.

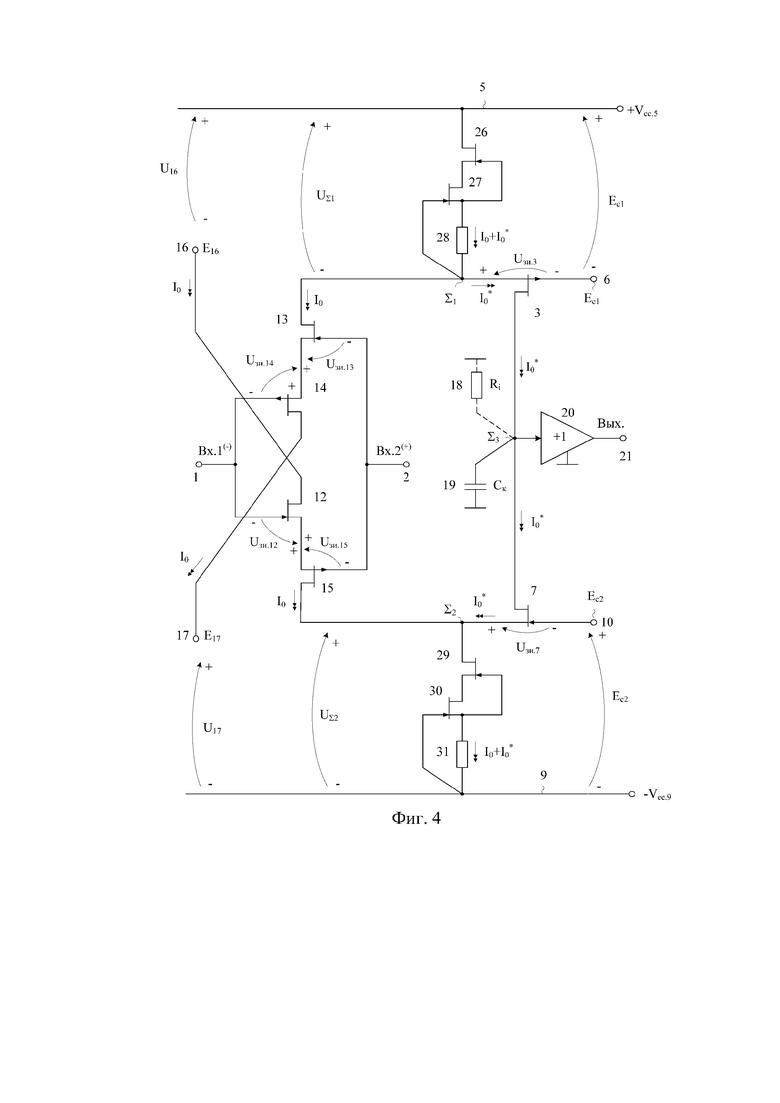

На фиг. 4 показан пример построения заявляемого устройства фиг. 2 с источниками опорного тока 4 и 8 при их реализации соответственно на полевых транзисторах 26, 27 и резисторе 28, а также полевых транзисторах 29, 30 и резисторе 31. Такие схемотехнические решения уменьшают систематическую составляющую напряжения смещения нуля ОУ.

На чертеже фиг. 5 представлена схема ОУ в соответствии с п.5 формулы изобретения.

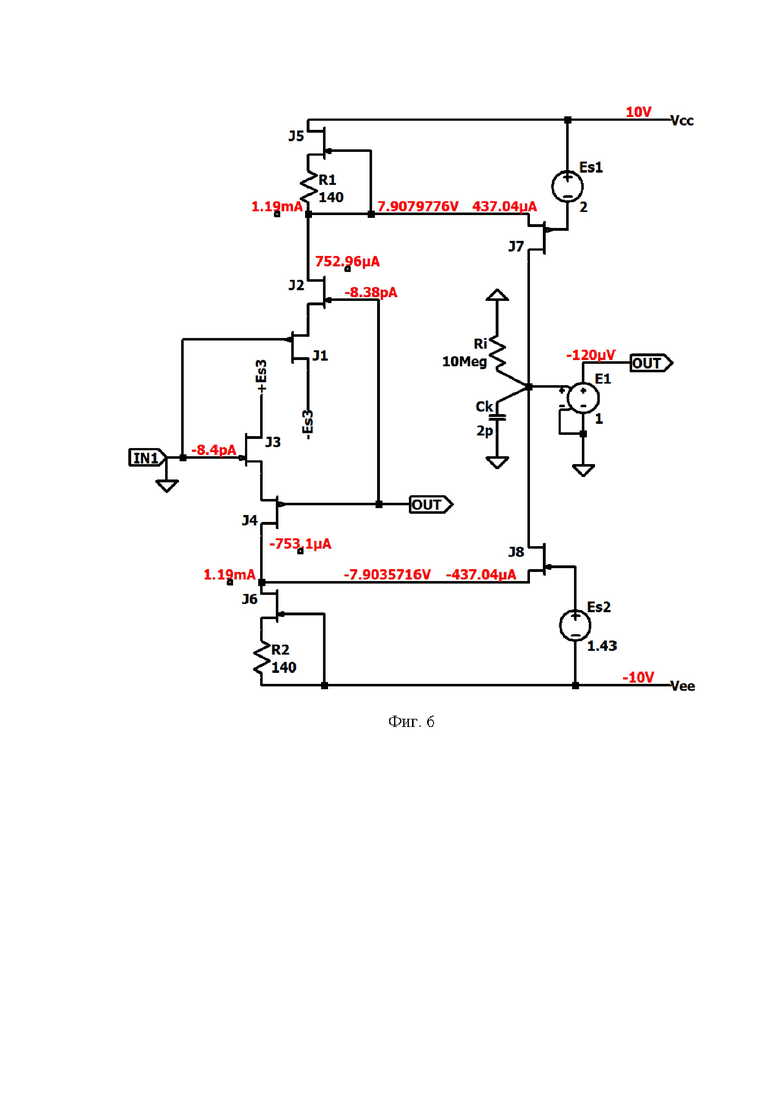

На чертеже фиг. 6 приведен статический режим ОУ фиг. 3 в среде LTspice при t=27°C, Vcc=10 В, Vee=-10 В, R1÷R2=140 Ом, Es1=2 В, Es2=1,43 В, +Es3=7,88 В, -Es3=-7,88 В, Ck=2 пФ, Ri=10 МОм.

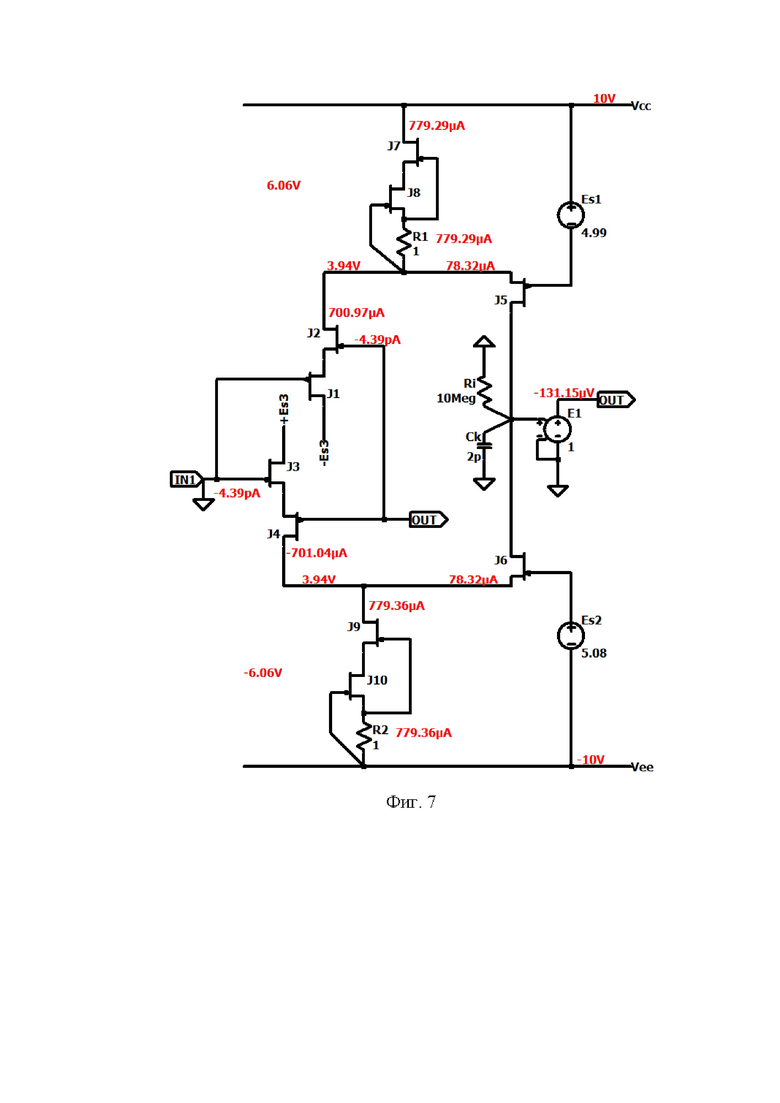

На чертеже фиг 7. показан статический режим ОУ фиг. 4 в среде LTspice при t=27°C, Vcc=10 В, Vee=-10 В, R1÷R2=1 Ом, Es1=4,99 В, Es2=5,08 В, +Es3=3,94 В, -Es3=-3,94 В, Ck=2 пФ, Ri=10 МОм.

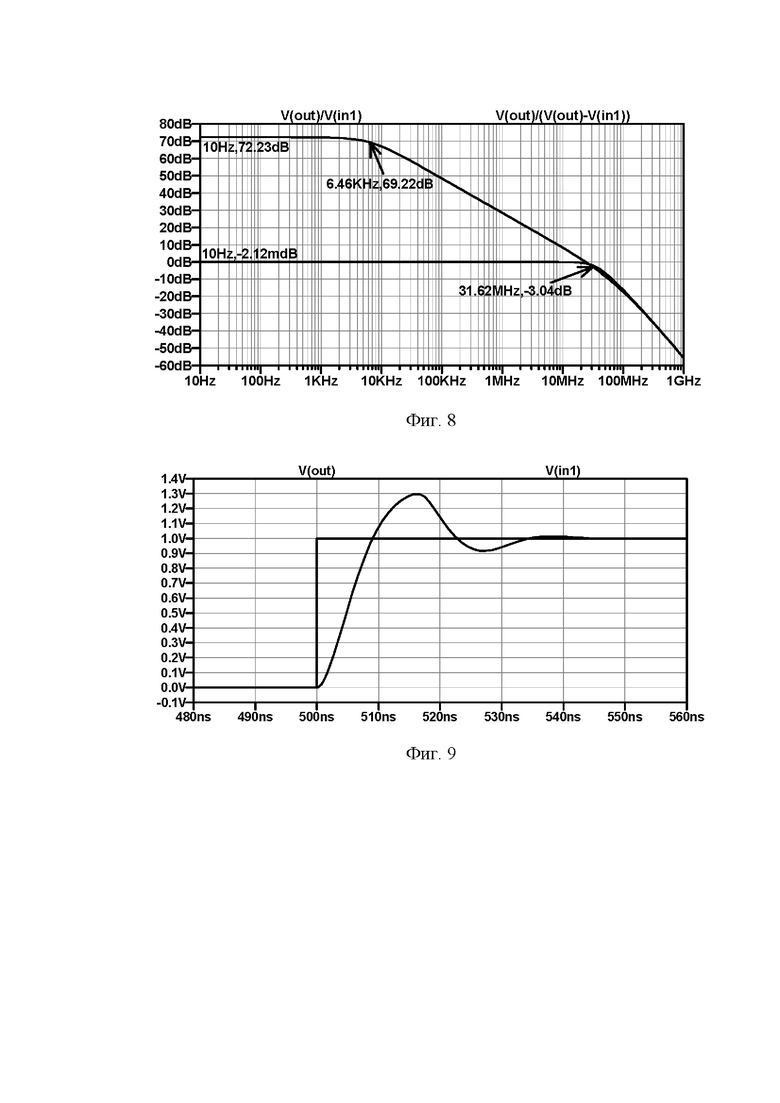

На чертеже фиг. 8 показана логарифмическая амплитудно-частотная характеристика (ЛАЧХ) ОУ фиг. 6 в среде LTspice при t=27°C, Vcc=10 В, Vee=-10 В, R1÷R2=1 Ом, Es1=4,99 В, Es2=5,08 В, +Es3=3,94 В, -Es3=-3,94 В, Ck=2 пФ, Ri=10 Мом.

На чертеже фиг. 9 представлен передний фронт переходного процесса ОУ фиг. 6 в среде LTspice при t=27°C, Vcc=10 В, Vee=-10 В, R1÷R2=1 Ом, Es1=4,99 В, Es2=5,08 В, +Es3=3,94 В, -Es3=-3,94 В, Ck=2 пФ, Ri=10 МОм.

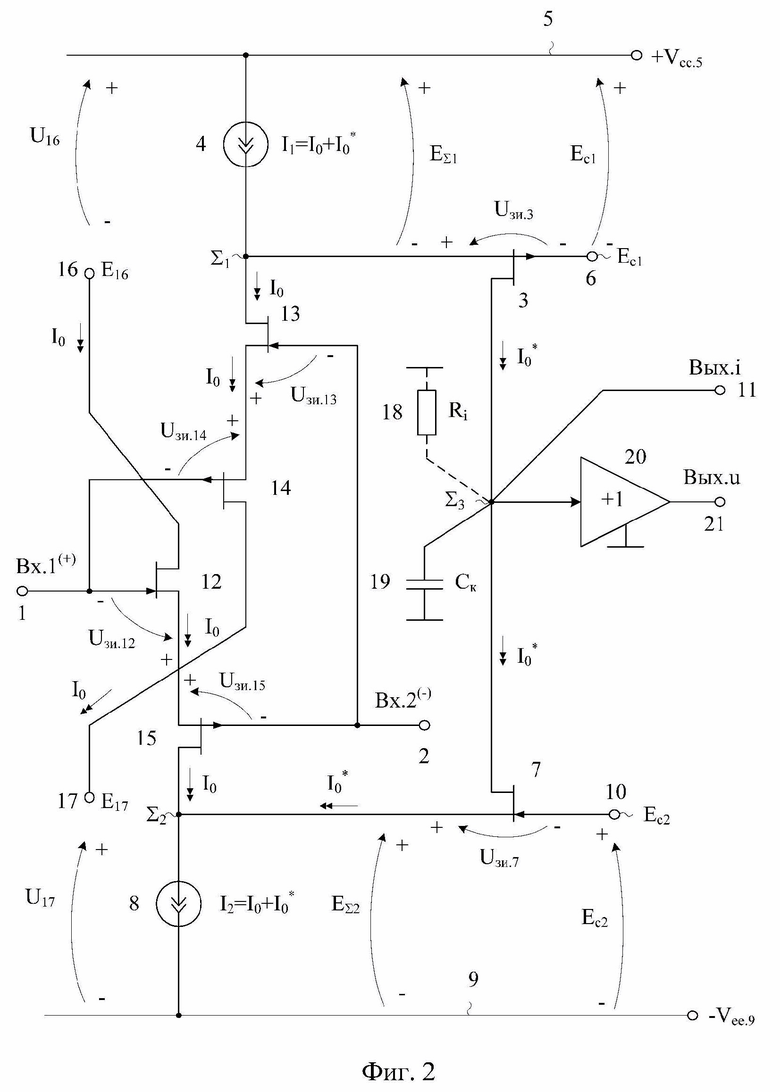

На чертеже фиг. 10 показан задний фронт переходного процесса ОУ фиг. 6 в среде LTspice при t=27°C, Vcc=10 В, Vee=-10 В, R1÷R2=1 Ом, Es1=4,99 В, Es2=5,08 В, +Es3=3,94 В, -Es3=-3,94 В, Ck=2 пФ, Ri=10 МОм.

Операционный усилитель с промежуточным двухтактным «перегнутым» каскодом на комплементарных полевых транзисторах фиг. 2 содержит первый 1 неинвертирующий и второй 2 инвертирующий входы устройства, первый 3 выходной полевой транзистор промежуточного каскада, исток которого через первый 4 источник опорного тока соединен с первой 5 шиной источника питания, а затвор связан с первым 6 источником напряжения смещения, второй 7 выходной полевой транзистор промежуточного каскада, исток которого через второй 8 источник опорного тока соединен со второй 9 шиной источника питания, а затвор связан со вторым 10 источником напряжения смещения, причем стоки первого 3 и второго 7 выходных полевых транзисторов промежуточного каскада соединены друг с другом и подключены к токовому выходу устройства 11, первый 12, второй 13, третий 14 и четвертый 15 входные полевые транзисторы входного дифференциального каскада. Затвор первого 12 входного полевого транзистора соединен с первым 1 неинвертирующим входом устройства, его исток соединен с истоком четвертого 15 входного полевого транзистора, затвор третьего 14 входного полевого транзистора подключен к первому 1 неинвертирующему входу устройства, а его исток соединен с истоком второго 13 входного полевого транзистора, причем сток второго 13 входного полевого транзистора соединен с истоком первого 3 выходного полевого транзистора промежуточного каскада, сток четвертого 15 входного полевого транзистора соединен с истоком второго 7 выходного полевого транзистора промежуточного каскада, а затворы второго 13 и четвертого 15 входных полевых транзисторов соединены со вторым 2 инвертирующим входом устройства, при этом сток первого 12 входного полевого транзистора подключен к третьему 16 источнику напряжения смещения, а сток третьего 14 входного полевого транзистора подключен к четвертому 17 источнику напряжения смещения. Интегрирующий корректирующий конденсатор Ск (19) обеспечивает устойчивость ОУ, а резистор 18 характеризует эквивалентное выходное сопротивление в высокоимпедансном узле Σ1.

На чертеже фиг. 2, в соответствии с п. 2 формулы изобретения, токовый выход 11 устройства соединен со входом дополнительного буферного усилителя 20, выход которого 21 является потенциальным выходом устройства.

В частном случае в качестве источников опорного тока 4 и 8 могут использоваться резисторы или специальные схемы, выполненные на JFet, как это предусмотрено в п. 3 формулы изобретения и показано на чертежах фиг. 3 и фиг. 4.

На чертеже фиг. 2, в соответствии с п.3 формулы изобретения, первый 4 источник опорного тока выполнен на первом 22 дополнительном полевом транзисторе, исток которого связан с затвором через первый 23 вспомогательный резистор, а сток согласован с первой 5 шиной источника питания, а второй 8 источник опорного тока выполнен на втором 24 дополнительном полевом транзисторе, затвор которого связан с истоком через второй 25 вспомогательный резистор и согласован со второй 9 шиной источника питания.

На чертежах фиг. 1-4, в соответствии с п. 4 формулы изобретения, в качестве полевых транзисторов схем используются полевые транзисторы с управляющим p-n переходом.

На чертеже фиг. 5, в соответствии с п. 5 формулы изобретения, в качестве полевых транзисторов заявляемых схем ОУ используются КМОП транзисторы со встроенным каналом.

Определим вначале систематическую составляющую напряжения смещения нуля (Uсм) ОУ фиг. 2.

Численные значения Uсм в ОУ зависят от токовой ошибки в высокоимпедансном узле Σ3, которая определяется неидентичностью первого 4 и второго 8 источников опорного тока. Если данные источники опорного тока выполняются в соответствии с фиг. 3 или фиг. 4, то первая систематическая составляющая токовой ошибки будет близка к нулю:

Uсм1=ΔIΣ/gDK, (1)

где ΔIΣ - токовая ошибка в высокоимпедансном узле Σ3,

gDK - крутизна преобразования входного дифференциального напряжения входного каскада в выходной ток высокоимпедансного узла Σ3.

Вторая составляющая напряжения смещения нуля (Uсм2) зависит от идентичности статических режимов первого 12 и второго 13 входных полевых транзисторов, а также третьего 14 и четвертого 15 входных полевых транзисторов по напряжению затвор-сток. Если эти напряжения неодинаковы, то из-за известного эффекта Эрли, который обусловлен внутренней обратной связью в транзисторах, токи стоков второго 13 и четвертого 15 входных полевых транзисторов будут неодинаковы. В этой связи в предлагаемой схеме фиг. 2 предусмотрено включение третьего 16 и четвертого 17 источников напряжения смещения, которые выбираются таким образом, чтобы выполнялись равенства

ЕΣ1=U16, (2)

ЕΣ2=U17, (3)

где U16 - напряжение между первой 5 шиной источника питания и источником Е16,

U17 - напряжение между второй 9 шиной источника питания и источником Е17.

Таким образом, в заявляемой схеме созданы условия, обеспечивающие минимизацию систематической составляющей напряжения смещения нуля.

Рассмотрим теперь работу схемы фиг. 2 при небольшом изменении входного дифференциального напряжения между входами 1 и 2.

Увеличение напряжения на входе 1 относительно входа 2 приводит к уменьшению токов стокоы транзисторов 13 и 14 и увеличения токов стоков транзисторов 12 и 15. Данные приращения передаются в истоки транзисторов 3 и 7 соответственно, а далее суммируются в высокоимпедансном узле Σ3. При этом коэффициент усиления по напряжению ОУ фиг. 2 определяется по формуле

Ky=RigDK, (4)

Ri - эквивалентное сопротивление в высокоимпедансном узле Σ3,

gDK - крутизна усиления входного дифференциального каскада на транзисторах 12, 13, 14 и 15.

За счет применения полевых транзисторов 3 и 7, а также наличия в цепи их истоков источников опорного тока 4 и 8, коэффициент усиления по напряжению ОУ фиг. 2 может принимать большие значения.

На основе рассматриваемой схемы ОУ могут быть реализованы так называемые трансимпедансные операционные усилители с использованием токового выхода 11, а также операционные усилители с потенциальным выходом 21, которые реализуются в соответствии с п. 2 формулы изобретения за счет введения буферного усилителя 20.

Замечательная особенность ОУ рассматриваемого подкласса состоит в том, что в нем реализуются предельно возможные значения частоты единичного усиления. Данный эффект обеспечивается применением двухтактного «перегнутого» каскода на транзисторах 3 и 7.

Напряжения смещения Ес1 и Ес2 выбираются исходя из требований к численным значениям напряжений в высокомпедансных узлах ЕΣ1, ЕΣ2, при которых транзисторы источников опорного тока, например, 22 и 24 на чертеже фиг. 3, работают в области высоких выходных сопротивлений.

Заданный запас устойчивости по фазе обеспечивается интегрирующим корректирующим конденсатором 19, который определяет наклон ЛАЧХ.

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с ОУ-прототипом.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Adel S. Sedra, Kenneth C. Smith, “Microelectronic Circuits”, Seventh Edition, New York, Oxford University Press, 2015, pp. 1025, Fig. 13.12

2. S.R. Zarabadi, F. Larsen and M. Ismail, "A reconfigurable op-amp/DDA CMOS amplifier architecture," in IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications, vol. 39, no. 6, pp. 484-487, June 1992, doi: 10.1109/81.153646

3. Эннс В.И., Кобзев Ю.М. Проектирование аналоговых КМОП-микросхем. Краткий справочник разработчика / Под редакцией канд.техн.наук В.И. Эннса. - М.: Горячая линия-Телеком. - 2005. - С. 206, рис. 3.81

4. M. Wang, T. Mayhugh, Sh. Embabi, E. Sanchez-Sinencio, “Constant-gm rail-to-rail CMOS op-amp input stage with overlapped transition regions”, IEEE Journal of. Solid-State Circuits, Vol. 34, No 2, 1999, pp. 148-156. Doi: 10.1109/4.743758.

5. Патент US 5.291.149, фиг. 1, 1994 г., фирма Murata Manufacturing Co, Ltd. (Япония)

6. Патент US 6.392.485, 2002 г., фирма Matsushita Electric Ind Co LTD (Япония)

7. Патентная заявка US 2004/0090268, 2004 г., фирма Texas Instruments Incorporated (США)

8. Патент CN 114465582, Fig. 5, 2022 г. (Китай)

9. Патент US 6.696.894, 2004 г., фирма Analog Devices (США)

10. Патент US 7.652.538, 2010 г., фирма Samsung Electronics Co. LTD (Южная Корея)

11. Патент US 5.805.021, фиг. 1, 1998 г., фирма Advanced Micro Devices (США)

12. Патент US 7.907.011, 2011 г., фирма Samsung Electronics Co. LTD (Южная Корея)

13. Патент US 5.894.245, 1999 г., фирма Samsung Electronics Co. LTD (Южная Корея)

14. Патентная заявка US 2005/0275459, 2005 г., фирма NEC Electronics Corporation (Япония)

15. Патент US 6.804.305, 2004 г., фирма International Business Machines Corporation (США)

| название | год | авторы | номер документа |

|---|---|---|---|

| Арсенид-галлиевый операционный усилитель с повышенным коэффициентом усиления и малым уровнем систематической составляющей напряжения смещения нуля | 2023 |

|

RU2820562C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ ДВУХТАКТНОГО "ПЕРЕГНУТОГО" КАСКОДА И КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРОВ С УПРАВЛЯЮЩИМ PN-ПЕРЕХОДОМ | 2022 |

|

RU2780220C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2022 |

|

RU2784666C1 |

| Операционный усилитель на основе широкозонных полупроводников | 2023 |

|

RU2822157C1 |

| Прецизионный арсенид-галлиевый операционный усилитель с малым уровнем систематической составляющей напряжения смещения нуля и повышенным коэффициентом усиления | 2023 |

|

RU2813370C1 |

| Арсенид-галлиевый операционный усилитель с малым напряжением смещения нуля | 2023 |

|

RU2812914C1 |

| Арсенид-галлиевый операционный усилитель для работы в широком диапазоне температур | 2023 |

|

RU2814685C1 |

| Арсенид-галлиевый операционный усилитель на основе "перегнутого" каскода | 2023 |

|

RU2820341C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ "ПЕРЕГНУТОГО" КАСКОДА | 2015 |

|

RU2595923C1 |

| НИЗКОТЕМПЕРАТУРНЫЙ ВХОДНОЙ КАСКАД ОПЕРАЦИОННОГО УСИЛИТЕЛЯ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ ВХОДНОГО СИНФАЗНОГО СИГНАЛА НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2020 |

|

RU2721943C1 |

Изобретение относится к области микроэлектроники. Технический результат - уменьшение влияния паразитных емкостей источников опорного тока I1, I2, устанавливающих статический режим входного дифференциального каскада, и их неидентичности на статические и динамические параметры операционного усилителя с двухтактным «перегнутым» каскодом. Такой результат обеспечивается за счет того, что в операционном усилителе затвор первого входного полевого транзистора соединен с первым неинвертирующим входом устройства, его исток соединен с истоком четвертого входного полевого транзистора, затвор третьего входного полевого транзистора подключен к первому неинвертирующему входу устройства, а его исток соединен с истоком второго входного полевого транзистора, причем сток второго входного полевого транзистора соединен с истоком первого выходного полевого транзистора промежуточного каскада, сток четвертого входного полевого транзистора соединен с истоком второго выходного полевого транзистора промежуточного каскада, затворы второго и четвертого входных полевых транзисторов соединены со вторым инвертирующим входом устройства, сток первого входного полевого транзистора подключен к третьему источнику напряжения смещения, сток третьего входного полевого транзистора подключен к четвертому источнику напряжения смещения. 4 з.п. ф-лы, 10 ил.

1. Операционный усилитель с промежуточным двухтактным «перегнутым» каскодом на комплементарных полевых транзисторах, содержащий первый (1) неинвертирующий и второй (2) инвертирующий входы устройства, первый (3) выходной полевой транзистор промежуточного каскада, исток которого через первый (4) источник опорного тока соединен с первой (5) шиной источника питания, а затвор связан с первым (6) источником напряжения смещения, второй (7) выходной полевой транзистор промежуточного каскада, исток которого через второй (8) источник опорного тока соединен со второй (9) шиной источника питания, а затвор связан со вторым (10) источником напряжения смещения, причем стоки первого (3) и второго (7) выходных полевых транзисторов промежуточного каскада соединены друг с другом и подключены к токовому выходу устройства (11), первый (12), второй (13), третий (14) и четвертый (15) входные полевые транзисторы входного дифференциального каскада, отличающийся тем, что затвор первого (12) входного полевого транзистора соединен с первым (1) неинвертирующим входом устройства, его исток соединен с истоком четвертого (15) входного полевого транзистора, затвор третьего (14) входного полевого транзистора подключен к первому (1) неинвертирующему входу устройства, а его исток соединен с истоком второго (13) входного полевого транзистора, причем сток второго (13) входного полевого транзистора соединен с истоком первого (3) выходного полевого транзистора промежуточного каскада, сток четвертого (15) входного полевого транзистора соединен с истоком второго (7) выходного полевого транзистора промежуточного каскада, а затворы второго (13) и четвертого (15) входных полевых транзисторов соединены со вторым (2) инвертирующим входом устройства, при этом сток первого (12) входного полевого транзистора подключен к третьему (16) источнику напряжения смещения, сток третьего (14) входного полевого транзистора подключен к четвертому (17) источнику напряжения смещения.

2. Операционный усилитель с промежуточным двухтактным «перегнутым» каскодом на комплементарных полевых транзисторах по п. 1, отличающийся тем, что токовый выход (11) устройства соединен со входом дополнительного буферного усилителя (20), выход которого (21) является потенциальным выходом устройства.

3. Операционный усилитель с промежуточным двухтактным «перегнутым» каскодом на комплементарных полевых транзисторах по п. 1, отличающийся тем, что первый (4) источник опорного тока выполнен на первом (22) дополнительном полевом транзисторе, исток которого связан с затвором через первый (23) вспомогательный резистор, а сток согласован с первой (5) шиной источника питания, а второй (8) источник опорного тока выполнен на втором (24) дополнительном полевом транзисторе, затвор которого связан с истоком через второй (25) вспомогательный резистор и согласован со второй (9) шиной источника питания.

4. Операционный усилитель с промежуточным двухтактным «перегнутым» каскодом на комплементарных полевых транзисторах по пп. 1, 3, отличающийся тем, что в качестве полевых транзисторов используются полевые транзисторы с управляющим p-n переходом.

5. Операционный усилитель с промежуточным двухтактным «перегнутым» каскодом на комплементарных полевых транзисторах по пп. 1, 3, отличающийся тем, что в качестве полевых транзисторов используются КМОП транзисторы со встроенным каналом.

| US 6696894 B1, 24.02.2004 | |||

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ ДВУХТАКТНОГО «ПЕРЕГНУТОГО» КАСКОДА | 2022 |

|

RU2786422C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ ДВУХТАКТНОГО "ПЕРЕГНУТОГО" КАСКОДА И КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРОВ С УПРАВЛЯЮЩИМ PN-ПЕРЕХОДОМ | 2022 |

|

RU2780220C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ «ПЕРЕГНУТОГО» КАСКОДА И КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРОВ | 2022 |

|

RU2773907C1 |

| US 4600893 A, 15.07.1986. | |||

Авторы

Даты

2025-04-01—Публикация

2024-09-27—Подача