ОБЛАСТЬ ТЕХНИКИ

[0001] Изобретение относится к схеме обнаружения и способу обнаружения.

УРОВЕНЬ ТЕХНИКИ

[0002] Обнаружение фазы представляет собой способ обнаружения фазового соотношения между двумя тактовыми сигналами и генерации выходного сигнала, соответствующего фазовому соотношению. Первоначально частоты двух тактовых сигналов для обнаружения фазы одинаковы, и традиционные схемы обнаружения фазы могут удовлетворять требованиям. Непрерывное развитие науки и технологий выдвигает новые требования к обнаружению фазы, то есть обнаружению фазы для высокочастотного тактового сигнала и низкочастотного тактового сигнала. На основе оригинального способа обнаружения фазы функция выполнения обнаружения фазы на тактовых сигналах с разными частотами может быть в основном реализована в режиме выполнения частотного разделения высокочастотного тактового сигнала с последующим выполнением обнаружения фазы.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

[0003] Согласно нескольким вариантам осуществления первый аспект изобретения предусматривает схему обнаружения, выполненную с возможностью обнаружения фазовой информации между двумя тактовыми сигналами разных частот. Два тактовых сигнала включают низкочастотный тактовый сигнал и высокочастотный тактовый сигнал. Схема обнаружения включает в себя модуль генерирования сигнала и модуль дискретизации.

[0004] Модуль генерирования сигнала выполнен с возможностью обнаружения низкочастотного тактового сигнала на фронте высокочастотного тактового сигнала для генерирования подлежащего дискретизации сигнала и генерирования целевого сигнала дискретизации, когда высокочастотный тактовый сигнал держится на заданном уровне и низкочастотный тактовый сигнал соответствует заданному состоянию.

[0005] Модуль дискретизации соединен с модулем генерирования сигналов и выполнен с возможностью обнаружения подлежащего дискретизации сигнала на фронте целевого сигнала дискретизации для генерирования сигнала результата обнаружения.

[0006] Согласно нескольким вариантам осуществления второй аспект изобретения предусматривает способ обнаружения, предназначенный для обнаружения фазовой информации между двумя тактовыми сигналами разных частот. Два тактовых сигнала включают низкочастотный тактовый сигнал и высокочастотный тактовый сигнал. Способ обнаружения включает следующие операции.

[0007] Низкочастотный тактовый сигнал обнаруживают на фронте высокочастотного тактового сигнала для генерирования подлежащего дискретизации сигнала и целевой дискретный сигнал генерируют, когда высокочастотный тактовый сигнал держится на заданном уровне и низкочастотный тактовый сигнал соответствует заданному состоянию.

[0008] Подлежащий дискретизации сигнал обнаруживают на фронте целевого сигнала дискретизации для генерирования сигнала результата обнаружения.

[0009] Подробности одного или нескольких вариантов осуществления изобретения изложены в сопроводительных графических материалах и описании ниже. Другие признаки и преимущества изобретения станут очевидными из технического описания, графических материалов и формулы изобретения.

КРАТКОЕ ОПИСАНИЕ ГРАФИЧЕСКИХ МАТЕРИАЛОВ

[0010] Чтобы сделать описание более ясным, ниже дается простое введение в сопроводительные графические материалы, которые необходимы для описания вариантов осуществления или известного уровня техники. Очевидно, что сопроводительные графические материалы в описании ниже представляют собой лишь некоторые варианты осуществления изобретения. Другие графические материалы могут быть получены специалистами в данной области техники без каких-либо творческих усилий согласно этим графическим материалам.

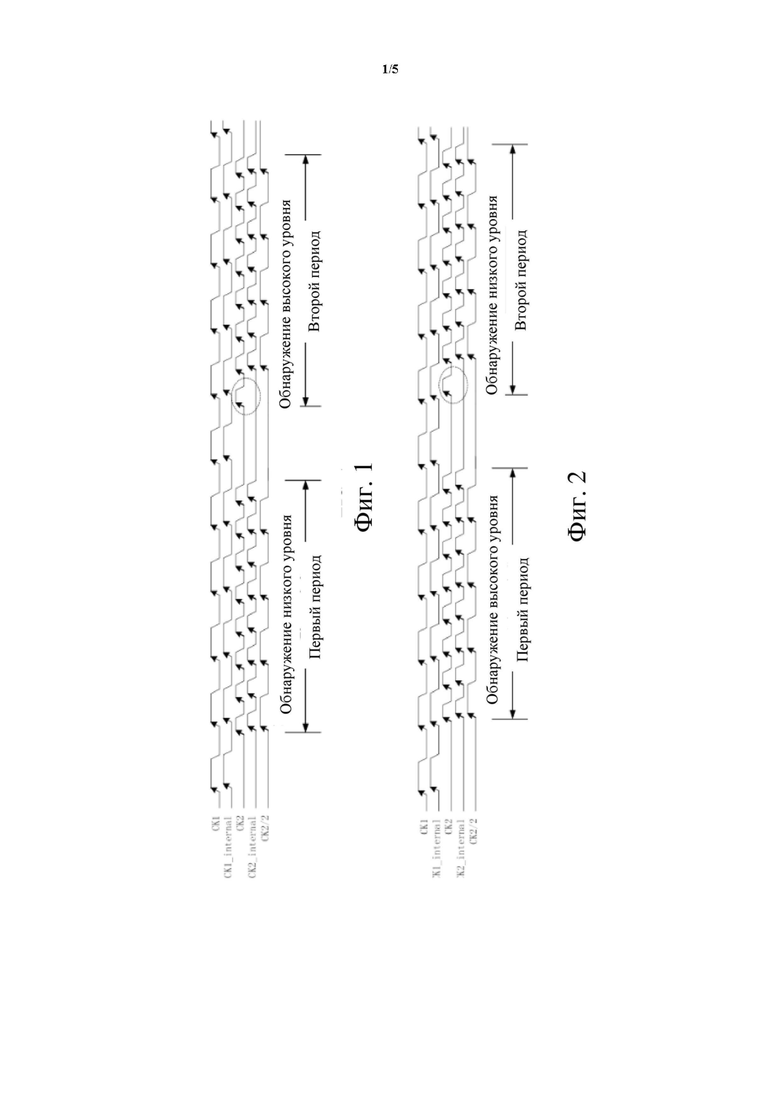

[0011] На фиг. 1 представлена схема временной последовательности результата обнаружения фазы в известном уровне техники.

[0012] На фиг. 2 представлена схема временной последовательности другого результата обнаружения фазы в известном уровне техники.

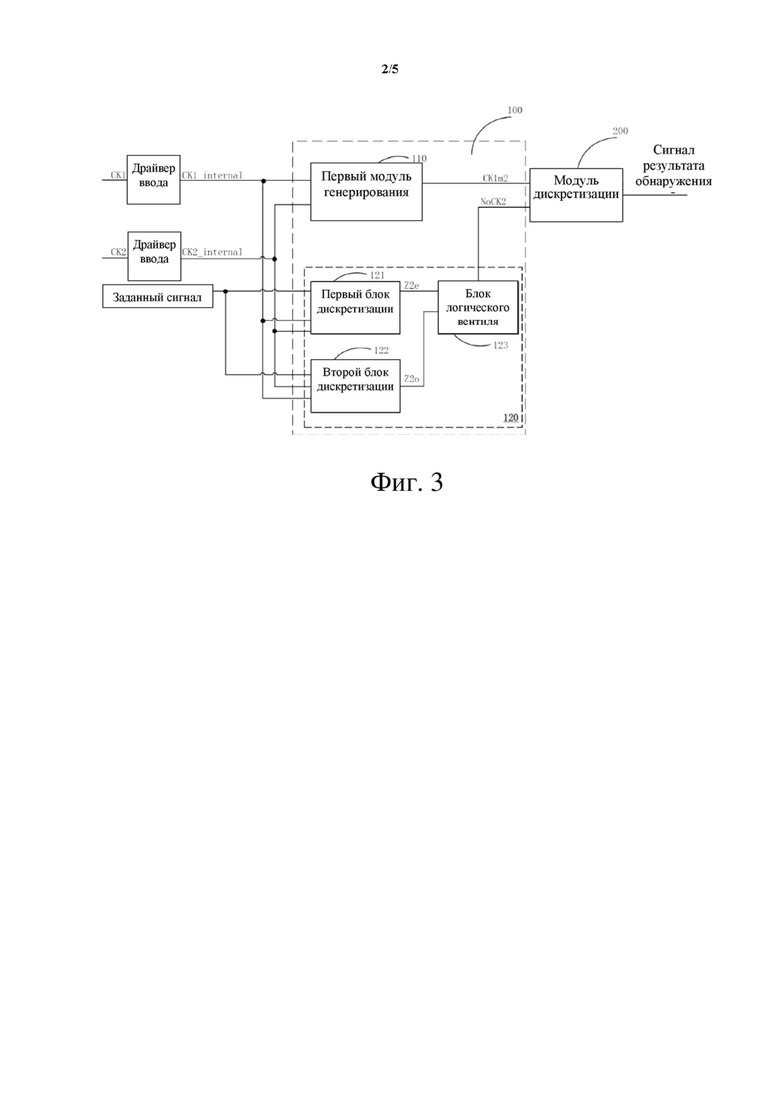

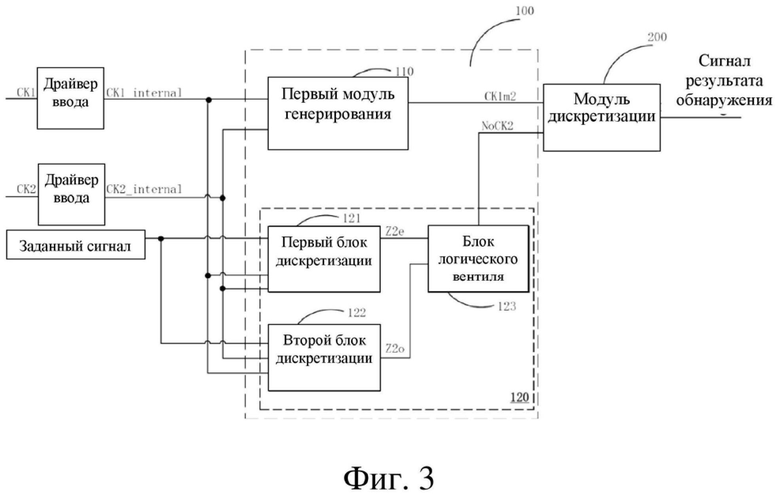

[0013] На фиг. 3 представлена структурная схема схемы обнаружения согласно одному варианту осуществления.

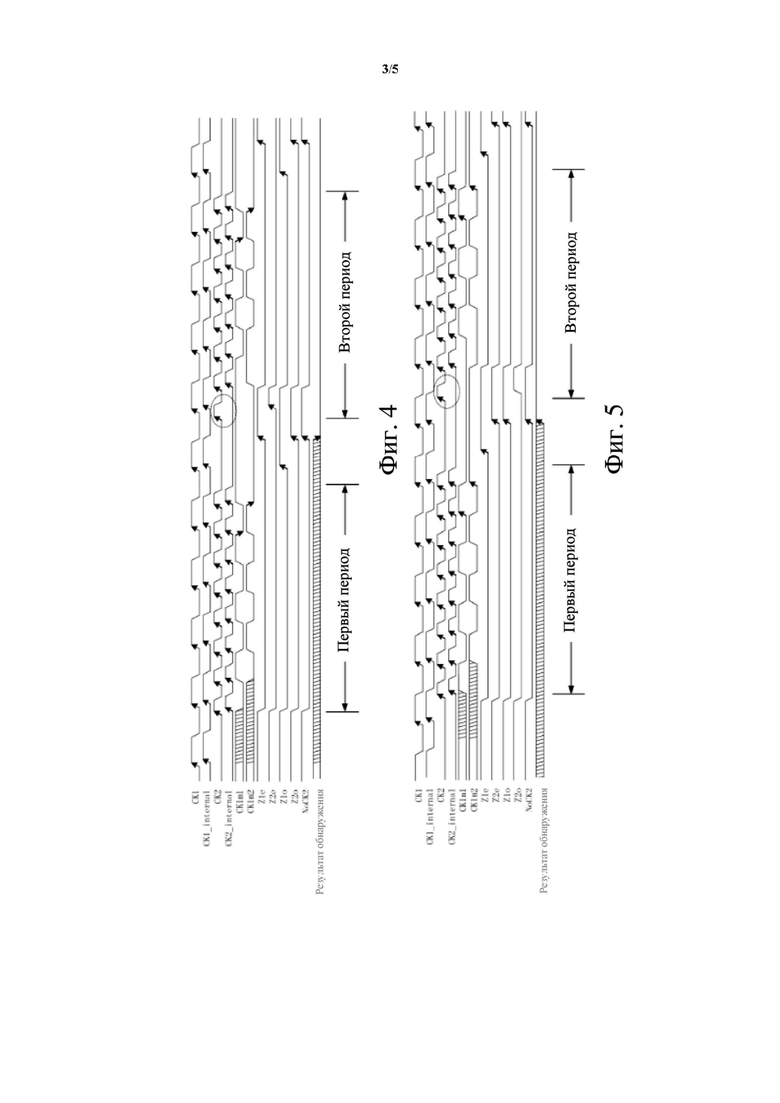

[0014] На фиг. 4 представлена схема временной последовательности, сгенерированная посредством обнаружения низкого уровня низкочастотного тактового сигнала схемой обнаружения согласно одному варианту осуществления.

[0015] На фиг. 5 представлена схема временной последовательности, сгенерированная посредством обнаружения высокого уровня низкочастотного тактового сигнала схемой обнаружения согласно одному варианту осуществления.

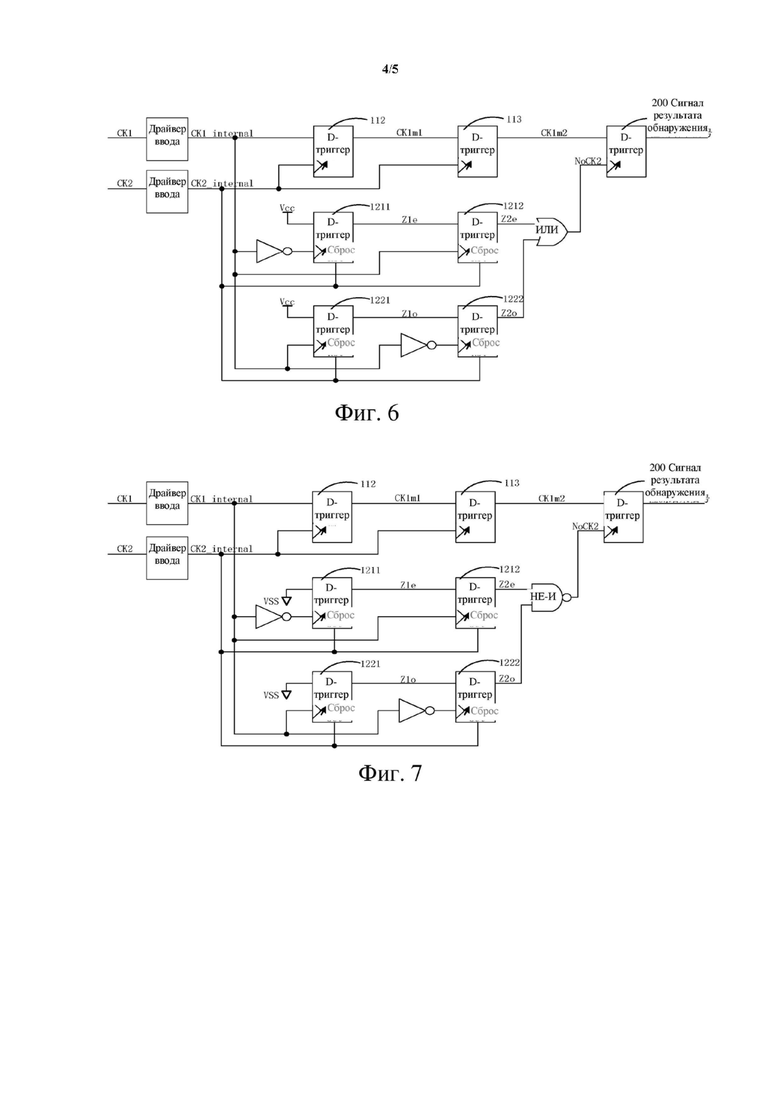

[0016] На фиг. 6 представлена структурная схема схемы обнаружения согласно одному варианту осуществления.

[0017] На фиг. 7 представлена структурная схема схемы обнаружения согласно другому варианту осуществления.

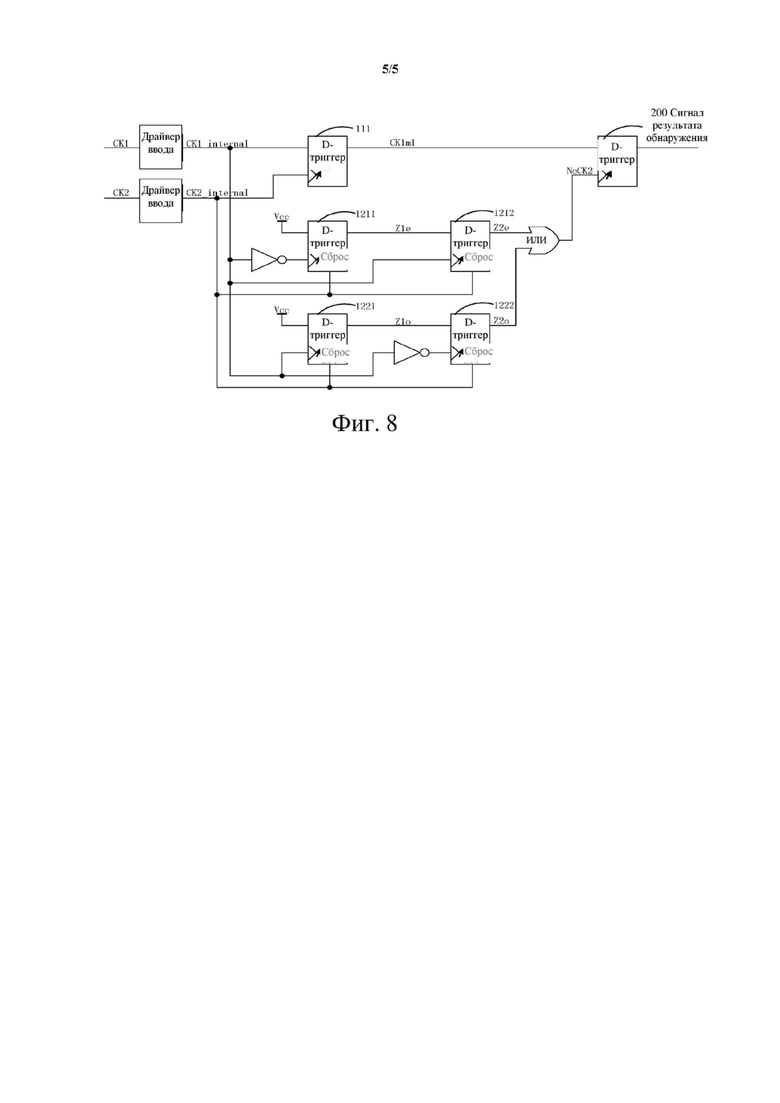

[0018] На фиг. 8 представлена структурная схема схемы обнаружения согласно еще одному варианту осуществления.

[0019] Описание численных обозначений элементов имеет следующий вид.

[0020] Модуль генерирования сигнала: 100; первый модуль генерирования: 110; пятый триггер: 111; шестой триггер: 112; седьмой триггер: 113; второй модуль генерирования: 120; первый блок дискретизации: 121; первый триггер: 1211; второй триггер: 1212; второй блок дискретизации: 122; третий триггер: 1221; четвертый триггер: 1222; блок логического вентиля: 123; и модуль дискретизации: 200.

ПОДРОБНОЕ ОПИСАНИЕ

[0021] В фактическом процессе использования тактовому сигналу необходимо сначала пройти через входной буфер для повышения эффективности тактового сигнала. Однако после прохождения тактового сигнала через входной буфер может возникнуть задержка, и даже первый импульс высокочастотного тактового сигнала может быть отфильтрован вследствие таких факторов, как нестабильное рабочее состояние, что тем самым сделает результат обнаружения фазы неверным. Следовательно, надежность существующей схемы обнаружения фазы и способа обнаружения является недостаточной.

[0022] Для облегчения понимания вариантов осуществления изобретения варианты осуществления изобретения будут подробно описаны ниже со ссылкой на сопроводительные графические материалы. Некоторые варианты осуществления изобретения представлены на сопроводительных графических материалах. Однако варианты осуществления изобретения могут быть осуществлены во многих других формах и не должны быть ограничены вариантами осуществления, изложенными в настоящем документе. Скорее эти варианты осуществления предусмотрены для того, чтобы раскрытие вариантов осуществления изобретения было полным и завершенным.

[0023] Если не определено иное, все технические и научные термины, используемые в данном документе, имеют то же значение, которое обычно понятно специалистам в области, к которой относятся варианты осуществления изобретения. Термины, используемые в данном документе в описании вариантов осуществления изобретения, служат для описания только конкретных вариантов осуществления и не предназначены для ограничения вариантов осуществления изобретения. Используемый в данном документе термин «и/или» включает любые и все комбинации одного или более из соответствующих перечисленных объектов.

[0024] Следует понимать, что хотя термины «первый», «второй» и т. п., используемые в изобретении, могут использоваться в данном документе для описания различных элементов, эти элементы не могут быть ограничены этими терминами. Эти термины приняты только для того, чтобы отличать один элемент от другого элемента. Например, без отступления от объема изобретения, первый триггер 1211 можно назвать вторым триггером 1212, и подобным образом второй триггер 1212 можно назвать первым триггером 1211. И первый триггер 1211, и второй триггер 1212 являются триггерами, но они не являются одним и тем же триггером.

[0025] Необходимо понимать, что «соединение» в следующих вариантах осуществления следует понимать как означающее «электрическое соединение», «соединение связи» и т. п., если соединенные схемы, модули, блоки и т. п. передают электрические сигналы или данные между собой.

[0026] Используемые в данном документе формы единственного числа и термины «указанный/этот» могут также включать формы множественного числа, если контексте явно не указывает иное. Также следует понимать, что термины «содержит/включает» или «имеет» и т. п. определяют наличие заявленного признака, элемента, этапа, операции, компонента, части или их комбинации, но не исключают наличия или добавления одного или более других признаков, элементов, этапов, операций, компонентов, частей или их комбинаций. В то же время термин «и/или», используемый в описании, включают любые и все комбинации соответствующих перечисленных объектов.

[0027] На фиг. 1 представлена схема временной последовательности результата обнаружения фазы в известном уровне техники. Со ссылкой на фиг. 1, два подлежащих обнаружению тактовых сигнала представляют собой CK1 и CK2 соответственно, а низкочастотный тактовый сигнал CK2_internal и высокочастотный тактовый сигнал CK1_internal получают соответственно после прохождения CK1 и CK2 через входной буфер. В известном уровне техники обработка частотного разделения должна быть выполнена на высокочастотном тактовом сигнале CK2_internal, чтобы получить сигнал CK2/2 с той же частотой, что и у низкочастотного тактового сигнала CK1_internal, а затем сигнал CK2/2 и низкочастотный тактовый сигнал CK1_internal сравнивают для получения фазовой информации между двумя подлежащими обнаружению тактовыми сигналами. Следует отметить, что высокая частота и низкая частота низкочастотного тактового сигнала CK1_internal и высокочастотного тактового сигнала CK2_internal относятся к относительности частот двух тактовых сигналов, то есть один из двух тактовых сигналов с более низкой частотой принимают как низкочастотный тактовый сигнал CK1_internal, а один с более высокой частотой принимают как высокочастотный тактовый сигнал CK2_internal, и не относится конкретно к тому, что сигнал в определенном диапазоне частот является низкочастотным тактовым сигналом или высокочастотным тактовым сигналом.

[0028] Как показано на фиг. 1, в первом периоде состояние низкого уровня низкочастотного тактового сигнала CK1_internal дискретизируют по нарастающему фронту сигнала CK2/2, то есть низкий уровень обнаруживают для генерирования результата обнаружения. Во втором периоде первый импульс в высокочастотном тактовом сигнале CK2_internal отфильтровывают, а импульс сигнала CK2, отмеченный кружком, теряется, так что временная последовательность сигнала CK2/2 с частотным разделением изменяется. Состояние высокого уровня низкочастотного тактового сигнала CK1_internal будет дискретизироваться по нарастающему фронту сигнала CK2/2, то есть высокий уровень обнаруживают для генерирования результата обнаружения, и в результате обнаружения возникает ошибка. Первый период и второй период относятся к первому периоду и второму периоду высокочастотного тактового сигнала CK2_internal. Со ссылкой на фиг. 1, каждый период включает множество сигналов с нарастающим фронтом, установленных через равные промежутки времени t1. Каждый сигнал с нарастающим фронтом реализован так, чтобы низкочастотный тактовый сигнал CK1_internal подвергался дискретизации один раз. Кроме того, заданный уровень держится в течение заданной длительности t2 между двумя смежными периодами высокочастотного тактового сигнала CK2_internal, а длительность t2 дольше, чем вышеуказанный временной интервал t1, например продолжительность t2 может быть равна продолжительности двух временных интервалов t1, тем самым различая разные периоды.

[0029] На фиг. 2 представлена схема временной последовательности другого результата обнаружения фазы в известном уровне техники. Со ссылкой на фиг. 2, в первом периоде состояние высокого уровня низкочастотного тактового сигнала CK1_internal дискретизируют по нарастающему фронту сигнала CK2/2, то есть высокий уровень обнаруживают для генерирования результата обнаружения. Во втором периоде первый импульс в высокочастотном тактовом сигнале CK2_internal отфильтровывают, а импульс в кружочке сигнала CK2 теряется, в результате чего временная последовательность сигнала CK2/2 с частотным разделением изменяется. Состояние низкого уровня низкочастотного тактового сигнала CK1_internal будет дискретизироваться по нарастающему фронту сигнала CK2/2, то есть низкий уровень обнаруживают для генерирования результата обнаружения, и в результате обнаружения возникает ошибка.

[0030] Следовательно, как показано на фиг. 1- 2, схема обнаружения в известном уровне техники может вызвать проблему неправильного результата обнаружения из-за того, что первый импульс в высокочастотном тактовом сигнале CK2_internal отфильтровывается.

[0031] На фиг. 3 представлена структурная схема схемы обнаружения согласно одному варианту осуществления. В этом варианте осуществления схема обнаружения выполнена с возможностью обнаружения фазовой информации между двумя тактовыми сигналами разных частот. Два тактовых сигнала включают в себя низкочастотный тактовый сигнал CK1_internal и высокочастотный тактовый сигнал CK2_internal. Вышеупомянутые два сигнала относятся к сигналам, выводимым после того, как подлежащие обнаружению тактовые сигналы CK1 и CK2 проходят через входной буфер, соответственно. Необходимо отметить, что в других вариантах осуществления определения низкочастотного тактового сигнала CK1_internal и высокочастотного тактового сигнала CK2_internal являются такими же, как и в этом варианте осуществления, и не будут подробно описаны.

[0032] Со ссылкой на фиг. 3, схема обнаружения включает в себя модуль 100 генерирования сигнала и модуль 200 дискретизации.

[0033] Модуль 100 генерирования сигнала выполнен с возможностью обнаружения низкочастотного тактового сигнала CK1_internal на фронте высокочастотного тактового сигнала CK2_internal для генерирования подлежащего дискретизации сигнала CK1m2 и генерирования целевого сигнала NoCK2 дискретизации, когда высокочастотный тактовый сигнал CK2_internal держится на заданном уровне и низкочастотный тактовый сигнал CK1_internal соответствует заданному состоянию.

[0034] Аналогично низкочастотному тактовому сигналу CK1_internal и высокочастотному тактовому сигналу CK2_internal в известном уровне техники, в этом варианте осуществления низкочастотный тактовый сигнал CK1_internal представляет собой непрерывный тактовый сигнал, а высокочастотный тактовый сигнал CK2_internal представляет собой прерывистый тактовый сигнал. В каждом периоде, в котором возникает высокочастотный тактовый сигнал, содержится множество импульсов высокочастотного тактового сигнала. Между двумя смежными периодами имеется интервальное время. В интервальное время, высокочастотный тактовый сигнал CK2_internal держится на заданном уровне. Следовательно, когда высокочастотный тактовый сигнал CK2_internal держится на заданном уровне, большем или равном заданной длительности, это указывает на то, что в настоящий момент он находится в интервальном времени между двумя смежными периодами. Необходимо отметить, что в других вариантах осуществления низкочастотный тактовый сигнал CK1_internal также может быть прерывистым тактовым сигналом, и настоящее изобретение не налагает ограничения на это.

[0035] На фиг. 4 представлена схема временной последовательности, сгенерированная посредством обнаружения низкого уровня низкочастотного тактового сигнала схемой обнаружения согласно одному варианту осуществления. Со ссылкой на фиг. 4, в этом варианте осуществления нарастающий фронт в целевом сигнале NoCK2 дискретизации генерируют не в ответ на нарастающий фронт или спадающий фронт высокочастотного тактового сигнала CK2_internal в периоде, а генерируют между двумя смежными периодами высокочастотного тактового сигнала CK2_internal. Следовательно, даже если часть импульсов сигнала в периоде отфильтровывается или возникают другие явления искажения, на целевой сигнал NoCK2 дискретизации это влиять не будет. Подлежащий дискретизации сигнал генерируют в ответ на фронт высокочастотного тактового сигнала CK2_internal, а низкочастотный тактовый сигнал CK1_internal предварительно дискретизируют для генерирования подлежащего дискретизации сигнала CK1m2, соответственно периоду высокочастотного тактового сигнала CK2_internal.

[0036] Продолжая ссылаться на фиг. 3, модуль 200 дискретизации соединен с модулем 100 генерирования сигналов и выполнен с возможностью обнаружения подлежащего дискретизации сигнала CK1m2 на фронте целевого сигнала NoCK2 дискретизации для генерирования сигнала результата обнаружения. На основе приведенной выше структуры схемы один импульсный сигнал в целевом сигнале NoCK2 дискретизации генерируется в соответствии с каждым периодом в высокочастотном тактовом сигнале CK2_internal, и импульсный сигнал генерируется между двумя смежными периодами высокочастотного тактового сигнала CK2_internal. Следовательно, аналогично целевому сигналу NoCK2 дискретизации, на сигнал результата обнаружения также не влияет изменение импульса в периоде высокочастотного тактового сигнала CK2_internal.

[0037] Высокочастотный тактовый сигнал CK2_internal вышеуказанной схемы обнаружения непрерывно выдает заданный уровень между двумя периодами, то есть после каждого периода высокочастотного тактового сигнала CK2_internal, только когда низкочастотный тактовый сигнал соответствует заданному состоянию, выводится результат обнаружения. Следовательно, даже если первый импульс в одном периоде высокочастотного тактового сигнала CK2_internal отфильтровывается, то на результат обнаружения это не повлияет, тем самым реализуется схема обнаружения с высокой надежностью.

[0038] В одном варианте осуществления, продолжая ссылаться на фиг. 3, модуль 100 генерирования сигнала содержит первый модуль 110 генерирования и второй модуль 120 генерирования.

[0039] Вывод данных первого модуля 110 генерирования соединен с низкочастотным тактовым сигналом CK1_internal, тактовый вывод первого модуля 110 генерирования соединен с высокочастотным тактовым сигналом CK2_internal, и первый модуль 110 генерирования выполнен с возможностью обнаружения низкочастотного тактового сигнала CK1_internal на фронте высокочастотного тактового сигнала CK2_internal для генерирования подлежащего дискретизации сигнала CK1m2.

[0040] Вывод данных второго модуля 120 генерирования соединен с заданным сигналом, тактовый вывод второго модуля 120 генерирования соединен с низкочастотным тактовым сигналом CK1_internal, вывод управления второго модуля 120 генерирования соединен с высокочастотным тактовым сигналом CK2_internal, и второй модуль 120 генерирования приспособлен, когда высокочастотный тактовый сигнал CK2_internal держится на заданном уровне, обнаруживать заданный сигнал на фронте низкочастотного тактового сигнала CK1_internal для генерирования целевого сигнала NoCK2 дискретизации. Заданный сигнал может быть сигналом высокого уровня или может быть сигналом низкого уровня. После того, как заданный сигнал обнаружен на фронте низкочастотного тактового сигнала CK1_internal, целевой сигнал NoCK2 дискретизации переключается в состояние уровня, такое же, как у заданного сигнала, для генерирования нарастающего фронта или спадающего фронта. Например, если заданный сигнал является сигналом высокого уровня, в ответ на фронт низкочастотного тактового сигнала CK1_internal целевой сигнал NoCK2 дискретизации переключается из состояния низкого уровня в состояние высокого уровня для генерирования одного нарастающего фронта, тем самым дискретизируя подлежащий дискретизации сигнал CK1m2.

[0041] В одном варианте осуществления, продолжая ссылаться на фиг. 3, вывод данных модуля 200 дискретизации соединен с первым модулем 110 генерирования, тактовый вывод модуля 200 дискретизации соединен со вторым модулем 120 генерирования, и модуль 200 дискретизации выполнен с возможностью обнаружения подлежащего дискретизации сигнала CK1m2 на фронте целевого сигнала NoCK2 дискретизации для генерирования сигнала результата обнаружения.

[0042] В одном варианте осуществления второй модуль 120 генерирования включает в себя первый блок 121 дискретизации, второй блок 122 дискретизации и блок 123 логического вентиля.

[0043] Вывод данных первого блока 121 дискретизации соединен с заданным сигналом, тактовый вывод первого блока 121 дискретизации соединен с низкочастотным тактовым сигналом CK1_internal, вывод управления первого блока 121 дискретизации соединен с высокочастотным тактовым сигналом CK2_internal, и первый блок 121 дискретизации приспособлен, когда низкочастотный тактовый сигнал CK1_internal выводит сигнал уровня первого заданного состояния, генерировать первый сигнал Z2e дискретизации с состоянием уровня таким же, как у заданного сигнала.

[0044] Вывод данных второго блока 122 дискретизации соединен с заданным сигналом, тактовый вывод второго блока 122 дискретизации соединен с низкочастотным тактовым сигналом, вывод управления второго блока 122 дискретизации соединен с высокочастотным тактовым сигналом CK2_internal, и второй блок 122 дискретизации приспособлен, когда низкочастотный тактовый сигнал CK1_internal выводит сигнал уровня второго заданного состояния, генерировать второй сигнал Z2o дискретизации с состоянием уровня таким же, как у заданного сигнала.

[0045] Продолжая ссылаться на фиг. 4, в первом периоде первый импульс высокочастотного тактового сигнала CK2_internal не отфильтровывается, и когда высокочастотный тактовый сигнал CK2_internal держится на заданном уровне (держится на низком уровне в варианте осуществления по фиг. 4), низкочастотный тактовый сигнал CK1_internal последовательно выводит сначала один нарастающий фронт и один спадающий фронт. Во втором периоде первый импульс высокочастотного тактового сигнала CK2_internal отфильтровывается, и когда высокочастотный тактовый сигнал CK2_internal держится на заданном уровне, низкочастотный тактовый сигнал CK1_internal последовательно выводит сначала один нарастающий фронт и один спадающий фронт. Следовательно, посредством установки первого блока 121 дискретизации и второго блока 122 дискретизации, а также того, что два блока дискретизации выполняют дискретизацию на основе низкочастотного тактового сигнала CK1_internal, выводя сигналы уровня разных заданных состояний соответственно, гарантируется, что правильный сигнал дискретизации может быть сгенерирован независимо от того, отфильтрован ли первый импульс высокочастотного тактового сигнала CK2_internal или нет.

[0046] Продолжая ссылаться на фиг. 3, два входных вывода блока 123 логического вентиля соответственно соединены с первым блоком 121 дискретизации и вторым блоком 122 дискретизации. Блок 123 логического вентиля выполнен с возможностью генерирования целевого сигнала NoCK2 дискретизации согласно первому сигналу Z2e дискретизации и второму сигналу Z2o дискретизации. Блок 123 логического вентиля логически обрабатывает первый сигнал Z2e дискретизации и второй сигнал Z2o дискретизации для выбора необходимого сигнала дискретизации, т. е. целевого сигнала NoCK2 дискретизации, из двух сигналов дискретизации, тем самым выдавая правильный результат обнаружения фазы. Блок 123 логического вентиля может быть одним из элемента И, элемента ИЛИ, элемента И-ИЛИ, элемента НЕ-И и т. п., которые могут реализовывать вышеуказанную функцию.

[0047] Кроме того, когда заданным сигналом является сигнал высокого уровня, в ответ на то, что низкочастотный тактовый сигнал CK1_internal соответствует заданному состоянию, первый сигнал Z2e дискретизации и второй сигнал Z2o дискретизации переключаются из состояния низкого уровня в состояние высокого уровня; когда заданным сигналом является сигнал низкого уровня, в ответ на то, что низкочастотный тактовый сигнал CK1_internal соответствует заданному состоянию, первый сигнал Z2e дискретизации и второй сигнал Z2o дискретизации переключаются из состояния высокого уровня в состояние низкого уровня. Разные состояния уровня должны соответствовать разным блокам 123 логического вентиля, чтобы генерировать целевой сигнал NoCK2 дискретизации. Таким образом, существует соответствующее отношение между логической функцией блока 123 логического вентиля и заданным сигналом, вводимым вторым модулем 120 генерирования.

[0048] В одном варианте осуществления первое заданное состояние заключается в том, что низкочастотный тактовый сигнал CK1_internal последовательно выводит один сигнал со спадающим фронтом и один сигнал с нарастающим фронтом. Второе заданное состояние заключается в том, что низкочастотный тактовый сигнал CK1_internal последовательно выводит один сигнал с нарастающим фронтом и один сигнал со спадающим фронтом. Первый блок 121 дискретизации генерирует первый сигнал Z2e дискретизации в ответ на первое заданное состояние, а второй блок 122 дискретизации генерирует второй сигнал Z2o дискретизации в ответ на второе заданное состояние. В этом варианте осуществления независимо от того, отфильтрован ли первый импульс высокочастотного тактового сигнала CK2_internal, второй сигнал Z2o дискретизации всегда берут как целевой сигнал NoCK2 дискретизации через блок 123 логического вентиля, тем самым гарантируя, что один правильный сигнал дискретизации может быть сгенерирован независимо от того, отфильтрован ли первый импульс высокочастотного тактового сигнала CK2_internal.

[0049] В одном варианте осуществления заданный сигнал представляет собой сигнал высокого уровня, блок 123 логического вентиля представляет собой вентильную схему ИЛИ, а вывод управления первого блока 121 дискретизации и вывод управления второго блока 122 дискретизации являются выводами сброса. То есть, когда разрешающий сигнал вводится на вывод управления первого блока 121 дискретизации и вывод управления второго блока 122 дискретизации, то есть когда на вывод управления вводится сигнал уровня, не являющегося заданным, (как, в одном варианте осуществления, если заданный уровень является низким уровнем, то сигнал высокого уровня вводится на вывод управления), как первый блок 121 дискретизации, так и второй блок 122 дискретизации выводят 0 в качестве начального выходного состояния первого блока 121 дискретизации и второго блока 122 дискретизации. Таким образом, когда низкочастотный тактовый сигнал CK1_internal выводит сигнал уровня, соответствующий первому заданному состоянию или второму заданному состоянию, соответственно, первый сигнал Z2e дискретизации или второй сигнал Z2o дискретизации переключается в состояние высокого уровня заданного сигнала, то есть в состояние «1».

[0050] В одном варианте осуществления заданный сигнал представляет собой сигнал низкого уровня, блок 123 логического вентиля представляет собой вентильную схему НЕ-И, а вывод управления первого блока 121 дискретизации и вывод управления второго блока 122 дискретизации являются заданными выводами. То есть, когда разрешающий сигнал вводится на вывод управления первого блока 121 дискретизации и вывод управления второго блока 122 дискретизации, то есть когда на выводы управления вводится сигнал уровня, не являющегося заданным, (в одном варианте осуществления, например, если заданный уровень является низким уровнем, то сигнал высокого уровня вводится на вывод управления), как первый блок 121 дискретизации, так и второй блок 122 дискретизации выводят 1 в качестве начального выходного состояния первого блока 121 дискретизации и второго блока 122 дискретизации. Таким образом, когда низкочастотный тактовый сигнал CK1_internal выводит сигнал уровня, соответствующий первому заданному состоянию или второму заданному состоянию, соответственно, первый сигнал Z2e дискретизации или второй сигнал Z2o дискретизации переключается в состояние низкого уровня заданного сигнала, то есть в состояние «0».

[0051] На фиг. 6 представлена структурная схема схемы обнаружения согласно одному варианту осуществления. Со ссылкой на фиг. 4 и фиг. 6, в этом варианте осуществления первый блок 121 дискретизации включает в себя первый триггер 1211 и второй триггер 1212.

[0052] Вывод данных первого триггера 1211 соединен с заданным сигналом, тактовый вывод первого триггера 1211 соединен с низкочастотным тактовым сигналом CK1_internal через инвертор, вывод управления первого триггера 1211 соединен с высокочастотным тактовым сигналом CK2_internal, и первый триггер 1211 выполнен с возможностью генерирования первого сигнала Z1e состояния, когда обнаружен сигнал со спадающим фронтом в первом заданном состоянии.

[0053] В варианте осуществления, показанном на фиг. 6, все триггеры являются D-триггерами, выводы управления всех триггеров являются выводами сброса, выводы сброса включаются на высоком уровне, а заданный сигнал является сигналом высокого уровня. Когда высокочастотный тактовый сигнал CK2_internal находится на высоком уровне, первый триггер 1211 выводит 0. Когда высокочастотный тактовый сигнал CK2_internal находится на низком уровне, в ответ на входной сигнал с тактового вывода первого триггера 1211, то есть нарастающий фронт инвертированного сигнала низкочастотного тактового сигнала CK1_internal, заданный сигнал Vcc дискретизируется, или в ответ на спадающий фронт низкочастотного тактового сигнала CK1_internal заданный сигнал Vcc дискретизируется.

[0054] Необходимо понимать, что в этом варианте осуществления в периоде импульса высокочастотного тактового сигнала CK2_internal все спадающие фронты низкочастотного тактового сигнала CK1_internal находятся в периоде высокого уровня высокочастотного тактового сигнала CK2_internal, то есть первый триггер 1211 не будет дискретизировать заданный сигнал Vcc, вводимый со входного вывода. Таким образом, в период импульса высокочастотного тактового сигнала CK2_internal выходной вывод первого триггера 1211 всегда выводит низкий уровень, а вне периода импульса высокочастотного тактового сигнала CK2_internal, то есть между двумя смежными периодами, первый триггер 1211 дискретизирует заданный сигнал Vcc и генерирует нарастающий фронт в первом сигнале Z1e состояния. Необходимо отметить, что приведенное выше описание предназначено только для примерного объяснения схемы временной последовательности, показанной на фиг. 4, и не предназначено для конкретного ограничения объема защиты изобретения, то есть продолжительность интервала между смежными нарастающими фронтами низкочастотного тактового сигнала CK1_internal не ограничивается двукратной длительностью интервала между смежными нарастающими фронтами высокочастотного тактового сигнала CK2_internal в варианте осуществления по фиг. 4. В других вариантах осуществления как низкочастотный тактовый сигнал CK1_internal, так и высокочастотный тактовый сигнал CK2_internal могут быть отрегулированы соответствующим образом согласно требованиям тестирования и не ограничены описанным выше случаем, в котором все спадающие фронты низкочастотного тактового сигнала CK1_internal находятся в периоде высокого уровня высокочастотного тактового сигнала CK2_internal. Для других низкочастотных тактовых сигналов CK1_internal и высокочастотных тактовых сигналов CK2_internal после регулировки схема обнаружения, основанная на этом варианте осуществления изобретения, также может выводить правильный сигнал обнаружения.

[0055] Второй триггер 1212 соединен с первым триггером 1211, тактовый вывод второго триггера 1212 соединен с низкочастотным тактовым сигналом CK1_internal, вывод управления второго триггера 1212 соединен с высокочастотным тактовым сигналом CK2_internal, входной вывод второго триггера 1212 соединен с выходным выводом первого триггера 1211, и второй триггер 1212 выполнен с возможностью задержки первого сигнала Z1e состояния для генерирования первого сигнала Z2e дискретизации. Подобно первому триггеру 1211, вне периода импульса высокочастотного тактового сигнала CK2_internal, то есть между двумя смежными периодами, в ответ на нарастающий фронт низкочастотного тактового сигнала CK1_internal второй триггер 1212 дискретизирует первый сигнал Z1e состояния для генерирования первого сигнала Z2e дискретизации. То есть первый триггер 1211 реализует распознавание спадающего фронта в низкочастотном тактовом сигнале CK1_internal, соответствующем первому заданному состоянию, а второй триггер 1212 реализует распознавание нарастающего фронта в низкочастотном тактовом сигнале CK1_internal, соответствующем первому заданному состоянию, тем самым вместе генерируя первый сигнал Z2e дискретизации.

[0056] Продолжая ссылаться на фиг. 6, в одном варианте осуществления второй блок 122 дискретизации включает в себя третий триггер 1221 и четвертый триггер 1222.

[0057] Вывод данных третьего триггера 1221 соединен с заданным сигналом Vcc, тактовый вывод третьего триггера 1221 соединен с низкочастотным тактовым сигналом CK1_internal, вывод управления третьего триггера 1221 соединен с высокочастотным тактовым сигналом CK2_internal, и третий триггер 1221 выполнен с возможностью генерирования второго сигнала Z1o состояния, когда обнаружен сигнал с нарастающим фронтом во втором заданном состоянии.

[0058] Когда высокочастотный тактовый сигнал CK2_internal находится на высоком уровне, третий триггер 1221 выводит 0. Когда высокочастотный тактовый сигнал CK2_internal находится на низком уровне, в ответ на входной сигнал из тактового вывода третьего триггера 1221, то есть нарастающий фронт низкочастотного тактового сигнала CK1_internal, заданный сигнал Vcc дискретизируется. Необходимо понимать, что в периоде импульса высокочастотного тактового сигнала CK2_internal все моменты нарастающих фронтов низкочастотного тактового сигнала CK1_internal находятся в пределах периода высокого уровня высокочастотного тактового сигнала CK2_internal, то есть заданный сигнал Vcc, вводимый из входного вывода, не будет дискретизирован. Таким образом, в период импульса высокочастотного тактового сигнала CK2_internal выходной вывод третьего триггера 1221 всегда выводит низкий уровень, а вне периода импульса высокочастотного тактового сигнала CK2_internal, т. е. между двумя смежными периодами, третий триггер 1221 дискретизирует заданный сигнал Vcc и генерирует нарастающий фронт во втором сигнале Z1o состояния.

[0059] Вывод данных четвертого триггера 1222 соединен с третьим триггером 1221, тактовый вывод четвертого триггера 1222 соединен с низкочастотным тактовым сигналом CK1_internal, вывод управления четвертого триггера 1222 соединен с высокочастотным тактовым сигналом CK2_internal, и входной вывод четвертого триггера 1222 соединен с выходным выводом третьего триггера 1221. Четвертый триггер 1222 выполнен с возможностью задержки второго сигнала Z1oZ2e состояния для генерирования второго сигнала Z2o дискретизации. Подобно третьему триггеру 1221, вне периода импульса высокочастотного тактового сигнала CK2_internal, т. е. между двумя смежными периодами, в ответ на спадающий фронт низкочастотного тактового сигнала CK1_internal, четвертый триггер 1222 дискретизирует первый сигнал Z1e состояния для генерирования второго сигнала Z2oZ2e дискретизации. То есть третий триггер 1221 реализует распознавание спадающего фронта в низкочастотном тактовом сигнале CK1_internal, соответствующем второму заданному состоянию, а четвертый триггер 1222 реализует распознавание нарастающего фронта в низкочастотном тактовом сигнале CK1_internal, соответствующем второму заданному состоянию, тем самым вместе генерируя второй сигнал Z2o дискретизации.

[0060] На фиг. 5 представлена схема временной последовательности, сгенерированная посредством обнаружения низкого уровня высокочастотного тактового сигнала схемой обнаружения согласно одному варианту осуществления. Со ссылкой на фиг. 5, логика дискретизации для обнаружения высокого уровня подобна логике для обнаружения низкого уровня, как показано на фиг. 4. То есть, когда высокочастотный тактовый сигнал CK2_internal держится на низком уровне, в ответ на последовательное генерирование спадающего фронта и нарастающего фронта в низкочастотном тактовом сигнале CK1_internal, схема обнаружения генерирует нарастающий фронт в первом сигнале Z2e дискретизации, а в ответ на последовательное генерирование нарастающего фронта и спадающего фронта в низкочастотном тактовом сигнале CK1_internal, схема обнаружения генерирует нарастающий фронт во втором сигнале Z2o дискретизации. Как можно видеть на фиг. 4 и фиг. 5, схема обнаружения этого варианта осуществления применима к двум разным режимам дискретизации, дискретизация высокого уровня и дискретизация низкого уровня, и имеет более высокую гибкость и совместимость.

[0061] Кроме того, когда схема логического вентиля этого варианта осуществления представляет собой вентиль ИЛИ, то есть по меньшей мере один из первого сигнала Z2e дискретизации или второго сигнала Z2o дискретизации находится на высоком уровне, целевой сигнал NoCK2 дискретизации находится на высоком уровне, тем самым обеспечивая точный целевой сигнал NoCK2 дискретизации.

[0062] На фиг. 7 представлена структурная схема схемы обнаружения согласно другому варианту осуществления. Со ссылкой на фиг. 7, в этом варианте осуществления выводы управления всех триггеров являются заданными выводами, и заданные выводы включаются на высоком уровне, а заданный сигнал является сигналом низкого уровня. Когда высокочастотный тактовый сигнал CK2_internal находится на высоком уровне, каждый триггер выводит 1. Когда высокочастотный тактовый сигнал CK2_internal находится на низком уровне, каждый триггер реагирует на входной сигнал с тактового вывода для дискретизации заданного сигнала Vss, поступающего с входного вывода. Следовательно, когда высокочастотный тактовый сигнал CK2_internal находится на низком уровне, первый триггер 1211 дискретизирует заданный сигнал Vss в ответ на спадающий фронт низкочастотного тактового сигнала CK1_internal для генерирования спадающего фронта в первом сигнале Z1e состояния, и первый сигнал Z1e состояния задерживается вторым триггером 1212 для генерирования первого сигнала Z2e дискретизации. Соответственно, третий триггер 1221 дискретизирует заданный сигнал Vss в ответ на спадающий фронт низкочастотного тактового сигнала CK1_internal для генерирования спадающего фронта во втором сигнале Z1o состояния, и второй сигнал Z1o состояния задерживается вторым триггером 1212 для генерирования второго сигнала Z2o дискретизации.

[0063] Кроме того, когда схема 123 логического вентиля этого варианта осуществления представляет собой вентиль НЕ-И, то есть по меньшей мере один из первого сигнала Z2e дискретизации или второго сигнала Z2o дискретизации находится на низком уровне, целевой сигнал NoCK2 дискретизации находится на высоком уровне, тем самым обеспечивая точный целевой сигнал NoCK2 дискретизации.

[0064] На фиг. 8 представлена структурная схема схемы обнаружения согласно еще одному варианту осуществления. Схема обнаружения этого варианта осуществления применима к высокочастотному тактовому сигналу CK2_internal, включая нечетное количество импульсных сигналов в каждом периоде. Со ссылкой на фиг. 8, первый модуль 110 генерирования включает в себя пятый триггер 111. Вывод данных пятого триггера 111 соединен с низкочастотным тактовым сигналом CK1_internal, тактовый вывод пятого триггера 111 соединен с высокочастотным тактовым сигналом CK2_internal, выходной вывод пятого триггера 111 соединен с выводом данных модуля 200 дискретизации, и пятый триггер 111 приспособлен для обнаружения низкочастотного тактового сигнала CK1_internal на фронте высокочастотного тактового сигнала CK2_internal для генерирования начального подлежащего дискретизации сигнала CK1m1. Начальный подлежащий дискретизации сигнал CK1m1 принимают как подлежащий дискретизации сигнал CK1m2.

[0065] Продолжая ссылаться на фиг. 6 и фиг. 7, когда каждый период высокочастотного тактового сигнала CK2_internal включает в себя четное количество импульсных сигналов, первый модуль 110 генерирования включает в себя шестой триггер 112 и седьмой триггер 113.

[0066] Что касается шестого триггера 112, вывод данных шестого триггера 112 соединен с низкочастотным тактовым сигналом CK1_internal, тактовый вывод шестого триггера 112 соединен с высокочастотным тактовым сигналом CK2_internal, а шестой триггер 112 приспособлен для обнаружения низкочастотного тактового сигнала CK1_internal на фронте высокочастотного тактового сигнала CK2_internal для генерирования начального подлежащего дискретизации сигнала CK1m1.

[0067] Что касается седьмого триггера 113, вывод данных седьмого триггера 113 соединен с шестым триггером 112, тактовый вывод седьмого триггера 113 соединен с высокочастотным тактовым сигналом CK2_internal, выходной вывод седьмого триггера 113 соединен с выводом данных модуля 200 дискретизации, и седьмой триггер 113 приспособлен для задержки начального подлежащего дискретизации сигнала CK1m1 для генерирования подлежащего дискретизации сигнала CK1m2.

[0068] В этом варианте осуществления седьмой триггер 113 настроен задерживать начальный подлежащий дискретизации сигнал CK1m1, чтобы опрокидывать состояние уровня начального подлежащего дискретизации сигнала CK1m1 и генерировать подлежащий дискретизации сигнала CK1m2, так чтобы дискретизировать состояние целевого уровня низкочастотного тактового сигнала CK1_internal.

[0069] Способ обнаружения предоставлен и выполнен с возможностью обнаружения фазовой информации между двумя тактовыми сигналами разных частот. Два тактовых сигнала включают в себя низкочастотный тактовый сигнал CK1_internal и высокочастотный тактовый сигнал CK2_internal. Способ обнаружения включает следующие операции.

[0070] Низкочастотный тактовый сигнал CK1_internal обнаруживают на фронте высокочастотного тактового сигнала CK2_internal для генерирования подлежащего дискретизации сигнала CK1m2, и целевой сигнал NoCK2 дискретизации генерируют, когда высокочастотный тактовый сигнал CK2_internal держится на заданном уровне и низкочастотный тактовый сигнал CK1_internal соответствует заданному состоянию.

[0071] Подлежащий дискретизации сигнал CK1m2 обнаруживают на фронте целевого сигнала NoCK2 дискретизации для генерирования сигнала результата обнаружения.

[0072] В одном варианте осуществления операция, при которой целевой сигнал NoCK2 дискретизации генерируют, когда высокочастотный тактовый сигнал CK2_internal держится на заданном уровне и низкочастотный тактовый сигнал CK1_internal соответствует заданному состоянию, включает следующую операцию.

[0073] Когда высокочастотный тактовый сигнал CK2_internal держится на заданном уровне, заданный сигнал обнаруживают на фронте низкочастотного тактового сигнала CK1_internal, соответствующего заданному состоянию, для генерирования целевого сигнала NoCK2 дискретизации.

[0074] В этом варианте осуществления после каждого периода высокочастотного тактового сигнала CK2_internal, только когда низкочастотный тактовый сигнал соответствует заданному состоянию, выводят результат обнаружения. Следовательно, даже если первый импульс высокочастотного тактового сигнала CK2_internal в одном периоде отфильтровывается, то на результат обнаружения это не повлияет, тем самым реализуют схему обнаружения с высокой надежностью.

[0075] Способ обнаружения в вышеупомянутом варианте осуществления соответствует схеме обнаружения согласно вышеупомянутым вариантам осуществления, и подробности могут быть получены со ссылкой на соответствующие варианты осуществления схемы обнаружения и здесь не будут описаны подробно.

[0076] Технические признаки вышеуказанных вариантов осуществления можно свободно комбинировать. Для краткости описание не приводится для всех возможных комбинаций технических признаков вариантов осуществления. Тем не менее, комбинации этих технических признаков следует рассматривать как попадающие в объем технического описания, если нет противоречий.

[0077] Вышеуказанные варианты осуществления описывают только несколько режимов реализации вариантов осуществления изобретения. Описание является конкретным и подробным, но его нельзя понимать как ограничение объема патента настоящего изобретения соответственно. Необходимо отметить, что несколько вариаций и модификаций также могут быть выполнены специалистами в данной области без отклонения от сущности вариантов осуществления изобретения, которые все попадают в рамки объема защиты вариантов осуществления изобретения. Таким образом, объем правовой охраны патента варианта осуществления изобретения необходимо определять согласно прилагаемой формуле изобретения.

Изобретение относится к измерительной технике и может быть использовано для обнаружения фазового соотношения между двумя тактовыми сигналами разных частот. Технический результат: повышение надежности. Сущность: схема обнаружения содержит модуль генерирования сигнала, выполненный с возможностью обнаружения низкочастотного тактового сигнала на фронте высокочастотного тактового сигнала для генерирования подлежащего дискретизации сигнала и генерирования целевого сигнала дискретизации, когда высокочастотный тактовый сигнал держится на заданном уровне и низкочастотный тактовый сигнал соответствует заданному состоянию, и модуль дискретизации. Модуль дискретизации соединен с модулем генерирования сигнала и выполнен с возможностью обнаружения подлежащего дискретизации сигнала на фронте целевого сигнала дискретизации для генерирования сигнала результата обнаружения. 2 н. и 11 з.п. ф-лы, 8 ил.

1. Схема обнаружения, выполненная с возможностью обнаружения фазовой информации между двумя тактовыми сигналами разных частот, где два тактовых сигнала содержат низкочастотный тактовый сигнал и высокочастотный тактовый сигнал, при этом схема обнаружения содержит:

модуль генерирования сигнала, выполненный с возможностью обнаружения низкочастотного тактового сигнала на фронте высокочастотного тактового сигнала для генерирования подлежащего дискретизации сигнала, а также генерирования целевого сигнала дискретизации, когда высокочастотный тактовый сигнал держится на заданном уровне и низкочастотный тактовый сигнал соответствует заданному состоянию; и

модуль дискретизации, соединенный с модулем генерирования сигнала и выполненный с возможностью обнаружения подлежащего дискретизации сигнала на фронте целевого сигнала дискретизации для генерирования сигнала результата обнаружения.

2. Схема обнаружения по п. 1, отличающаяся тем, что модуль генерирования сигнала содержит:

первый модуль генерирования, при этом вывод данных первого модуля генерирования сигнала соединен с низкочастотным тактовым сигналом, тактовый вывод первого модуля генерирования соединен с высокочастотным тактовым сигналом и первый модуль генерирования выполнен с возможностью обнаружения низкочастотного тактового сигнала на фронте высокочастотного тактового сигнала для генерирования подлежащего дискретизации сигнала; и

второй модуль генерирования, при этом вывод данных второго модуля генерирования соединен с заданным сигналом, тактовый вывод второго модуля генерирования соединен с низкочастотным тактовым сигналом, вывод управления второго модуля генерирования соединен с высокочастотным тактовым сигналом и второй модуль генерирования приспособлен, когда высокочастотный тактовый сигнал держится на заданном уровне, для обнаружения заданного сигнала на фронте низкочастотного тактового сигнала для генерирования целевого сигнала дискретизации.

3. Схема обнаружения по п. 2, отличающаяся тем, что вывод данных модуля дискретизации соединен с первым модулем генерирования, тактовый вывод модуля дискретизации соединен со вторым модулем генерирования, а модуль дискретизации выполнен с возможностью обнаружения подлежащего дискретизации сигнала на фронте целевого сигнала дискретизации для генерирования сигнала результата обнаружения.

4. Схема обнаружения по п. 3, отличающаяся тем, что второй модуль генерирования содержит:

первый блок дискретизации, при этом вывод данных первого блока дискретизации соединен с заданным сигналом, тактовый вывод первого блока дискретизации соединен с низкочастотным тактовым сигналом, вывод управления первого блока дискретизации соединен с высокочастотным тактовым сигналом и первый блок дискретизации приспособлен, когда низкочастотный тактовый сигнал выводит сигнал уровня первого заданного состояния, для генерирования первого сигнала дискретизации с состоянием уровня, идентичным состоянию уровня заданного сигнала;

второй блок дискретизации, при этом вывод данных второго блока дискретизации соединен с заданным сигналом, тактовый вывод второго блока дискретизации соединен с низкочастотным тактовым сигналом, вывод управления второго блока дискретизации соединен с высокочастотным тактовым сигналом и второй блок дискретизации приспособлен, когда низкочастотный тактовый сигнал выводит сигнал уровня второго заданного состояния, для генерации второго сигнала дискретизации с состоянием уровня, идентичным состоянию уровня заданного сигнала; и

блок логического вентиля, при этом два входных конца блока логического вентиля соответственно соединены с первым блоком дискретизации и вторым блоком дискретизации и блок логического вентиля выполнен с возможностью генерации целевого сигнала дискретизации согласно первому дискретному сигналу и второму дискретному сигналу.

5. Схема обнаружения по п. 4, отличающаяся тем, что заданный сигнал представляет собой сигнал высокого уровня, блок логического вентиля представляет собой вентильную схему ИЛИ, а вывод управления первого блока дискретизации и вывод управления второго блока дискретизации представляют собой выводы сброса.

6. Схема обнаружения по п. 4, отличающаяся тем, что заданный сигнал представляет собой сигнал низкого уровня, блок логического вентиля представляет собой вентильную схему НЕ-И, а вывод управления первого блока дискретизации и вывод управления второго блока дискретизации представляют собой заданные выводы.

7. Схема обнаружения по п. 4, отличающаяся тем, что первое заданное состояние заключается в том, что низкочастотный тактовый сигнал последовательно выводит один сигнал со спадающим фронтом и один сигнал с нарастающим фронтом в последовательности, а второе заданное состояние заключается в том, что низкочастотный тактовый сигнал последовательно выводит один сигнал с нарастающим фронтом и один сигнал со спадающим фронтом в последовательности.

8. Схема обнаружения по п. 7, отличающаяся тем, что первый блок дискретизации содержит:

первый триггер, при этом вывод данных первого триггера соединен с заданным сигналом, тактовый вывод первого триггера соединен с низкочастотным тактовым сигналом через инвертор, вывод управления первого триггера соединен с высокочастотным тактовым сигналом и первый триггер приспособлен для генерирования первого сигнала состояния, когда обнаружен сигнал со спадающим фронтом в первом заданном состоянии; и

второй триггер, соединенный с первым триггером, при этом тактовый вывод второго триггера соединен с низкочастотным тактовым сигналом, вывод управления второго триггера соединен с высокочастотным тактовым сигналом и второй триггер приспособлен задерживать первый сигнал состояния для генерирования первого сигнала дискретизации.

9. Схема обнаружения по п. 7, отличающаяся тем, что второй блок дискретизации содержит:

третий триггер, при этом вывод данных третьего триггера соединен с заданным сигналом, тактовый вывод третьего триггера соединен с низкочастотным тактовым сигналом, вывод управления третьего триггера соединен с высокочастотным тактовым сигналом и третий триггер приспособлен для генерирования второго сигнала состояния, когда обнаружен сигнал со спадающим фронтом во втором заданном состоянии; и

четвертый третий триггер, при этом вывод данных четвертого триггера соединен с третьим триггером, тактовый вывод четвертого триггера соединен с низкочастотным тактовым сигналом, вывод управления четвертого триггера соединен с высокочастотным тактовым сигналом и четвертый триггер приспособлен задерживать второй сигнал состояния для генерирования второго сигнала дискретизации.

10. Схема обнаружения по п. 2, отличающаяся тем, что каждый период высокочастотного тактового сигнала содержит нечетное количество импульсных сигналов, при этом первый модуль генерирования содержит:

пятый триггер, причем вывод данных пятого триггера соединен с низкочастотным тактовым сигналом, тактовый вывод пятого триггера соединен с высокочастотным тактовым сигналом, выходной вывод пятого триггера соединен с выводом данных модуля дискретизации и пятый триггер приспособлен для обнаружения низкочастотного тактового сигнала на фронте высокочастотного тактового сигнала для генерирования подлежащего дискретизации сигнала.

11. Схема обнаружения по п. 2, отличающаяся тем, что каждый период высокочастотного тактового сигнала содержит четное количество импульсных сигналов, при этом первый модуль генерирования содержит:

шестой триггер, причем вывод данных шестого триггера соединен с низкочастотным тактовым сигналом, тактовый вывод шестого триггера соединен с высокочастотным тактовым сигналом и шестой триггер приспособлен для обнаружения низкочастотного тактового сигнала на фронте высокочастотного тактового сигнала для генерирования начального подлежащего дискретизации сигнала; и

седьмой триггер, причем вывод данных седьмого триггера соединен с шестым триггером, тактовый вывод седьмого триггера соединен с высокочастотным тактовым сигналом, выходной вывод седьмого триггера соединен с выводом данных модуля дискретизации и седьмой триггер приспособлен задерживать начальный подлежащий дискретизации сигнал для генерирования подлежащего дискретизации сигнала.

12. Способ обнаружения, предназначенный для обнаружения фазовой информации между двумя тактовыми сигналами разных частот, где два тактовых сигнала содержат низкочастотный тактовый сигнал и высокочастотный тактовый сигнал, при этом способ обнаружения содержит:

обнаружение низкочастотного тактового сигнала на фронте высокочастотного тактового сигнала для генерирования подлежащего дискретизации сигнала и генерирование целевого сигнала дискретизации, когда высокочастотный тактовый сигнал держится на заданном уровне и низкочастотный тактовый сигнал соответствует заданному состоянию; и

обнаружение подлежащего дискретизации сигнала на фронте целевого сигнала дискретизации для генерирования сигнала результата обнаружения.

13. Способ обнаружения по п. 12, отличающийся тем, что генерирование целевого сигнала дискретизации в случае, когда высокочастотный тактовый сигнал держится на заданном уровне и низкочастотный тактовый сигнал соответствует заданному состоянию, содержит:

когда высокочастотный тактовый сигнал держится на заданном уровне, обнаружение заданного сигнала на фронте низкочастотного тактового сигнала, соответствующего заданному состоянию, для генерирования целевого сигнала дискретизации.

| US 5553275 A1, 03.09.1996 | |||

| CN 101551418 B, 13.04.2011 | |||

| Устройство для торкретирования и подачи кислорода в конвертер | 1984 |

|

SU1199804A1 |

| CN 101046489 A, 03.10.2007 | |||

| Фазометр с масштабно-временным преобразованием | 1987 |

|

SU1422180A1 |

| ФАЗОМЕТР | 2015 |

|

RU2582625C1 |

Авторы

Даты

2023-10-30—Публикация

2021-06-17—Подача