Область изобретения

Изобретение относится к процессорам, а в частности, к архитектуре и протоколу шины с учетверенной подкачкой.

С увеличением сложности современного программного обеспечения и приложений и спроса на них возникает требование к процессорам обеспечить возрастающую производительность и полосу частот. В наличии может быть один или более ресурсов, работа которых может ограничить характеристики компьютера, такие как скорость ввода-вывода (I/O) или полоса частот, размер памяти и т.п. Одним из ресурсов, который обычно ограничивает или снижает характеристики компьютера, является скорость и полоса частот процессорной шины или внешней шины, которая представляет собой шину, предусмотренную между одним или более процессорами и набором микросхем. К примеру, некоторые процессоры Pentium® (такие как процессоры Pentium® Pro фирмы Intel Corporation) включают в себя 64-разрядную шину данных и могут передавать 8 байтов за период тактового сигнала процессора, а также могут передавать 32-байтовую строку кэша за 4 периода тактового сигнала. Таким образом, если тактовый сигнал процессора обеспечивается с частотой 100 МГц (например), скорость передачи данных составит 800 Мбайт в секунду. Различные подробности по архитектуре процессора Pentium Pro можно найти в "Pentium Pro Family Developer's Manual, Volume 1: Specifications", January, 1996, ISBN 1-55512-259-0. Хотя скорость передачи данных, равная 800 Мбайт/сек, достаточна для многих применений, существует потребность в процессорной шине, которая обеспечивает улучшенные скорость передачи данных или полосу частот.

Сущность изобретения

Согласно варианту осуществления настоящего изобретения обеспечивается способ передачи информации по многоточечной шине от задающего исполнительного устройства (агента) к одному или более принимающих исполнительных устройств (агентов). Как для задающего агента, так и для принимающего агента предусматривается тактовый сигнал общей шины. Шинная транзакция выдается от задающего агента к одному или более принимающим агентам, в том числе: 1) задающий агент задает множество информационных элементов для запроса по адресной шине с частотой, которая кратна частоте тактового сигнала шины; и 2) задающий агент активирует первый стробирующий сигнал, чтобы идентифицировать, когда принимающий агент должен осуществлять выборку информационных элементов, заданных на адресной шине. Этот способ включает в себя также передачу данных от задающего агента к одному или более принимающим агентам, при этом: 1) задающий агент задает множество информационных элементов на шину данных с частотой, которая является другим кратным от частоты тактового сигнала шины; и 2) задающий агент активирует второй стробирующий сигнал, чтобы идентифицировать, когда один или более принимающих агентов должны осуществлять выборку информационных элементов, заданных на шину данных.

Краткое описание чертежей

Предшествующее описание, а также лучшее понимание настоящего изобретения станут яснее из нижеследующего подробного описания примерных вариантов выполнения и формулы изобретения, рассматриваемых совместно с сопровождающими чертежами, которые все образуют часть раскрытия данного изобретения. Хотя предшествующее и нижеследующее записанное и проиллюстрированное раскрытие посвящено раскрываемым примерным вариантам выполнения, следует ясно понимать, что это сделано только в качестве иллюстрации и примера и не ограничивает изобретения. Сущность и объем настоящего изобретения ограничиваются только понятиями приложенной формулы изобретения.

Нижеследующее представляет краткое описание чертежей, где:

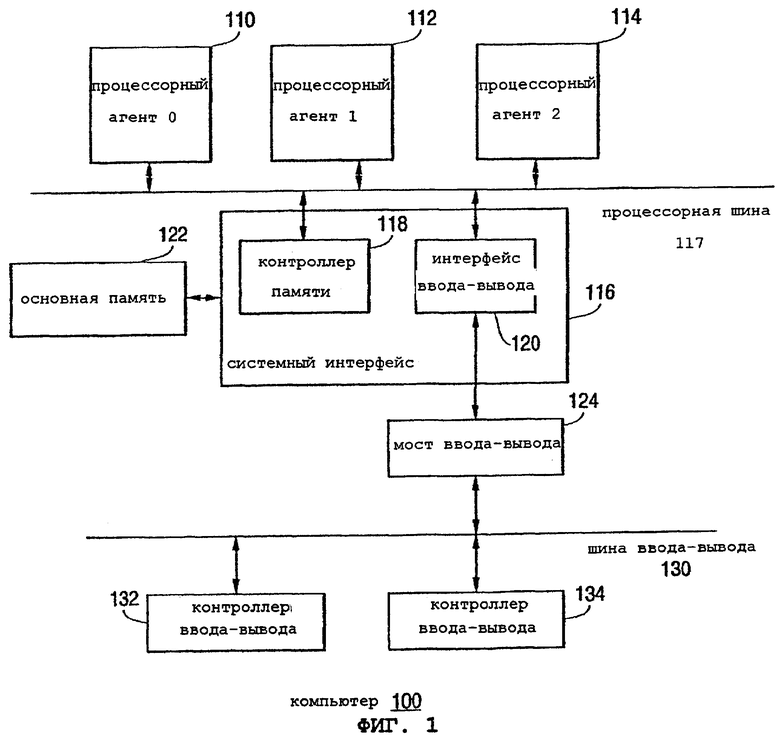

Фиг.1 является блок-схемой, иллюстрирующей компьютер согласно примерному варианту выполнения настоящего изобретения.

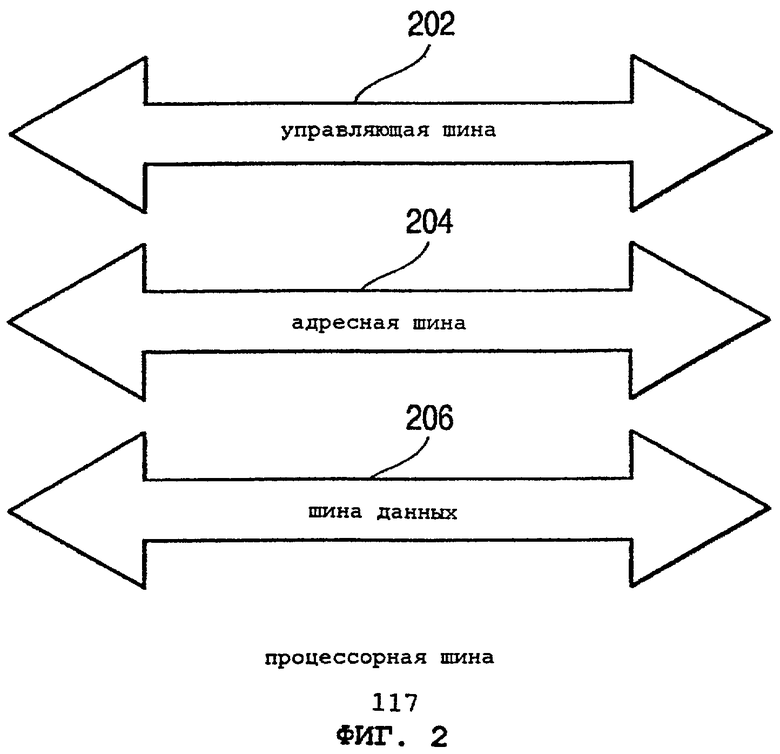

Фиг.2 представляет собой схему, иллюстрирующую процессорную шину согласно этому примерному варианту выполнения.

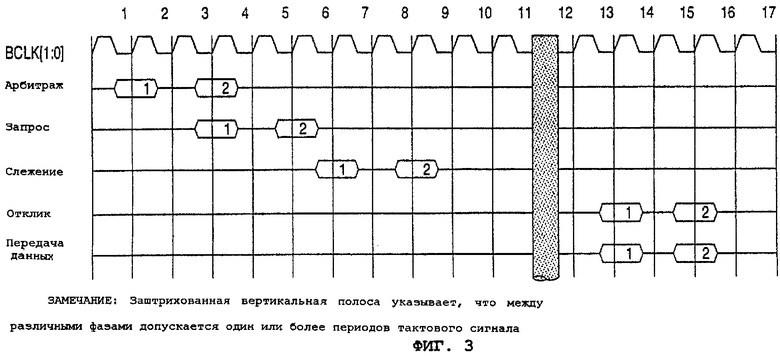

Фиг.3 является временной диаграммой, иллюстрирующей примерные фазовые соотношения шинной транзакции для двух примерных транзакций согласно варианту выполнения.

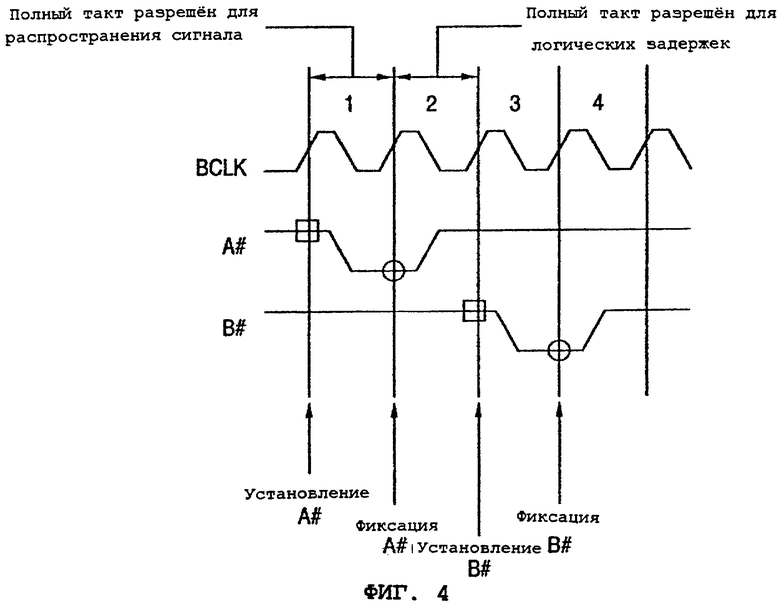

Фиг.4 является примерной временной диаграммой, иллюстрирующей примерную работу в обычном режиме тактированной сигнализации согласно варианту выполнения.

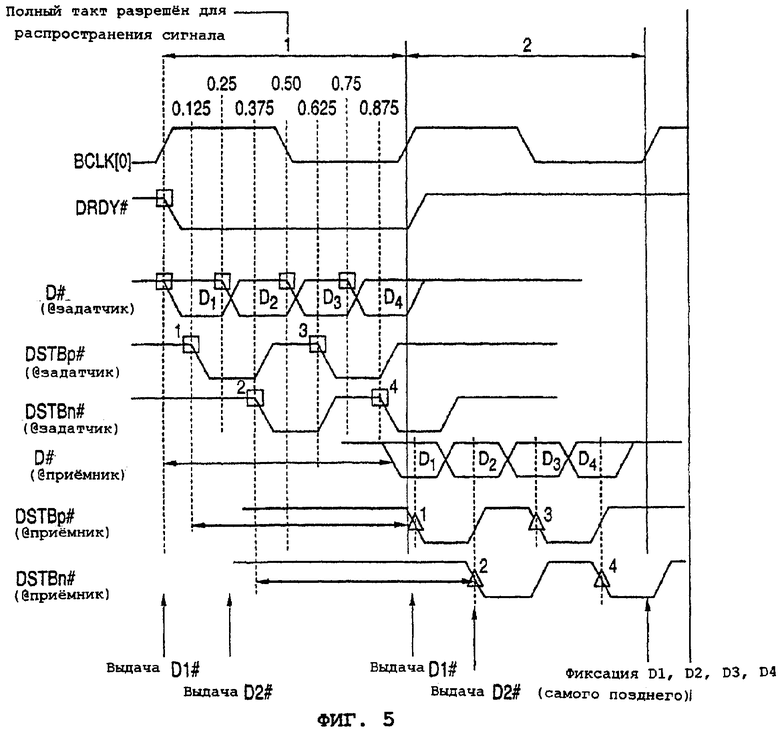

Фиг.5 представляет собой временную диаграмму, иллюстрирующую работу примерного режима сигнализации с учетверенной подкачкой.

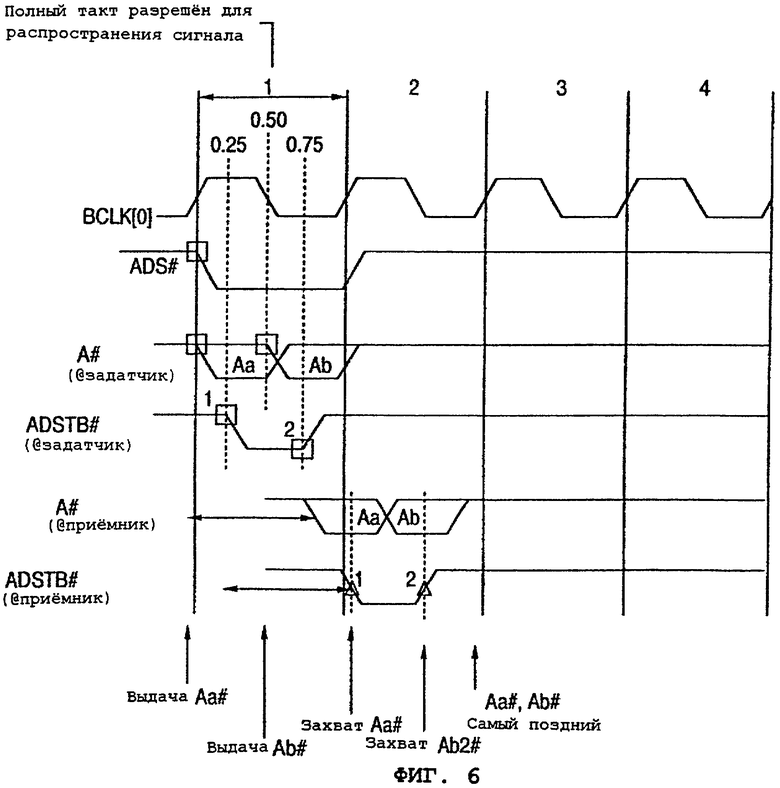

Фиг.6 представляет собой временную диаграмму, иллюстрирующую работу примерного режима сигнализации с двойной подкачкой согласно варианту выполнения.

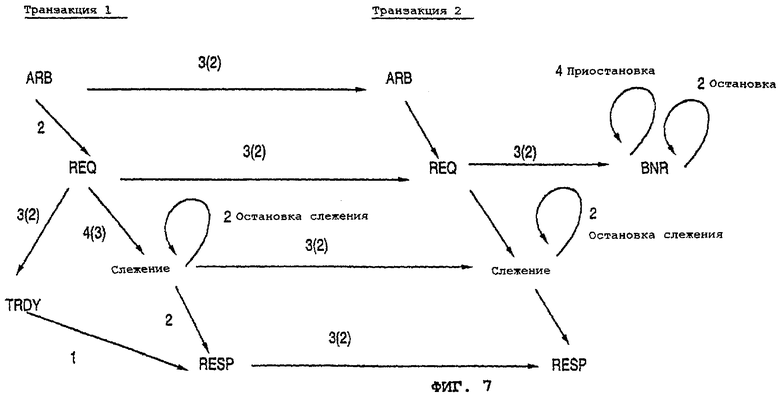

Фиг.7 является диаграммой, иллюстрирующей минимальное запаздывание или задержку между фазами транзакции.

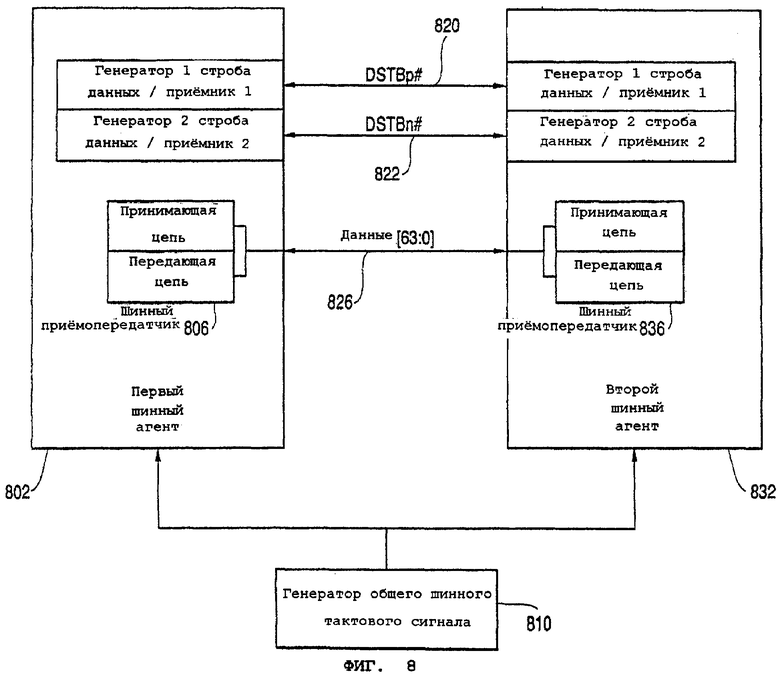

Фиг.8 является блок-схемой устройства для передачи информации между агентами согласно варианту выполнения.

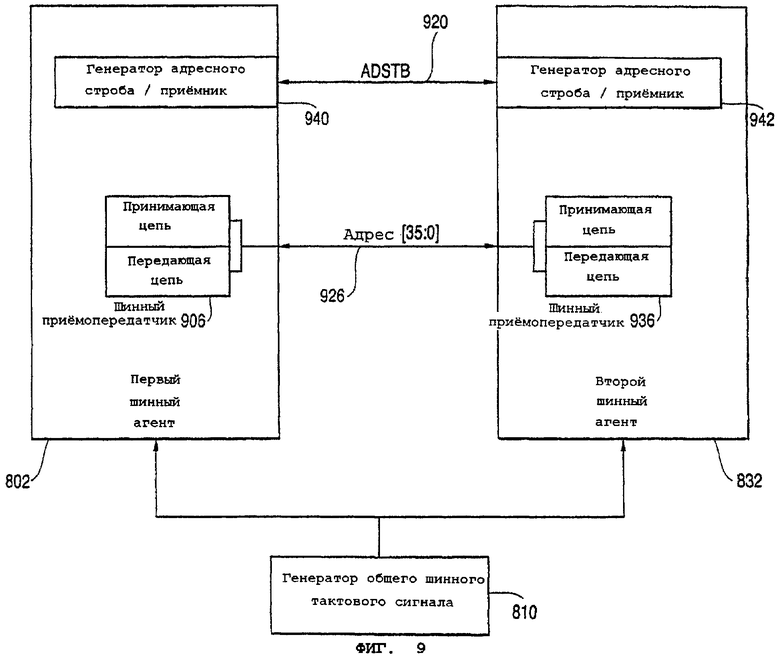

Фиг.9 является блок-схемой устройства для передачи информации между агентами согласно другому варианту выполнения.

Предпочтительный вариант осуществления изобретения

I. Введение

Согласно варианту осуществления, процессорная шина соединяется со множеством шинных агентов. Эта шина является расширяемой, потому что некоторые виды сигналов передаются с помощью обычного режима тактированной сигнализации, тогда как другие виды сигналов передаются с помощью режима сигнализации с множественной подкачкой.

В обычном режиме тактированной сигнализации сигналы (такие как управляющие сигналы) могут задаваться на шине с частотой, которая практически равна частоте обычного тактового сигнала шины. В этом режиме фронты тактового сигнала шины идентифицируют точки для осуществления выборки сигналов, выданных на эту шину.

Пропускную способность шины можно повысить в случае работы шины в режиме сигнализации с множественной подкачкой, в котором множество информационных элементов выдаются на эту шину задающим агентом (исполнительным устройством) с частотой, которая кратна частоте шинного тактового сигнала. Задающий агент также временно активирует стробирующий сигнал, чтобы идентифицировать моменты выборки для информационных элементов, заданных в этом режиме сигнализации с множественной подкачкой. Информационные элементы для запроса могут задаваться, например, с помощью режима сигнализации с двойной подкачкой, в котором два информационных элемента задаются в течение одного периода тактового сигнала шины. Элементы данных для передачи по линии данных могут задаваться, к примеру, с помощью режима сигнализации с учетверенной подкачкой, в котором четыре элемента данных задаются в течение одного периода шинного тактового сигнала. Множество стробирующих сигналов могут временно активироваться с задержкой или в шахматном порядке для снижения частоты этих стробирующих сигналов. Симметрия выборки может быть улучшена с помощью только одного вида фронтов (например, либо нарастающих фронтов, либо спадающих фронтов) в стробирующих сигналах, чтобы идентифицировать моменты выборки. Кроме того, минимальные запаздывания между фазами транзакции можно модифицировать, чтобы точнее соответствовать максимальной скорости работы шины в режиме сигнализации с множественной подкачкой.

II. Архитектура

Фиг.1 является блок-схемой, иллюстрирующей компьютер согласно примерному варианту выполнения настоящего изобретения. Этот компьютер включает в себя один или более процессоров, в том числе процессор 110, процессор 112 и процессор 114. Каждый процессор включает в себя также внутреннюю кэш-память (не показана).

Каждый процессор соединяется также с общей процессорной шиной 117 (известной также под названием главная шина или внешняя шина). Фиг.2 представляет собой схему, иллюстрирующую процессорную шину 117 согласно примерному варианту выполнения. Как показано на фиг.2, эта процессорная шина 117 включает в себя управляющую шину 202, адресную шину 294 и шину 206 данных. Согласно варианту выполнения, эта шина 206 данных включает в себя многие сигналы, в том числе 64 линии D[63:0] данных. Адресная шина 204 тоже включает в себя многие сигналы, в том числе 36 адресных линий А[35:0]. Процессорная шина 117 включает в себя шинный тактовый сигнал (ШТС) (BCLK). Этот шинный тактовый сигнал является обычным и подается ко всем агентам (исполнительным устройствам) по управляющей шине 202 процессорной шины 117. Управляющая шина 202 тоже включает в себя многие сигналы. Адресная шина 204, управляющая шина 202 и шина 206 данных являются каждая предпочтительно многоточечными двунаправленными шинами. Согласно варианту выполнения выражение "многоточечный" означает, что шины соединяются с тремя или более шинными агентами, в противоположность двухточечной шине, которая соединяется только между двумя шинными агентами.

Системный интерфейс 116 (или набор микросхем) также соединяется с процессорной шиной 117 для взаимодействия нескольких других компонентов с процессорной шиной 117. Системный интерфейс 116 включает в себя контроллер 118 памяти для взаимодействия основной подсистемы 122 памяти с процессорной шиной 117. Эта основная подсистема 122 памяти включает в себя, как правило, одну или более плат памяти и управляющую схему. Системный интерфейс 116 включает в себя также контроллер 120 ввода/вывода (I/O) для взаимодействия одного или более мостов ввода/вывода или устройств ввода/вывода с процессорной шиной 117. В этом примере компьютера, показанного на фиг.1, контроллер 120 ввода/вывода обеспечивает взаимодействие моста 124 ввода/вывода с процессорной шиной 117. Мост 124 ввода/вывода работает в качестве шинного моста для осуществления взаимодействия между системным интерфейсом 116 и шиной 130 ввода/вывода. С этой шиной 130 ввода/вывода могут соединяться один или более контроллеров ввода/вывода и устройств ввода/вывода, таких, к примеру, как контроллер 132 ввода/вывода и контроллер 134 ввода/вывода. Шина 130 ввода/вывода может быть шиной интерфейса периферийных устройств (ИПУ) (PCI) или шиной ввода/вывода иного типа.

III. Агенты

Шинные агенты (исполнительные устройства) совершают на процессорной шине 117 транзакции по передаче данных и системной информации. Шинным агентом является любое устройство, которое соединено с процессорной шиной 117. Может быть несколько классификаций шинных агентов:

1) Центральный агент: управляет сбросом, конфигурацией и инициализацией аппаратного обеспечения, специальными транзакциями и централизованными обнаружением и обработкой ошибок аппаратного обеспечения. Примером является процессор.

2) Агент ввода/вывода: взаимодействует с устройствами ввода/вывода с использованием адресов портов ввода/вывода. Может быть шинным мостом к другой шине, использующей устройства ввода/вывода, таким как мост ИПУ.

3) Агент памяти: например, контроллер 118 памяти, обеспечивает доступ к основной памяти. Конкретный шинный агент может выполнять одну или более ролей в транзакции:

1) Запрашивающий агент: шинный агент, который инициирует транзакцию.

2) Адресуемый агент: агент, к которому адресуется транзакция. Также называется целевым агентом. Транзакция памяти или ввода/вывода адресуется к агенту памяти или ввода/вывода, который распознает конкретный адрес памяти или ввода/вывода. Отличающаяся ответная транзакция адресуется к агенту, который осуществляет исходную транзакцию.

3) Следящий агент: кэширующий шину агент, который наблюдает ("следит") за шинными транзакциями для поддержания согласованной работы кэша.

4) Отвечающий агент: агент, который обеспечивает отклик на транзакцию (как правило, адресуемый агент). Согласно варианту выполнения отвечающий агент выдает отклик на управляющую шину с помощью стробов RS[2:0] отклика.

4. Операции, транзакции и фазы

Согласно варианту осуществления, активность шины на процессорной шине 117 иерархически организуется в операции, транзакции и фазы.

Операцией является шинная процедура, которая представляется неделимой (например, представляется неделимой или представляется происходящей одномоментно) для программного обеспечения, даже хотя она может и не быть неделимой на шине 117. Операция может состоять из единственной шинной транзакции, но иногда может включать в себя множество шинных транзакций или единственную транзакцию со множеством передач данных. Примеры включают в себя операцию считывания, операцию записи, фиксированную операцию считывания-модификации-записи и иные операции.

Транзакция представляет собой набор шинных действий, относящихся к единственному шинному запросу. Транзакция начинается с арбитража шины и установления сигнала ADS# (указывающего, что задается адрес) и адреса транзакции. Транзакции задаются, например, для передачи данных, для опроса об измененном состоянии кэша или для снабжения системы информацией.

Фаза использует конкретный набор сигналов для передачи информации конкретного вида. Фазы могут включать в себя: арбитраж, запрос, слежение, отклик и данные. Не все транзакции содержат все фазы, а некоторые фазы могут перекрываться. Фаза арбитража состоит в том, что шинные агенты определяют, кто будет следующим владельцем шины (агент должен владеть шиной до осуществления транзакции). Фаза запроса является фазой, в которой транзакция выдается на шину. Фаза слежения есть фаза, в которой проводится согласование кэша. Фазой отклика является фаза, в которой адресуемый или целевой агент задает на шину отклик на транзакцию. В фазе данных запрашивающий или отвечающий или следящий агент задает данные транзакций или обращается к ним.

По процессорной шине 117 передаются четыре управляющих сигнала, в том числе шинный тактовый сигнал BCLK[1:0], сигнал INIT# инициализации и сигнал RESET# сброса. Шинный тактовый сигнал BCLK[1:0] является дифференциальным шинным тактовым сигналом и может генерироваться микросхемой тактового генератора или схемой тактового генератора. Два шинных тактовых сигнала BCLK[1:0] логически идентичны и физически маршрутизируются как два отдельных сигнала, для снижения временной расфазировки. Согласно варианту выполнения все агенты инициируют свои общие тактовые выходные сигналы и запирают свои общие тактовые входы по нарастающему фронту шинного тактового сигнала. Каждый процессор выделяет свой внутренний тактовый сигнал из шинного тактового сигнала BCLK путем умножения и/или деления частоты шинного тактового сигнала на число или числа.

Согласно варианту выполнения, входной сигнал RESET# сбрасывает все шинные агенты в известные состояния и делает недействительными их внутренние кэши. Модифицированное или необновленное содержимое линии кэша теряется. После того как сигнал RESET# снимается, каждый процессор начинает обработку вектора сброса при включении питания, определенного в процессе конфигурации.

Согласно варианту выполнения, входной сигнал INIT# устанавливает в исходное состояние все процессоры без воздействия на их внутренние кэши или их регистры с плавающей запятой. Каждый процессор начинает обработку вектора сброса при включении питания, определенного в процессе компоновки.

Фиг.3 является временной диаграммой, иллюстрирующей примерные соотношения фаз шинной транзакции для двух примерных транзакций согласно варианту выполнения. Сверху показаны периоды (1, 2, 3, 4,... 17) шинного тактового сигнала (BCLK [1:0]). Прямоугольники с номером 1 указывают разные фазы для транзакции 1, тогда как прямоугольники с номером 2 указывают фазы для транзакции 2. Как видно из фиг.3, транзакции обеспечиваются в виде конвейера. К примеру, для транзакции 1 арбитраж происходит в периодах 1 и 2 шинного тактового сигнала, запрос происходит в периодах 3 и 4, слежение происходит в периодах 6 и 7, а отклик и передача данных происходят в периодах 13 и 14. Таким образом, можно видеть, что отклик и передача данных могут происходить во многих периодах шинного тактового сигнала после фазы исходного запроса. Может быть также перекрытие между фазами различных транзакций. К примеру, фаза арбитража для транзакции 2 происходит приблизительно в то же самое время, что и фаза запроса для транзакции 1.

5. Режимы сигнализации

Согласно варианту выполнения процессорная шина 117 является расширяемой и поддерживает два режима сигнализации. Первым является обычный режим тактированной сигнализации, в котором активация и выборка всех сигналов или моменты фиксации происходят с привязкой к общему шинному тактовому сигналу (BCLK#), т.е. непрерывно обеспечиваются между всеми агентами. Шинный тактовый сигнал обычно генерируется микросхемой тактового генератора или схемой тактового генератора, предусмотренной на материнской плате, и является общим для всех процессоров или агентов в компьютере. Тактирование сигнала относительно общего шинного тактового сигнала именуется режимом сигнализации с общим тактовым сигналом (1X). Согласно варианту выполнения многие управляющие сигналы, подаваемые по управляющей шине, передаются с помощью режима сигнализации с общим тактовым сигналом (1X).

Вторым режимом сигнализации является режим сигнализации с множественной подкачкой, который обеспечивает частоту передачи информации, которая кратна частоте передачи, поддерживаемой режимом сигнализации с общим тактовым сигналом. Таким образом, согласно варианту выполнения режим сигнализации с множественной подкачкой может поддерживать передачу информации по процессорной шине 117 между агентами с частотой, которая кратна частоте общего (т.е. системного) шинного тактового сигнала. Например, режим сигнализации с множественной подкачкой может обеспечить, скажем, режим сигнализации с двойной подкачкой, который позволяет передавать информацию (к примеру, данные, адреса или иную информацию) с удвоенной (2Х) частотой относительно частоты общего тактового сигнала, либо может обеспечить режим сигнализации с учетверенной подкачкой, который обеспечивает передачу информации с учетверенной (4Х) частотой шинного тактового сигнала. Чтобы облегчить передачу информации на таких частотах, которые больше, чем у общего шинного тактового сигнала, задающий агент также формирует или обеспечивает сопровождающий сигнал, известный как тактирующий "строб", используемый приемником для захвата или фиксации информации с множественной подкачкой.

Выражение "установленный" означает, что сигнал переводится в свой активный уровень (т.е. переводится в ноль для активного низкоуровневого сигнала), а выражение "снятый" означает, что сигнал переводится в свой неактивный уровень. Квадратные, круглые и треугольные символы используются в некоторых временных диаграммах, описанных ниже, чтобы указать, когда конкретные сигналы задаются или выбираются. Квадрат указывает, что сигнал задается (устанавливается, инициируется) в этом периоде тактового сигнала. Круг указывает, что сигнал выбирается (отслеживается, фиксируется) в этом периоде тактового сигнала. Круг обычно используется, чтобы показать момент выборки на основании нарастающего (или спадающего) фронта шинного тактового сигнала (BCLK) в режиме сигнализации с общим тактовым сигналом (1X). Треугольник указывает, что сигнал выбирается или захватывается на основании нарастающего или спадающего фронта сопровождающего сигнала, названного "строб". Этот строб предпочтительно может устанавливаться или активироваться только в ходе передачи информации (к примеру, данных, адресов, иной информации) по процессорной шине как правило в режиме с множественной подкачкой.

А. Режим сигнализации с общим тактовым сигналом

Согласно варианту осуществления режима сигнализации с общим тактовым сигналом (1X) всем агентам на процессорной шине 117 требуется задавать свои активные выходные сигналы и выбирать требуемые входные сигналы. Согласно варианту выполнения каждый входной сигнал должен выбираться во время допустимого интервала выборки по нарастающему фронту шинного тактового сигнала, а его следствие или результат должен выдаваться на шину 117 не раньше, чем по следующему нарастающему фронту шинного тактового сигнала. Этот примерный подход обеспечивает один полный период шинного тактового сигнала для осуществления межкомпонентной связи (передача и распространение сигналов) и по меньшей мере один полный период шинного тактового сигнала в приемнике, чтобы интерпретировать сигналы и вычислить и вывести ответный сигнал. В результате после того, как агент выдает данные на процессорную шину в одном или более периодах шинного тактового сигнала, имеется пауза в один период шинного тактового сигнала (например, "мертвый" период или неактивный период) перед тем, как другой агент может управлять процессорной шиной 117.

Фиг.4 представляет собой примерную временную диаграмму, иллюстрирующую примерную работу в режиме сигнализации с общим тактовым сигналом (1X) согласно варианту выполнения. Сигналы показаны по мере их появления на процессорной шине 117. Показаны четыре периода шинного тактового сигнала (BCLK). Показаны также два дополнительных примерных сигнала, включающие А# и В#, которые могут быть сигналами любого вида. К примеру. A# может быть первым управляющим сигналом от первого агента, тогда как B# может быть вторым сигналом от второго агента. Первый и второй управляющие сигналы могут быть обеспечены, например, в качестве части процедуры установления связи или шинного протокола.

Как показано на фиг.4, сигнал А# задается (или устанавливается) по нарастающему фронту периода 1 тактового сигнала (как показано квадратом в А#) и фиксируется в приемнике по нарастающему фронту в начале периода 2 шинного тактового сигнала (как показано кружком для A#). Таким образом, период 1 тактового сигнала обеспечивается для распространения сигнала. Хотя А# задается в начале периода 1, он не наблюдается на шине до начала периода 2. Затем имеется пауза, или неактивный период тактового сигнала (во время периода 2 шинного тактового сигнала для логических задержек и для того, чтобы приемник интерпретировал эти сигналы). Приемник затем задает или устанавливает сигнал B# в начале периода 3 шинного тактового сигнала (как показано квадратом для В#), который наблюдается или захватывается другими агентами в начале периода 4 (как показано кружком для B#).

Согласно варианту выполнения процессор включает в себя 64-байтовую строку кэш-памяти (вместо 32-байтовой строки кэш-памяти, использованной некоторыми процессорами Pentium).

Поэтому, если данные передавались с использованием режима сигнализации с общим тактовым сигналом (1X) и 64 линий шины данных, 64 байта (одна строка кэш-памяти) может выдаваться или передаваться в 8 периодах шинного тактового сигнала. Однако во многих применениях может быть желательно обеспечить более быструю скорость переноса данных или более широкую полосу пропускания.

Б. Режимы сигнализации с множественной подкачкой

Во многих случаях длина процессорной шины 117, электрические ограничения (в том числе запаздывание на распространение сигнала по шине) могут препятствовать увеличению частоты процессорной шины. Поэтому, согласно варианту выполнения, протокол сигнализации с множественной подкачкой, а не повышение частоты тактового сигнала процессорной шины, увеличивает скорость передачи данных (по сравнению с режимом сигнализации с общим тактовым сигналом) путем оперирования с подходящей группой шинных сигналов (например, адресной шины или шины данных) на кратной частоте шинного тактового сигнала (BCLK).

1. Пример режима сигнализации с учетверенной подкачкой

В режиме сигнализации с учетверенной подкачкой подходящая группа шинных сигналов обрабатывается на учетверенной (4Х) частоте шинного тактового сигнала (BCLK). Иными словами, в режиме сигнализации с учетверенной подкачкой четыре элемента информации выдаются на процессорную шину 117 в одном периоде шинного тактового сигнала (это время, которое заняло бы задание одного элемента информации в режиме сигнализации с общим тактовым сигналом 1X).

Фиг.5 представляет собой временную диаграмму, иллюстрирующую работу в режиме сигнализации с учетверенной подкачкой согласно варианту выполнения. Хотя этот режим сигнализации с учетверенной подкачкой может использоваться для сигналов любого вида, протокол сигнализации с учетверенной подкачкой используется, согласно примерному варианту выполнения, для передачи данных. На фиг.5 показаны два периода шинного тактового сигнала и часть третьего периода шинного тактового сигнала. В наихудшем случае "пролетное" время (или время распространения сигнала) по процессорной шине 117 таково, что второй информационный элемент может задаваться на процессорную шину 117 в задатчике (т.е. в агенте, выдающем информацию на процессорную шину) до того, как первый информационный элемент зафиксирован в приемнике (принимающих агентах).

Согласно варианту выполнения задатчик (или задающий агент) посылает или задает новый информационный элемент по нарастающему фронту и в моментах времени 25%, 50% и 75% периода шинного тактового сигнала (BCLK).

Приемник также посылает сопровождающий тактирующий сигнал, известный как стробирующий сигнал данных, который указывает, когда должен приемник выбирать или захватывать данные. Этот стробирующий сигнал предпочтительно посылается или задается (активируется), только когда информация посылается с помощью режима сигнализации с множественной подкачкой.

Ввиду того, что данные и стробирующие сигналы генерируются одним и тем же задатчиком или источником, эти данные и стробы будут иметь один и тот же маршрут. В результате стробирующий сигнал и сигналы данных должны иметь один и тот же маршрут, а потому и одинаковую задержку. Поэтому преимущество, достигаемое задатчиком или источником, посылающим как строб, так и данные, состоит в том, что сигналы данных и стробирующий сигнал поступят синфазно (или синхронно) к каждому агенту на шине 117. Таким образом, этот способ посылки задатчиком как данных, так и тактирующего стробирующего сигнала можно назвать синхронной передачей от источника. В режиме сигнализации с учетверенной подкачкой должно быть четыре строба данных (например, четыре тактирующих стробирующих фронта), причем каждый идентифицирует выборку информации (или момент захвата) в каждом периоде шинного тактового сигнала, по одному для каждого из четырех элементов. К сожалению, могут возникнуть трудности при генерировании стробирующего сигнала на относительно высоких частотах. При высоких частотах тактового сигнала разность между скоростью нарастающего фронта и скоростью спадающего фронта может быть значительной. Кроме того, может быть затруднительно обеспечить тактовый сигнал или стробирующий сигнал с 50%-ной скважностью. В результате на некоторых тактовых частотах ни нарастающий фронт, ни спадающий фронт стробирующего сигнала не должны использоваться для идентификации моментов выборки, т.к. это может создать асимметрию или ввести некоторую неопределенность тактирования. Наоборот, может быть выгодно использовать только один из двух фронтов строба (т.е. использовать только нарастающие фронты или только спадающие фронты стробирующих сигналов для осуществления выборки или захвата данных с учетверенной подкачкой), чтобы получить более симметричные или однородные стробирующие интервалы тактового сигнала или выборки.

Если используется только один из фронтов строба, это, как правило, потребует тактовую частоту, которая кратна частоте шинного тактового сигнала. В случае данных с учетверенной подкачкой (четыре элемента данных на период шинного тактового сигнала) частота стробирующего сигнала должна быть в четыре раза больше (4Х) частоты шинного тактового сигнала, если для тактирования используется только один фронт.

К сожалению, если частота тактового сигнала процессора составляет 100 МГц (к примеру), это потребует частоту стробирующего сигнала, которая равна 400 МГц (в этом примере). Однако частота стробирующего сигнала, которая в четыре раза больше частоты шинного тактового сигнала, может столкнуться с задержками, которые отличаются от задержек передаваемых данных или информации, что может повлиять на согласование данных и строба в приемнике. Такое рассогласование между переданным стробирующим сигналом и переданными данными может заставить приемник захватывать искаженные или неверные данные. Кроме того, на таких высоких частотах (например, 400 МГц) ослабление сигнала может быть значительно выше.

Поэтому, согласно варианту выполнения, для того, чтобы обеспечить четыре строба на период шинного тактового сигнала без использования стробирующей частоты, которая в четыре раза (4Х) выше частоты шинного тактового сигнала, используется множество стробирующих данные сигналов. Согласно варианту выполнения два стробирующих данные сигнала (DSTBp# и DSTBn#) подаются каждый с удвоенной частотой шинного тактового сигнала. Таким образом, если частота шинного тактового сигнала составляет 100 МГц, эти два стробирующих данные сигнала будут иметь каждый частоту 200 МГц при активировании или генерировании эадатчиком (или задающим агентом). Альтернативно, можно использовать четыре стробирующих данные сигнала (каждый с той же самой частотой, что и шинный тактовый сигнал при активировании), причем каждый обеспечивает один строб или спадающий фронт на период шинного тактового сигнала.

На временной диаграмме фиг.5 задатчик посылает или задает новый элемент информации или данных по нарастающему фронту и в моменты 25%, 50% и 75% периода 1 шинного тактового сигнала. Элементы данных помечены D1, D2, D3 и D4 для четырех элементов данных в этом примере. Этот вариант осуществления также использует два стробирующих данные сигнала, включающие DSTBp# и DSTBn#. Согласно варианту выполнения эти два стробирующих данные сигнала генерируются в противофазе друг с другом (или в шахматном либо сдвинутом порядке). Это дает возможность одному из этих стробирующих сигналов идентифицировать моменты выборки для нечетных элементов данных (например, D1, D3, D5, ...), а другой стробирующий сигнал использовать для четных элементов данных (например, D2, D4, D6, ...).

Хотя в примере на фиг.5 показаны только два стробирующих сигнала, для идентификации моментов выборки данных при синхронной передаче от источника можно использовать любое число стробирующих сигналов. Как отмечено выше, может быть особенно выгодно предусмотреть множество стробирующих сигналов так, чтобы только один из двух фронтов этих стробирующих сигналов мог использоваться для идентификации моментов выборки (или стробов) при снижении частоты этих стробирующих сигналов. К примеру, если использовался бы протокол шестерной (6Х) подкачки (вместо учетверенной подкачки), то можно было бы использовать три стробирующих сигнала, где все три стробирующих сигнала могли бы иметь одинаковый сдвиг или располагаться в шахматном порядке так, что строб 1 мог бы использоваться для элементов данных D1 и D4, строб 2 - для элементов данных D2 и D5, а строб 3 - для элементов данных D3 и D6, и т.д.

Согласно варианту выполнения, только один из двух фронтов этих стробирующих сигналов используется для идентификации или синхронизации моментов выборки данных. В этом конкретном варианте выполнения для идентификации моментов для выборки информации или данных используются только спадающие фронты двух стробирующих данные сигналов. Эти стробы данных (или спадающие фронты стробирующих данные сигналов) расположены посередине в каждом из четырех элементов информации или данных. Таким образом, четыре спадающих фронта (или строба) в стробирующих данные сигналах будут приходиться на моменты 12,5%, 37,5%, 62,5% и 87,5% периода шинного тактового сигнала (BCLK). Поэтому два стробирующих сигнала обеспечивают одинаково разнесенные стробы или падающие фронты.

Как показано на фиг.5, сигнал DRDY# выдается на шину 117 в начале периода 1 шинного тактового сигнала (как показано квадратом для DRDY#). DRDY# указывает, что на процессорную шину 117 выданы достоверные данные и они должны быть выбраны или захвачены. Первый элемент данных (D1) выдается задатчиком на процессорную шину 117 по нарастающему фронту периода 1 шинного тактового сигнала (как показано первым прямоугольником для сигнала D#(@задатчик)). Затем первый стробирующий данные сигнал (DSTBp#) активируется задатчиком в точке 12,5% первого периода шинного тактового сигнала, как показано первым квадратом в сигнале DSTBp#(@задатчик). Таким образом, строб (или нарастающий фронт) для первого элемента данных (D1) находится посередине в первом элементе данных. После того как стробирующий сигнал активирован или включен, он обычно остается активированным, пока данные выдаются на шину.

Кроме того, второй элемент данных выдается задатчиком в точке 25% периода 1 шинного тактового сигнала, как показано вторым прямоугольником для сигнала D#(@задатчик). Второй стробирующий данные сигнал (DSTBn#) активируется в точке 37,5% периода 1 шинного тактового сигнала и обеспечивает спадающий фронт (или строб), который находится посередине во втором элементе данных (D2).

Подобным же образом третий и четвертый элементы данных (D3 и D4 соответственно) задаются в точках 50% и 75% периода 1 шинного тактового сигнала. Соответствующие стробы данных (спадающие фронты стробирующих данные сигналов) задаются или обеспечиваются эадатчиком в точке 62,5% (стробирующим сигналом DSTBp#) и в точке 87,5% (стробирующим сигналом DSTBn#). Поскольку эти стробирующие данные сигналы подаются с частотой, которая вдвое (2Х) выше частоты шинного тактового сигнала, каждый стробирующий данные сигнал обеспечит строб или спадающий фронт каждые полпериода шинного тактового сигнала. Таким образом, стробирующий сигнал DSTBp# обеспечивает спадающие фронты или стробы в точках 12,5% и 62,5% периода шинного тактового сигнала, тогда как стробирующий сигнал DSTBn# обеспечивает спадающие фронты или стробы в точках 37,5% и 87,5% периода шинного тактового сигнала. Таким образом, можно видеть, что два стробирующих данные сигнала (DSTBp# и DSTBn#) расположены в шахматном порядке или в противофазе друг с другом. Это позволяет попеременно возникающим стробирующим сигналам обеспечивать спадающий фронт (или строб) каждые четверть периода шинного тактового сигнала (между обоими стробирующими данные сигналами). Это обеспечивает четыре строба или спадающих фронта на период шинного тактового сигнала для идентификации моментов выборки или захвата для четырех элементов данных за период шинного тактового сигнала с уменьшением частоты каждого строба. Кроме того, тактирование и схема упрощаются, потому что в качестве строба в каждом стробирующем данные сигнале используется один и тот же фронт.

Согласно варианту осуществления, чтобы обеспечить правильную работу, запаздывание при передаче информации от задающего агента к любому приемнику должно быть меньше или равно одному шинному такту минус время установки фиксации входного сигнала. Этим устраняется состязание на линиях данных для следующих друг за другом фаз данных, если приемник становится владельцем шины во время следующей фазы.

Фиг.5 показывает также захват данных приемником. После того, как сигналы (данные и стробы данных) выдаются задатчиком, эти сигналы распространяются по процессорной шине 117 и достигают цели или приемника. Первый элемент данных принимается приемником, как показано сигналом D#(@приемник). Этот первый элемент данных (D1) выбирается или захватывается по первому стробу, который представляет собой первый спадающий фронт сигнала DSTBp#(@приемник). Первый треугольник для DSTBp#(@приемник) идентифицирует строб или момент выборки или захвата первого элемента данных, а второй треугольник для DSTBp#(@приемник) идентифицирует момент или строб для выборки третьего элемента данных в приемнике. Подобным же образом два треугольника для второго стробирующего данные сигнала (DSTBn#(@приемник)) идентифицируют моменты выборки или захвата приемником второго и четвертого элементов данных (D2, D4).

Как показано на фиг.5, первый элемент данных D1 может выбираться или захватываться (стробироваться) в приемник после нарастающего фронта в начале периода 2 и не раньше, чем в точке 12,5% тактового периода 2 (следующего тактового периода). (Используемые здесь выражения "захват", "выборка" и "фиксация" означают приблизительно одно и то же). Однако данные для всех элементов данных не фиксируются в приемнике до прихода нарастающего фронта периода 3 шинного тактового сигнала. Таким образом, хотя элемент данных D1 принимается и захватывается вблизи начала периода 2 шинного тактового сигнала, все данные не становятся доступными для приемника до начала периода 3 шинного тактового сигнала. Принимающий агент предпочтительно включает в себя буфер FIFO (первым вошел - первым вышел), которого достаточно для хранения восьми элементов данных. FIFO для восьми элементов данных достаточен для хранения четырех элементов одной передачи данных и следующих четырех элементов для следующей передачи. Это позволяет принимать и захватывать четыре новых элемента данных в то время, как предыдущие четыре элемента данных выталкиваются или выводятся из FIFO в приемник. Чистый эффект составляет четырехкратную полосу частот в режиме сигнализации с общим тактовым сигналом с добавлением запаздывания для первой группы сигналов, фиксируемой внутри приемника или устройства.

Вдобавок, согласно варианту выполнения, множество линий используется для передачи множества копий каждого из двух стробирующих данные сигналов (DSTBp# и DSTBn#). Согласно варианту выполнения, имеется четыре сигнала DSTBn# и четыре сигнала DSTBp#, как представлено в нижеследующей таблице.

Пример варианта осуществления охвата стробов данных

Четыре сигнала DSTBp# логически идентичны, как и четыре сигнала DSTBn#, но каждый из стробирующих данные сигналов физически маршрутизируется с поднабором запрошенных сигналов (т.е. поднабор линий данных), чтобы уменьшить искажение или несогласование тактирования между сигналами данных и сигналами стробов данных.

Фиг.8 является блок-схемой устройства для передачи информации между агентами согласно варианту выполнения. Первый шинный агент 802 соединяется со вторым шинным агентом 832. Первый шинный агент 802 включает в себя генератор 1 строба данных / приемник 1 для генерирования и приема первого стробирующего данные сигнала (например, DSTBp#) по первой двунаправленной линии 820 стробирующего данные сигнала, и генератор 2 строба данных / приемник 2 для генерирования и приема второго стробирующего данные сигнала (например, DSTBn#) по второй двунаправленной линии 822 стробирующего данные сигнала. Шинный агент 802 включает в себя также шинный приемопередатчик 806, содержащий передающую цепь для передачи или выдачи сигналов данных на шину данных или линии 826 сигнала данных и приемную цепь для приема сигналов данных по линиям 826 сигнала данных. Второй шинный агент 832 аналогично включает в себя генератор 1 строба данных и генератор 2 строба данных для генерирования двух сигналов строба данных на линии 820 и 822 стробирующего данные сигнала, соответственно. Генератор 810 общего (или системного) шинного тактового сигнала обеспечивает общий или системный тактовый сигнал для шинных агентов 802 и 832.

2. Согласование скорости адресной шины с шиной данных

Согласно варианту выполнения, размер строки кэша увеличен до 64 байтов (размер строки кэша в некоторых процессорах Pentium составляет 32 байта). Тем самым, используя протокол сигнализации с учетверенной подкачкой и разрядности шины данных с 64 линиями данных, строка кэша (или 64 байта) могут передаваться в двух периодах шинного тактового сигнала:

64 байта=(2 периода)×(4 подкачки/период)(8 байтов за подкачку).

Однако в некоторых процессорах Pentium запрос (включая адрес) передается в трех периодах шинного тактового сигнала. Эти три периода шинного тактового сигнала для фазы запроса для некоторых процессоров Pentium включали в себя следующее:

Период 1 - подфаза а - адрес (подаваемый по адресной шине) и тип запроса (например, чтение, запись).

Период 2 - подфаза b - вспомогательные данные для запроса, в том числе разрешения байтов, длина и т.п. (подаваемые по адресным линиям или адресной шине).

Период 3 - пассивный период или период обработки, который позволяет сигналам на шине проходить, чтобы дать возможность другому агенту управлять шиной.

Таким образом, согласно варианту осуществления, строка кэша может передаваться по шине данных в двух периодах шинного тактового сигнала. Однако в некоторых процессорах Pentium тактирование адреса и запроса требует три периода шинного тактового сигнала для передачи запроса. Тем самым, в некоторых процессорах Pentium тактирование адресной шины или полоса частот не согласуются со скоростью усовершенствованной шины данных с учетверенной подкачкой, как она описана в вышеприведенном варианте выполнения (см. фиг.5). Одним из более дефицитных и ценных ресурсов является разрядность шины данных и полоса частот шины данных. Таким образом, согласно варианту выполнения, может быть предпочтительно для полосы частот шины данных сузить или ограничить процессорную шину, но не полосу частот адресной шины. Поэтому, чтобы предохранить адресную шину от замедления или сужения процессорной шины, желательно подстраивать тактирование адреса и запроса на адресной шине, чтобы оно по меньшей мере соответствовало полосе частот или скорости шины данных (в этом примере для передачи одной строки кэша на шине данных).

Поэтому, согласно варианту выполнения, тактирование и скорость фазы запроса, подаваемой по адресной шине, подстраивалась для согласования с полной скоростью шины данных. Желательно сохранять пассивный период или период обработки. Тем самым, согласно варианту выполнения, адресная шина подкачивалась дважды, чтобы обеспечить два информационных элемента (подфаза а и подфаза b запроса) в одном периоде шинного тактового сигнала.

3. Пример режима сигнализации с двойной подкачкой

В целом, согласно варианту выполнения, режим сигнализации с двойной подкачкой оперирует с соответствующей группой шинной сигнализации на удвоенной (2Х) частоте шинного тактового сигнала (BCLK). Фиг.6 представляет собой временную диаграмму, иллюстрирующую работу в примере режима сигнализации с двойной подкачкой согласно варианту выполнения. Хотя двойная подкачка может применяться к любым сигналам, в этом варианте выполнения двойная подкачка применяется к адресной шине.

На фиг.6 снижается уровень сигнала ADS# в начале фазы запроса. В режиме сигнализации с двойной подкачкой два элемента информации выдаются на шину за то время, которое занимает выдача одного элемента с помощью режима сигнализации с общим тактовым сигналом (т.е. в течение одного периода шинного тактового сигнала). Вследствие времени "пролета" (или времени распространения сигнала на процессорной шине 117) вторая группа сигналов или информационный элемент могут задаваться в задатчике перед тем, как первый элемент фиксируется в приемнике(-ax). Согласно варианту осуществления, задатчик посылает новый информационный элемент по нарастающему фронту и в точке 50% периода шинного тактового сигнала.

Как показано на фиг.6, подфаза а запроса (Аа), обеспечивающая адрес транзакции, посылается в первой половине периода 1 шинного тактового сигнала, начинаясь на спадающем фронте в начале периода 1 шинного тактового сигнала. Подфаза b запроса (Ab), обеспечивающая некоторые вспомогательные данные для транзакции, посылается во второй половине периода 1 шинного тактового сигнала, начинаясь в точке 50% периода 1 шинного тактового сигнала. Эти два информационных элемента показаны на фиг.6 как два прямоугольника для Аа и АВ для линий А# (@задатчик). (Аа указывает на подфазу а запроса, поданную по линиям Адрес, тогда как Ab указывает на подфазу b запроса, поданную по линиям Адрес). Таким образом, адресная шина имеет двойную подкачку, потому что два информационных элемента (Аа и Ab) передаются или посылаются в течение одного периода шинного тактового сигнала.

Кроме того, поскольку информация для запроса будет посылаться с помощью режима сигнализации с двойной подкачкой (два информационных элемента за период шинного тактового сигнала), информация предпочтительно посылается в виде синхронной передачи с источником. Тем самым, в дополнение к двум информационным элементам, задатчик также задает или активирует стробирующий адрес сигнал, чтобы обеспечить два адресных строба за период шинного тактового сигнала (когда он активирован). Эти адресные стробы обеспечивают или идентифицируют моменты выборки двух информационных элементов (Аа и Ab), посылаемых по адресной шине.

Согласно варианту выполнения, стробирующий адрес сигнал (ADSTB#) используется с той же частотой, что и шинный тактовый сигнал (BCLK). Однако, чтобы обеспечить два строба в течение одного периода шинного тактового сигнала, и спадающие фронты, и нарастающие фронты стробирующего адрес сигнала будут использоваться в качестве стробов или чтобы идентифицировать моменты выборки для двух информационных элементов, поданных по адресной шине. Как показано на фиг.6, задатчик активирует стробирующий адрес сигнал (ADSTB#) в точке 25% периода 1 шинного тактового сигнала, которая соответствует середине информационного элемента 1 (Аа). Согласно варианту выполнения, адресный строб для первого информационного элемента (Аа или подфаза а запроса) обеспечивается по спадающему фронту сигнала ADSTB# (задается в точке 25% периода 1 шинного тактового сигнала), тогда как адресный строб для второго информационного элемента (Ab или подфаза b запроса) обеспечивается по нарастающему фронту сигнала ADSTB# (задается в точке 75% периода 1 шинного тактового сигнала).

Даже хотя адресный строб имеет такую же частоту, что и шинный тактовый сигнал, этот шинный тактовый сигнал не должен использоваться в качестве стробирующего сигнала для информационных элементов, потому что шинный тактовый сигнал не обеспечивает нарастающего и спадающего фронтов в подходящие моменты времени. Кроме того, шинный тактовый сигнал активируется всегда (в противоположность стробирующему сигналу, который активируется только во время синхронной с источником передачи). Стробирующий адрес сигнал используется, чтобы обеспечить стробы или моменты выборки для двух информационных элементов, потому что стробирующий адрес сигнал можно активировать (включать) и деактивировать (выключать) независимо от состояния или фазы шинного тактового сигнала. Если строб задается от того же самого источника, что и информация, задержка в стробе совпадает с задержкой в информации, а следовательно больше, чем одному байту разрешается находиться на линии в одно и то же время.

Информационные элементы (Аа и Ab) и стробирующий адрес сигнал распространяются вдоль процессорной шины 117 и достигают приемника в начале периода 2 шинного тактового сигнала. Как показано на фиг.6, первый информационный элемент (Аа) захватывается или выбирается по спадающему фронту сигнала (ADSTB#(@приемник), а второй информационный элемент захватывается или выбирается по нарастающему фронту сигнала (ADSTB#(@приемник), как показано двумя треугольниками на сигнале (ADSTB#(@приемник). Таким образом, можно видеть, что приемник захватывает данные или информацию детерминистически на основании указания от задатчика, когда данные доступны (и должны быть захвачены).

Согласно варианту осуществления, запаздывание передачи данных от задающего агента к любому приемнику должно быть меньше и равно одному периоду шинного тактового сигнала минус время установки фиксации входного сигнала. Это позволит избежать состязания на адресных линиях (или адресной шине) и других линиях для второй или последующей фазы, если приемник становится владельцем следующей фазы. Чистый эффект заключается в двойной полосе частот по сравнению с режимом сигнализации с общим тактовым сигналом с добавлением запаздывания для первой группы сигналов, фиксируемой внутри приемника или устройства.

Согласно варианту выполнения, приемник включает в себя четырехэлементный буфер FIFO для хранения четырех информационных элементов, переданных по адресной шине во время фазы запроса. Это позволяет принимать и захватывать в FIFO элементы из подфазы а и подфазы b одного запроса, и в то же самое время позволяет считывать из FIFO и фиксировать в приемнике элементы из подфазы а и подфазы b предыдущего запроса.

Поэтому, согласно варианту выполнения, единственный стробирующий адрес сигнал используется на той же самой частоте, что и у шинного тактового сигнала, чтобы обеспечить стробы для двух информационных элементов, передаваемых по адресной шине. На этих частотах для адресного строба (та же самая частота, что и для шинного тактового сигнала) ослабление сигналов не представляет собой проблемы. Кроме того, любая асимметрия в скважности стробов не создает проблем, потому что только два информационных элемента передаются за период шинного тактового сигнала. Следовательно, для стробирующего адрес сигнала можно использовать единственный адресный строб на той же частоте, что и для шинного тактового сигнала, в котором в качестве стробов используются как спадающие, так и нарастающие фронты.

Альтернативно, можно использовать множество (или два) стробирующих адрес сигналов с использованием только одного из фронтов каждого стробирующего адрес сигнала в качестве строба. К примеру, можно было бы использовать первый стробирующий адрес сигнал, активированный (имеющий спадающий фронт) в точке 25% периода 1, и второй стробирующий адрес сигнал, активированный (имеющий спадающий фронт) в точке 75% периода 1. Тем самым моменты активации двух стробирующих адрес сигналов имели бы сдвиг или шахматный порядок. Поскольку в течение одного периода шинного тактового сигнала выдаются только два элемента, частота стробирующих адрес сигналов могла бы быть выбрана такой же, что и выбранная частота шинного тактового сигнала, или другая частота.

Фиг.9 является блок-схемой устройства передачи информации между агентами согласно другому варианту выполнения. Первый шинный агент 802 соединяется со вторым шинным агентом 832. Первый шинный агент 802 включает в себя генератор 940 адресного строба для генерирования стробирующего адрес сигнала (например, ADSTB#) на двунаправленную линию 920 стробирующего адрес сигнала. Шинный агент 802 включает в себя также шинный приемопередатчик 906, содержащий передающую схему для передачи или выдачи адреса и других сигналов на адресную шину или линии 926 адресных сигналов и приемную схему для приема сигналов, принятых по линиям 926 адресных сигналов. Второй шинный агент 832 подобным же образом включает в себя генератор 942 адресного строба для генерирования стробирующего адрес сигнала на двунаправленную линию 920 стробирующего адрес сигнала. Второй шинный агент 832 включает в себя также шинный приемопередатчик 936, содержащий приемную схему и передающую схему для передачи сигналов и приема сигналов, соответственно, по линиям 926 адресных сигналов.

Как описано выше, передача данных одной строки кэша может осуществляться в двух периодах шинного тактового сигнала с помощью режима сигнализации с учетверенной подкачкой, а запрос адреса может передаваться в двух периодах шинного тактового сигнала с помощью режима с двойной подкачкой. Тем самым как адресная шина, так и шина данных имеют одинаковую пиковую пропускную способность, что обеспечивает сбалансированную процессорную шину. Если не указано обратное, большинство, если не все из оставшихся сигналов передаются с помощью режима сигнализации с общим тактовым сигналом.

VII. Перенастройка шинного протокола на новую частоту в тракте из двух периодов

Как описано выше, процессорная шина обеспечивает увеличенную полосу частот запроса и данных путем использования протоколов сигнализации с множественной подкачкой. Это увеличение полосы частот запроса (на адресной шине) и полосы частот данных (на шине данных) осуществляется без увеличения разрядности шины данных (64 линии), без использования дорогостоящей топологии тактирования или маршрутизации и с сохранением того же самого вида шинного протокола, что и используемый в некоторых из процессоров Pentium.

В некоторых процессорах Pentium режим сигнализации с общим тактовым сигналом использовался для передачи восьми байтов данных за период шинного тактового сигнала с помощью 64 линий данных, что позволяло передавать строку кэша из 32 байтов за четыре периода шинного тактового сигнала. Согласно варианту выполнения изобретения, эта строка кэша была увеличена до 64 линий, и режим сигнализации с учетверенной подкачкой (передающий 32 байта на период шинного тактового сигнала) может использоваться для посылки строки кэша из 64 байтов в двух периодах шинного тактового сигнала. Кроме того, в некоторых процессорах Pentium запрос передается в трех периодах шинного тактового сигнала, включая подфазу а в периоде 1 шинного тактового сигнала, подфазу b в периоде 2 и период обработки (или пассивный период) для периода 3. Согласно варианту выполнения изобретения, режим сигнализации с двойной подкачкой используется на адресной шине для передачи обеих подфаз а и b запроса в единственном периоде шинного тактового сигнала. Это снижает длительность фазы запроса до двух периодов шинного тактового сигнала, что согласуется с длительностью передачи строки кэша (также два периода шинного тактового сигнала). Таким образом, вследствие того, что фаза запроса имеет длительность в два периода шинного тактового сигнала и передача строки кэша требует двух периодов шинного тактового сигнала, скорость в тракте или частота в тракте процессорной шины может в целом считаться равной двум периодам шинного тактового сигнала.

Согласно варианту выполнения изобретения, шинный протокол перенастраивался или модифицировался для подстройки запаздывания или задержки между началом следующих друг за другом фаз для более полного согласования новой частоты в тракте из двух периодов шинного тактового сигнала для процессорной шины. Фиг.7 представляет собой диаграмму, иллюстрирующую минимальное запаздывание или задержку между фазами транзакции (в том числе, фазами арбитража, запроса, слежения и отклика). Фазы арбитража (Arb), запроса (Req), слежения и отклика (Resp) показаны для двух транзакций (транзакция 1 и транзакция 2). Цифры проставлены для указания запаздывания или задержки между фазами. Первая цифра указывает минимальное число периодов шинного тактового сигнала между началом фаз, как это воплощено в некоторых процессорах Pentium, тогда как вторая цифра (взятая в скобки) указывает новое минимальное запаздывание между фазами после того, как шинный протокол был подстроен или перенастроен для более полного согласования с новой частотой в тракте из двух периодов шинного тактового сигнала. Если показана только одна цифра, это указывает на то, что между некоторыми процессорами Pentium и вариантом осуществления изобретения нет никакого изменения в задержке или запаздывании между фазами.

Как отмечено выше, минимальное запаздывание между фазами, показанное на фиг.7, как правило, составляет два периода шинного тактового сигнала. На фиг.7 минимальное запаздывание между началом фазы арбитража и началом фазы запроса для транзакции (например, транзакции 1) остается неизменным и равным двум периодам шинного тактового сигнала. Минимальное запаздывание от начала фазы запроса до начала фазы слежения транзакции уменьшено с четырех периодов шинного тактового сигнала до трех периодов. Минимальное запаздывание между началом фазы слежения до начала фазы запроса остается неизменным и равным двум периодам шинного тактового сигнала. Минимальное запаздывание между началом фазы запроса и моментом, когда целевой агент может установить сигнал TRDY#, уменьшено с трех до двух периодов шинного тактового сигнала. Минимальное запаздывание от установки сигнала TRDY# до начала фазы отклика остается неизменным и равным двум периодам шинного тактового сигнала.

Помимо этого, минимальное запаздывание между одинаковыми или соответствующими фазами следующих друг за другом транзакций модифицировано для более полного согласования с частотой в тракте из двух периодов шинного тактового сигнала. На фиг.7 минимальное запаздывание между следующими друг за другом произвольными фазами (например, минимальное запаздывание между началом фазы арбитража транзакции 1 и началом фазы арбитража транзакции 2) уменьшено с трех периодов шинного тактового сигнала до двух периодов. Минимальное запаздывание между следующими друг за другом фазами запроса уменьшено с трех периодов шинного тактового сигнала до двух. Минимальное запаздывание между следующими друг за другом фазами слежения уменьшено с трех периодов шинного тактового сигнала до двух. И, наконец, минимальное запаздывание между следующими друг за другом фазами отклика уменьшено с трех периодов шинного тактового сигнала до двух.

Каждая из этих фаз будет описана вместе с кратким пояснением некоторых изменений или модификаций в шинном протоколе для этой фазы, которые вносят вклад в уменьшение запаздывания между фазами (если уменьшение запаздывания имеет место).

Когда запрашивающий агент не является владельцем шины, транзакции начинаются с фазы арбитража, в которой запрашивающий агент становится владельцем шины. После того, как запрашивающий агент становится владельцем шины, транзакция входит в фазу запроса. В первой подфазе (подфаза а) фазы запроса сигнал ADS# (указывающий достоверный адрес) задается вместе с адресом транзакции и достаточной информацией, чтобы начать слежение и обращение к памяти. Во второй подфазе (подфаза b) фазы запроса различная вспомогательная для запроса информация выдается на шину 117, в том числе разрешения байтов (указывающие, какие байты данных будут подаваться на линии данных), идентификатор отсрочки, длина транзакции и иная информация транзакции. Первая и вторая фазы инициируются в течение одного периода шинного тактового сигнала. В результате, согласно варианту выполнения, об информации запроса (большая часть из которой подается, например, по адресной шине) говорится, что она имеет удвоенную скорость передачи данных.

Согласно варианту выполнения, каждая транзакция имеет фазу слежения. Результаты слежения из фазы слежения указывают, ссылается ли адрес, заданный для транзакции, на достоверную или модифицированную (необновленную) строку кэша в кэше любого шинного агента. Результаты слежения указывают также, будет ли транзакция завершаться в порядке очередности или может быть отсрочена для возможного завершения с измененной очередностью. Агент может задержать транзакцию, если он не готов к слежению, путем растягивания фазы слежения с помощью задержки слежения.

Каждая из фаз будет описана с выделением отличий, воплощенных для уменьшения запаздывания между фазами (где это приемлемо).

1) Фаза арбитража: никакие транзакции не могут инициироваться до тех пор, пока шинный агент владеет процессорной шиной 117. Транзакции необходимо лишь находиться в этой фазе, если агент, который желает выдать эту транзакцию на процессорную шину 117, не является уже владельцем шины 117. Согласно варианту выполнения, предусматривается протокол арбитража шины, который поддерживает два класса шинных агентов: симметричные агенты и приоритетные агенты. Процессоры на шине 117, как правило, рассматриваются как симметричные агенты. Приоритетным агентом (например, системный интерфейс 116) обычно считается тот, который выступает от имени подсистемы ввода-вывода (мост 124 ввода-вывода или агенты ввода-вывода) и подсистемы памяти (агенты памяти, расположенные в подсистеме 122 основной памяти).

Примерная сигнальная группа, которая может использоваться для владельца шины, показана ниже (как это используется здесь, знак # указывает активные сигналы низкого уровня):

ПРИМЕРНЫЕ СИГНАЛЫ АРБИТРАЖА

Процессорная шина 117 позволяет множеству агентов одновременно осуществлять арбитраж для доступа к шине 117. Симметричные агенты осуществляют арбитраж для доступа к шине 117 на основании схемы приоритета в порядке круговой очереди. Эта схема арбитража гарантирует справедливый доступ к фазе запроса для всех симметричных агентов. Каждый симметричный агент имеет уникальный идентификатор агента, назначенный при сбросе (например, агенты 0, 1, 2, 3), и арбитраж будет осуществляться в порядке круговой очередности. После сброса агент 0 имеет наивысший приоритет, за ним следуют агенты 1, 2 и 3. Каждый симметричный агент сохраняет общий идентификатор ротации, который отражает идентификатор симметричного агента самого недавнего владельца шины. При каждом событии арбитража симметричный агент с наивысшим приоритетом становится владельцем шины и может входить в фазу запроса, если нет других действий с более высоким приоритетом, предотвращающих использование шины. Приоритетный агент(ы) имеет более высокий приоритет, нежели симметричный владелец.

Симметричный агент запрашивает шину путем утверждения своего сигнала BREQ#. На основании значения, выбранного на BREQ#, и последнего симметричного владельца шины все агенты могут одновременно определить следующего симметричного владельца шины. Приоритетный агент запрашивает шину путем установки сигнала BPRI#, который временно отменяет схему арбитража, потому что никакой симметричный агент не будет инициировать другую транзакцию не захваченной шины до тех пор, пока сигнал BPRI# не будет выбран неактивным. Приоритетный агент всегда является очередным владельцем шины. Сигнал BNR# может устанавливаться любым шинным агентом, чтобы заблокировать дальнейшие транзакции от поступления на шину (обычно используется, когда системные ресурсы, такие как буферы, заполнены и не могут принять другую транзакцию). Установка сигнала LOCK# указывает, что шинный агент выполняет неделимую последовательность шинных транзакций, которую нельзя прерывать.

Приоритетный агент может отменить установление BPRI# и оставить владельца шины в том же самом периоде, который он генерировал в своем последнем запросе. В некоторых процессорах Pentium после того, как отменена установка сигнала BPRI#, установка этого сигнала BPRI# должна быть отменена минимально на два периода шинного тактового сигнала. Это согласуется с прежней частотой в три периода шинного тактового сигнала (в некоторых процессорах Pentium) и, таким образом, обеспечивает сбалансированный доступ к шине между симметричными агентами и приоритетными агентами. Согласно варианту выполнения, протокол изменялся, чтобы потребовать отмены установки сигнала BPRI# минимум только на один период шинного тактового сигнала после его установки. Это изменение в текущем варианте выполнения поддерживает скорость в тракте в два периода шинного тактового сигнала с одним периодом шинного тактового сигнала для установки и одним периодом для отмены установки.

Как отмечалось, сигнал BNR# может использоваться для задержки дальнейших запросов, например, когда агент не имеет достаточно ресурсов для поддержания другой транзакции. Согласно варианту выполнения, протокол остановки запроса воплощается и определяется на основании трех состояний:

1) Свободное: в этом состоянии способность агента выдавать запросы не ограничена протоколом задержки запроса BNR#, а ограничена только тем, что он является владельцем шины, и частотой следования запроса. В некоторых процессорах Pentium момент выборки BNR# в свободном состоянии имеет место через три периода тактового сигнала после того, как сигнал ADS# выбран установленным. Согласно варианту выполнения, момент выборки BNR# подстраивался, чтобы иметь место через два периода тактового сигнал (а не три) после того, как сигнал ADS# выбран установленным. Когда агент намерен остановить генерирование нового запроса в свободном состоянии, этот агент задает BNR# активным в периоде тактового сигнала перед моментом выборки достоверного BNR# из ADS#. В следующем периоде тактового сигнала все агенты наблюдают активный BNR# в момент выборки BNR#, и переходят в остановленное состояние.

2) Приостановленное: в этом состоянии агент может инициировать один запрос, когда он является владельцем шины и поддерживается максимальная частота запроса ADS#. Момент выборки BNR# находится в первом периоде тактового сигнала приостановленного состояния. В прерванном состоянии, если BNR# выбирается активным в момент выборки BNR#, состояние переходит в остановленное состояние. Если BNR# выбирается неактивным в момент выборки BNR#, осуществляется переход в свободное состояние.

3) Остановленное: в этом состоянии агент не может инициировать запроса до тех пор, пока BNR#, выбранный в момент выборки BNR#, не станет неактивным. Момент выборки BNR# начинается в периоде шинного тактового сигнала, когда происходит переход в остановленное состояние, и в каждом другом последующем периоде тактового сигнала все время, пока BNR# выбирается активным в свой момент выборки. Состояние остановленного запроса всегда инициализируется в остановленное после события сброса (либо INIT#, либо RESET#). Агент может продлить остановленное состояние путем установки BNR# каждые два периода тактового сигнала (перед допустимыми моментами выборки). Если BNR# не выбирается активным в остановленном состоянии, состояние остановленного запроса перейдет в приостановленное состояние.

Поэтому, требование, чтобы была отменена установка сигнала BNR# только минимально на один период (а не на два) шинного тактового сигнала после его установки, и подстройка момента выборки BNR# в свободном состоянии так, чтобы она происходила через два (а не три) периода тактового сигнала после того, как сигнал ADS# выбирается установленным, уменьшает минимальное запаздывание между началом следующих друг за другом фаз арбитража с трех периодов шинного тактового сигнала до двух периодов шинного тактового сигнала.

2) Фаза запроса: фаза запроса является фазой, в которой транзакция реально инициируется или выдается на шину. Согласно варианту выполнения, фаза запроса составляет по длительности один период общего шинного тактового сигнала. Фаза запроса включает в себя две подфазы, в том числе подфазу а (в течение первой половины фазы запроса) и подфазу b (в течение второй подфазы в фазе запроса). В фазе запроса передается информация запроса, включающая в себя адрес транзакции. Фаза запроса начинается с установки сигнала ADS# - стробирующего адрес сигнала. Ниже дается примерная группа сигналов, которые могут использоваться для передачи запроса.

ПРИМЕРНЫЕ СИГНАЛЫ ЗАПРОСА

Примечания:

а. Эти сигналы выдаются на указанный контакт в течение первой подфазы (подфаза а) в фазе запроса.

b. Эти сигналы выдаются в течение второй подфазы (подфаза Ь) в фазе запроса.

Таким образом, адрес транзакции передается по Аа[35:3] (где "А" указывает адресные линии или адресную шину 204, а "а" указывает сигналы, передаваемые в течение подфазы а), а дополнительная информация (например, разрешения байтов, атрибуты, расширенные функции), описывающие эту транзакцию, передаются по Ab[35:3] ("b" указывает, что эта дополнительная информация передается по адресным линиям в течение подфазы b). Установка ADS# определяет начало фазы запроса. ADSTB[1:0]# следует предпочтительно переключать один раз в каждом периоде шинного тактового сигнала, в котором устанавливается ADS#, и ни в каких иных периодах. REQa[4:0]# и REQb[4:0]# идентифицируют вид транзакции.

Согласно варианту выполнения, запрос может задаваться на процессорную шину:

1) через один период после получения владения шиной, и

2) через два или более периодов после установки ADS# для предыдущей транзакции, и

3) при наблюдении BNR# неактивным, и

4) при наблюдении LOCK# неактивным, если он не активирован данным агентом.

Некоторые процессоры Pentium требуют минимальной задержки в три периода тактового сигнала после установления ADS# предыдущей транзакции перед тем, как запрос может быть выдан на процессорную шину. Чтобы уменьшить минимальное запаздывание между фазами запроса следующих друг за другом транзакций с трех периодов тактового сигнала до двух периодов тактового сигнала, агент может выдавать запрос на шину после только двух периодов шинного тактового сигнала после установления сигнала ADS# предыдущей транзакции, согласно варианту выполнения. Как отмечалось выше, сигнал ADS# идентифицирует начало фазы запроса и указывает, что на процессорную шину выдана подфаза а запроса, включая адрес (поданный по адресной шине) и запрос (поданный по линиям REQ#[4:0]).

3) Фаза слежения: согласно варианту выполнения, процессорная шина поддерживает согласованность кэша для множества использующих кэш агентов. Согласованность (или когерентность данных) гарантирует, что система или компьютер со множеством уровней кэша и памяти и множеством использующих кэш агентов представляет модель совместно используемой памяти, в которой предпочтительно никакой агент никогда не считывает устаревшие (или неправильные) данные и действия по мере надобности могут быть выстроены последовательно. Строка представляет собой блок кэширования в использующих кэш агентах. Согласно варианту выполнения, строка кэша имеет 64 байта, но могут использоваться и строки кэша иных размеров.

Протокол кэша связывает состояния со строками и определяет правила, управляющие переходами состояний. Каждая строка имеет состояние в каждом кэше. Согласно варианту выполнения, имеется четыре состояния строк, в том числе: М (модифицированное), которое указывает, что строка находится в данном кэше и содержит более свежее значение строки, нежели в памяти, и что эта строка неверна во всех других агентах; Э (эксклюзивное), указывающее, что строка находится в этом кэше и имеет то же самое значение, что и в памяти, и неверна во всех иных агентах; С (совместное), указывающее на то, что эта строка находится в данном кэше, содержит то же самое значение, что и в памяти, и может быть в других агентах; и Н (недоступное), указывающее, что строка недоступна в данном кэше и должна быть выбрана из другого кэша или агента.

Фаза слежения представляет собой фазу, в которой согласованность кэша навязывается. Ниже приведен примерный перечень сигналов слежения, которые могут использоваться в фазе слежения:

ПРИМЕРНЫЕ СИГНАЛЫ СЛЕЖЕНИЯ

В фазе слежения все осуществляющие кэширование агенты выдают результаты своего слежения и участвуют в разрешении согласованности кэша. Агенты генерируют результаты внутреннего слежения почти для всех транзакций памяти, которые не являются их собственными. Все осуществляющие кэширование агенты (следящие агенты) выдают результаты своего слежения на шину в этой фазе с помощью сигналов HIT# и HITM#. HIT# устанавливается в течение фазы слежения, чтобы указывать ту копию строки кэша, которая содержит запрошенные данные, хранящиеся в кэше другого агента на данном интерфейсе. HITM# устанавливается в течение фазы слежения, чтобы указывать, что модифицированная копия строки кэша, которая содержит запрошенные данные, находится в кэше другого агента на данном интерфейсе. Если HIT# и HITM# установлены агентом одновременно в течение фазы слежения, то происходит остановка слежения и текущая фаза слежения должна быть продлена. DEFER# устанавливается в течение фазы слежения, чтобы указать, что завершение текущей транзакции не гарантируется.

В некоторых процессорах Pentium результаты слежения выдавались через четыре периода тактового сигнала после того, как сигнал ADS# был установлен, и по меньшей мере, через три периода тактового сигнала после фазы слежения предыдущей транзакции. Однако, согласно варианту выполнения, эти минимальные запаздывания модифицировались для более полного согласования с новой частотой в тракте процессорной шины. Согласно варианту выполнения, результаты слежения могут теперь выдаваться через три периода тактового сигнала после того, как устанавливается сигнал ADS# (т.е. через три периода шинного тактового сигнала после начала фазы запроса) и по меньшей мере через два периода тактового сигнала после фазы слежения (т.е. по меньшей мере через два периода тактового сигнала после того, как результаты слежения выдавались на шину для предыдущей транзакции). Тем самым максимальная частота активации для сигналов HIT#/HITM#/DEFER# (результаты слежения) изменились с одного раза на каждые три периода шинного тактового сигнала до одного раза на каждые два периода шинного тактового сигнала. Отметим, что запаздывание от окончания фазы запросы (подфазы b) до фазы слежения остается одним и тем же, поскольку фаза запроса укоротилась на один период.

4) Фаза отклика: в этой фазе запрашивающий агент выдает отклик транзакции на процессорную шину. Запросы, инициированные в фазе запроса, поступают в порядке очередности, сохраняемой каждым шинным агентом. Отвечающим агентом является агент, ответственный за завершение транзакции на вершине очереди. Отвечающий агент представляет собой устройство или агента, адресованного транзакцией в течение фазы запроса. Ниже дается примерная группа сигналов, которые могут использоваться в фазе отклика:

ПРИМЕРНЫЕ СИГНАЛЫ ОТКЛИКА

Отклик на транзакцию кодируется на линиях RS[2:0]# сигналов. Примеры возможных откликов включают в себя: нормальный отклик данных (когда отвечающему агенту требуется передать данные считывания вместе с откликом), повторный отклик (когда DEFER# устанавливается в течение фазы слежения, указывая, что транзакцию нужно повторить), отсроченный отклик (когда откликающийся агент или отвечающий агент обещает завершить транзакцию в будущем с помощью отсроченной повторной транзакции), отклик без данных (когда никакие данные не возвращаются адресованным агентом) и т.д. TRDY# устанавливается откликающимся агентом для указания того, что он готов принять данные записи или обратной записи, и т.п. Сигналы RSP# обеспечивают четность для сигналов RS.

В некоторых процессорах Pentium отклик можно задавать после минимум трех периодов шинного тактового сигнала после фазы отклика предыдущей транзакции. Согласно варианту выполнения, это минимальное запаздывание между фазами отклика следующих друг за другом транзакций подстраивалось для более полного согласования с новой частотой в тракте процессорной шины. Согласно варианту выполнения, отклик можно выдавать после минимум двух периодов шинного тактового сигнала после отклика предыдущей транзакции. Это минимальное запаздывание, как правило, подвержено другим ограничениям, которые могут продлить это запаздывание. Вследствие режима сигнализации с двойной подкачкой, используемого для сигналов запроса, отклик можно выдавать один раз на каждые два периода шинного тактового сигнала (по сравнению с одним разом на три периода шинного тактового сигнала для некоторых процессоров Pentium).

Запрос, инициированный транзакцией, представляет собой транзакцию, где запрашивающий агент имеет данные записи для передачи. Адресованный агент устанавливает TRDY#, чтобы показать свою способность принимать данные от запрашивающего агента с намерением выполнить транзакцию записи. В некоторых процессорах Pentium сигнал TRDY# может устанавливаться после минимум трех периодов шинного тактового сигнала после установления сигнала ADS# для той же самой транзакции. Как правило, имеются другие ограничения, которые могут удлинить это запаздывание. Это запаздывание модифицировалось для более полного согласования с новой частотой в тракте процессорной шины. Согласно варианту выполнения, адресованный агент может устанавливать сигнал TRDY# после минимум двух периодов шинного тактового сигнала после установления сигнала ADS# для той же самой транзакции. Отметим, что запаздывание от конца фазы запроса до TRDY# остается неизменной.

5) Фаза данных (передачи): во время этой фазы данные передаются между различными шинными агентами по процессорной шине 117. На основании фазы запроса транзакция содержит либо передачу "инициированных запросом" данных (записи) или передачу "инициированных откликом" данных (чтения), либо отсутствие передачи данных. Фаза данных может перекрываться фазой запроса для транзакции.

Ниже представлен примерный перечень сигналов, которые могут использоваться в фазе данных:

ПРИМЕРНЫЕ СИГНАЛЫ ДАННЫХ

DRDY# указывает, что достоверные данные помещены на шину 117 и должны быть зафиксированы. Владелец шины данных устанавливает DRDY# для каждого периода шинного тактового сигнала, в котором достоверные данные подлежат передаче. Установление DRDY# можно отменить, чтобы ввести состояние ожидания в фазу данных. DRDY# можно использовать, чтобы удержать шину данных перед первым установлением DRDY# и между следующими друг за другом установлениями DRDY# для передачи множества данных с шинным тактовым сигналом. DINV[3:0]# используются для указания на то, что биты данных инвертированы источником данных.

Сигналы D[63:0]# данных шины 206 данных (фиг.2) обеспечивают 64-разрядный тракт между шинными агентами. Для частичной передачи, включая транзакции считывания ввода-вывода и записи ввода-вывода, сигналы (BE[7:0]#) разрешения байтов определяют, какие байты шины данных будут содержать достоверные данные. Сигналы DP могут использоваться, чтобы обеспечить четность для сигналов данных.

Согласно варианту выполнения, данные могут передаваться с помощью протокола фиксированной синхронизации с источником с множественной подкачкой (например, 4Х), в котором сигналы D[63:0]# данных используются для передачи четырех 8-байтовых элементов данных в единственном периоде шинного тактового сигнала. Первые 8 байтов (в пакетном порядке) передаются в первой четверти шинного такта, второй 8-байтовый элемент - во второй четверти шинного такта, третий 8-байтовый элемент - в третьей четверти шинного такта, а четвертый 8-байтовый элемент - четвертой четверти шинного такта. Данные могут передаваться в первой четверти шинного такта, если эти данные, подлежащие передаче, имеют длину от 1 до 8 байтов, и данные могут передаваться в первых двух четвертях шинного такта, если эти данные имеют длину 9-16 байтов.

Несколько вариантов выполнения настоящего изобретения конкретно проиллюстрированы и описаны здесь. Однако понятно, что модификации и вариации настоящего изобретения охватываются вышеприведенными разъяснениями и находятся в объеме приложенной формулы изобретения без отрыва от сущности и предполагаемого объема изобретения.

К фиг.1:

100 - компьютер

110 - процессорный агент 0

112 - процессорный агент 1

114 - процессорный агент 2

117 - процессорная шина

116 - системный интерфейс

118 - контроллер памяти

120 - интерфейс ввода-вывода

122 - основная память

124 - мост ввода-вывода

130 - шина ввода-вывода

132 - контроллер ввода-вывода

134 - контроллер ввода-вывода

К фиг.2:

115 - процессорная шина

202 - управляющая шина

204 - адресная шина

206 - шина данных

К фиг.3;

1 - Арбитраж

2 - Запрос

3 - Слежение

4 - Отклик

5 - Передача данных

6 - ЗАМЕЧАНИЕ: Заштрихованная вертикальная полоса указывает, что между различными фазами допускается один или более периодов тактового сигнала

К фиг.4:

7 - Полный такт разрешен для распространения сигнала

8 - Полный такт разрешен для логических задержек

9 - Установление А#

10 - Фиксация А#

11 - Установление В#

12 - Фиксация В#

К фиг.5:

7 - Полный такт разрешен для распространения сигнала

13 - (@задатчик)

14 - (@приемник)

15 - Выдача (D1# или D2#)

16 - Выдача (D1# или D2#)

17 - Фиксация D1, D2, D3, D4 (самого позднего)

К фиг.6:

7 - Полный такт разрешен для распространения сигнала

13 - (@задатчик)

14 - (@приемник)

15 - Выдача (Аа# или Ab#)

16 - Захват (Аа# или Ab#)

18 - Самый поздний

К фиг.7:

19 - Транзакция 1

20 - Транзакция 2

21 - Слежение

22 - Остановка слежения

23 - Приостановка

24 - Остановка

К фиг.8:

25 - Генератор 1 строба данных / приемник 1

26 - Генератор 2 строба данных / приемник 2

27 - Принимающая цепь

28 - Передающая цепь

802 - Первый шинный агент

806 - Шинный приемопередатчик

810 - Генератор общего шинного тактового сигнала

826 - Данные

832 - Второй шинный агент

836 - Шинный приемопередатчик

К фиг.9:

(см. также подписи к фиг.8)

906, 936=806, 836

926 - Адрес

940, 942 - Генератор адресного строба / приемник

| название | год | авторы | номер документа |

|---|---|---|---|

| ПАРАЛЛЕЛЬНО СОГЛАСОВАННАЯ ШИННАЯ СИСТЕМА | 2001 |

|

RU2239230C2 |

| СОВМЕСТИМОСТЬ ОДНОПРОВОДНОЙ И ТРЕХПРОВОДНОЙ ШИН | 2005 |

|

RU2352980C2 |