Предлагаемое изобретение относится к технике радиолокации, радиосвязи, радионавигации и радиоуправления и может быть использовано в радиоэлектронных системах для решения задачи обнаружения сигналов.

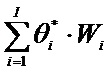

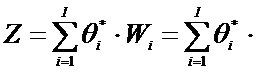

Известна оптимальная комплексная система обнаружителей (КСО), реализуемая на этапе первичной обработки сигналов [Сосулин Ю.Г. Теоретические основы радиолокации и радионавигации. - М.: Радио и связь, 1992, C. 299, рис.8.4]. Система содержит набор согласованных фильтров и умножителей (по числу I объединяемых обнаружителей), сумматор и пороговое устройство. Аналоговые сигналы, поступающие на входы согласованных фильтров, после их прохождения и умножения на весовые коэффициенты преобразуются в корреляционные интегралы qi, i = , которые в виде аналоговых реализаций поступают на входы сумматора. На выходе сумматора формируется решающая статистика Z =

, которые в виде аналоговых реализаций поступают на входы сумматора. На выходе сумматора формируется решающая статистика Z =  , поступающая на вход порогового устройства, которое после ее сравнения с заданным порогом вырабатывает решение о наличии или отсутствии сигнала.

, поступающая на вход порогового устройства, которое после ее сравнения с заданным порогом вырабатывает решение о наличии или отсутствии сигнала.

Аналогичная КСО имеет место в многопозиционных радиолокационных станциях (МПРЛС) при централизованном обнаружении [Черняк В.С. Многопозиционная радиолокация. - М.: Радио и связь, 1993. - С. 155], когда по линиям передачи данных (ЛПД) в центр обработки информации (ЦОИ) передаются корреляционные интегралы, сформированные всеми позициями МПРЛС, а решение о наличии или отсутствии сигнала принимается только в ЦОИ после суммирования этих корреляционных интегралов и сравнения полученной суммы с порогом. В случае превышения порога принимается решение о наличии сигнала, в противном случае - об отсутствии сигнала.

К недостаткам системы можно отнести ее громоздкость и сложность -в реализации, особенно в многопозиционной радиолокационной станции, где требуется передавать в ЦОИ аналоговые реализации сигналов, что предъявляет высокие требования к пропускной способности ЛПД.

Значительно проще реализуется оптимизация КСО на этапе вторичной обработки сигналов [Сосулин Ю.Г. Теоретические основы радиолокации и радионавигации. - М.: Радио и связь, 1992, с. 298, рис.8.3]. Система содержит I объединяемых обнаружителей и умножителей, сумматор и пороговое устройство. Каждый обнаружитель представляет собой согласованный фильтр и пороговое устройство и формирует предварительное (частное) решение о наличии (

о наличии ( = 1) или отсутствии (

= 1) или отсутствии ( = 0) сигналов путем сравнения с порогом корреляционного интеграла q

= 0) сигналов путем сравнения с порогом корреляционного интеграла q , поступающего с выхода согласованного фильтра на пороговое устройство. Частные решения поступают на входы умножителей и после умножения на соответствующие весовые коэффициенты

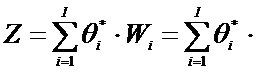

, поступающего с выхода согласованного фильтра на пороговое устройство. Частные решения поступают на входы умножителей и после умножения на соответствующие весовые коэффициенты  поступают на входы сумматора. На выходе сумматора формируется решающая статистика Z =

поступают на входы сумматора. На выходе сумматора формируется решающая статистика Z =  , поступающая на вход порогового устройства, которое после - ее сравнения с заданным порогом вырабатывает общее решение о наличии или отсутствии сигнала.

, поступающая на вход порогового устройства, которое после - ее сравнения с заданным порогом вырабатывает общее решение о наличии или отсутствии сигнала.

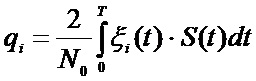

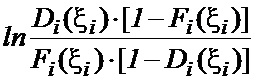

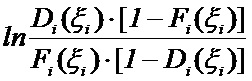

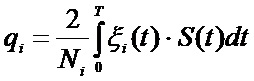

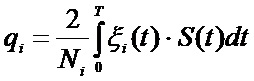

Известно также комплексное устройство обнаружения в многопозиционной радиолокационной станции [Патент РФ RU 2556710 «Комплексное устройство обнаружения в многопозиционной радиолокационной станции»], являющееся многоканальным и содержащее в каждом канале согласованный фильтр, два функциональных преобразователя и линию передачи данных, а в общей части сумматор и пороговое устройство. Устройство реализует алгоритм оптимального по критерию Неймана-Пирсона комплексирования обнаружителей на этапе вторичной обработки, и работает следующим образом (рассмотрим работу одного i-го канала устройства, поскольку каналы идентичны). Аналоговый входной сигнал  (t), в состав которого входит детерминированный сигнал S(t), поступает на вход согласованного фильтра , с выхода которого аналоговый сигнал в виде корреляционного интеграла

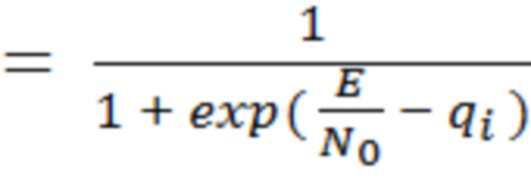

(t), в состав которого входит детерминированный сигнал S(t), поступает на вход согласованного фильтра , с выхода которого аналоговый сигнал в виде корреляционного интеграла  поступает на вход первого функционального преобразователя , который преобразует значения qi и поступающие на его второй и третий входы значения Е и N0 в апостериорную вероятность наличия сигнала Pi в соответствии с выражением

поступает на вход первого функционального преобразователя , который преобразует значения qi и поступающие на его второй и третий входы значения Е и N0 в апостериорную вероятность наличия сигнала Pi в соответствии с выражением

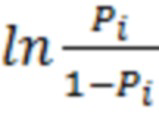

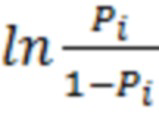

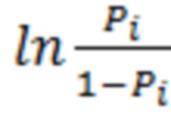

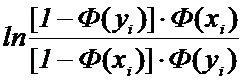

. Значение вероятности Pi по линии передачи данных передается в центр обработки информации, где поступает на вход второго функционального преобразователя, который преобразует ее в выходной сигнал i-го канала устройства в соответствии с выражением

. Значение вероятности Pi по линии передачи данных передается в центр обработки информации, где поступает на вход второго функционального преобразователя, который преобразует ее в выходной сигнал i-го канала устройства в соответствии с выражением  . Эти сигналы с выходов всех каналов устройства

. Эти сигналы с выходов всех каналов устройства  (i =

(i = ) поступают на соответствующие входы сумматора. Сформированная на выходе сумматора решающая статистика

) поступают на соответствующие входы сумматора. Сформированная на выходе сумматора решающая статистика

подается на вход общего порогового устройства, где ее значение сравнивается с величиной порога

подается на вход общего порогового устройства, где ее значение сравнивается с величиной порога  , поступающей на второй вход общего порогового устройства в качестве внешнего сигнала. В зависимости от результата сравнения общее пороговое устройство формирует общее решение

, поступающей на второй вход общего порогового устройства в качестве внешнего сигнала. В зависимости от результата сравнения общее пороговое устройство формирует общее решение  в виде 1 (если порог превышен - сигнал есть) или 0 (порог не превышен - сигнала нет).

в виде 1 (если порог превышен - сигнал есть) или 0 (порог не превышен - сигнала нет).

Устройство позволяет сократить объем передаваемой по ЛПД информации за счет использования в решающей статистике апостериорных вероятностей правильного обнаружения и ложной тревоги, однако эти вероятности определены косвенно, что обуславливает недостаток - передачу информации от всех входящих в его состав обнаружителей, хотя некоторые из них приняли решение об отсутствии сигнала ( = 0) и могли бы не участвовать в формировании решающей статистики.

= 0) и могли бы не участвовать в формировании решающей статистики.

По техническому решению наиболее близким к предлагаемому изобретению является комплексное устройство обнаружения - в многопозиционной радиолокационной станции, аналогичное рассмотренному выше [Патент РФ RU 2778247 «Комплексное устройство обнаружения в многопозиционной радиолокационной станции»], которое и выбрано в качестве прототипа.

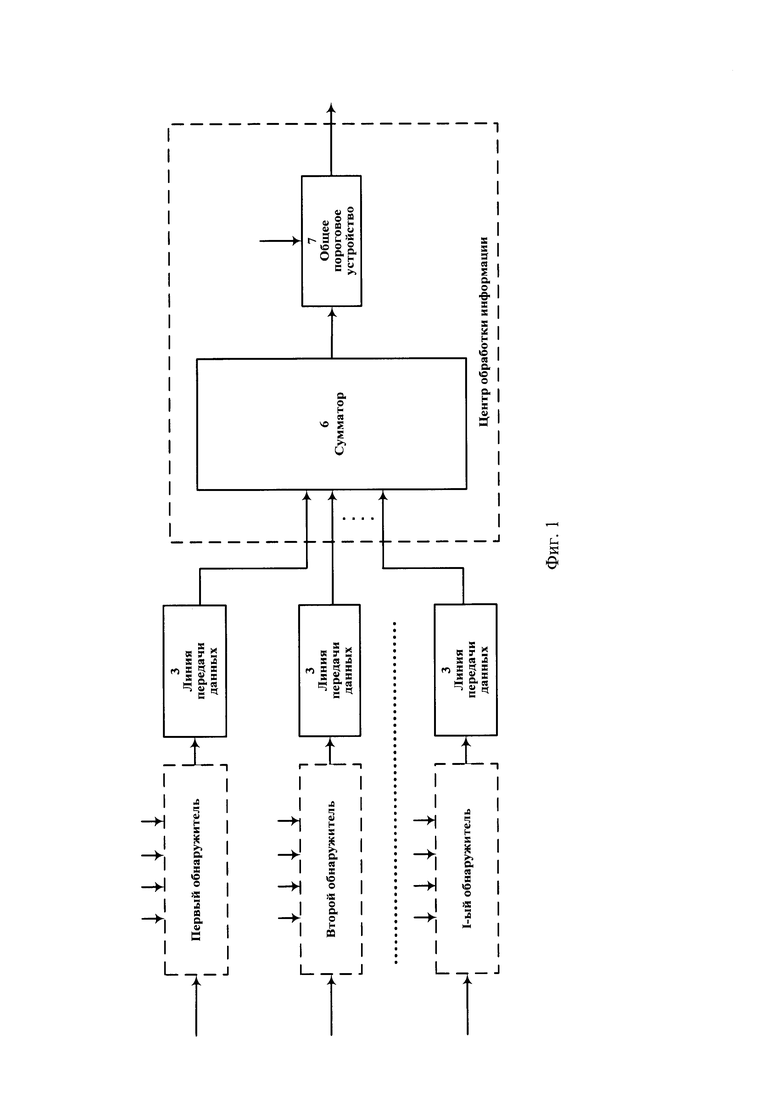

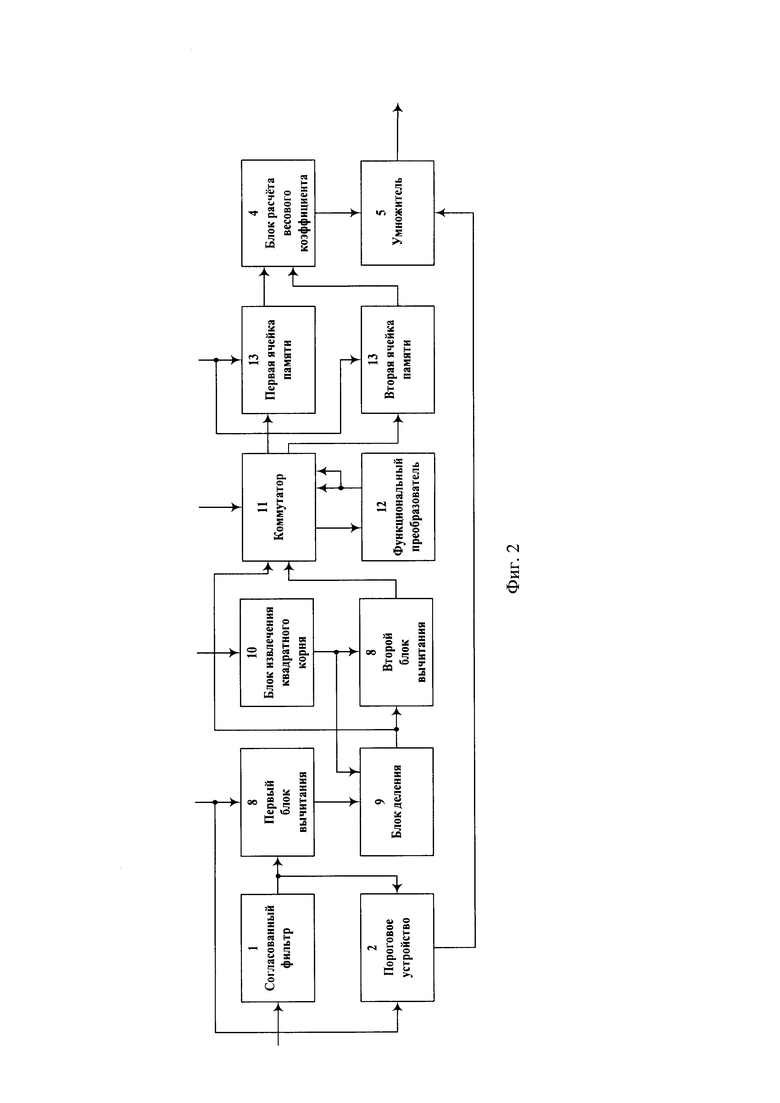

Блок-схема устройства-прототипа представлена на фиг. 1,2,3.

Устройство является I-канальным (по числу позиций МПРЛС), причем каждый канал содержит (фиг.2):

1 - согласованный фильтр, выход которого подключен ко входу порогового устройства 2 и первому входу первого блока вычитания 8;

2 - пороговое устройство, вход которого подключен к выходу согласованного фильтра 1, а второй вход является внешним входом сигнала порогового уровня. Выход порогового устройства 2 подключен к первому входу умножителя 5;

8 - первый и второй блоки вычитания. Первый вход первого блока вычитания 8 подключен к выходу согласованного фильтра 1 и входу порогового устройства 2, а второй вход этого блока соединен с внешним входом сигнала порогового уровня и вторым входом порогового устройства 2. Первый вход второго блока вычитания 8 подключен к выходу блока деления 9 и первому входу коммутатора 11, а второй вход - ко второму входу блока деления 9 и выходу блока извлечения квадратного корня 10. Выход первого блока вычитания 8 соединен с первым входом блока деления 9, а выход второго блока вычитания 8 - со вторым входом коммутатора 11;

9 - блок деления, первый и второй входы которого соединены соответственно с выходом первого блока вычитания 8 и с выходом блока извлечения квадратного корня 10. Выход блока деления подключен к первым входам второго блока вычитания 8 и коммутатора 11;

10 - блок извлечения квадратного корня, вход которого является внешним входом отношения сигнал/шум, а выход подключен ко вторым входам второго блока вычитания 8 и блока деления 9;

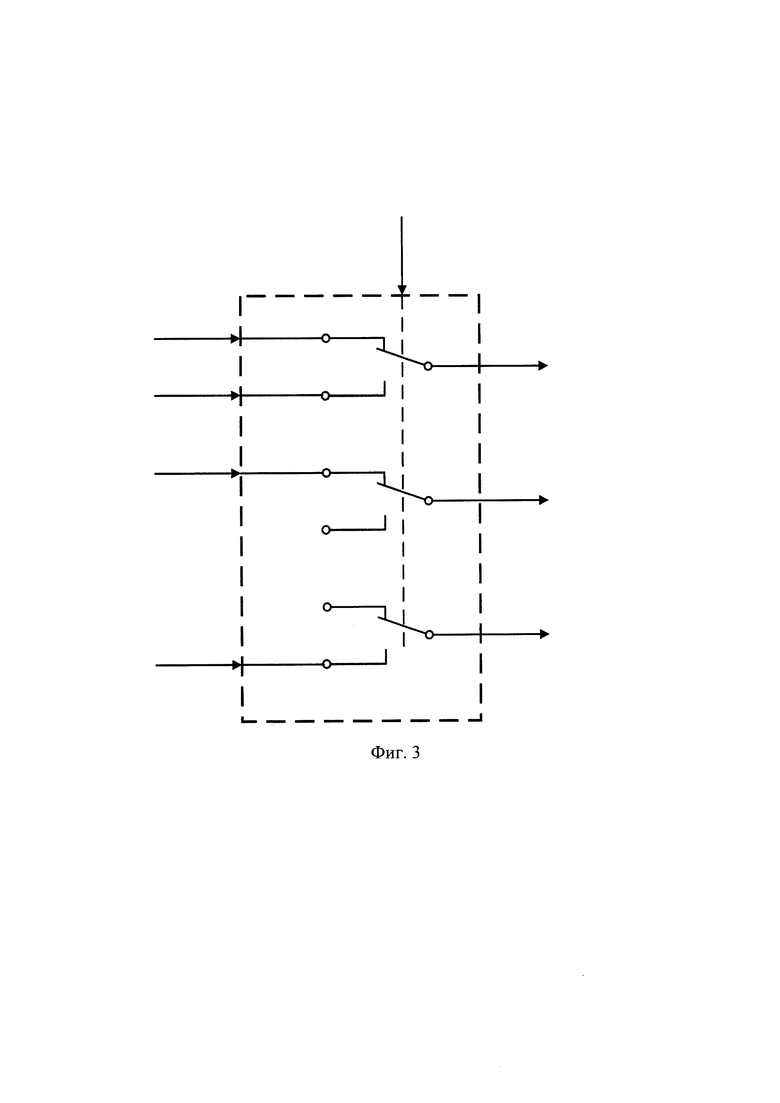

11 - коммутатор (фиг. 3), первый и второй входы которого подключены соответственно к выходу блока деления 9 и выходу второго блока вычитания 8, третий и четвертый входы объединены и подключены к выходу функционального преобразователя 12. Управляющий вход коммутатора является внешним входом устройства. Первый выход коммутатора 11 соединен со входом функционального преобразователя 12, -а второй и третий выходы - соответственно со входом первой и второй ячеек памяти 13;

12 - функциональный преобразователь, вход которого соединен с первым выходом коммутатора 11, а выход - с третьим и четвертым входами коммутатора 11;

13 - первая и вторая ячейки памяти, первый вход каждой из которых подключен соответственно ко второму и третьему выходам коммутатора 11,

вторые входы объединены и являются внешним входом считывания. Выход первой и второй ячеек 13 подключен к соответствующему входу блока расчета весового коэффициента 4;

4 - блок расчета весового коэффициента, первый и второй входы которого подключены соответственно к выходам первой и второй ячеек памяти 13. Выход блока 4 подключен ко второму входу умножителя 5;

5 - умножитель, первый вход которого подключен к выходу порогового устройства 2, а второй вход - к выходу блока расчета весового коэффициента 4. Выход умножителя 5 подключен ко входу линии передачи данных 3 (фиг.1);

3 - линия передачи данных (ЛПД), вход которой подключен к выходу умножителя 5, а выход является выходом канала устройства и подключен к соответствующему входу сумматора 6.

Сигналы с выходов ЛПД 3 поступают в общую часть устройства, которая содержит:

6 - сумматор на I входов, каждый из которых подключен к выходу соответствующей ЛПД 3. Выход сумматора 6 подключен ко входу общего порогового устройства 7;

7 - общее пороговое устройство, вход которого подключен к выходу сумматора 6, второй вход является внешним входом сигнала общего порогового уровня, а выход является выходом устройства.

Устройство реализует алгоритм оптимального по критерию Неймана-Пирсона комплексирования обнаружителей на этапе вторичной обработки, который заключается в сравнении с порогом следующей решающей статистики [Сосулин Ю.Г. Теоретические основы радиолокации и радионавигации. - М.: Радио и связь, 1992. С. 298]

(1)

(1)

где i - номер обнаружителя (или позиции МПРЛС);

I - количество объединяемых обнаружителей;

- частные решения объединяемых обнаружителей о наличии сигнала или его отсутствии;

- частные решения объединяемых обнаружителей о наличии сигнала или его отсутствии;

,

,  - апостериорные вероятности правильного обнаружения и ложной тревоги соответственно;

- апостериорные вероятности правильного обнаружения и ложной тревоги соответственно;

Wi

- весовые коэффициенты (

- весовые коэффициенты ( ).

).

Устройство работает следующим образом (рассмотрим работу одного

i-го канала устройства (фиг.2), поскольку каналы идентичны). Аналоговый входной сигнал (t) поступает на вход согласованного фильтра 1, с выхода которого аналоговый сигнал в виде корреляционного интеграла

(t) поступает на вход согласованного фильтра 1, с выхода которого аналоговый сигнал в виде корреляционного интеграла  поступает на первый вход первого блока вычитания 8 и вход порогового устройства 2, где его значение сравнивается с величиной порога

поступает на первый вход первого блока вычитания 8 и вход порогового устройства 2, где его значение сравнивается с величиной порога  поступающей на вторые входы первого блока вычитания 8 и порогового устройства 2 в качестве внешнего сигнала. В зависимости от результата сравнения пороговое устройство 2 формирует частное решение

поступающей на вторые входы первого блока вычитания 8 и порогового устройства 2 в качестве внешнего сигнала. В зависимости от результата сравнения пороговое устройство 2 формирует частное решение  в виде 1 (если порог превышен - сигнал есть) или 0 (порог не превышен - сигнала нет), которое поступает на первый вход умножителя 5. Результат вычитания

в виде 1 (если порог превышен - сигнал есть) или 0 (порог не превышен - сигнала нет), которое поступает на первый вход умножителя 5. Результат вычитания

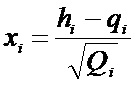

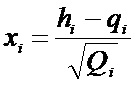

с выхода первого блока вычитания 8 подается на первый вход блока деления 9. Со второго внешнего входа устройства сигнал Qi поступает на вход блока извлечения квадратного корня 10, с выхода которого

с выхода первого блока вычитания 8 подается на первый вход блока деления 9. Со второго внешнего входа устройства сигнал Qi поступает на вход блока извлечения квадратного корня 10, с выхода которого подается на вторые входы блока деления 9 и второго блока вычитания 8. В результате с выхода блока деления 9 снимается сигнал

подается на вторые входы блока деления 9 и второго блока вычитания 8. В результате с выхода блока деления 9 снимается сигнал  , поступающий на первые входы коммутатора 11 и второго блока вычитания 8, с выхода которого сигнал yi = xi -

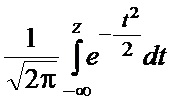

, поступающий на первые входы коммутатора 11 и второго блока вычитания 8, с выхода которого сигнал yi = xi -  подается на второй вход коммутатора 11. В исходном состоянии первый вход коммутатора 11 соединен с его первым выходом, третий вход - со вторым выходом, в результате чего сигнал xi поступает на вход функционального преобразователя 12, реализующего выражение (6), с выхода которого значение Ф (xi) подается на вход первой ячейки памяти 13. При поступлении внешнего сигнала на управляющий вход коммутатора 11 происходит подключение второго и четвертого входов коммутатора соответственно к первому и третьему его выходам, в результате чего сигнал yi поступает на вход функционального преобразователя 12, с выхода которого значение Ф (yi) подается на вход второй ячейки памяти 13. По внешнему сигналу считывания, поступающему на управляющие входы ячеек памяти 13, сигналы Ф (xi) и Ф (yi) одновременно поступают на первый и второй входы блока расчета весового коэффициента 4, с выхода которого значение коэффициента Wi

подается на второй вход коммутатора 11. В исходном состоянии первый вход коммутатора 11 соединен с его первым выходом, третий вход - со вторым выходом, в результате чего сигнал xi поступает на вход функционального преобразователя 12, реализующего выражение (6), с выхода которого значение Ф (xi) подается на вход первой ячейки памяти 13. При поступлении внешнего сигнала на управляющий вход коммутатора 11 происходит подключение второго и четвертого входов коммутатора соответственно к первому и третьему его выходам, в результате чего сигнал yi поступает на вход функционального преобразователя 12, с выхода которого значение Ф (yi) подается на вход второй ячейки памяти 13. По внешнему сигналу считывания, поступающему на управляющие входы ячеек памяти 13, сигналы Ф (xi) и Ф (yi) одновременно поступают на первый и второй входы блока расчета весового коэффициента 4, с выхода которого значение коэффициента Wi

поступает на второй вход умножителя 5, на первый вход которого поступает частное решение

поступает на второй вход умножителя 5, на первый вход которого поступает частное решение  с выхода порогового устройства 2. Результат перемножения

с выхода порогового устройства 2. Результат перемножения  с выхода умножителя 5 через ЛПД 3 поступает на соответствующий вход сумматора 6. Сформированная в сумматоре 6 решающая статистика

с выхода умножителя 5 через ЛПД 3 поступает на соответствующий вход сумматора 6. Сформированная в сумматоре 6 решающая статистика

с его выхода подается на вход общего порогового устройства 7, где ее значение сравнивается с величиной порога h, поступающей на второй вход общего порогового устройства 7 в качестве внешнего сигнала. В зависимости от результата сравнения общее пороговое устройство 7 формирует общее решение

с его выхода подается на вход общего порогового устройства 7, где ее значение сравнивается с величиной порога h, поступающей на второй вход общего порогового устройства 7 в качестве внешнего сигнала. В зависимости от результата сравнения общее пороговое устройство 7 формирует общее решение  в виде 1 (если порог превышен - сигнал есть) или 0 (порог не превышен - сигнала нет).

в виде 1 (если порог превышен - сигнал есть) или 0 (порог не превышен - сигнала нет).

К недостатку прототипа следует отнести то, что сложная помеховая обстановка оказывает значительное влияние на эффективность обнаружения воздушных объектов и может привести к снижению вероятности правильного обнаружения при принятии решения о наличии или отсутствии цели.

Целью изобретения является снижение степени влияния сложной помеховой обстановки на эффективность обнаружения воздушных объектов.

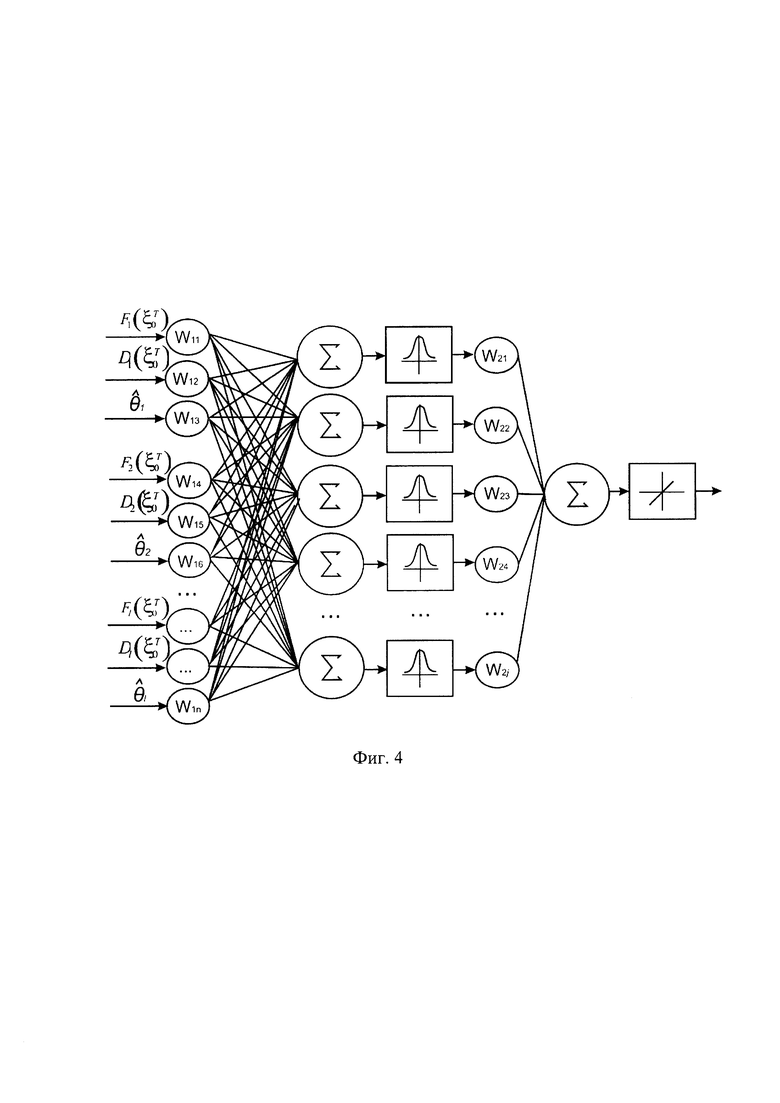

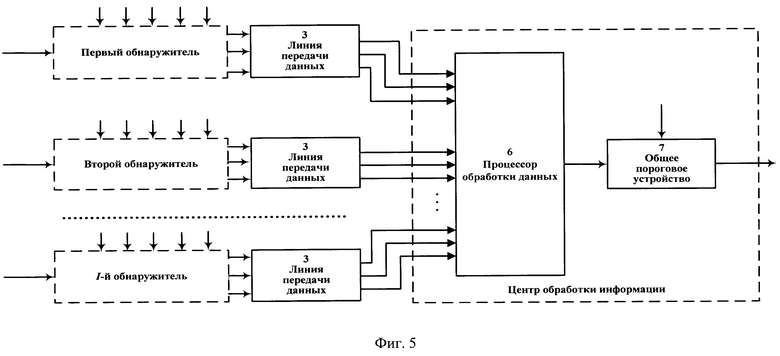

Указанной цели можно добиться путем использования в общей части устройства процессора обработки данных (далее - процессор), реализованного на основе радиальной базисной нейронной сети, обладающей свойством устойчивости к зашумлению входных данных. Ее преимуществом, по сравнению с сетями прямого распространения, является отсутствие проблемы выбора структуры и скорость обучения.

Цель изобретения достигается тем, что в известное устройство, являющееся многоканальным, содержащее общее пороговое устройство, второй вход которого является внешним входом сигнала общего порогового уровня, а в каждом канале согласованный фильтр, пороговое устройство, первый и второй блоки вычитания, блок деления, блок извлечения квадратного корня, коммутатор, функциональный преобразователь, первую и вторую ячейки памяти, линию передачи данных, причем выход согласованного фильтра в каждом канале подключен к первым входам порогового устройства и первого блока вычитания, второй вход которого соединен с первым внешним входом сигнала порогового уровня и со вторым входом порогового устройства, а выход - с первым входом блока деления, второй вход которого соединен со вторым входом второго блока вычитания и выходом блока извлечения квадратного корня, вход которого является вторым внешним входом устройства; выход блока деления подключен к первым входам коммутатора и второго блока вычитания, выход которого соединен со вторым входом коммутатора, первый выход которого подключен ко входу функционального преобразователя, выход которого соединен с третьим и четвертым входами коммутатора, управляющий вход которого является третьим внешним входом устройства, а второй и третий выходы коммутатора подключены к первым входам соответственно первой и второй ячеек памяти, вторые входы которых объединены и являются внешним входом считывания, в общую часть устройства дополнительно введен процессор, выход которого соединен со входом общего порогового устройства, а в каждый канал устройства дополнительно введены третий и четвертый блоки вычитания, первые входы которых соединены с выходами соответственно первой и второй ячеек памяти, вторые входы объединены и соединены с внешним входом сигнала единичного уровня, а выходы являются соответственно первым и вторым выходами канала устройства, третьим выходом которого является выход порогового устройства, причем эти выходы через линию передачи данных подключены к соответствующим входам процессора.

Сопоставительный анализ с прототипом показывает, что заявляемое многоканальное устройство отличается тем, что в каждый канал вместо исключенных блока расчета весового коэффициента и умножителя добавлены третий и четвертый блоки вычитания, а в общей части устройства сумматор заменен на процессор, реализованный на основе уже обученной искусственной радиальной базисной нейронной сети. Процедура обучения заключается в подаче на входы ИНС (фиг.4) обучающего вектора, представляющего собой совокупность частных решений объединяемых обнаружителей и их апостериорных вероятностей правильного обнаружения и ложной тревоги, и последующего сравнения окончательного решения о наличии или отсутствия цели с заданным, при формировании обучающего вектора, результатом.

Таким образом, заявляемое устройство соответствует критерию изобретения «новизна».

Сравнение заявляемого решения с другими техническими решениями показывает, что вновь введенные элементы известны [Нейронные сети. Matlab/ Под ред. В.С. Медведева, В.Г Потемкина - М.: ДИАЛОГ-МИФИ, 2002, с. 47-88, 140-144, 263-267].

Однако при их введении в заявляемое устройство оно проявляет новые свойства, приводящие к снижению степени влияния сложной помеховой обстановки на эффективность обнаружения воздушных объектов. Это позволяет сделать вывод о соответствии технического решения критерию «существенные отличия».

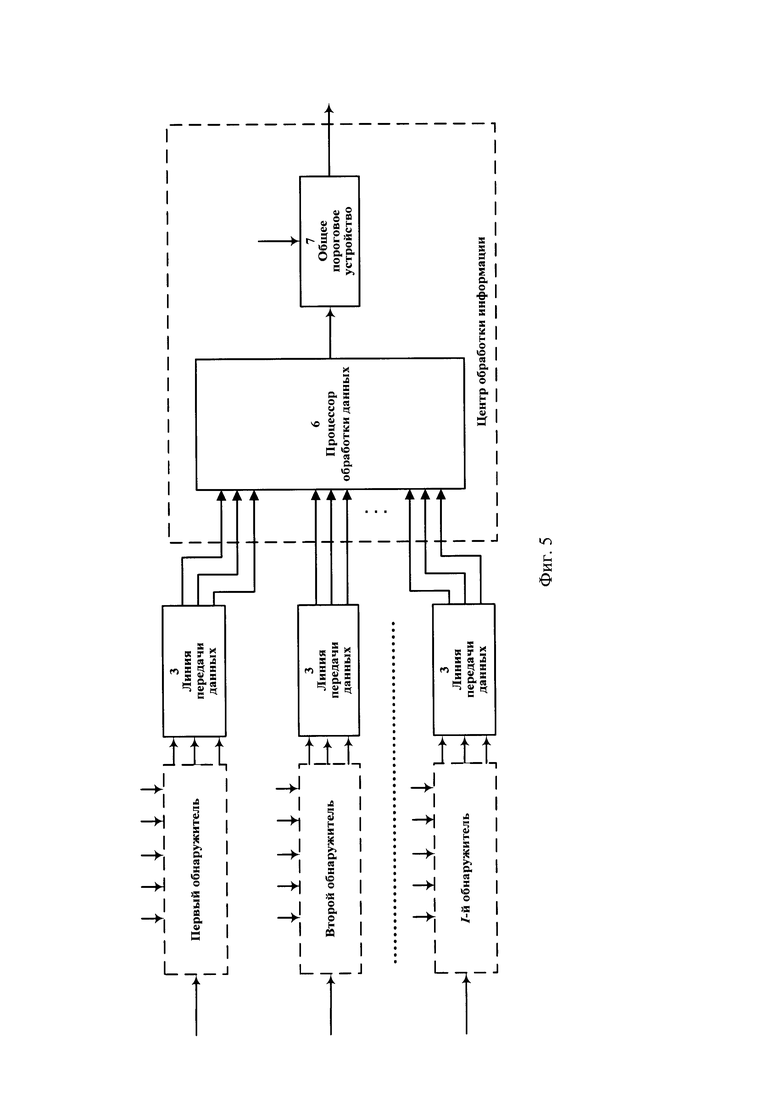

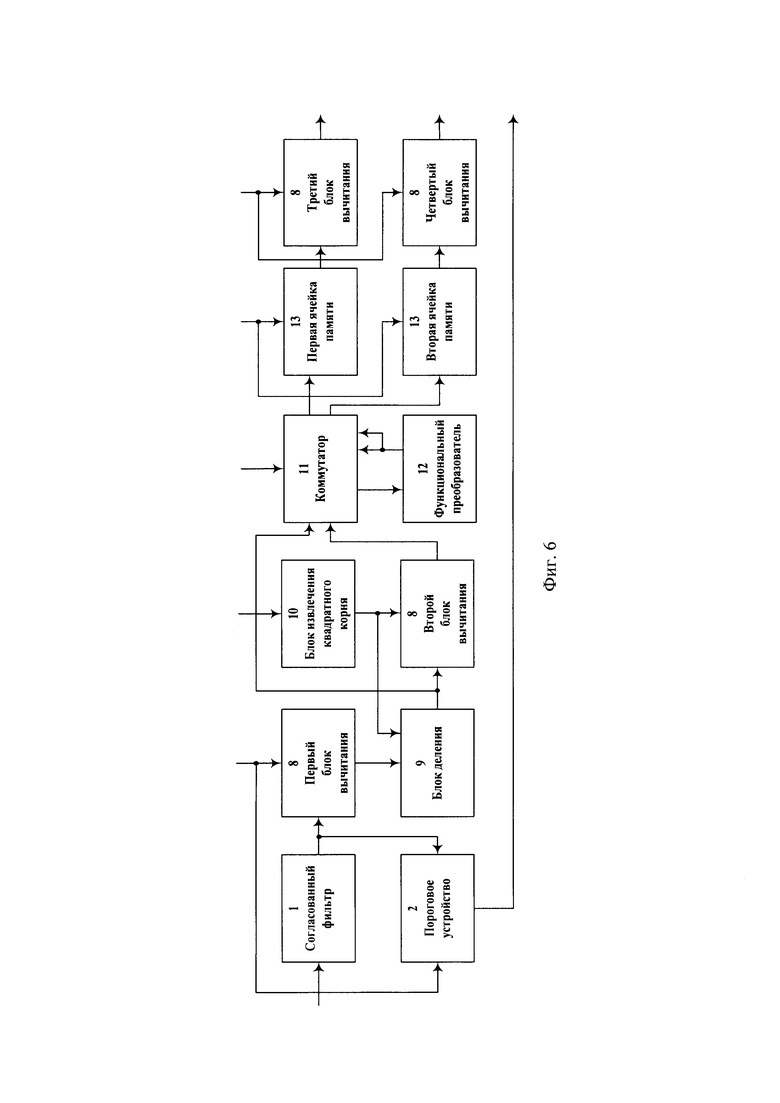

Обобщенная блок-схема устройства представлена на фиг.5, а блок-схема одного обнаружителя - на фиг.6. На этих схемах одинаковые с прототипом блоки имеют ту же нумерацию.

Устройство является I-канальным (по числу обнаружителей), причем каждый канал содержит (фиг.6):

1 - согласованный фильтр, выход которого подключен к первым входам порогового устройства 2 и первого блока вычитания 8;

2 - пороговое устройство, первый вход которого подключен к выходу согласованного фильтра 1, а второй вход является внешним входом сигнала порогового уровня. Выход порогового устройства 2 подключен к третьему входу соответствующей линии передачи данных 3 (фиг.5);

8 - первый и второй блоки вычитания. Первый вход первого блока вычитания 8 подключен к выходу согласованного фильтра 1 и входу порогового устройства 2, а второй вход этого блока соединен с внешним входом сигнала порогового уровня и вторым входом порогового устройства 2. Первый вход второго блока вычитания 8 подключен к выходу блока деления 9 и первому входу коммутатора 11, а второй вход - ко второму входу блока деления 9 и выходу блока извлечения квадратного корня 10. Выход первого блока вычитания 8 соединен с первым входом блока деления 9, а выход второго блока вычитания 8 - со вторым входом коммутатора 11. Первые входы третьего и четвертого блоков вычитания 8 подключены соответственно к выходу первой и второй ячеек памяти 13, вторые входы объединены и подключены к внешнему входу сигнала единичного уровня, а выходы - к первому и второму входам ЛПД 3 (фиг. 5);

9 - блок деления, первый и второй входы которого соединены соответственно с выходом первого блока вычитания 8 и с выходом блока извлечения квадратного корня 10. Выход блока деления подключен к первым входам второго блока вычитания 8 и коммутатора 11;

10 - блок извлечения квадратного корня, вход которого является внешним входом отношения сигнал/шум, а выход подключен ко вторым входам второго блока вычитания 8 и блока деления 9;

11 - коммутатор (фиг. 3), первый и второй входы которого подключены соответственно к выходу блока деления 9 и выходу второго блока вычитания 8, третий и четвертый входы объединены и подключены к выходу функционального преобразователя 12. Управляющий вход коммутатора является внешним входом устройства. Первый выход коммутатора 11 соединен со входом функционального преобразователя 12, а второй и третий выходы - соответственно с первыми входами первой и второй ячеек памяти 13;

12 - функциональный преобразователь, вход которого соединен с первым выходом коммутатора 11, а выход - с третьим и четвертым входами коммутатора 11;

13 - первая и вторая ячейки памяти, первые входы каждой из которых подключены соответственно ко второму и третьему выходам коммутатора 11, вторые входы объединены и являются внешним входом считывания, а выход подключен к первому входу соответственно третьего -и четвертого блоков вычитания 8 (фиг.6);

3 - линия передачи данных (ЛПД) (фиг.5), первый и второй входы которой подключены к выходам соответственно третьего и четвертого блоков вычитания 8, третий вход - к выходу порогового устройства 2.

Сигналы с выходов ЛПД 3 поступают в общую часть устройства, которая содержит:

6 - процессор, реализованный на основе искусственной радиальной базисной нейронной сети на 3I входов, каждый из которых подключен к выходам ЛПД 3. Выход процессора 6 подключен ко входу общего порогового устройства 7;

7 - общее пороговое устройство, первый вход которого подключен к выходу процессора 6, второй вход является внешним входом сигнала общего порогового уровня, а выход является выходом устройства.

Устройство работает следующим образом (рассмотрим работу одного

i-го канала устройства (фиг.6), поскольку каналы идентичны). Аналоговый входной сигнал (t) поступает на вход согласованного фильтра 1, с выхода которого аналоговый сигнал в виде корреляционного интеграла

(t) поступает на вход согласованного фильтра 1, с выхода которого аналоговый сигнал в виде корреляционного интеграла  поступает на первый вход первого блока вычитания 8 и вход порогового устройства 2, где его значение сравнивается с величиной порога

поступает на первый вход первого блока вычитания 8 и вход порогового устройства 2, где его значение сравнивается с величиной порога  поступающей на вторые входы первого блока вычитания 8 и порогового устройства 2 в качестве внешнего сигнала. В зависимости от результата сравнения пороговое устройство 2 формирует частное решение

поступающей на вторые входы первого блока вычитания 8 и порогового устройства 2 в качестве внешнего сигнала. В зависимости от результата сравнения пороговое устройство 2 формирует частное решение  в виде 1 (если порог превышен - «цель есть») или 0 (порог не превышен - «цели нет»), которое поступает на третий вход ЛПД 3. Результат вычитания

в виде 1 (если порог превышен - «цель есть») или 0 (порог не превышен - «цели нет»), которое поступает на третий вход ЛПД 3. Результат вычитания

с выхода первого блока вычитания 8 подается на первый вход блока деления 9. Со второго внешнего входа устройства сигнал Qi поступает на вход блока извлечения квадратного корня 10, с выхода которого

с выхода первого блока вычитания 8 подается на первый вход блока деления 9. Со второго внешнего входа устройства сигнал Qi поступает на вход блока извлечения квадратного корня 10, с выхода которого подается на вторые входы блока деления 9 и второго блока вычитания 8. В результате с выхода блока деления 9 снимается сигнал

подается на вторые входы блока деления 9 и второго блока вычитания 8. В результате с выхода блока деления 9 снимается сигнал  , поступающий на первые входы коммутатора 11 и второго блока вычитания 8, с выхода которого сигнал yi = xi -

, поступающий на первые входы коммутатора 11 и второго блока вычитания 8, с выхода которого сигнал yi = xi -  подается на второй вход коммутатора 11. В исходном состоянии первый вход коммутатора 11 соединен с его первым выходом, третий вход - со вторым выходом, в результате чего сигнал xi поступает на вход функционального преобразователя 12, реализующего выражение Ф (z) =

подается на второй вход коммутатора 11. В исходном состоянии первый вход коммутатора 11 соединен с его первым выходом, третий вход - со вторым выходом, в результате чего сигнал xi поступает на вход функционального преобразователя 12, реализующего выражение Ф (z) =  (функция Лапласа), с выхода которого значение Ф (xi) подается на первый вход первой ячейки памяти 13. При поступлении внешнего сигнала на управляющий вход коммутатора 11 происходит подключение второго и четвертого входов коммутатора соответственно к первому и третьему его выходам, в результате чего сигнал yi поступает на вход функционального преобразователя 12, с выхода которого значение Ф (yi) подается на первый вход второй ячейки памяти 13. По внешнему сигналу считывания, поступающему на управляющие вторые входы первой и второй ячеек памяти 13, сигналы Ф (xi) и Ф (yi) одновременно поступают на первые входы соответственно третьего и четвертого блоков вычитания, на вторые входы которых поступает внешний сигнал единичного уровня. С выходов третьего и четвертого блоков вычитания 8 сформированные сигналы -

(функция Лапласа), с выхода которого значение Ф (xi) подается на первый вход первой ячейки памяти 13. При поступлении внешнего сигнала на управляющий вход коммутатора 11 происходит подключение второго и четвертого входов коммутатора соответственно к первому и третьему его выходам, в результате чего сигнал yi поступает на вход функционального преобразователя 12, с выхода которого значение Ф (yi) подается на первый вход второй ячейки памяти 13. По внешнему сигналу считывания, поступающему на управляющие вторые входы первой и второй ячеек памяти 13, сигналы Ф (xi) и Ф (yi) одновременно поступают на первые входы соответственно третьего и четвертого блоков вычитания, на вторые входы которых поступает внешний сигнал единичного уровня. С выходов третьего и четвертого блоков вычитания 8 сформированные сигналы - = 1 - Ф (xi),

= 1 - Ф (xi),  = 1 - Ф (yi) поступают соответственно на первый и второй вход ЛПД 3, на третий вход которой поступает сигнал

= 1 - Ф (yi) поступают соответственно на первый и второй вход ЛПД 3, на третий вход которой поступает сигнал  с выхода порогового устройства 2. Эти сигналы через ЛПД 3 поступают на соответствующие входы процессора 6. Сформированный в процессоре 6 сигнал подается на вход общего порогового устройства 7, где он сравнивается с величиной порога h, поступающей на второй вход общего порогового устройства 7 в качестве внешнего сигнала. В зависимости от результата сравнения общее пороговое устройство 7 формирует общее решение

с выхода порогового устройства 2. Эти сигналы через ЛПД 3 поступают на соответствующие входы процессора 6. Сформированный в процессоре 6 сигнал подается на вход общего порогового устройства 7, где он сравнивается с величиной порога h, поступающей на второй вход общего порогового устройства 7 в качестве внешнего сигнала. В зависимости от результата сравнения общее пороговое устройство 7 формирует общее решение  в виде 1 (если порог превышен - «цель есть») или 0 (порог не превышен - «цели нет»).

в виде 1 (если порог превышен - «цель есть») или 0 (порог не превышен - «цели нет»).

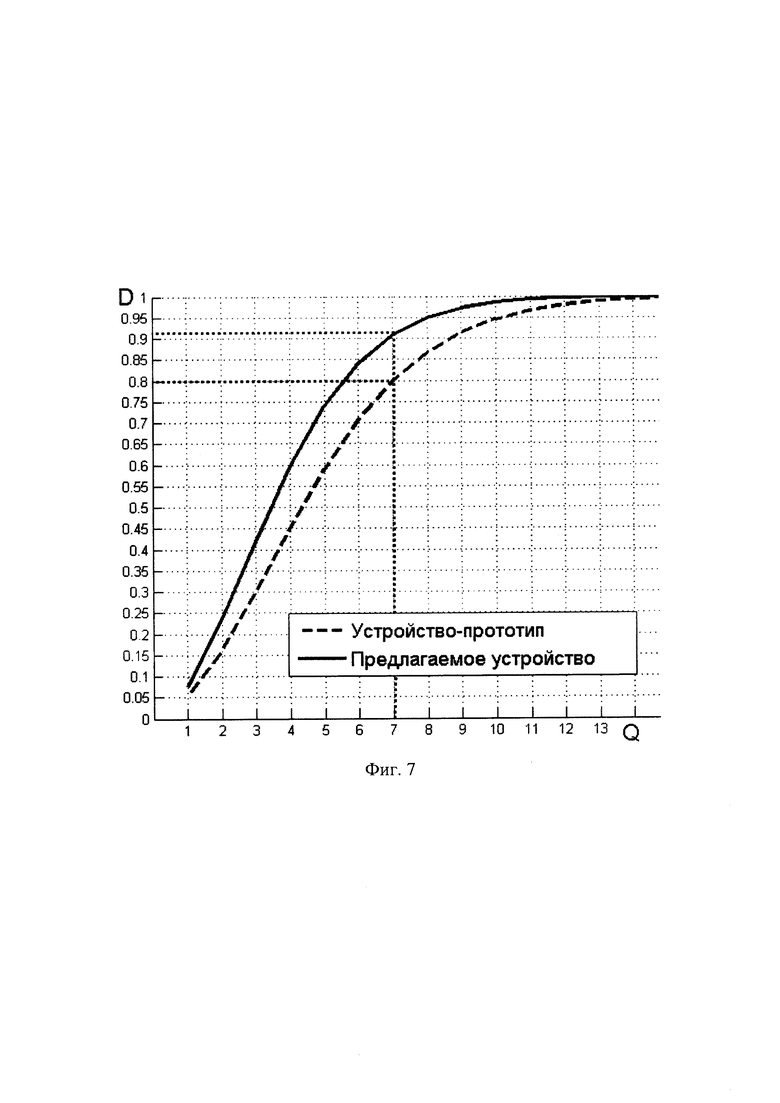

Поскольку получить аналитическое выражение для оценки вероятности правильного обнаружения цели предлагаемым комплексным устройством не удается, для подтверждения большей эффективности предлагаемого устройства по сравнению с прототипом было проведено статистическое компьютерное моделирование процесса приема сигнала трехканальными устройствами - прототипом и предлагаемым устройством. Входящие в их состав обнаружители имеют следующие общие характеристики:

первый обнаружитель - Q1 = 13; h1 = 8;

второй обнаружитель - Q2 = 13; h2 = 9;

третий обнаружитель - Q3 = 19; h3 = 12.

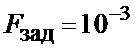

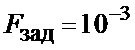

При этом значение порога в общем пороговом устройстве принималось равным h = 0,56 (выбор порога осуществлялся, исходя из заданной вероятности ложной тревоги  , что соответствует критерию Неймана-Пирсона).

, что соответствует критерию Неймана-Пирсона).

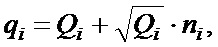

Для оценки вероятности правильного обнаружения цели полагаем, что цель есть ( ) и в каждом розыгрыше генерируем корреляционные интегралы с использованием соотношения [Информационные технологии в радиотехнических системах: учеб. пособие /В.А. Васин, И.Б. Власов, Ю.М. Егоров и др. - М.: Изд-во МГТУ им. Н.Э. Баумана, 2003. - С. 85]

) и в каждом розыгрыше генерируем корреляционные интегралы с использованием соотношения [Информационные технологии в радиотехнических системах: учеб. пособие /В.А. Васин, И.Б. Власов, Ю.М. Егоров и др. - М.: Изд-во МГТУ им. Н.Э. Баумана, 2003. - С. 85]

(2)

(2)

где ni - независимые стандартные (с нулевым математическим ожиданием и единичной дисперсией) гауссовские случайные величины.

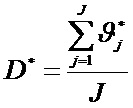

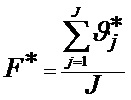

Результатом j-го розыгрыша процесса обнаружения комплексным устройством является решение  в виде 1 («цель есть») либо 0 («цели нет»). После проведения достаточно большого количества (J) розыгрышей получаем оценку вероятности правильного обнаружения как частоту соответствующего события

в виде 1 («цель есть») либо 0 («цели нет»). После проведения достаточно большого количества (J) розыгрышей получаем оценку вероятности правильного обнаружения как частоту соответствующего события  .

.

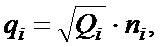

При необходимости получения оценки вероятности ложной тревоги меняется формула (2) розыгрыша значений корреляционных интегралов на соответствующую случаю отсутствия цели:

(3)

(3)

Далее процесс моделирования ничем не отличается от рассмотренного выше и после проведения большого количества (J) розыгрышей получаем оценку вероятности ложной тревоги  .

.

В результате проведения J = 106 розыгрышей процесса обнаружения для заданной вероятности ложной тревоги  были получены следующие результаты:

были получены следующие результаты:

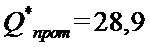

- для прототипа Dпрот* = 0,9891, Fпрот* = 10-3;

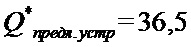

- для предлагаемого устройства Dпредл.устр* = 0,9984, Fпредл.устр* = 10-3.

Расчёт отношения сигнал/шум, являющегося показателем сложной помеховой обстановки, на выходах комплексных систем обнаружения прототипа и предлагаемого устройства осуществлялся по известной формуле [Жиронкин С. Б., Близнюк А. А., Слободянюк А. В. Алгоритм частично децентрализованной обработки апостериорной информации в комплексной системе обнаружения // Успехи современной радиоэлектроники. 2021. - № 2 (75). С. 51.]:

(4)

(4)

В результате расчетов были получены следующие значения отношения сигнал/шум:

- для прототипа  ;

;

- для предлагаемого устройства  .

.

Графики зависимости вероятности правильного обнаружения от отношения сигнал/шум (фиг.7) построены по формулам: [Жиронкин С. Б., Близнюк А. А., Слободянюк А. В. Алгоритм частично децентрализованной обработки апостериорной информации в комплексной системе обнаружения // Успехи современной радиоэлектроники. 2021. № 2 (75). С. 52.]

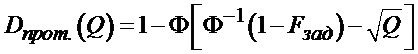

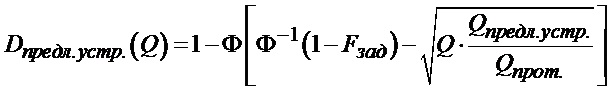

для прототипа:

, (5)

, (5)

для предлагаемого устройства с учетом энергетического выигрыша относительно прототипа:

. (6)

. (6)

Из анализа графиков следует, что независимо от условий помеховой обстановки (отношения сигнал/шум), прототип проигрывает предлагаемому устройству в эффективности обнаружения цели на всем интервале значений отношения сигнал/шум. Например, для значения отношения сигнал/шум  , значения вероятности правильного обнаружения составили:

, значения вероятности правильного обнаружения составили:

при применении прототипа Dпрот = 0,8;

при применении предлагаемого устройства Dпред.устр = 0,92.

Таким образом, использование заявленного устройства позволило повысить вероятность правильного обнаружения в заданных условиях сложной помеховой обстановки ( ) на

) на  15% по сравнению с прототипом.

15% по сравнению с прототипом.

Таким образом, в одинаковых с прототипом условиях помеховой обстановки предлагаемое устройство обеспечивает снижение степени влияния сложной помеховой обстановки на эффективность обнаружения воздушных объектов, что подтверждает выполнение поставленной цели изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Комплексное устройство обнаружения в многопозиционной радиолокационной станции | 2021 |

|

RU2778247C1 |

| Комплексное устройство обнаружения воздушных объектов | 2024 |

|

RU2835495C1 |

| Двухканальное устройство обнаружения | 2022 |

|

RU2791090C1 |

| Комплексная система обнаружения в многопозиционной радиолокационной станции | 2016 |

|

RU2608556C1 |

| КОМПЛЕКСНОЕ УСТРОЙСТВО ОБНАРУЖЕНИЯ В МНОГОПОЗИЦИОННОЙ РАДИОЛОКАЦИОННОЙ СТАНЦИИ | 2014 |

|

RU2556710C1 |

| КОМПЛЕКСНОЕ УСТРОЙСТВО ОБНАРУЖЕНИЯ | 2015 |

|

RU2587161C1 |

| Комплексный обнаружитель прямолинейной траектории воздушного объекта в пространстве с использованием преобразования Хафа | 2019 |

|

RU2732916C1 |

| Устройство синхронизации шумоподобных сигналов | 1985 |

|

SU1352663A1 |

| СПОСОБ ОБНАРУЖЕНИЯ СИГНАЛА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2169378C1 |

| УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ СИГНАЛОВ И ОПРЕДЕЛЕНИЯ НАПРАВЛЕНИЯ НА ИХ ИСТОЧНИК | 2012 |

|

RU2499276C1 |

Изобретение относится к технике радиолокации, радиосвязи, радионавигации и радиоуправления и может быть использовано в радиоэлектронных системах для решения задачи обнаружения сигналов. Технический результат - снижение степени влияния сложной помеховой обстановки на эффективность обнаружения воздушных объектов. Такой результат обеспечивается за счет дополнительного введения в каждый канал комплексного устройства обнаружения воздушных объектов третьего и четвертого блока вычитания, а в общую часть устройства введен процессор обработки данных, реализованный на основе обученной искусственной радиальной базисной нейронной сети. Перечисленные средства соответствующим образом соединены между собой и другими элементами устройства. 7 ил.

Комплексное устройство обнаружения воздушных объектов, являющееся многоканальным, содержащее общее пороговое устройство, второй вход которого является внешним входом сигнала общего порогового уровня, а в каждом канале согласованный фильтр, пороговое устройство, первый и второй блоки вычитания, блок деления, блок извлечения квадратного корня, коммутатор, функциональный преобразователь, первую и вторую ячейки памяти, линию передачи данных, причем выход согласованного фильтра в каждом канале подключен к первым входам порогового устройства и первого блока вычитания, второй вход которого соединен с первым внешним входом сигнала порогового уровня и со вторым входом порогового устройства, а выход - с первым входом блока деления, второй вход которого соединен со вторым входом второго блока вычитания и выходом блока извлечения квадратного корня, вход которого является вторым внешним входом устройства; выход блока деления подключен к первым входам коммутатора и второго блока вычитания, выход которого соединен со вторым входом коммутатора, первый выход которого подключен ко входу функционального преобразователя, выход которого соединен с третьим и четвертым входами коммутатора, управляющий вход которого является третьим внешним входом устройства, а второй и третий выходы коммутатора подключены к первым входам соответственно первой и второй ячеек памяти, вторые входы которых объединены и являются внешним входом считывания, отличающееся тем, что в общую часть устройства дополнительно введен процессор обработки данных, реализованный на основе обученной искусственной радиальной базисной нейронной сети, выход которого соединен со входом общего порогового устройства, а в каждый канал устройства дополнительно введены третий и четвертый блоки вычитания, первые входы которых соединены с выходами соответственно первой и второй ячеек памяти, вторые входы объединены и соединены с внешним входом сигнала единичного уровня, а выходы являются соответственно первым и вторым выходами канала устройства, третьим выходом которого является выход порогового устройства, причем эти выходы через линию передачи данных подключены к соответствующим входам процессора обработки данных.

| Комплексное устройство обнаружения в многопозиционной радиолокационной станции | 2021 |

|

RU2778247C1 |

| КОМПЛЕКСНОЕ УСТРОЙСТВО ОБНАРУЖЕНИЯ В МНОГОПОЗИЦИОННОЙ РАДИОЛОКАЦИОННОЙ СТАНЦИИ | 2014 |

|

RU2556710C1 |

| Способ распознавания типового состава групповой воздушной цели из класса "самолеты с турбореактивными двигателями" на основе калмановской фильтрации и нейронной сети | 2022 |

|

RU2786518C1 |

| US 2021208247 A1, 08.07.2021 | |||

| US 6366236 B1, 02.04.2002. | |||

Авторы

Даты

2024-03-26—Публикация

2023-11-17—Подача