Область техники

Заявляемое устройство относится к областям радиотехники, электроники и измерительной техники и предназначено для неискажённой передачи широкополосных сигналов в электронных системах различного назначения при однополярном питании.

Предшествующий уровень техники

В отличие от широко известных устройств передачи сигнала с биполярным питанием, для устройств с однополярным питанием получение выходного напряжения, близкого к нулю, оказывается непростой задачей. Например, если к выходному напряжению добавляется пьедестал для смещения этого напряжения ближе к нулю, то возникает необходимость точного поддержания заданного уровня этого пьедестала, особенно при малых передаваемых сигналах, когда их амплитуда может измеряться несколькими милливольтами. А уменьшение напряжения питания (особенно для мобильных устройств), что является основной тенденцией в указанных областях техники, приводит к острой необходимости снижения минимального неискажённого выходного напряжения для сохранения или расширения динамического диапазона передаваемых сигналов.

Поэтому проблема получения минимального («околонулевого») выходного напряжения в устройствах передачи сигнала, имеющих однополярное питание, является одной из актуальных проблем современной электроники, в том числе при разработке аналоговых и аналого-цифровых микросхем. Кроме того, для любых устройств передачи сигнала, в том числе имеющих однополярное питание, важной задачей является обеспечение высокой скорости нарастания сигнала, что необходимо для неискажённой передачи широкополосных сигналов.

Из уровня техники известно решение, описывающее использование операционного усилителя (ОУ) с однополярным питанием для передачи сигнала, раскрытое в спецификациях микросхемы OPA189, производимой Texas Instruments Incorporated (/data_sheets/ OPAx189 Precision, Lowest-Noise, 36-V, Zero-Drift, 14-MHz, MUX-Friendly, Rail-to-Rail Output Operational Amplifiers datasheet ((SBOS830I - SEPTEMBER 2017 - REVISED OCTOBER 2021). Известное решение представляет собой последовательное соединение входной цепи ОУ, рассчитанной на работу в диапазоне входных напряжений от минус 0,1 В до напряжения питания, уменьшенного на 2,5 В, и трёх усилительных модулей, обеспечивающих коэффициент передачи 170 дБ при разомкнутой цепи обратной связи.

Так как выходное напряжение в известном решении зависит от сопротивления нагрузки, то оно составляет от 20 мВ (при сопротивлении нагрузки 10 КОм) до 80 мВ (при сопротивлении нагрузки 2 КОм), что в ряде случаев является недопустимо большой величиной и приводит к искажениям «околонулевого» передаваемого сигнала. Недостатком известного решения является невозможность получить выходное напряжение, достаточно близкое к нулю, то есть пропорциональное передаваемому сигналу.

Известно также аналогичное техническое решение, раскрытое в описании патента US 9,548,707 «Output stage for near rail operation» (17 января 2017 г.).

Известное решение для неискажённой передачи низковольтных сигналов при однополярном питании содержит дифференциальный усилитель, имеющий неинвертирующий «+» и инвертирующий «-» входы, основной транзистор, включённый по схеме с общим эмиттером, генератор тока, буферный транзистор и схему задания выходного тока. При этом выход дифференциального усилителя подсоединён к управляющему электроду основного транзистора, генератор тока подсоединён к одному из электродов основного транзистора и к управляющему электроду буферного транзистора, а эмиттер буферного транзистора подсоединён к входу схемы задания выходного тока и одновременно является выходом устройства-аналога.

Недостатком известного решения является тот факт, что его выходное напряжение практически не может быть менее 2 мВ (см. US 9,548,707, столбец 3, строки 63 - 65). А этого на практике недостаточно для получения выходного напряжения, близкого к нулю, и, следовательно, для неискажённой передачи низковольтных сигналов.

Другим аналогом является техническое решение, раскрытое в описании публикации заявки на выдачу патента Китая CN 111930167 A «Output stage bleeder circuit applied to ultralow quiescent current LDO» (13 ноября 2020 г.).

Известное решение содержит ОУ, имеющий неинвертирующий «+» вход и инвертирующий «-» вход, который является входом устройства, транзистор, затвор которого подсоединён к выходу ОУ, а исток является выходом устройства, резистивный делитель, включённый между выходом устройства и источником тока, выполненным в виде токового зеркала, а также задатчик тока Ib, причём средняя точка делителя подсоединена к неинвертирующему «+» входу ОУ.

Недостатком известного решения является тот факт, что его использование не позволяет одновременно получить «околонулевое» выходное напряжение и достаточно высокую скорость нарастания сигнала.

Наиболее близким к предлагаемому техническому решению является устройство, известное из уровня техники и описанное в патенте США US 6.356,153 B1 «Rail-to-rail input/output operational amplifier and method» (12 марта 2002 г.). Указанное устройство, содержит входной каскад, два ОУ и выходной каскад. Для достижения целей предлагаемого технического решения существенной является часть известного устройства, состоящая из двух ОУ и выходного каскада, которая и выбрана в качестве прототипа. Таким образом, устройство, выбранное в качестве прототипа, содержит два ОУ, четыре транзистора, два резистора и схему обеспечения режима класса AB.

При этом первый электрод первого транзистора соединён с выходом первого ОУ, а второй электрод первого транзистора соединён с первым выводом схемы обеспечения режима класса AB и с первым электродом третьего транзистора. Первый вход первого ОУ предназначен для подсоединения к источнику сигнала, третий электрод первого транзистора соединён с другим входом первого ОУ, а также с первым выводом первого резистора, а третий электрод третьего транзистора подсоединён к второму выводу первого резистора.

Кроме того, первый электрод второго транзистора соединён с выходом второго ОУ, второй электрод второго транзистора соединён с вторым выводом схемы обеспечения режима класса AB и с первым электродом четвёртого транзистора, третий электрод второго транзистора соединён с одним из входов второго ОУ, а также с первым выводом второго резистора, третий электрод четвёртого транзистора подсоединён к второму выводу второго резистора, второй вход второго ОУ предназначен для подсоединения к источнику сигнала, а вторые электроды третьего и четвёртого транзисторов соединены между собой.

Общими признаками предлагаемого технического решения и устройства-прототипа являются: два ОУ, два транзистора и резистор, при этом первый вывод первого транзистора соединён с выходом первого ОУ, а первый вход первого ОУ предназначен для подсоединения к источнику сигнала.

Кроме того, первый вывод второго транзистора соединён с выходом второго ОУ, а третий вывод второго транзистора соединён с одним из входов второго ОУ и с первым выводом резистора.

Известное устройство работает в режиме усиления класса АВ, для которого характерны нелинейные искажения сигнала. Вследствие этого устройство-прототип не обеспечивает неискажённую передачу сигналов, в том числе широкополосных «околонулевых» сигналов.

Раскрытие сущности изобретения

Задачей заявленного решения является преодоление недостатков известных решений и создание устройства передачи сигнала, имеющего однополярное питание, предназначенного для неискажённой передачи сигналов в широком динамическом диапазоне, которое обеспечивало бы возможность получения минимального («околонулевого») выходного напряжения (доли милливольт) при подаче на его вход широкополосного «околонулевого» входного сигнала.

Технический результат, который невозможно достичь ни одним из известных решений, заключается в значительном расширении динамического диапазона устройств передачи сигнала, имеющих однополярное питание, при одновременном обеспечении высокой скорости нарастания выходного сигнала.

Указанный технический результат достигается тем, что в известное устройство, содержащее два ОУ, два транзистора и один резистор с их связями, введены узел обратной связи и задатчик выходного тока. При этом третий вывод первого транзистора подсоединён к второму выводу второго транзистора и точка их соединения предназначена для подключения нагрузки и узла обратной связи, который подсоединён также ко второму входу первого ОУ. Задатчик выходного тока подсоединён к другому входу второго ОУ. Вышеописанные соединения элементов заявленного устройства позволяют выделить в его составе стабилизатор тока, образованный вторым ОУ, вторым транзистором и резистором с их соединениями. Причём входом стабилизатора тока является выход задатчика выходного тока, а выходом стабилизатора тока является второй вывод резистора.

Заявляемое устройство имеет более простую структуру по сравнению с прототипом и в то же время обеспечивает возможность получения минимального («околонулевого») выходного напряжения (доли милливольт по сравнению с единицами и десятками милливольт у аналогов). При этом достигается высокая скорость нарастания выходного сигнала, что необходимо для неискажённой передачи широкополосных сигналов, а также отсутствуют нелинейные искажения благодаря использованию режима усиления класса А.

В результате значительно расширяется динамический диапазон устройств передачи широкополосного сигнала, имеющих однополярное питание.

Также для патентной защиты представлено заявленное техническое решение, выполненное в виде интегральной микросхемы, содержащей ряд элементов заявленного устройства.

В данном варианте осуществления заявленного технического решения указанный технический результат достигается тем, что устройство, выполненное в виде интегральной микросхемы, содержит совокупность ряда элементов предлагаемой схемы, а именно два ОУ, два транзистора, и резистор. Выход первого ОУ соединён с первым электродом первого транзистора, выход второго ОУ соединён с первым электродом второго транзистора. Второй вход первого ОУ соединён с выводом интегральной микросхемы, предназначенным для подачи входного сигнала. Третий электрод второго транзистора подсоединён к первому входу второго ОУ и к выводу резистора. При этом третий электрод первого транзистора соединён со вторым электродом второго транзистора, и точка их соединения соединена с выводом интегральной микросхемы, который предназначен для подключения нагрузки, а также для подсоединения первого вывода узла обратной связи, внешнего по отношению к интегральной микросхеме.

Дополнительно интегральная микросхема снабжена выводом для подключения второго вывода внешнего узла обратной связи. Упомянутый вывод микросхемы соединён с вторым входом первого ОУ и может также использоваться для подключения источника второго входного сигнала. Дополнительно интегральная микросхема может быть снабжена выводом соединённым с вторым входом второго ОУ и предназначенным для подключения внешнего задатчика тока.

Краткое описание прилагаемых чертежей

Заявляемое техническое решение поясняется далее с помощью фигур, на которых представлены некоторые из возможных вариантов реализации устройства передачи сигнала.

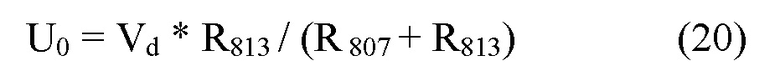

На Фиг. 1 представлена схема устройства-прототипа.

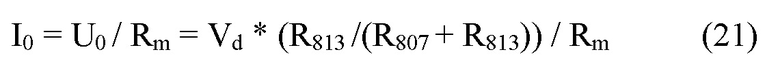

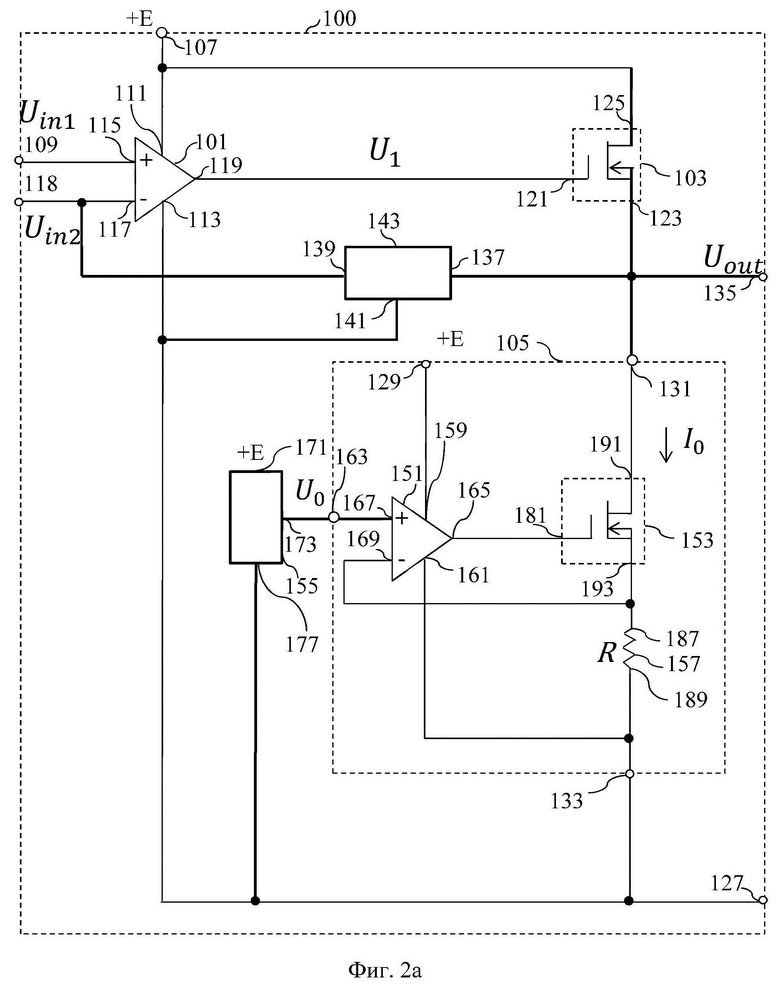

На Фиг. 2a представлено схематическое изображение заявленного устройства в сравнении с прототипом.

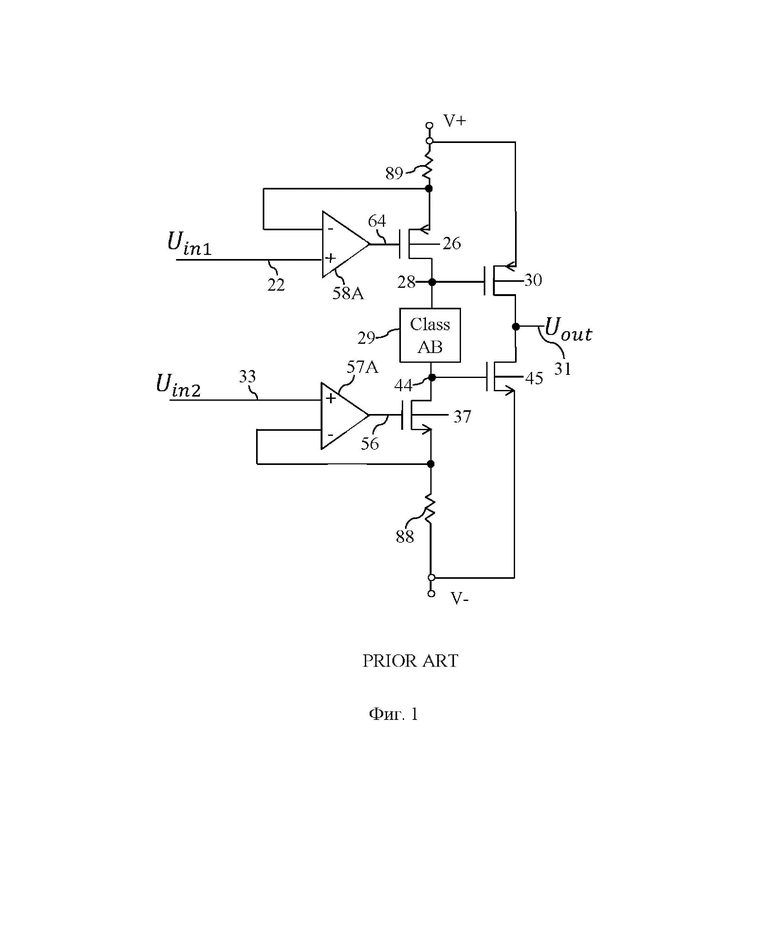

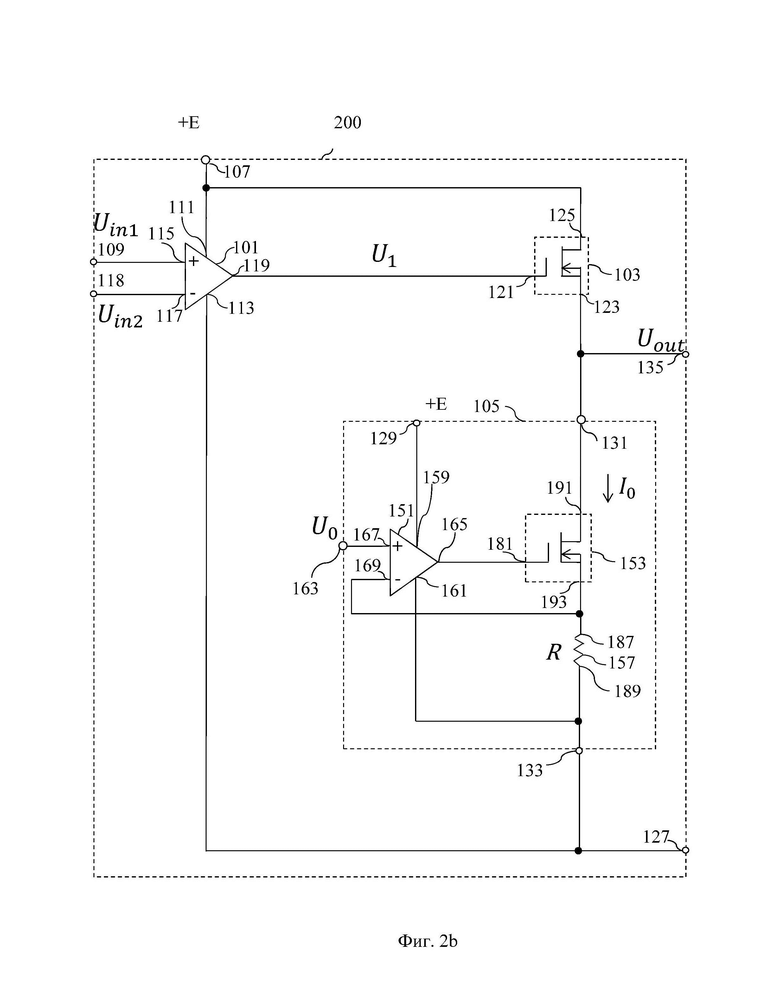

На Фиг. 2b представлено схематическое изображение заявленного устройства, выполненного в виде интегральной микросхемы.

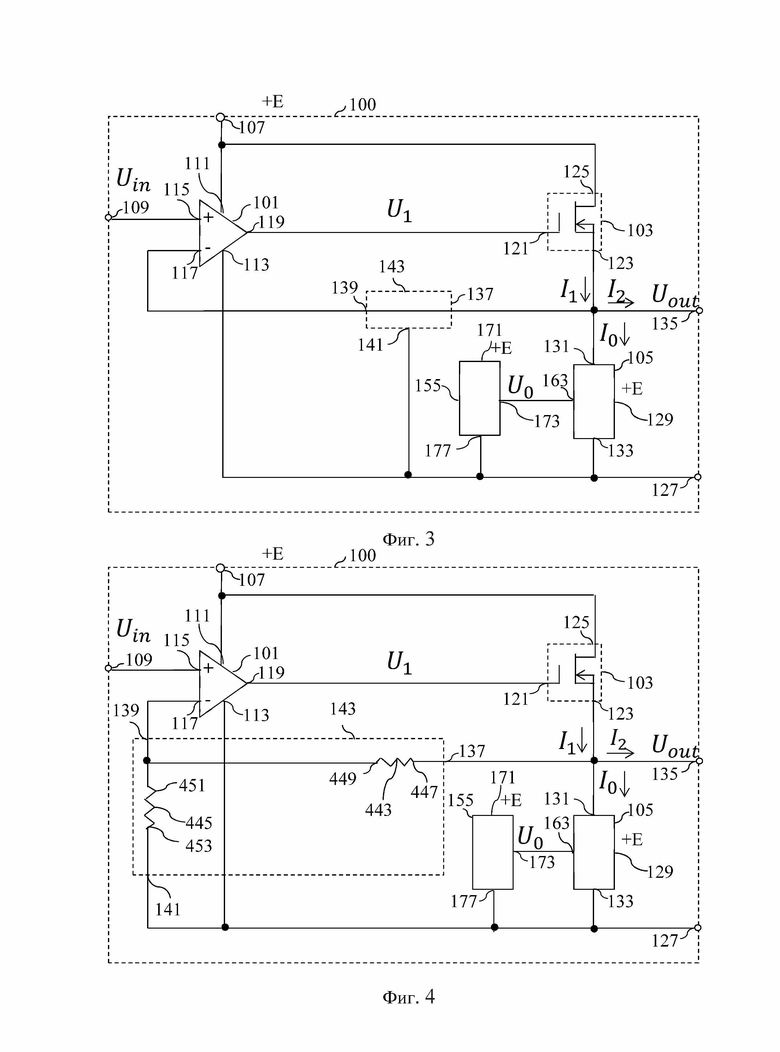

На Фиг. 3 представлена схема заявленного устройства для одного из возможных вариантов реализации.

На Фиг. 4 представлена схема заявленного устройства для другого возможного варианта реализации.

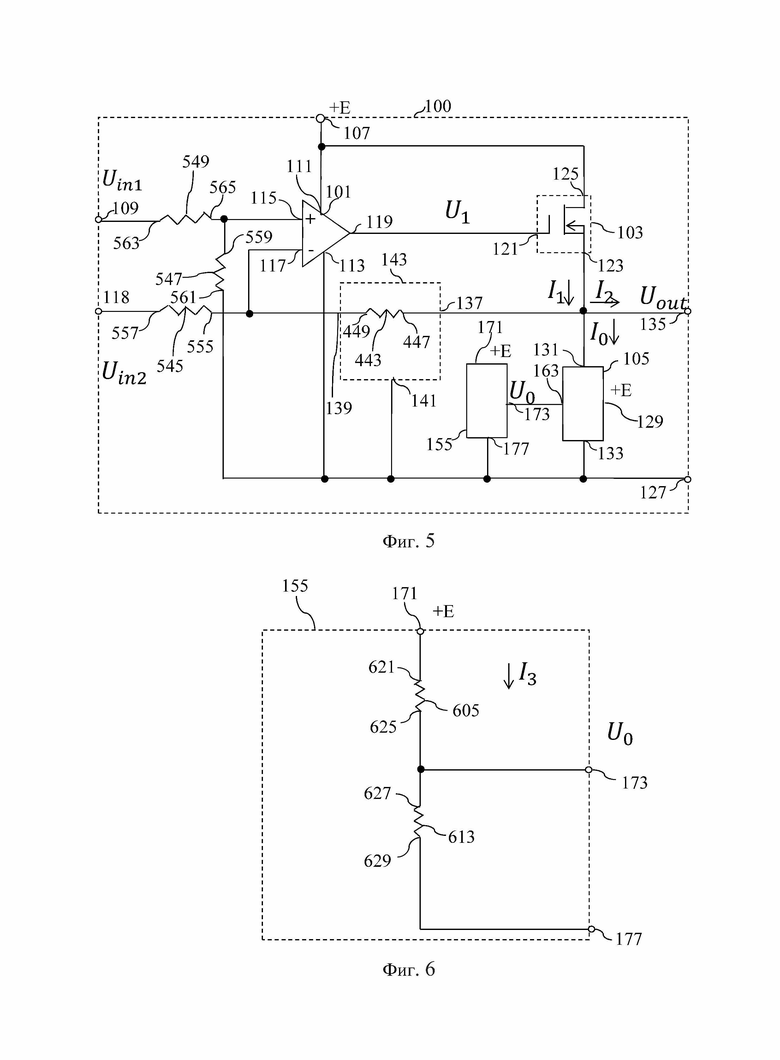

На Фиг. 5 представлена схема заявленного устройства для третьего возможного варианта реализации.

На Фиг. 6 представлена схема одного из возможных вариантов реализации задатчика выходного тока для стабилизатора тока в заявленном устройстве.

На Фиг. 7 представлена схема другого возможного варианта реализации задатчика выходного тока для стабилизатора тока в заявленном устройстве.

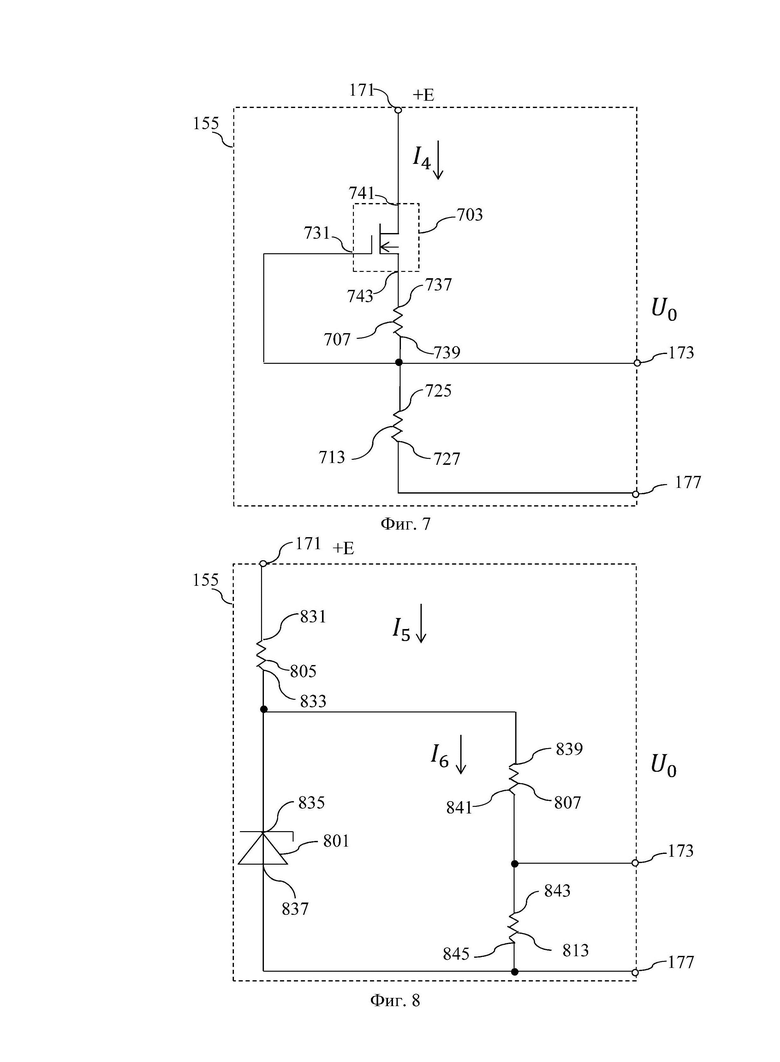

На Фиг. 8 представлена схема третьего возможного варианта реализации задатчика выходного тока для стабилизатора тока в заявленном устройстве.

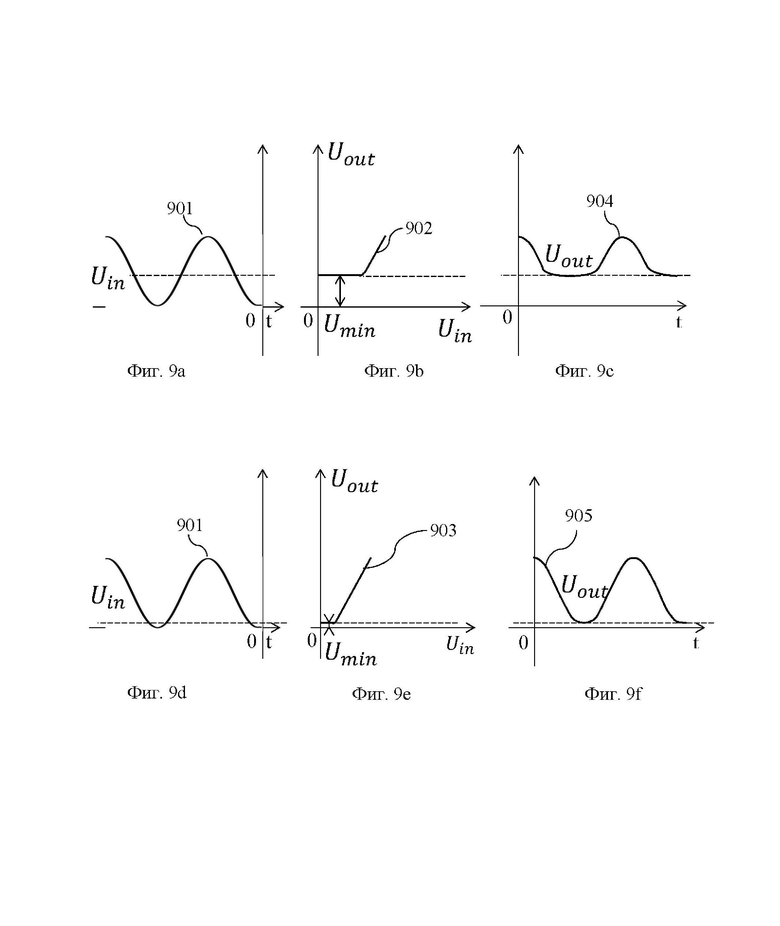

На Фиг. 9a-9f представлены графики, иллюстрирующие снижение уровня искажений передаваемого сигнала при использовании заявленного технического решения.

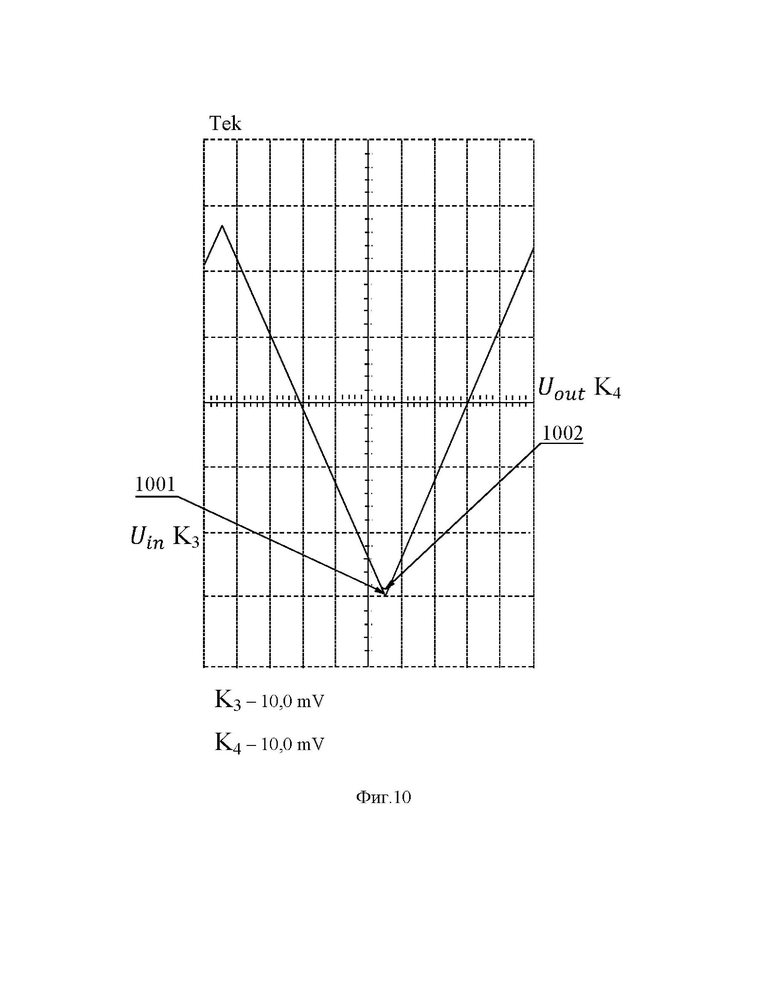

На Фиг. 10 представлены результаты экспериментов, подтверждающих достижение заявленного технического результата (скриншот с экрана осциллографа).

Детальное описание прилагаемых чертежей

Далее со ссылками на фигуры поясняются конструкция и работа заявленного устройства.

На Фиг. 1 изображена часть устройства, известного из уровня техники (см. патент US 6.356,153 B1). Устройство-прототип содержит: два ОУ (58A; 57A), четыре транзистора (26; 30; 37; 45), два резистора (89; 88) и схему обеспечения режима класса AB (29), причём устройство-прототип имеет два входа (22; 33), подсоединённые к входам первого и второго ОУ, соответственно, а выходом устройства является точка соединения (31) третьих электродов третьего и четвёртого транзисторов.

Схематическое изображение заявленного устройства в сравнении с прототипом представлено на Фиг. 2a, где устройство в целом обозначено 100. Заявленное устройство содержит, например: 101 - первый ОУ, 103 - первый транзистор (в схеме, представленной на Фиг.2 - полевой МОП-транзистор), 155 - задатчик выходного тока, 107 - вывод устройства, предназначенный для подключения к положительному полюсу источника питания (ИП), 109 - первый входной вывод устройства, 111, 113 - первый и второй выводы питания первого ОУ 101 соответственно, 115 - первый (на фиг.2а - неинвертирующий «+») вход первого ОУ 101, подсоединённый к первому входному выводу 109 устройства, 117 - второй (на фиг.2а - инвертирующий «-») вход первого ОУ 101, подсоединённый к второму входному выводу 118 устройства, 119 - выход первого ОУ 101, подсоединённый к первому (управляющему) выводу 121 первого транзистора 103 (в схеме, представленной на Фиг. 2a - затвор). Второй вывод 125 первого транзистора 103 (в схеме, представленной на Фиг. 2a - сток), соединён с первым выводом 111 питания первого ОУ 101 и подсоединён к выводу 107 устройства, предназначенному для подключения к положительному полюсу ИП, а второй вывод питания 113 первого ОУ 101 соединен с выводом 127 устройства, который предназначен для подключения к общему проводу (корпусу) и отрицательному полюсу ИП. Третий вывод 123 первого транзистора 103 (в схеме, представленной на Фиг. 2a - исток) соединён с вторым выводом 191 (в схеме, представленной на Фиг. 2a - сток) второго транзистора 153 (в схеме, представленной на Фиг.2 - полевой МОП-транзистор), точка их соединения соединена с выводом 135 устройства, предназначенным для подключения нагрузки.

Третий вывод 193 второго транзистора 153 (в схеме, представленной на Фиг. 2a - исток) подсоединён к первому входу 169 (на фиг.2а - инвертирующий «-») второго ОУ 151 и к первому выводу 187 резистора 157.

Первый (управляющий) вывод 181 второго транзистора 153 (в схеме, представленной на Фиг. 2а - затвор), подсоединён к выходу 165 второго ОУ 151.

Первый вывод питания 159 второго ОУ 151 подсоединён к контакту 129, который предназначен для подключения к положительному полюсу ИП, а второй вывод питания 161 второго ОУ 151 и второй вывод 189 резистора 157 подсоединены к выводу 127 устройства 100, который предназначен для подключения к общему проводу (корпусу) и отрицательному полюсу ИП

Первый вывод 137 узла обратной связи (УОС) 143 подсоединён к общей точке первого транзистора 103 и второго транзистора 153, второй вывод 139 УОС 143 подсоединён к второму входу 117 первого ОУ 101, третий вывод 141 УОС 143 подсоединён к выводу 127 устройства 100.

Как уже отмечалось выше, второй ОУ 151, второй транзистор 153 и резистор 157 с их соединениями образуют стабилизатор тока 105, входом которого является контакт 131, подсоединённый к второму выводу 191 второго транзистора 153 и к выводу 135 устройства 100. Выходом стабилизатора тока является контакт 133, подсоединённый к второму выводу 189 резистора 157 и к выводу 127 устройства 100, а потенциал, управляющий значением тока стабилизатора тока 105, подаётся с второго вывода 173 задатчика выходного тока 155 через контакт 163 стабилизатора тока 105, на второй вход 167 (на фиг.2а - неинвертирующий «+») второго операционного усилителя 151.

При этом контакт 171 задатчика тока 155 и контакт 129 стабилизатора тока 105 предназначены для подсоединения к положительному полюсу ИП, а вывод 177 задатчика тока 155 подсоединён к выводу 127.

На схеме, представленной на Фиг. 2a, условно не показаны: ИП, источник входного сигнала и нагрузка, которые должны быть подключены к соответствующим выводам устройства.

В целях лучшего понимания заявленного технического решения, схема которого представлена на Фиг. 2a, утолщёнными линиями показаны связи и элементы, отсутствующие в устройстве-прототипе, благодаря введению которых достигается заявленный технический результат. В том числе отмечены УОС и задатчик тока с их связями.

Схематическое изображение заявленного устройства, выполненного в виде интегральной микросхемы, представлено на Фиг. 2b, где устройство в целом обозначено 200. Заявленное устройство содержит: 101 - первый ОУ, 103 - первый транзистор (в схеме, представленной на Фиг.2b - полевой МОП-транзистор), 105 - стабилизатор тока, реализованный аналогично Фиг.2а. Устройство 200 также снабжено выводами: 107 - вывод, предназначенный для подключения к положительному полюсу ИП, 135 - вывод, предназначенный для подключения нагрузки и внешнего УОС, 127 - вывод, предназначенный для подключения к отрицательному полюсу ИП, 109 - первый входной вывод, предназначенный для подключения к источнику сигнала, 118 - второй входной вывод, предназначенный для подключения к внешнему УОС и к другому источнику сигнала и 163 - вывод, предназначенный для подключения к выходу задатчика тока.

Первый вход 115 (на Фиг. 2b - неинвертирующий «+») первого ОУ 101 подсоединён к первому входному выводу 109 устройства 200, 117 - второй вход (на Фиг. 2b - инвертирующий «-») первого ОУ 101 подсоединён к второму входному выводу 118 устройства 200, 121 - первый (управляющий) электрод первого транзистора 103 (в схеме, представленной на Фиг. 2b - затвор), подсоединён к выходу 119 первого ОУ 101. Второй электрод 125 первого транзистора 103 (в схеме, представленной на Фиг. 2b - сток), соединён с первым выводом питания 111 первого ОУ 101 и подсоединён к выводу 107 устройства, предназначенному для подключения к положительному полюсу ИП. Второй вывод питания 113 первого ОУ 101 соединён с выводом 127 устройства 200.

Точка соединения третьего электрода 123 первого транзистора 103 (в схеме, представленной на Фиг. 2b - исток) и первого вывода 131 стабилизатора тока 105 соединена с выводом 135 устройства 200. Выход 133 стабилизатора тока 105, подсоединён к выводу 127 устройства 200, предназначенному для подключения к отрицательному полюсу ИП. Контакт 129 стабилизатора тока 105 предназначен для подсоединения к положительному полюсу ИП.

На схеме, представленной на Фиг. 2b, условно не показаны: ИП, источник входного сигнала и нагрузка, УОС и задатчик выходного тока с их связями, которые должны быть подключены к соответствующим выводам интегральной микросхемы 200.

Схема заявленного устройства для одного из возможных вариантов реализации представлена на Фиг. 3, где устройство в целом обозначено 100. Схема содержит 101 - ОУ, 103 - транзистор, 105 - стабилизатор тока, 155 - задатчик выходного тока и УОС 143. При этом 107 - вывод устройства, предназначенный для подключения к положительному полюсу ИП, 109 - первый входной вывод устройства, 111 и 113 - первый и второй выводы питания ОУ 101 соответственно. ОУ 101 также имеет первый (на Фиг. 3 - неинвертирующий «+») вход 115, подсоединённый к первому входному выводу 109 устройства, второй (на Фиг. 3 - инвертирующий «-») вход 117, а также выход 119, подсоединённый к первому (управляющему) выводу 121 транзистора 103 (на Фиг. 3 - затвор). Третий вывод 123 транзистора 103 (на Фиг. 3 - исток) подсоединён к первому выводу 131 стабилизатора тока 105 и к выводу 135 устройства 100, предназначенному для подключения нагрузки, а второй вывод 125 транзистора 103 (на Фиг. 3 - сток) соединён с первым выводом питания 111 ОУ 101 и подсоединён к выводу 107 устройства 100, предназначенному для подключения к положительному полюсу ИП.

При этом вывод питания 129 стабилизатора тока 105 также предназначен для подключения к положительному полюсу ИП. Кроме того, схема содержит вывод устройства 127, предназначенный для подключения к отрицательному полюсу ИП, соединённый общим проводом (корпусом) устройства с вторым выводом питания 113 ОУ 101, вторым выводом 133 стабилизатора тока 105 и с выводом 177 задатчика выходного тока 155. Вывод 163 стабилизатора тока 105 соединён с вторым выводом 173 задатчика выходного тока 155.

В качестве УОС 143 использован обычный проводник, соединяющий первый 137 и второй 139 выводы УОС 143. Первый вывод 137 УОС 143 подсоединён к точке соединения транзистора 103 и стабилизатора тока 105, второй вывод 139 УОС 143 подсоединён к второму входу 117 ОУ 101, третий, незадействованный, вывод 141 УОС 143 подсоединён к выводу 127 устройства.

Контакт 171 задатчика выходного тока 155 и контакт 129 стабилизатора тока 105 предназначены для подсоединения к положительному полюсу ИП.

Для подключения нагрузки предназначен вывод 135 устройства, соединённый с первым выводом 131 стабилизатора тока 105, с третьим выводом 123 транзистора 103 и с первым выводом 137 УОС 143.

На схеме, представленной на Фиг. 3, условно не показаны: ИП, источник входного сигнала и нагрузка, которые должны быть подключены к соответствующим выводам устройства.

Схема заявленного устройства для другого из возможных вариантов реализации представлена на Фиг. 4, где устройство в целом обозначено 100. Схема содержит: 101 -ОУ, 103 - транзистор, 105 - стабилизатор тока, 155 - задатчик выходного тока и УОС 143. При этом 107 - вывод устройства, предназначенный для подключения к положительному полюсу ИП, 109 - первый входной вывод устройства 100, 111 и 113 - первый и второй выводы питания ОУ 101 соответственно. ОУ 101 также имеет первый (на Фиг. 4 - неинвертирующий «+») вход 115, подсоединённый к первому входному выводу 109 устройства 100, второй (на Фиг. 4 - инвертирующий «-») вход 117, а также выход 119, подсоединённый к первому (управляющему) электроду 121 транзистора 103 (на Фиг. 4 - затвор). Третий вывод 123 транзистора 103 (на Фиг. 3 - исток) подсоединён к первому выводу 131 стабилизатора тока 105 и к выводу 135 устройства, предназначенному для подключения нагрузки, а второй электрод 125 транзистора 103 (на Фиг. 4 - сток) соединён с первым выводом питания 111 ОУ 101 и подсоединён к выводу 107 устройства, предназначенному для подключения к положительному полюсу ИП. При этом вывод питания 129 стабилизатора тока 105 также предназначен для подключения к положительному полюсу ИП. Кроме того, схема содержит вывод устройства 127, предназначенный для подключения к отрицательному полюсу ИП, соединённый общим проводом (корпусом) устройства с вторым выводом питания 113 ОУ 101, вторым выводом 133 стабилизатора тока 105 и с выводом 177 задатчика выходного тока 155. Вывод 163 стабилизатора тока 105 соединён с вторым выводом 173 задатчика выходного тока 155. Контакт 171 задатчика выходного тока 155 и контакт 129 стабилизатора тока 105 предназначены для подсоединения к положительному полюсу ИП.

Также на схеме, представленной на Фиг. 4, показан УОС 143, в состав которого входят первый делитель, содержащий первый резистор 443 и второй резистор 445. Первый вывод 447 первого резистора 443 подсоединён к первому выводу 137 УОС 143, а второй вывод 449 первого резистора 443 подсоединён ко второму выводу 139 УОС 143 и к первому выводу 451 второго резистора 445. Первый вывод 451 второго резистора 445 соединён со вторым выводом 449 первого резистора 443, а второй вывод 453 второго резистора 445 соединён с выводом 141 УОС 143. При этом первый вывод 137 УОС 143 подсоединён к точке соединения транзистора 103 и стабилизатора тока 105, второй вывод 139 УОС 143 подсоединён к второму входу 117 ОУ 101, третий вывод 141 УОС 143 подсоединён к выводу 127 устройства 100. Для подключения нагрузки предназначен вывод 135 устройства 100 , соединённый с первым выводом 131 стабилизатора тока 105, с третьим выводом 123 транзистора 103 и с первым выводом 137 УОС 143.

На схеме, представленной на Фиг. 4, условно не показаны: ИП, источник входного сигнала и нагрузка, которые должны быть подключены к соответствующим выводам устройства.

Схема заявленного устройства для третьего возможного варианта реализации представлена на Фиг. 5, где устройство в целом обозначено 100. Схема содержит: 101 - ОУ, 103 - транзистор, 105 - стабилизатор тока, 155 - задатчик выходного тока и УОС 143. При этом 107 - вывод устройства 100, предназначенный для подключения к положительному полюсу ИП, 109 - первый входной вывод устройства 100, 111 и 113 - первый и второй выводы питания ОУ 101 соответственно. ОУ 101 также имеет первый (на Фиг. 5 - неинвертирующий «+») вход 115, подсоединённый к первому входному выводу 109 устройства, второй (на Фиг. 5 - инвертирующий «-») вход 117, а также выход 119, подсоединённый к первому (управляющему) электроду 121 транзистора 103 (на Фиг. 5 - затвор). Третий вывод 123 транзистора 103 (на Фиг. 5 - исток) подсоединён к первому выводу 131 стабилизатора тока 105 и к выводу 135 устройства, предназначенному для подключения нагрузки, а второй электрод 125 транзистора 103 (на Фиг. 5 - сток) соединён с первым выводом питания 111 ОУ 101 и подсоединён к выводу 107 устройства, предназначенному для подключения к положительному полюсу ИП. При этом вывод питания 129 стабилизатора тока 105 также предназначен для подключения к положительному полюсу ИП. Кроме того, схема содержит вывод устройства 127, предназначенный для подключения к отрицательному полюсу ИП, соединённый общим проводом (корпусом) устройства с вторым выводом питания 113 ОУ 101, вторым выводом 133 стабилизатора тока 105 и с выводом 177 задатчика выходного тока 155. Вывод 163 стабилизатора тока 105 соединён с вторым выводом 173 задатчика выходного тока 155. Контакт 171 задатчика выходного тока 155 и контакт 129 стабилизатора тока 105 предназначены для подсоединения к положительному полюсу ИП.

Устройство 100, схема которого изображена на Фиг. 5, также содержит УОС 143, в состав которого входит резистор 443, при этом первый вывод 447 резистора 443 подсоединён к первому выводу 137 УОС 143, второй вывод 449 резистора 443 подсоединён к второму выводу 139 УОС 143. Первый вывод 137 УОС 143 подсоединён к точке соединения транзистора 103 и стабилизатора тока 105, второй вывод 139 УОС 143 подсоединён к второму входу 117 ОУ 101, третий, незадействованный, вывод 141 УОС 143 подсоединён к выводу 127 устройства 100.

Кроме того, устройство 100, схема которого изображена на Фиг. 5, дополнительно снабжено вторым входным выводом 118, а также содержит третий резистор 545, четвёртый резистор 547 и пятый резистор 549, при этом четвёртый, 547, и пятый, 549, резисторы представляют собой второй делитель напряжения (547; 549). Упомянутый второй входной вывод 118 подсоединён к первому выводу 557 третьего резистора 545, второй вывод 555 которого подсоединён к второму входу 117 ОУ 101 и к второму выводу 139 УОС 143. К первому входу 115 (на Фиг. 5 - неинвертирующему «+») ОУ 101 подсоединён первый вывод 559 четвёртого резистора 547, второй вывод 561 которого подсоединён к выводу 127 устройства 100. Пятый резистор 549 подсоединён своим первым входом 563 к первому входному выводу 109 устройства 100, а своим вторым выводом 565 подсоединён к первому входу 115 ОУ 101.

На схеме, представленной на Фиг. 5, условно не показаны: ИП, источники входных сигналов и нагрузка, которые должны быть подключены к соответствующим выводам устройства.

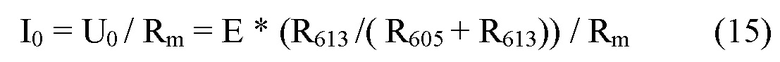

На Фиг. 6 представлена схема одного из возможных вариантов реализации задатчика выходного тока 155 (в виде третьего делителя напряжения) в заявленном устройстве. Данная схема может быть включена в конструкцию любого из устройств, реализующих заявленное техническое решение, в том числе, но не только, в конструкции устройств, реализованных по схемам, представленным на Фиг. 3, 4 и 5. Цифрами на схеме, представленной на Фиг. 6, обозначены: задатчик выходного тока 155 в целом, первый резистор 605 третьего делителя напряжения и второй резистор 613 третьего делителя напряжения. При этом первый вывод 621 первого резистора 605 подсоединён к первому выводу 171 задатчика выходного тока 155, который предназначен для подключения его к положительному полюсу ИП, второй вывод 629 второго резистора 613 подсоединён к третьему выводу 177 задатчика выходного тока 155, который предназначен для подключения его к отрицательному полюсу ИП, а второй вывод 625 первого резистора 605 и первый вывод 627 второго резистора 613 подсоединены к второму выводу 173 задатчика выходного тока 155, который предназначен для подключения к стабилизатору тока 105.

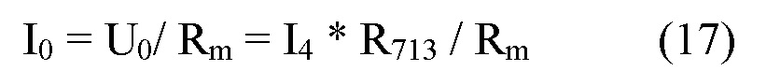

На Фиг. 7 представлена схема другого возможного варианта реализации задатчика выходного тока 155 в заявленном устройстве (с использованием полевого транзистора и четвертого делителя напряжения). Данная схема может быть включена в конструкцию любого из устройств, реализующих заявленное техническое решение, в том числе, но не только, в конструкции устройств, реализованных по схемам, представленным на Фиг. 3, 4 и 5. Цифрами на схеме, представленной на Фиг. 7, обозначены: в целом задатчик выходного тока 155, полевой транзистор 703, первый резистор 707, второй резистор 713 (являющиеся первым и вторым элементами четвертого делителя напряжения). Сток 741 полевого транзистора 703 подсоединён к первому выводу 171 задатчика выходного тока 155, который предназначен для подключения его к положительному полюсу ИП, исток 743 полевого транзистора 703 подсоединён к первому выводу 737 первого резистора 707, затвор 731 полевого транзистора 703 подсоединён к точке соединения второго вывода 739 первого резистора 707 и первого вывода 725 второго резистора 713, и к второму выводу 173 задатчика выходного тока 155, который предназначен для подключения к стабилизатору тока 105. При этом второй вывод 727 второго резистора 713 подсоединён к третьему выводу 177 задатчика выходного тока 155, который предназначен для подключения его к отрицательному полюсу ИП.

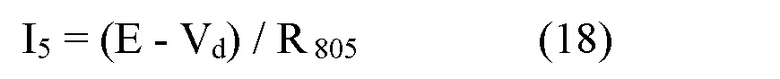

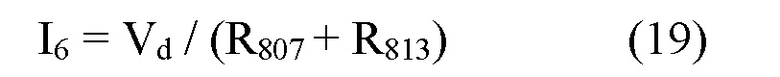

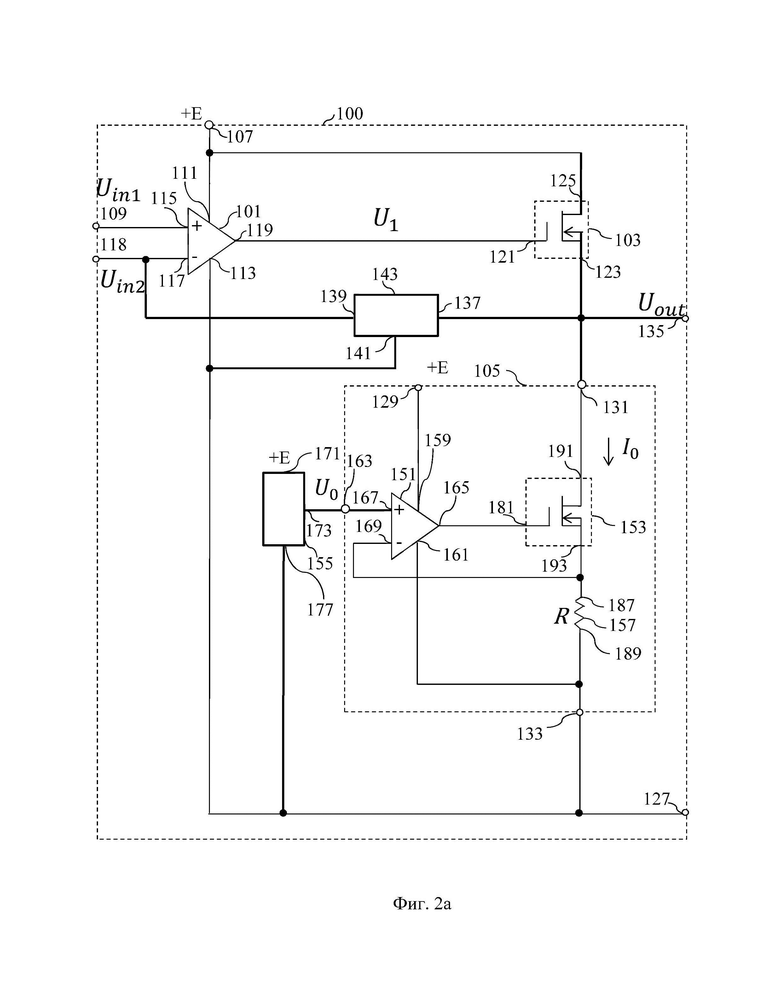

На Фиг. 8 представлена схема ещё одного возможного варианта реализации задатчика выходного тока 155 в заявленном устройстве (с использованием источника опорного напряжения и пятого делителя напряжения). Данная схема может быть включена в конструкцию любого из устройств, реализующих заявленное техническое решение, в том числе, но не только, в конструкции устройств, реализованных по схемам, представленным на Фиг. 3, 4 и 5. Цифрами на схеме, представленной на Фиг. 8, обозначены: в целом задатчик выходного тока 155, источник опорного напряжения 801, первый резистор 805, второй резистор 807, третий резистор 813 (являющиеся первым вторым и третьим элементами пятого делителя напряжения). Первый вывод 831 первого резистора 805 подсоединён к первому выводу 171 задатчика выходного тока 155, который предназначен для подключения его к положительному полюсу ИП, второй вывод 833 первого резистора 805 подсоединён к первому выводу 835 источника опорного напряжения 801 и к первому выводу 839 второго резистора 807, второй вывод 841 второго резистора 807 подсоединён к первому выводу 843 третьего резистора 813 и к второму выводу 173 задатчика выходного тока 155, который предназначен для подключения к стабилизатору тока 105. Второй вывод 845 третьего резистора 813 подсоединён к третьему выводу 177 задатчика выходного тока 155, который предназначен для подключения его к отрицательному полюсу ИП, и к второму выводу 837 источника опорного напряжения 801.

На Фиг. 9a - 9f представлены графики, иллюстрирующие снижение уровня искажений передаваемого сигнала при использовании заявленного технического решения. Цифрами на графиках обозначены: 901- входной сигнал, 902 - амплитудная характеристика известных технических решений, 903 - амплитудная характеристика заявленного технического решения, 904 - выходной сигнал известных технических решений (искажённый), 905 - выходной сигнал заявленного технического решения.

На Фиг. 10 представлены осциллограммы входного и выходного сигналов заявленного устройства, подтверждающих достижение заявленного технического результата. Цифрами на рисунке обозначены: 1001 - осциллограмма входного испытательного напряжения, 1002 - осциллограмма выходного напряжения.

Подробное описание осуществления изобретения

Устройство 100 для передачи сигнала, имеющее однополярное питание, в одном из возможных вариантов реализации работает в режиме повторителя напряжения (см. Фиг. 3). При подаче входного сигнала напряжением Uin на вывод 109 устройства, предназначенный для подключения к источнику входного сигнала, и последующем поступлении Uin на первый, неинвертирующий вход 115 ОУ 101, на выходе 119 ОУ 101 возникает напряжение U1, поступающее на первый (управляющий) электрод 121 транзистора 103, который работает в линейном режиме. Стабилизатор тока 105 формирует постоянный стабильный ток I0 , величина которого зависит от напряжения U0, которое поступает на управляющий вход 163 стабилизатора тока 105 с второго вывода 173 задатчика выходного тока 155.

Параметры стабилизатора тока 105 выбираются таким образом, чтобы минимальное падение напряжения на нём (между его выводами 131 и 133), Umin cs, соответствующее началу режима стабилизации тока, было бы равно, например, 0,2 мВ (или другой величине, обеспечивающей неискажённую передачу сигналов).

Протекание тока I0 через стабилизатор тока 105 создаёт на выводах 131 и 133 последнего выходное напряжение Uout, которое с выводов устройства 135 и 127, подсоединённых, соответственно, к выводам 131 и 133 стабилизатора тока 105, передаётся в нагрузку (на схеме, представленной на Фиг. 3, условно не показана).

Ток I1, текущий через транзистор 103, определяется и током I0 стабилизатора тока 105, и током нагрузки I2 = Uout/R, где R - активное сопротивление нагрузки.

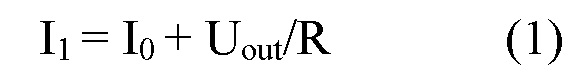

Если нагрузка подсоединена между выводами устройства 135 и 127, тогда:

и необходимо, чтобы значение этого тока не превышало максимально допустимого для транзистора 103.

Если нагрузка подсоединена между выводами устройства 135 и 107, тогда:

и необходимо, чтобы значение этого тока было не меньше величины, обеспечивающей линейный режим работы транзистора 103.

С первого вывода 131 стабилизатора тока 105 напряжение Uout через УОС 143, выполненный в виде проводника, поступает на инвертирующий (“-”) вход 117 ОУ 101, благодаря чему формируется цепь глубокой обратной связи: ОУ 101 - транзистор 103 - УОС 143 - ОУ 101. Если выходное напряжение Uout на инвертирующем (“-”) входе 117 ОУ 101 по какой-то причине станет меньше, чем значение Uin на его неинвертирующем (“+”) входе 115, то напряжение U1 на первом (управляющем) электроде 121 транзистора 103 увеличивается и приоткрывает транзистор 103, в результате чего увеличивается выходное напряжение Uout предлагаемого устройства, которое достигает значения Uin, и начинает выполняться соотношение:

С другой стороны, если выходное напряжение Uout на инвертирующем (“-”) входе 117 ОУ 101 будет больше, чем значение Uin на неинвертирующем (“+”) входе 115 ОУ 101, то напряжение U1 на первом (управляющем) электроде 121 транзистора 103 уменьшается и призакрывает транзистор 103, в результате чего уменьшается выходное напряжение Uout предлагаемого устройства, которое достигает значения Uin, и снова начинает выполняться соотношение (3).

Следовательно, выходное напряжение Uout для схемы, представленной на Фиг. 3, всегда практически равно напряжению входного сигнала Uin.

Коэффициент передачи К заявленного устройства, выполненного по схеме, представленной на Фиг. 3, равен единице, поэтому оно выполняет функции повторителя напряжения.

Стандартные ОУ с однополярным питанием (например: OPA189, OPA365 производства фирмы Texas Instruments, и другие), которые можно использовать в качестве ОУ 101 в заявленном устройстве, не в состоянии обеспечить напряжение U1 на выходе 119 ОУ 101 меньше, чем несколько десятков милливольт. Однако U1 в заявленном устройстве, выполненном по схеме, представленной на Фиг. 3, всегда превышает значение Uout на величину разности потенциалов между управляющим электродом 121 транзистора 103 и его третьим электродом 123, подсоединённым к первому выводу 131 стабилизатора тока 105. Именно эта разность потенциалов обеспечивает смещение выходного напряжения U1 стандартного ОУ 101 в сторону «околонулевых» значений на выходе заявленного устройства и, следовательно, способствует значительному снижению уровня искажений при передаче «околонулевых» сигналов при однополярном питании, тем самым способствует расширению динамического диапазона устройств передачи сигнала, имеющих однополярное питание. (Сказанное обеспечивается, если напряжение затвор-исток транзистора 103 превышает минимальное выходное напряжение ОУ 101, см. Umin на Фиг. 9e).

При увеличении входного напряжения Uin до единиц вольт (зависит от параметров стандартного ОУ 101) схема ведёт себя точно таким же образом, т.е. обеспечивает соотношение (3), при этом значение Uout всегда меньше, чем U1, на величину разности потенциалов между управляющим электродом 121 транзистора 103 и его третьим электродом 123. Так же работает и устройство 200, выполненное в виде интегральной микросхемы (с тем лишь отличием, что УОС 143 и задатчик выходного тока 155 могут быть внешними по отношению к микросхеме и подключаться к ранее указанным выводам).

Для случаев, когда требуется получить коэффициент передачи, превышающий единицу, например, 1,5 или 10, или любое другое технически реализуемое значение (режим усиления), УОС 143 будет содержать делитель напряжения, выполненный, например, в виде резистивного делителя.

Схема такого варианта заявляемого устройства представлена на Фиг. 4 (схема усилителя). Устройство 100 в этом случае работает следующим образом. При подаче на вывод 109 устройства, предназначенный для подключения к источнику входного сигнала (и, соответственно, на неинвертирующий (“+”) вход 115 ОУ 101) входного сигнала напряжением Uin, на выходе 119 ОУ 101 возникает напряжение U1, поступающее на первый (управляющий) электрод 121 транзистора 103, который работает в линейном режиме. Стабилизатор тока 105 формирует постоянный стабильный ток I0, величина которого зависит от напряжения U0, которое поступает на управляющий вход 163 стабилизатора тока 105 с второго вывода 173 задатчика выходного тока 155. Параметры стабилизатора тока 105 выбираются таким образом, чтобы минимальное падение напряжения на нём (между его выводами 131 и 133), Umin cs, соответствующее началу режима стабилизации тока, было бы равно, например, 0,2 мВ (или другой величине, обеспечивающей неискажённую передачу сигналов).

Протекание тока I0 через стабилизатор тока 105 создаёт на выводах 131 и 133 последнего, выходное напряжение Uout, которое с выводов устройства 135 и 127, подсоединённых, соответственно, к выводам 131 и 133 стабилизатора тока 105, передаётся в нагрузку (на схеме, представленной на Фиг. 4, условно не показана).

Ток I1, текущий через транзистор 103, определяется и током I0 стабилизатора тока 105, и током нагрузки I2 = Uout/R, где R - активное сопротивление нагрузки.

Если нагрузка подсоединена между выводами устройства 135 и 127, тогда выполняется соотношение (1). В этом случае необходимо, чтобы значение этого тока не превышало максимально допустимого для транзистора 103.

Если нагрузка подсоединена между выводами устройства 135 и 107, тогда выполняется соотношение (2), и необходимо, чтобы значение этого тока было не меньше величины, обеспечивающей линейный режим работы транзистора 103.

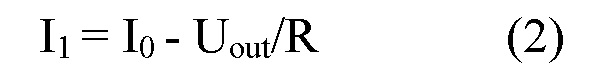

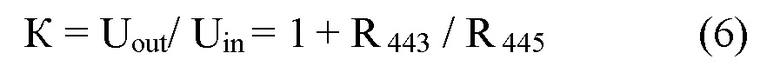

С первого вывода 131 стабилизатора тока 105 напряжение Uout поступает на инвертирующий «-» вход 117 ОУ 101 через УОС 143, содержащий первый делитель напряжения (образованный первым и вторым резисторами 443 и 445), благодаря чему формируется цепь обратной связи: ОУ 101 - транзистор 103 - УОС 143 - ОУ 101. При этом на инвертирующий «-» вход 117 ОУ 101 поступает напряжение

где R 443, R445 - номинальные значения сопротивлений первого 443 и второго 445 резисторов, соответственно.

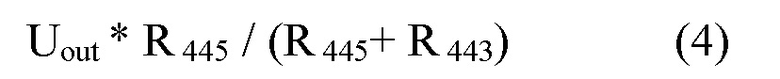

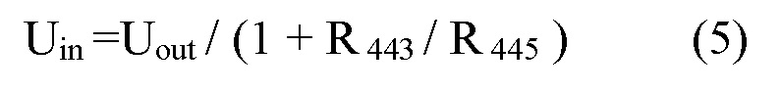

Если значение этого напряжения по какой-то причине меньше, чем значение Uin на первом входе 115 ОУ 101, то напряжение U1 на первом (управляющем) выводе 121 транзистора 103 увеличивается и приоткрывает транзистор 103, в результате чего увеличивается выходное напряжение Uout предлагаемого устройства. Указанное увеличенное напряжение через УОС 143, содержащий первый делитель напряжения (443, 445), снова поступает на второй вход 117 ОУ 101, и этот процесс происходит до тех пор, пока не начнёт выполняться соотношение:

С другой стороны, если значение напряжения Uout* (1 + R443 / R445), на инвертирующем «-» входе 117 ОУ 101 будет больше, чем значение Uin на его неинвертирующем «+» входе 115, то напряжение U1 на первом (управляющем) выводе 121 транзистора 103 будет уменьшаться и закрывать транзистор 103. В результате этого уменьшается выходное напряжение Uout предлагаемого устройства. Это уменьшенное напряжение через УОС 143, содержащий первый делитель напряжения (443, 445), снова поступает на инвертирующий «-» вход 117 ОУ 101, пока снова не начнёт выполняться соотношение (5).

Следовательно, выходное напряжение Uout для схемы, представленной на Фиг. 4, практически всегда равно напряжению входного сигнала Uin с коэффициентом передачи:

Таким образом, достигается коэффициент передачи заявленного устройства, выполненного по схеме Фиг. 4, превышающий единицу, например, 1,5 или 10, или любое другое технически реализуемое значение (в зависимости от соотношения номиналов R 443 и R445), поэтому оно выполняет функции усилителя.

Стандартные ОУ с однополярным питанием (например: OPA189, OPA365 производства фирмы Texas Instruments, и другие), которые можно использовать в качестве ОУ (101) в заявленном устройстве, не в состоянии обеспечить напряжение U1 на выходе 119 ОУ 101 меньше, чем несколько десятков милливольт. Однако U1 в заявленном устройстве, выполненном по схеме, представленной на Фиг. 4, всегда превышает значение Uout на величину разности потенциалов между управляющим электродом 121 транзистора 103 и его третьим электродом 123, подсоединённым к первому выводу 131 стабилизатора тока 105. Именно эта разность потенциалов обеспечивает смещение выходного напряжения U1 стандартного ОУ 101 в сторону «околонулевых» значений на выходе заявленного устройства и, следовательно, способствует значительному снижению уровня искажений при передаче низковольтных сигналов при однополярном питании, тем самым способствует расширению динамического диапазона устройств передачи сигнала, имеющих однополярное питание. (Сказанное обеспечивается, если напряжение затвор-исток транзистора 103 превышает минимальное выходное напряжение ОУ 101, см. Umin на Фиг. 9e).

При увеличении входного напряжения Uin до единиц вольт (зависит от параметров стандартного ОУ 101) схема ведёт себя точно таким же образом, т.е. обеспечивает соотношение (5), при этом значение Uout всегда меньше, чем U1, на величину разности потенциалов между управляющим электродом 121 транзистора 103 и его третьим электродом 123. Так же работает и устройство 200, выполненное в виде интегральной микросхемы (с тем лишь отличием, что УОС 143 и задатчик выходного тока 155 могут быть внешними по отношению к микросхеме).

Для случаев, когда необходимо получить разность двух напряжений и эту разность усилить, ослабить или передать без изменения (режим дифференциального усиления) схема устройства будет содержать дополнительный вход, подсоединённый к инвертирующему «-» входу операционного усилителя через дополнительный резистор. Кроме того, схема устройства будет содержать второй делитель напряжения, включённый между основным входом устройства и входом операционного усилителя.

Такая схема (третий возможный вариант реализации) представлена на Фиг. 5 (схема дифференциального усилителя). Устройство 100 в этом случае работает следующим образом. На вывод устройства 109, предназначенный для подключения к первому источнику входного сигнала (на рисунке не показан), подаётся первый входной сигнал напряжением Uin1 Через второй делитель напряжения, образованный пятым резистором 549 и четвёртым резистором 547, напряжение Uin1 поступает на неинвертирующий (“+”) вход 115 ОУ 101, а на инвертирующий «-» вход 117 ОУ 101 с вывода 118 устройства через третий резистор 545 поступает второй входной сигнал напряжением Uin2. При этом на выходе 119 ОУ 101 возникает напряжение U1, которое поступает на первый (управляющий) электрод 121 транзистора 103, который работает в линейном режиме.

Стабилизатор тока 105 формирует постоянный стабильный ток I0, величина которого зависит от напряжения U0, которое поступает на управляющий вход 163 стабилизатора тока 105 с второго вывода 173 задатчика выходного тока 155. Параметры стабилизатора тока 105 выбираются таким образом, чтобы минимальное падение напряжения на нём (между его выводами 131 и 133), Umin cs, соответствующее началу режима стабилизации тока, было бы равно, например: 0,2 мВ (или другой величине, обеспечивающей неискажённую передачу сигналов).

Протекание тока I0 через стабилизатор тока 105 создаёт на выводах 131 и 133 последнего выходное напряжение Uout, которое с выводов устройства 135 и 127, подсоединённых, соответственно, к выводам 131 и 133 стабилизатора тока 105, передаётся в нагрузку (на схеме, представленной на Фиг. 5, условно не показана).

Ток I1, текущий через транзистор 103, определяется и током I0 стабилизатора тока 105, и током нагрузки I2 = Uout/R, где R - активное сопротивление нагрузки.

Если нагрузка подсоединена между выводами устройства 135 и 127, тогда выполняется соотношение (1). В этом случае необходимо, чтобы значение этого тока не превышало максимально допустимого для транзистора 103. Если нагрузка подсоединена между выводами устройства 135 и 107, тогда выполняется соотношение (2), и необходимо, чтобы значение этого тока было не меньше величины, обеспечивающей линейный режим работы транзистора 103.

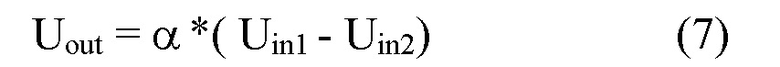

В то же время часть выходного напряжения Uout через УОС 143, содержащий первый резистор 443, поступает на инвертирующий «-» вход 117 ОУ 101 (причём первый резистор 443 и третий резистор 545 образуют шестой делитель напряжения). Выходное напряжение Uout в схеме, представленной на Фиг. 5, связано с входными напряжениями Uin1, Uin2 известным соотношением:

где

α - дифференциальный коэффициент передачи входных напряжений;

R443, R545, R547, R549 - номинальные значения сопротивлений первого 443, третьего 545, четвёртого 547 и пятого 549 резисторов, соответственно.

При реализации конкретных устройств по данному варианту строгое соблюдение условия (8) не обязательно: номиналы первого 443, третьего 545, четвёртого 547 и пятого 549 резисторов могут быть выбраны, исходя из задачи, решаемой устройством.

В зависимости от номинальных значений сопротивлений резисторов, дифференциальный коэффициент α может быть больше единицы, меньше единицы, или равен единице, что позволяет разность двух напряжений усилить, ослабить или передать без изменения. Таким образом, выходное напряжение Uout всегда пропорционально разности напряжений входных сигналов Uin1 - Uin2.

Кроме того, в этом варианте устройства достигается возможность усиления или ослабления разности двух напряжений при соответствующем выборе номиналов первого 443, третьего 545, четвёртого 547 и пятого 549 резисторов, поэтому оно выполняет функции дифференциального усилителя.

Стандартные ОУ с однополярным питанием (например: OPA189, OPA365 производства фирмы Texas Instruments и другие), которые можно использовать в качестве ОУ (101) в заявленном устройстве, не в состоянии обеспечить напряжение U1 на выходе 119 ОУ 101 меньше, чем несколько десятков милливольт. Однако U1 в заявленном устройстве, выполненном по схеме, представленной на Фиг. 5, всегда превышает значение Uout на величину разности потенциалов между управляющим электродом 121 транзистора 103 и его третьим электродом 123, соединённым с первым выводом 131 стабилизатора 105 тока. Именно эта разность потенциалов обеспечивает смещение выходного напряжения U1 стандартного ОУ 101 в сторону «околонулевых» значений на выходе заявленного устройства и, следовательно, способствует значительному снижению уровня искажений при передаче низковольтных сигналов при однополярном питании, тем самым способствует расширению динамического диапазона устройств передачи сигнала, имеющих однополярное питание (сказанное обеспечивается, если напряжение затвор-исток транзистора 103 превышает минимальное выходное напряжение ОУ 101, см. Umin на Фиг. 9e).

При увеличении входных напряжений Uin1, Uin2 до единиц вольт (зависит от параметров стандартного ОУ 101) схема ведёт себя точно таким же образом, т.е. обеспечивает соотношение (7), при этом значение Uout всегда меньше, чем U1, на величину разности потенциалов между управляющим электродом 121 транзистора 103 и его третьим электродом 123. Так же работает и устройство 200, выполненное в виде интегральной микросхемы (с тем лишь отличием, что УОС 143 и задатчик выходного тока 155 могут быть внешними по отношению к микросхеме).

Помимо вариантов реализации заявленного технического решения, которые приведены на представленных схемах: Фиг.3, Фиг. 4 и Фиг.5 и описаны выше, возможны и другие схемы устройств, отличающиеся подключением к входам и выходу ОУ различных сочетаний электрорадиоэлементов, как это показано, например, в уже упоминавшемся источнике: спецификации ОУ OPA189.

Далее приведено описание работы стабилизатора тока 105 по схеме согласно Фиг. 2a. Данная схема может быть включена в конструкцию и в работу всех возможных вариантов реализации заявленного технического решения, в частности, но не только, по схемам, представленным на Фиг.3, Фиг.4, Фиг.5.

При наличии на выводах 135 и 127 заявленного устройства выходного напряжения Uout, оно оказывается приложенным к выводам 131 и 133 стабилизатора тока 105 и распределяется между вторым транзистором 153, т.е. между его электродами 181 и 193, и резистором 157, т.е. между выводами последнего 187 и 189.

Напряжение с вывода 187 резистора 157 поступает на первый вход 169 второго ОУ 151 и сравнивается с напряжением U0 на втором входе 167 второго ОУ 151, которое поступает с второго вывода 173 задатчика выходного тока 155 через вывод 163 стабилизатора тока 105. Если напряжение на первом входе 169 второго ОУ 151 больше, чем напряжение U0 на его втором входе 167, то на выходе 165 второго ОУ 151 формируется сигнал рассогласования, поступающий на управляющий электрод 181 второго транзистора 153, работающего в линейном режиме. Под действием указанного сигнала рассогласования этот транзистор призакрывается, ток через него уменьшается, и напряжение на выводе 187 резистора 157 (а, следовательно, и на первом входе 169 второго ОУ 151) становится равным напряжению U0 на его втором входе 167. Напротив, если напряжение на первом входе 169 второго ОУ 151 меньше, чем напряжение на его втором входе 167, то на выходе 165 второго ОУ 151 изменяется уровень сигнала рассогласования, поступающего на управляющий электрод 181 второго транзистора 153. Под действием указанного сигнала рассогласования второй транзистор 153 приоткрывается, ток через него увеличивается, и напряжение на выводе 187 резистора 157, а, следовательно, и на первом входе 169 второго ОУ 151 снова становится равным напряжению U0 на его втором входе 167.

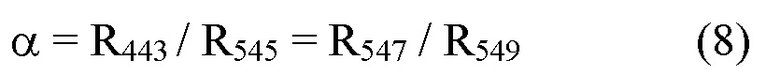

Таким образом, в стабилизаторе тока 105, выполненном согласно схеме, представленной на Фиг. 2a, всегда выполняется соотношение:

где

Rm - номинал сопротивления резистора 157;

U0 - напряжение на втором выводе 173 задатчика выходного тока 155.

Иными словами, через стабилизатор тока 105 всегда протекает постоянный стабильный ток:

величина которого задаётся напряжением U0 на выходе задатчика выходного тока 155 (на его втором выводе 173).

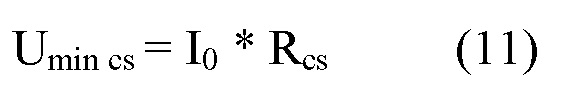

Падение напряжения между выводами 131 и 133 стабилизатора тока 105 Umin cs, соответствующее началу режима стабилизации тока, определяется формулой:

где

I0 - постоянный стабильный ток стабилизатора тока 105;

Rcs - сопротивление между выводами 131 и 133 стабилизатора тока 105,

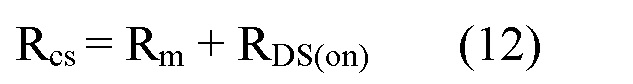

причём:

где

Rm - номинал сопротивления резистора 157;

RDS(on) - сопротивление канала второго транзистора 153 в открытом состоянии, (англ: Static Drain-to-Source On-State Resistance, т.е. RDS(on)).

Выбирая соответствующим образом номинал R сопротивления резистора 157 и подбирая второй транзистор 153 с нужным RDS(on), можно без труда обеспечить выполнение ранее сформулированного условия, чтобы напряжение между выводами 131 и 133 стабилизатора тока 105 Umin cs, соответствующее началу режима стабилизации тока, было равно, например: 0,2 мВ (или другой величине, обеспечивающей неискажённую передачу сигналов).

Величина сопротивления канала второго транзистора 153 в открытом состоянии RDS(on) для получения Umin cs равного, например: 0,2 мВ, должна составлять несколько сотен миллиОм. При этом паразитные ёмкости сток-исток и затвор-сток второго транзистора 153 могут иметь значения нескольких десятков пикофарад каждая, что препятствует неискажённой передаче широкополосных сигналов. Однако в заявляемом техническом решении ёмкость затвор-сток шунтируется выходным сопротивлением второго ОУ 151, а влияние ёмкости сток-исток нейтрализуется обратной связью по цепи: исток 193 второго транзистора 153 - первый вход 169 второго ОУ 151 - его же выход 165 - затвор 181 второго транзистора 153. В результате достигается высокая скорость нарастания выходных сигналов.

С учётом сказанного схема, представленная на Фиг. 2a, обеспечивает значительное расширение динамического диапазона устройств передачи сигнала, имеющих однополярное питание, при одновременном обеспечении высокой скорости нарастания выходного сигнала, чем достигается заявленный технический результат.

Переходя к описанию задатчика выходного тока 155, показанного в общем виде на схеме Фиг.2a, следует отметить, что он может быть реализован самыми разными способами. Схема одного из возможных вариантов реализации задатчика выходного тока 155 для стабилизатора тока 105 в заявленном устройстве представлена на Фиг. 6. Схема работает следующим образом.

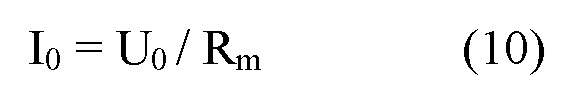

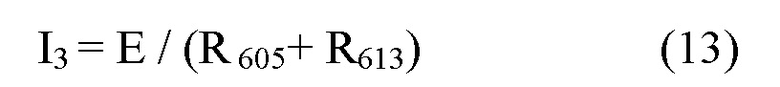

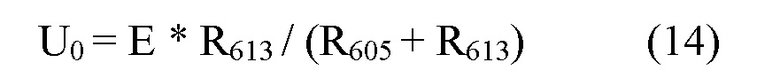

При подаче на первый вывод 171 задатчика выходного тока 155 напряжения питания Е, через последовательно соединённые резисторы 605 и 613 задатчика выходного тока 155 начинает течь постоянный ток величиной:

где R605 и R613 - номинальные значения сопротивлений первого 605 и второго 613 резисторов задатчика выходного тока 155, соответственно. В результате на втором выводе 173 задатчика выходного тока 155 появляется напряжение U0, численно равное падению напряжения от тока I3 на втором резисторе 613 задатчика выходного тока 155:

Используя формулу (10), получим, что через стабилизатор тока 105 в случае использования задатчика выходного тока 155, выполненного по схеме, представленной Фиг. 6, будет протекать постоянный стабильный ток:

Выбирая соответствующим образом значения E, R613, R605 и Rm, можно всегда обеспечить требуемую величину тока I0. Следовательно, задатчик выходного тока 155, показанный на схеме Фиг. 6, обеспечивает работоспособность стабилизатора тока 105 схемы, представленной на Фиг. 2a, и всего заявленного устройства в целом.

Однако схеме, представленной на Фиг. 6, присущ недостаток, заключающийся в зависимости выходного напряжения U0 от величины напряжения питания E, которое может быть нестабильным.

Схема другого возможного варианта реализации задатчика выходного тока 155 для стабилизатора тока 105 в заявленном устройстве, обладающая повышенной стабильностью напряжения U0, представлена на Фиг. 7. Схема работает следующим образом.

При подаче на первый вывод 171 задатчика выходного тока 155 напряжения питания Е, через последовательно соединённые полевой транзистор 703, первый 707 и второй 713 резисторы задатчика выходного тока 155 начинает течь постоянный ток I4. Согласно свойствам полевого транзистора, если напряжение сток-исток между электродами 741 (сток) и 743 (исток) полевого транзистора 703 задатчика выходного тока 155 превышает величину напряжения отсечки (характерный параметр для полевых транзисторов), то ток I4 между этими электродами не зависит от приложенного напряжения сток-исток, а зависит только от свойств полевого транзистора и от напряжения затвор-исток. Величина напряжения затвор-исток между электродами 731 и 743 полевого транзистора 703 задатчика выходного тока 155 определяется падением напряжения на первом резисторе 707 и равна I4 * R707. При этом на втором резисторе 713 формируется падение напряжения:

где R707 и R713 - номинальные значения сопротивлений первого и второго резисторов задатчика выходного тока 155.

И это напряжение U0, не зависящее от напряжения питания Е, поступает на второй вывод 173 задатчика выходного тока 155. Используя формулу (10), получим, что через генератор тока 105 в случае использования задатчика выходного тока 155, выполненного по схеме, представленной на Фиг. 7, будет протекать постоянный стабильный ток:

Выбирая соответствующим образом полевой транзистор 703, а также значения R713 и Rm, можно всегда обеспечить требуемую величину тока I0. Следовательно, задатчик выходного тока 155, показанный на схеме Фиг. 7, обеспечивает работоспособность стабилизатора тока 105 и всего заявленного устройства в целом. При этом стабильность напряжения U0 (а, следовательно, и тока I0 стабилизатора тока 105) намного выше, чем в схеме, представленной на Фиг. 6, поскольку ток I3 полевого транзистора 703 намного стабильнее, чем напряжение питания Е.

Схема третьего возможного варианта реализации задатчика выходного тока 155 для стабилизатора тока 105 в заявленном устройстве, обладающая повышенной стабильностью напряжения U0, представлена на Фиг. 8. Схема работает следующим образом.

При подаче на первый вывод 171 задатчика выходного тока 155 напряжения питания Е, через последовательно соединённые первый, второй и третий резисторы 805, 807 и 813 задатчика выходного тока 155 начинает течь постоянный ток. Причём через первый резистор 805 течёт ток I5, равный:

где Vd - напряжение между выводами 835 и 837 источника опорного напряжения 801 задатчика выходного тока 155;

а через второй и третий резисторы 807 и 813 течёт ток, равный:

В результате на первом выводе 843 третьего резистора 813 и, следовательно, на втором выводе 173 задатчика выходного тока 155 появляется напряжение U0, не зависящее от напряжения питания Е и численно равное падению напряжения от тока I3 на третьем резисторе 813 задатчика выходного тока 155:

Используя формулу (10), получим, что через стабилизатор тока 105 в случае использования задатчика выходного тока 155, выполненного по схеме, представленной на Фиг.8, будет протекать постоянный стабильный ток:

Выбирая соответствующим образом значения E, R813, R807 и Rm, можно всегда обеспечить требуемую величину тока I0. Следовательно, задатчик выходного тока 155, показанный на схеме Фиг. 8, обеспечивает работоспособность стабилизатора тока 105 и всего заявленного устройства в целом. При этом стабильность напряжения U0 (а, следовательно, и тока I0 стабилизатора тока 105) намного выше, чем в схеме, представленной на Фиг. 6, поскольку напряжение Vd между выводами 835 и 837 источника 801 опорного напряжения намного стабильнее, чем напряжение питания Е.

На основе вышеизложенного, достижение заявленного технического результата иллюстрируется графиками, представленными на Фиг. 9a - 9f, где видно:

901 - входной неискажённый сигнал имеет вид синусоиды с минимальным значением, равным нулю;

902 - реальная амплитудная характеристика известных технических решений имеет существенную нелинейность в начальной области, что приводит к искажениям «околонулевых» сигналов;

903 - амплитудная характеристика заявленного технического решения близка к линейной, что способствует уменьшению искажений «околонулевых» сигналов;

904 - выходной сигнал известных технических решений имеет искажённый вид за счёт уплощения синусоиды в области малых значений;

905 - выходной сигнал заявленного технического решения имеет значительно меньшие искажения синусоиды в области малых значений, что позволяет расширить динамический диапазон устройств передачи сигналов, имеющих однополярное питание.

Нелинейные искажения, характерные для устройств, использующих режим усиления класса АВ (например, для устройства-прототипа), также отсутствуют, поскольку заявленное устройство работает в режиме усиления класса А.

Приведённые примеры и схемы реализации устройства не ограничивают объём заявленного изобретения. Специалистам в данной области очевидно, что возможны различные варианты технической реализации аппаратной части отдельных элементов. Например, вышеописанный первый делитель напряжения, образованный резисторами 443 и 445 (а также второй делитель напряжения, образованный резисторами 549 и 547, третий делитель напряжения, образованный резисторами 605 и 613, четвёртый делитель напряжения, образованный резисторами 707 и 713, пятый делитель напряжения, образованный резисторами 805, 807 и 813, см. Фиг. 4, 5, 6, 7, 8 соответственно, наконец, шестой делитель напряжения, образованный резисторами 443 и 545, см. Фиг. 5) может быть резистивным делителем, или может быть выполнен в виде делителя из последовательно включённых транзисторов, или может быть выполнен любым другим способом, обеспечивающим создание в средней точке делителя необходимого напряжения. Более того, любые резисторы, упомянутые в настоящем описании, могут быть выполнены как элементы, имеющие преимущественно активное сопротивление, например, в интегральной микросхеме роль резистора может играть слой полупроводника, изолированный от других элементов.

Аналогично, в качестве усилителей 101 и 151 (см. Фиг. 2a) могут быть использованы микросхемы операционных усилителей, например: OPA189, OPA365 и многих других. Основные параметры микросхем: усиление при разомкнутой обратной связи (нагрузка = 10 Ω) - не менее 100 дБ; частота единичного усиления - не менее 1МГц. Допустимый минимальный входной сигнал должен быть ниже потенциала нулевой шины, например, на 0,1 В, а смещение нуля должно быть в разы меньше, чем минимальное выходное напряжение Uout. В качестве транзисторов 103, 153 могут использоваться полевые транзисторы, например: BSS83, RU1C001UN, FDN028N20 и другие полевые транзисторы. В этом случае первый, управляющий электрод является затвором, второй электрод является стоком, третий электрод является истоком. Основные параметры для транзистора 103: ток стока I0 не менее 100 мА, напряжение затвор-исток должно превышать минимальное выходное напряжение ОУ 101. Для второго транзистора 153 величина RDS (on) должна составлять не более нескольких сотен миллиОм. Для обоих транзисторов паразитные ёмкости должны быть минимальными. Могут также использоваться и другие транзисторы, в том числе биполярные. В этом случае первый, управляющий электрод является базой, второй электрод является коллектором, третий электрод является эмиттером. В качестве транзисторов 703 (см. Фиг. 7) могут использоваться только полевые транзисторы, например: BSS83, RU1C001UN и другие. Основное условие для выбора полевого транзистора по его характеристикам: напряжение сток-исток должно быть больше напряжения отсечки. В качестве задатчиков тока 155 (см. схему Фиг. 2a), кроме схем, представленных на Фиг. 6 - 8, могут использоваться иные схемы, обеспечивающие формирование стабильного напряжения U0, которое задаёт постоянный стабильный ток I0 стабилизатора тока 105.

Части одних элементов, упомянутых в описании, могут отличаться, частично совпадать или полностью совпадать с частями других элементов, если иное не указано в явном виде. Кроме того, части одних элементов могут располагаться в различных частях других элементов, если иное не указано в явном виде. Если указано, что элемент «соединён» с другим элементом, это означает, что элемент может быть «напрямую соединён» с другим элементом или «электрически соединён» с другим элементом через третий элемент. Например, между ОУ 101 и транзистором 103 может быть включён развязывающий резистор или согласующий каскад. То же относится к соединению второго ОУ 151 и второго транзистора 153 в стабилизаторе тока 105. Кроме того, если не указано обратное, слово «включать» и его формы «включает» или «включающий» подразумевает наличие указанных элементов, но не отсутствие любых других элементов.

Заявляемое устройство может быть выполнено, например, в виде микросхемы, либо микросборки, либо микроплаты, выводами которой являются выводы: 107, 109, 127, 135. Заявляемое устройство может быть выполнено также в виде микросхемы, либо микросборки, либо микроплаты, выводами которой являются выводы: 107, 109, 119, 127, 129,135, 167, к которым подсоединяется микросхема, либо микросборка, либо микроплата с выводами: 121, 123, 125, 171, 173.177. Заявляемое устройство может быть выполнено также в виде микросхемы ОУ с выводами: 111, 113, 115, 117, 119, 131, 133, 167, к которым подсоединяется микросхема, либо микросборка, либо микроплата с выводами: 121, 123, 125, 137, 139, 141, 171, 173, 177.

Возможны и иные варианты разбиения устройства на составные части, и заявленное устройство также может быть частью других структур или других микросхем, либо микросборок, либо микроплат.

Экспериментальные результаты

С целью подтверждения достижимости заявленного технического результата, было проведено макетирование двух вариантов устройств передачи сигнала, соответствующих схеме, представленной на Фиг. 2a (в режиме повторителя напряжения). В одном из макетов в качестве ОУ 101 и 151 были использованы микросхемы OPA 2189, а в другом макете - микросхемы OPA 365. В обоих макетах в качестве транзисторов 103 и 153 были использованы транзисторы RU1C001UN и NTNS3C68NZ, соответственно.

Результаты макетирования приведены в таблице.

ОУ 101, 151 это OPA 2189

ОУ 101, 151 это OPA 365

Из приведённых данных следует, что технический результат, достигаемый заявляемым изобретением, действительно заключается в значительном расширении динамического диапазона устройств передачи сигнала, имеющих однополярное питание, по сравнению с известными аналогами, при одновременном обеспечении высокой скорости нарастания выходного сигнала.

На Фиг. 10 приведены осциллограммы входного испытательного напряжения Uin (график 1001) и выходного напряжения Uout (график 1002) для макета №1. Пилообразная форма входного испытательного напряжения выбрана для большей наглядности. Входное напряжение Uin поступало по каналу К3 осциллографа (масштаб 10 мВ/клетка), выходное напряжение Uout индицировалось на канале К4 осциллографа (масштаб также 10 мВ/клетка). Из осциллограмм видно, что искажения минимального выходного сигнала (скругление пилы) составляют менее 1 мВ. Таким образом, подтверждается получение заявленного технического результата.

Заявляемое устройство, выполненное в соответствии с вышеприведёнными рекомендациями и приложенными чертежами, обладает высокой повторяемостью.

Заявленное изобретение описано на основании того, что в настоящее время рассматривается как практически возможная реализация различных вариантов устройства. Однако следует иметь в виду, что заявленное изобретение не ограничено приведёнными вариантами, но, напротив, предназначено для использования в различных модификациях и равнозначных воплощениях, которые соответствуют идеям и духу приведённой ниже формулы. Так, устройства передачи сигнала с расширенным динамическим диапазоном, имеющие однополярное питание, могут использоваться в качестве буфера сигнала для чувствительных высокоимпедансных датчиков, во входных каскадах АЦП и выходных каскадах ЦАП, в том числе в интегральном исполнении, в качестве детекторов малых сигналов и во множестве других приложений. Соответственно, рисунки и описание работы являются иллюстративными и не ограничивают возможности реализации изобретения.

Заявленное техническое решение определяется нижеследующей формулой изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЭЛЕКТРОННО-УПРАВЛЯЕМЫЙ РЕЗИСТОР | 2019 |

|

RU2760031C1 |

| Устройство для контроля и регулирования производительности | 1990 |

|

SU1791032A1 |

| Устройство управления электронно-управляемым резистором | 2021 |

|

RU2822988C2 |

| Низковольтный стабилизатор напряжения | 1980 |

|

SU868725A1 |

| Стабилизированный источник питания | 1981 |

|

SU1029167A1 |

| Триггерный логический элемент И-НЕ/ИЛИ-НЕ | 2022 |

|

RU2783403C1 |

| Стабилизатор постоянного напряжения | 1979 |

|

SU838677A1 |

| Триггерный логический элемент И/ИЛИ | 2020 |

|

RU2745398C1 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ ТОКА (ВАРИАНТЫ) | 2024 |

|

RU2821721C1 |

| Триггерный логический элемент НЕ/ИЛИ/И/ИЛИ-НЕ/И-НЕ | 2021 |

|

RU2760206C1 |

Изобретение относится к областям радиотехники, электроники и измерительной техники. Технический результат - расширение динамического диапазона передаваемых сигналов и высокая скорость нарастания выходного сигнала. Для этого предложено устройство для передачи сигнала, имеющее однополярное питание, содержащее два операционных усилителя (ОУ), два транзистора, резистор, узел обратной связи (УОС) и задатчик тока. Выход первого ОУ соединён с первым электродом первого транзистора, первый вход первого ОУ соединён с выводом для приёма входного сигнала. Второй транзистор, второй ОУ и резистор образуют стабилизатор тока (СТ). Точка соединения входа CT, третьего электрода первого транзистора и первого вывода УОС зарезервирована для подключения нагрузки. Второй вывод УОС соединён со вторым входом первого ОУ. 2 н. и 13 з.п. ф-лы, 16 ил., 1 табл.

1. Устройство передачи сигнала, имеющее однополярное питание (100), содержащее первый операционный усилитель (101), второй операционный усилитель (151), первый транзистор (103), второй транзистор (153) и резистор (157), выход (119) первого операционного усилителя (101) соединен с первым электродом (121) первого транзистора (103), неинвертирующий вход (115) первого операционного усилителя (101) соединен с выводом (109) устройства (100), предназначенным для подачи входного сигнала, выход (165) второго операционного усилителя (151) соединен с первым электродом (181) второго транзистора (153), третий электрод (193) второго транзистора (153) подсоединен к инвертирующему входу (169) второго операционного усилителя (151) и к выводу (187) резистора (157), отличающееся тем, что устройство (100) снабжено узлом обратной связи (143) и задатчиком выходного тока (155), точка соединения третьего электрода (123) первого транзистора (103) и второго электрода (191) второго транзистора (153) соединена с первым выводом (137) узла обратной связи (143) и предназначена для подключения нагрузки, второй электрод (125) первого транзистора (103) соединен с первым выводом (111) питания первого операционного усилителя (101) и подсоединен к выводу (107) устройства, предназначенному для подключения к положительному полюсу источника питания, второй вывод (139) узла обратной связи (143) подсоединен к инвертирующему входу (117) первого операционного усилителя (101), выход (173) задатчика выходного тока (155) подсоединен к неинвертирующему входу (167) второго операционного усилителя (151).

2. Устройство по п. 1, отличающееся тем, что узел обратной связи (143) является проводником.

3. Устройство по п. 1, отличающееся тем, что узел обратной связи (143) содержит первый делитель напряжения (443; 445), первый элемент (443) первого делителя напряжения (443; 445) включен между первым (137) и вторым (139) выводами узла обратной связи (143), второй элемент (445) первого делителя напряжения (443; 445) включен между вторым (139) и третьим (141) выводами узла обратной связи (143).

4. Устройство по п. 1, отличающееся тем, что оно содержит второй делитель напряжения (547; 549), включенный между первым выводом (109) устройства и неинвертирующим входом (115) первого операционного усилителя (101), а также содержащее элемент (545), имеющий преимущественно активное сопротивление, включенный между вторым выводом (118) устройства и инвертирующий входом (117) первого операционного усилителя (101), причем узел обратной связи (143) содержит элемент (443), имеющий преимущественно активное сопротивление, включенный между первым (137) и вторым (139) выводами узла обратной связи (143).

5. Устройство по п. 1, отличающееся тем, что первый транзистор (103) и второй транзистор (153) являются полевыми транзисторами, их первые электроды (121) и (181) являются затворами, а их вторые электроды (125) и (191), соответственно, являются стоками.

6. Устройство по п. 1, отличающееся тем, что первый транзистор (103) и второй транзистор (153) являются биполярными транзисторами, их первые электроды (121) и (181) являются базами, а их вторые электроды (125) и (191), соответственно, являются коллекторами.

7. Устройство по п. 1, в котором задатчик выходного тока (155) содержит третий делитель напряжения (605; 613), первый вывод (621) первого элемента (605) третьего делителя напряжения (605; 613) соединен с первым выводом (171) упомянутого задатчика выходного тока (155), точка соединения первого (605) и второго (613) элементов третьего делителя напряжения (605; 613) соединена с вторым выводом (173) упомянутого задатчика выходного тока (155), второй вывод (629) второго элемента (613) третьего делителя напряжения (605; 613) подсоединен к третьему выводу (177) задатчика выходного тока (155).

8. Устройство по п. 1, в котором задатчик выходного тока (155) содержит полевой транзистор (703) и четвертый делитель напряжения (707; 713), при этом сток (741) полевого транзистора (703) подсоединен к первому выводу (171) упомянутого задатчика выходного тока (155), исток (743) полевого транзистора (703) подсоединен к первому выводу (737) первого элемента (707) четвертого делителя напряжения (707; 713), затвор (731) полевого транзистора (703) подсоединен к точке соединения первого (707) и второго (713) элементов четвертого делителя напряжения (707; 713) и к второму выводу (173) упомянутого задатчика выходного тока (155), второй вывод (727) второго элемента (713) четвертого делителя напряжения (707; 713) подсоединен к третьему выводу (177) упомянутого задатчика выходного тока (155).

9. Устройство по п. 1, в котором задатчик выходного тока (155) содержит источник опорного напряжения (801) и пятый делитель напряжения (805; 807; 813), первый вывод (831) первого элемента (805) пятого делителя напряжения (805; 807; 813) подсоединен к первому выводу (171) упомянутого задатчика выходного тока (155), второй вывод (833) первого элемента (805) пятого делителя напряжения (805; 807; 813) подсоединен к первому выводу (835) источника опорного напряжения (801), и к первому выводу (839) второго элемента (807) пятого делителя напряжения (805; 807; 813), второй вывод (841) второго элемента (807) пятого делителя напряжения (805; 807; 813) подсоединен к второму выводу (173) упомянутого задатчика выходного тока (155) и к первому выводу (843) третьего элемента (813) пятого делителя напряжения (805; 807; 813), второй вывод (845) третьего элемента (813) пятого делителя напряжения (805; 807; 813) подсоединен к третьему выводу (177) упомянутого задатчика выходного тока (155) и к второму выводу (837) источника опорного напряжения (801).

10. Интегральная микросхема для передачи сигнала, имеющая однополярное питание (200), содержащая первый операционный усилитель (101), второй операционный усилитель (151), первый транзистор (103), второй транзистор (153), и резистор (157), выход (119) первого операционного усилителя (101) соединен с первым электродом (121) первого транзистора (103), неинвертирующий вход (115) первого операционного усилителя (101) соединен с выводом (109) интегральной микросхемы (200), предназначенным для подачи входного сигнала, выход (165) второго операционного усилителя (151) соединен с первым электродом (181) второго транзистора (153), третий электрод (193) второго транзистора (153) подсоединен к инвертирующему входу (169) второго операционного усилителя (151) и к выводу (187) резистора (157), второй электрод (125) первого транзистора (103) соединен с первым выводом (111) питания первого операционного усилителя (101) и подсоединен к выводу (107) устройства, предназначенному для подключения к положительному полюсу источника питания,

отличающаяся тем, что в интегральной микросхеме (200) третий электрод (123) первого транзистора (103) соединен со вторым электродом (191) второго транзистора (153), и точка их соединения подсоединена к выводу (135), предназначенному для подключения нагрузки, вывод (135) предназначен для подключения первого вывода внешнего узла обратной связи (143), при этом вывод (118) соединен с инвертирующим входом (117) первого операционного усилителя (101) и предназначен для подключения второго вывода внешнего узла обратной связи (143).

11. Интегральная микросхема по п. 10, отличающаяся тем, что вывод (118) предназначен для подачи второго входного сигнала.

12. Интегральная микросхема по п. 10, отличающаяся тем, что она содержит задатчик выходного тока (155), содержащий третий делитель напряжения (605; 613), первый вывод (621) первого элемента (605) третьего делителя напряжения (605; 613) соединен с первым выводом (171) упомянутого задатчика выходного тока (155), точка соединения первого (605) и второго (613) элементов третьего делителя напряжения (605; 613) соединена с вторым выводом (173) задатчика выходного тока (155), второй вывод (629) второго элемента (613) третьего делителя напряжения (605; 613) подсоединен к третьему выводу (177) упомянутого задатчика выходного тока (155).

13. Интегральная микросхема по п. 10, отличающаяся тем, что она содержит задатчик выходного тока (155), состоящий из полевого транзистора (703) и четвертого делителя напряжения (707; 713), при этом сток (741) полевого транзистора (703) подсоединен к первому выводу (171) задатчика выходного тока (155), исток (743) полевого транзистора (703) подсоединен к первому выводу (737) первого элемента (707) четвертого делителя напряжения (707; 713), затвор (731) полевого транзистора (703) подсоединен к точке соединения первого (707) и второго (713) элементов четвертого делителя напряжения (707; 713), и к второму выводу (173) задатчика выходного тока (155), второй вывод (727) второго элемента (713) четвертого делителя напряжения (707; 713) подсоединен к третьему выводу (177) упомянутого задатчика выходного тока (155), при этом выход (173) задатчика выходного тока (155) подсоединен к неинвертирующему входу (167) второго операционного усилителя (151).