Изобретение относится к импульсной технике и предназначено для использования в ключевых генераторах, вторичных источниках электропитания. Конкретно, изобретение может быть использовано в фазоимпульсном модуляторе, генерирующем две пары парафазных сигналов, так, чтобы вторая пара имела регулируемый сдвиг (временную задержку) относительно первой.

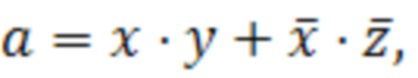

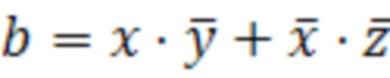

Известны фазоимпульсные модуляторы (SU 1614110 и RU 2013859), построенные на основе одного и того же принципа, формирующие на выходе два сигнала, сдвинутые относительно друг друга на tи. Устройства содержат генератор тактовых импульсов (ГТИ), первый выход которого соединен с входом синхронизации широтно-импульсного модулятора (ШИМ), вход которого соединен с входной шиной управляющего напряжения, а выход - с первым входом сигнала х логического дешифратора, второй вход сигнала у которого соединен с вторым выходом ГТИ, а его первый выход сигнала а и второй выход сигнала b являются выходами устройства, при этом логический дешифратор реализует логическую функцию

Известен также многоканальный широтно-импульсный преобразователь по патенту РФ №2733782, содержащий генератор опорных сигналов, N пилообразных выходов которого соединены с соответствующими инверсными входами N сравнивающих устройств, прямые входы которых соединены параллельно к входной шине многоканального ШИП, а также N-канальный суммирующий ключевой усилитель, содержащий N входов, N пар устройств совпадения (УС) и N RS-триггеров. а N-канальный генератор опорных сигналов дополнительно содержит N выходов тактовых импульсов, синхронных с соответствующими выходами пилообразных напряжений.

Общими недостатками вышеперечисленных устройств по отношению к заявляемому, является низкая надежность, обусловленная отсутствием возможности введения бестоковой паузы, необходимой для управления ключами преобразователя.

Одной из функций бестоковой паузы является предотвращение разрыва цепи управления при прохождении сквозного тока, когда два переключающих элемента одновременно находятся во включенном состоянии. Кроме того, в общем случае бестоковая пауза устанавливается для того, чтобы минимизировать потери мощности переключающих элементов путем установки оптимальных временных интервалов переключения в соответствии с характеристиками включения-выключения двух различных переключающих элементов.

Задача повышения надежности устройства при управлении мощными силовыми ключами за счет исключения в них сквозных токов в какой-то степени решается в цифровом широтно-импульсном модуляторе по авторскому свидетельству SU 1478316.

Недостатками являются указанного решения являются низкая возможность регулировать фазовый сдвиг ШИМ, а также то, что бестоковая пауза определяется быстродействием элементов и времязадающими цепочками ждущих одновибраторов. Изменять величину бестоковой паузы в процессе работы ШИМ-модулятора не представляется возможным.

Задача устранения сквозных токов за счет введения бестоковой паузы решается в целом ряде патентов США. Яркий представитель традиционного подхода к формированию бестоковой паузы - патент US 7057910. По сигналу равенства счетчика заданному порогу срабатывания формируется сигнал тактирования счетного триггера 1, формирующий комплементарную пару сигналов PWM1 и PWM2, а также, по нарастающему фронту соответствующего сигнала (PWM1 или PWM2), запускающий один из двух таймеров бестоковой паузы. Блок сложения времени бестоковой паузы добавляет время, прошедшее до тех пор, пока значение таймера не достигнет заданного значения регистра в качестве первого времени бестоковой паузы при нарастании первого ШИМ-сигнала. С другой стороны, время, прошедшее до тех пор, пока значение таймера не достигнет установленного значения другого регистра, добавляется как второе время бестоковой паузы при нарастании второго ШИМ-сигнала. Подобным же образом организовано обеспечение бестоковой паузы в патентах US6937084, US7375480, US8816621. Недостаток этих устройств заключается в сложности за счет введения дополнительного таймера-счетчика бестоковой паузы и блока добавления бестоковой паузы. Аналогичным недостатком обладает устройство по патенту US 7953500. Устройство содержит таймер/счетчик, который ведет отсчет от нуля до тех пор, пока не достигнет значения, заданного регистром периода, что определяется путем сравнения в компараторе. Регистр периода содержит заданное пользователем значение, которое представляет максимальное значение счетчика, определяющее период ШИМ. Когда значение таймер/счетчика совпадает со значением в регистре периода, таймер/счетчик очищается сигналом сброса от компаратора, и цикл повторяется. Регистр рабочего цикла хранит заданное пользователем значение рабочего цикла. Выходной сигнал ШИМ инициируется всякий раз, когда значение таймера/счетчика меньше значения рабочего цикла, сохраненного в регистре рабочего цикла, и когда значение таймера/счетчика больше или равно значению регистра рабочего цикла. Сигналы ШИМ в двухтактном устройстве могут генерироваться с помощью переключающего триггера и элементов И.

Второй подход к формированию бестоковой паузы приведен в патенте US 7250740, где для формирования ШИМ предназначен двоично-реверсивный счетчик 1, а за формирование бестоковой паузы отвечает второй двоично-реверсиный счетчик, который, при помощи собственной схемы управления формирует расширенный вниз на величину бестоковой паузы А и расширенный вверх на величину бестоковой паузы В сигналы, и задерживает сигнал второго счетчика на сумму отсчетов бестоковой паузы А и В. Недостаток заключается в наличии дополнительного таймера с задержкой относительно основного.

Наиболее близким к заявляемому изобретению по принципу формирования ШИМ-сигналов является устройство генерации повторяющихся сигналов широтно-импульсной модуляции по патенту US8558632.

Устройство содержит генератор тактовой частоты, цифровой мастер-счетчик, который создает основную временную базу и генерирует сигнал начала цикла ШИМ, указанный мастер-счетчик состоит из регистра предела счета, компаратора и счетчика, формирователи ШИМ-сигналов по числу генерируемых сигналов ШИМ, при этом каждый формирователь состоит из регистра длительности импульса, компаратора длительности импульса, счетчика длительности импульса, регистра фазового сдвига, компаратора фазового сдвига и счетчика фазового сдвига. Мастер-счетчик сбрасывает счетчики фазового сдвига в каждой из цепей формирователей ШИМ. Счетчик фазового сдвига продолжает отсчет до тех пор, пока он не совпадет с соответствующим значением сдвига фазы в регистре сдвига фазы. Затем соответствующий счетчик длительности импульса сбрасывается и перезапускается. Импульс продолжается до тех пор, пока его значение в счетчике длительности импульса не совпадет с указанным значением в регистре, после чего счетчик длительности импульса останавливается до тех пор, пока не будет сброшен за счет сигнала со счетчика сдвига фазы. Выходы компараторов длительности импульсов выдают выходные ШИМ-сигналы в виде повторяющейся серии одноцикловых ШИМ-сигналов.

Недостатками, устраняемыми заявляемым устройством, являются сложность схемы, обусловленная большим количеством формирователей ШИМ-сигналов, число которых равно числу генерируемых ШИМ-сигналов, наличие большого числа счетчиков, отсутствие входного сигнала синхронизации, все формирователи синхронизируются сигналом мастер-счетчика и сбой в его работе приведет к сбоям работы всего устройства, а также отсутствием введения бестоковой паузы.

Задачей изобретения является упрощение схемы с одновременным повышением надежности работы за счет введения бестоковой паузы, а также расширение арсенала средств, используемых для генерации смещенных по фазе ШИМ-сигналов, например, для фазоимпульсных модуляторов.

В первом варианте поставленная задача решается тем, что в устройство для генерации двух пар комплементарных ШИМ-сигналов, содержащее генератор тактовой частоты, мастер-счетчик, связанный с формирователями ШИМ - сигналов, содержащими компараторы, введены схема управления, схема вычисления опорных сигналов и порогов срабатывания и элемент НЕ, при этом мастер-счетчик выполнен в виде двоично-реверсивного счетчика, схема управления имеет четыре входа, предназначенных для подачи сигналов тактового генератора, сигнала предела счета, сигнала внешней синхронизации и сигнала значения регистра мастер-счетчика и этим входом соединена с выходом мастер-счетчика, при этом первый формирователь ШИМ-сигналов состоит из первого, второго, третьего и четвертого компараторов, первого, второго, третьего и четвертого логических элементов И, где первые входы компараторов соединены с выходом мастер-счетчика, выходы компараторов соединены попарно с первыми входами указанных элементов И, выходы первого и второго элементов И соединены с входами первого RS-триггера, а выходы третьего и четвертого элементов И соединены с входами второго RS-триггера; второй формирователь ШИМ-сигналов состоит из пятого, шестого, седьмого и восьмого компараторов, пятого шестого, седьмого и восьмого элементов И, при этом первые входы указанных компараторов соединены с выходом двоично-реверсивного мастер-счетчика, выходы компараторов попарно соединены с первыми входами пятого, шестого, седьмого и восьмого элементов И, выходы пятого и шестого элементов И соединены с входами третьего RS-триггера, выходы седьмого и восьмого элементов И соединены со входами четвертого RS-триггера, вход элемента НЕ (инвертора тактовой частоты), являющегося общим элементом первого и второго формирователей, соединен с выходом схемы управления, а выход элемента НЕ соединен с вторыми входами третьего, четвертого, седьмого и восьмого логических элементов И, упомянутая схема вычисления опорных сигналов и порогов срабатывания имеет три входа, предназначенных для подачи сигналов предела счета, фазового сдвига и бестоковой паузы, первый выход указанной схемы вычисления опорных сигналов и порогов срабатывания соединен со вторыми входами первого и четвертого компараторов, второй выход - со вторыми входами второго и третьего компараторов, третий, четвертый и пятый и шестой выходы соединены с вторыми входами пятого, шестого, седьмого и восьмого компараторов, соответственно, выходы RS - триггеров являются выходами ШИМ - сигналов..

Техническим эффектом заявляемого изобретения является снижение количества формирователей и наличие только одного счетчика. Технический эффект достигается применением двоично-реверсивного счетчика, схемы вычисления опорных сигналов и порогов срабатывания, сигнала внешней синхронизации, а также определенной конфигурацией формирователей ШИМ-сигналов. При этом сигнал пилообразного напряжения представляет собой равнобедренный треугольник, в отличие от прототипа, в котором нарастающий сигнал «пилы» является прямоугольным треугольником, вырабатывающим сигнал синхронизации для формирователей ШИМ по достижению предела счета.

Первый вариант изобретения предназначен для случая, когда фазовый сдвиг ограничен в пределах диапазона от значения бестоковой паузы до значения разницы предела счета и бестоковой паузы.

Второй вариант изобретения предназначен для особого случая, когда фазовый сдвиг (ФС) выходит за пределы выше указанного диапазона.

В устройство по второму варианту для генерации двух пар комплементарных ШИМ-сигналов, содержащее генератор тактовой частоты, мастер-счетчик, связанный с формирователями ШИМ- сигналов, содержащими компараторы, введены схема управления, схема вычисления опорных сигналов и порогов срабатывания и элемент НЕ, при этом мастер-счетчик выполнен в виде двоично-реверсивного счетчика, схема управления имеет четыре входа, предназначенных для подачи сигналов тактового генератора, сигнала предела счета, сигнала внешней синхронизации и сигнала значения регистра мастер-счетчика и этим входом соединена с выходом мастер-счетчика, при этом первый формирователь ШИМ-сигналов состоит из первого, второго, третьего и четвертого компараторов, первого, второго, третьего и четвертого логических элементов И, где первые входы компараторов соединены с выходом мастер-счетчика, выходы компараторов соединены попарно с первыми входами указанных элементов И, выходы первого и второго элементов И соединены с входами первого RS-триггера, а выходы третьего и четвертого элементов И соединены с входами второго RS-триггера; второй формирователь ШИМ-сигналов состоит из пятого, шестого, седьмого и восьмого компараторов, пятого шестого, седьмого и восьмого элементов И, первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, а также первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с инверсией, при этом первые входы указанных компараторов соединены с выходом двоично-реверсивного мастер-счетчика, выходы компараторов попарно соединены с первыми входами пятого, шестого, седьмого и восьмого элементов И, выходы пятого и шестого элементов И соединены с входами третьего RS-триггера, выходы седьмого и восьмого элементов И соединены со входами четвертого RS-триггера, вход элемента НЕ (инвертора тактовой частоты), являющегося общим элементом первого и второго формирователей, соединен с выходом схемы управления, а выход элемента НЕ соединен с вторыми входами третьего, четвертого логических элементов И, а также со вторыми входами второго элемента исключающее ИЛИ и второго элемента исключающее ИЛИ с инверсией, кроме того, выход схемы управления соединен с первыми входами первого элемента ИСКЛЮЧЮЩЕЕ ИЛИ и первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с инверсией, выходы которых соединены со вторыми входами пятого и шестого логических элементов И, соответственно, выходы второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с инверсией соединены с вторыми входами седьмого и восьмого элементов И, соответственно; упомянутая схема вычисления опорных сигналов и порогов срабатывания имеет три входа, предназначенных для подачи сигналов предела счета, фазового сдвига и бестоковой паузы, первый выход указанной схемы вычисления опорных сигналов и порогов срабатывания соединен со вторыми входами первого и четвертого компараторов, второй выход - со вторыми входами второго и третьего компараторов, третий, четвертый и пятый и шестой выходы соединены с вторыми входами пятого, шестого, седьмого и восьмого компараторов, соответственно, седьмой выход указанной схемы соединен с первыми входами первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, а восьмой выход - с первыми входами первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с инверсией, выходы RS-триггеров являются выходами ШИМ-сигналов.

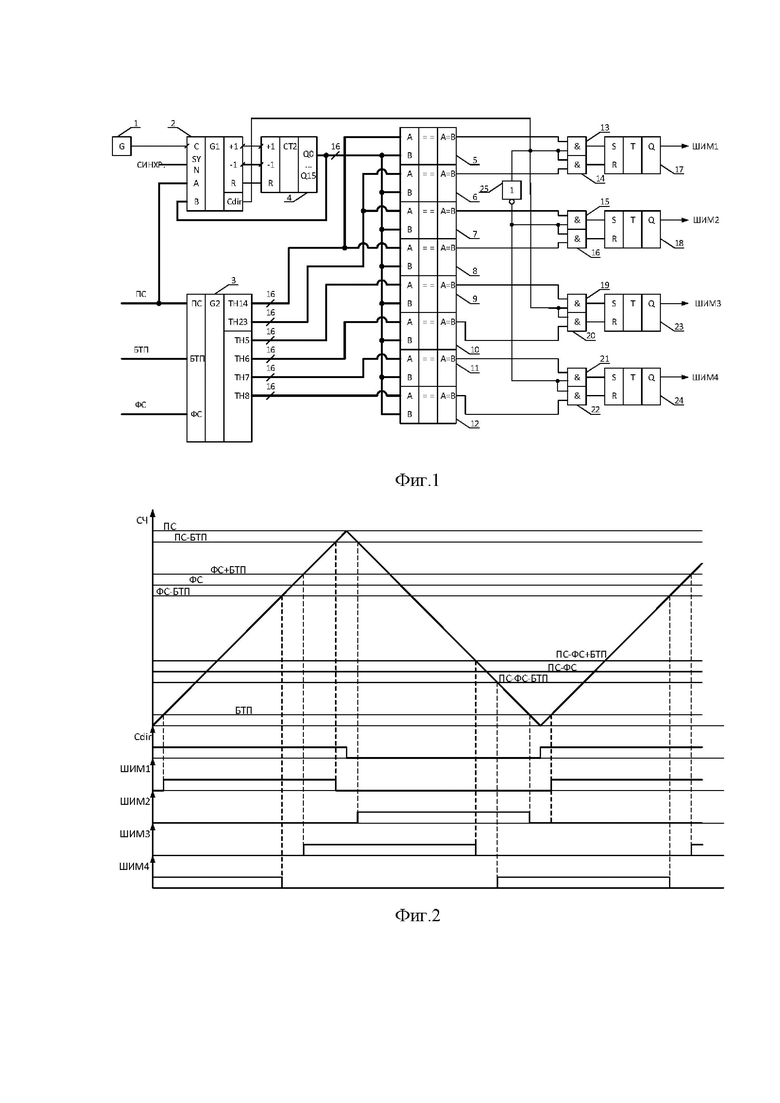

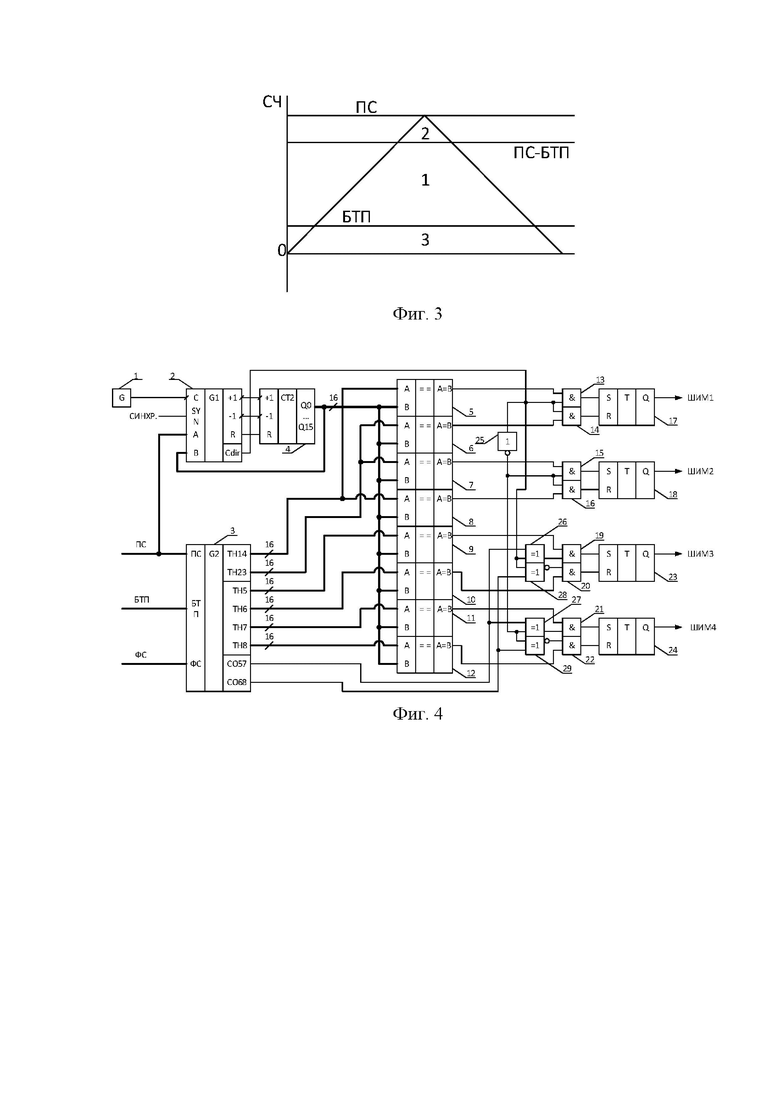

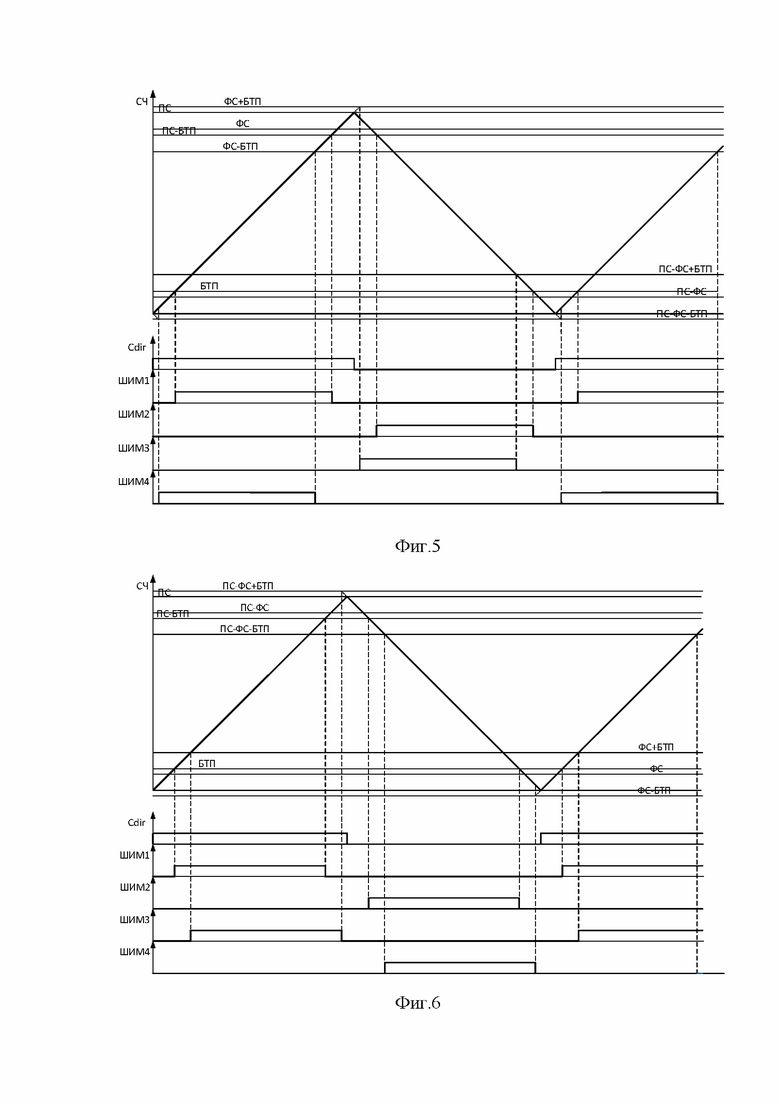

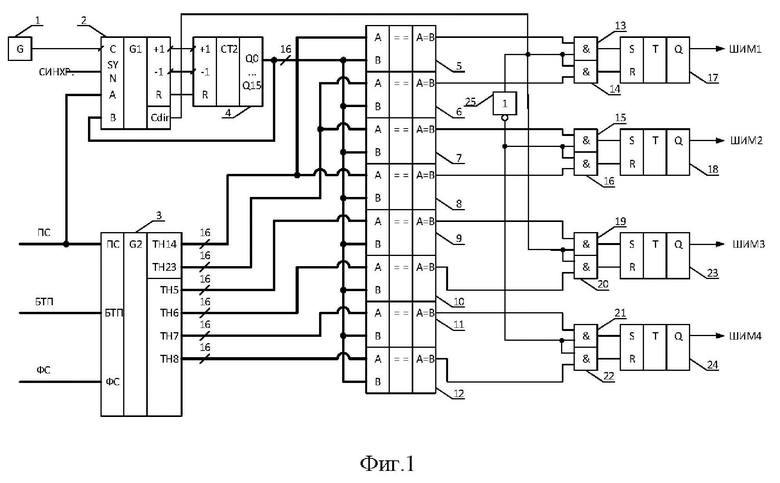

Далее сущность изобретения поясняется с помощью рисунков, на которых представлено: на фиг.1 - структурная схема предлагаемого устройства по первому варианту; на фиг.2 - временные диаграммы формирования ШИМ по первому варианту изобретения; на фиг. 3 - зоны расположения фазового сдвига относительно предела счета и бестоковой паузы; на фиг.4 - структурная схема предлагаемого устройства по второму варианту; на фиг. 5, 6 - временные диаграммы формирования ШИМ по второму варианту изобретения.

Устройство для генерации двух пар комплементарных ШИМ-сигналов, показанное на фиг.1 содержит тактовый генератор 1, схему управления 2, схему вычисления опорных сигналов и порогов срабатывания 3, двоично-реверсивный мастер-счетчик 4, первый формирователь ШИМ-сигналов, содержащий компараторы 5, 6, 7 и 8, элементы И 13, 14, 15 и 16 и два RS-триггера 17 и 18; второй формирователь ШИМ-сигналов, содержащий компараторы 9, 10, 11 и 12, элементы И 19, 20, 21 и 22 и два RS-триггера 23 и 24. Двоично-реверсивный счетчик 4 предназначен для подсчета количества импульсов поступивших на дискретные входы «+1» или «-1». Схема управления 2 может быть выполнена, например, на ПЛИС семейства Altera MAX V типа 5M570ZT100C5N, на четыре входа которой(ого), подаются сигналы тактового генератора 1, предела счета, сигнал внешней синхронизации и сигналы значения регистра мастер-счетчика 4 (Q1..Q15), объединенные в 16-разрядную шину. Первые входы четырех компараторов 5-8 соединены с выходом двоично-реверсивного счетчика 4 посредством 16-разрядной шины, выходы компараторов 5 и 6 соединены с первыми входами элементов И 13 и 14, соответственно, выходы компараторов 7 и 8 соединены с первыми входами элементов И 15 и 16, соответственно. Выходы элементов И 13 и 14 соединены с входами первого RS-триггера 17, выходы элементов И 15 и 16 - с входами второго RS-триггера 18. Первые входы четырех компараторов 9-12, соединены с выходом двоично-реверсивного мастер-счетчика 4. Выходы компараторов 9 и 10 соединены с первыми входами элементов И 19, 20, соответственно, выходы компараторов 11 и 12 соединены с первыми входами элементов И 21 и 22, соответственно. Выходы элементов И 19 и 20 соединены с входами RS-триггера 23, выходы элементов И 21 и 22 соединены с входами RS-триггера 24. Элемент НЕ 25 является общим элементом первого и второго формирователей и соединен между выходом Сdir схемы управления 2 и вторыми входами элементов И 15 и 16, а также вторыми входами элементов И 21, 22. Схема 3 вычисления опорных сигналов и порогов срабатывания может быть выполнена на ПЛИС семейства Altera MAX V типа 5M570ZT100C5N, на три входа которой(ого) подаются сигналы предела счета (ПС), фазового сдвига (ФС) и бестоковой паузы (БТП), задаваемые с внешнего устройства. Схема 3 имеет шесть выходов со значениями порогов срабатывания, которые соединены с компараторами первого и второго формирователей следующим образом: первый выход соединен со вторыми входами компараторов 5 и 8, второй выход - со вторыми входами компараторов 6 и 7, третий, четвертый, пятый и шестой выходы указанной схемы 3 соединены со вторыми входами компараторов 9, 10, 11 и 12, соответственно. Выходы RS-триггеров 17, 18, 23 и 24 являются выходами ШИМ-сигналов.

Устройство работает следующим образом: Тактовая частота с генератора 1 подается на схему управления 2, которая тактирует двоично-реверсивный счетчик 4. Двоично-реверсивный счетчик 4 предназначен для подсчета количества импульсов, поступивших на дискретные входы «+1» или «-1». При поступлении переднего фронта импульса на вход «+1» счетчик увеличивает свое значение на 1, при поступлении переднего фронта импульса на вход «-1» счетчик уменьшает свое значение на 1. Счетчик имеет входы ограничения верхнего «H» и нижнего «L» пределов подсчета. При достижении указанных пределов дальнейшее поступление импульсов на входы «+1» или «-1» не изменяет значение счетчика. Схема управления 2 формирует динамические сигналы управления «+1», «-1» и статические сигналы «R», «Cdir». Выходной сигнал схемы управления «R» сбрасывает выходы счетчика Q0…Q15 в состояние «0», при этом сигнал «Cdir» устанавливается в состояние «1», сигнализируя о режиме счета счетчика «вверх». При достижении равенства значения счетчика 4, подаваемого на вход В схемы управления сигналу предела счета, подаваемого на вход А схемы управления, схема управления 2 прекращает тактирование входа «+1» счетчика 4 и начинает тактирование входа «-1» счетчика. На выходе счетчика 4 формируется пилообразный сигнал, имеющий форму равнобедренного треугольника. Сигнал внешней синхронизации «SYN» предназначен для синхронизации нескольких модуляторов между собой, и при поступлении активного уровня «SYN» сигнал двоичного счетчика Q0…Q15 сбрасывается в состояние «0», сигнал «Cdir» переводится в состояние «1», сигналы «+1», «-1» переводятся в неактивное состояние до снятия активного уровня со входа «SYN» системы управления.

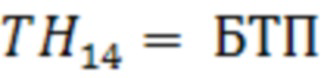

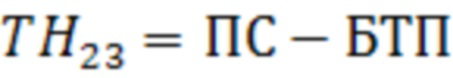

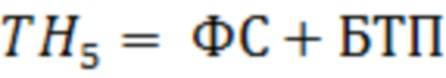

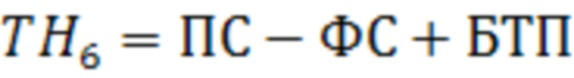

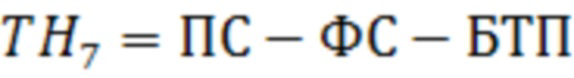

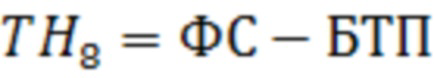

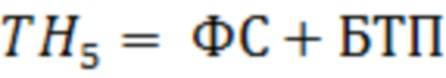

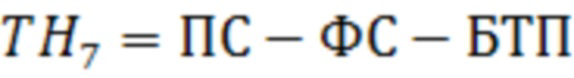

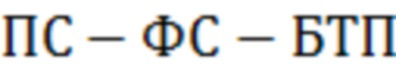

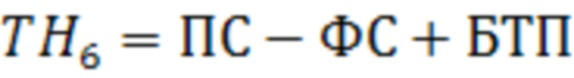

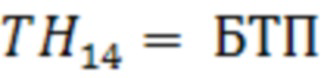

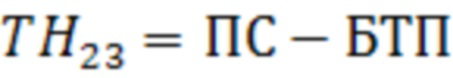

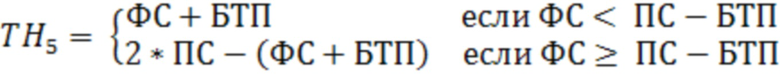

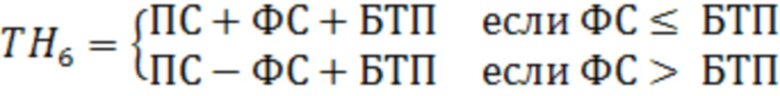

Схема 3 вычисления опорных сигналов и порогов срабатывания имеет на входе три входных шины - предел счета (ПС), фазовый сдвиг (ФС) и бестоковая пауза (БТП). Для первого варианта схема программируется на формирование следующих порогов срабатывания:

- поступает на компараторы 5 и 8,

- поступает на компараторы 5 и 8,

- поступает на компараторы 6 и 7,

- поступает на компараторы 6 и 7,

- поступает на компаратор 9,

- поступает на компаратор 9,

- поступает на компаратор 10,

- поступает на компаратор 10,

- поступает на компаратор 11,

- поступает на компаратор 11,

- поступает на компаратор 12.

- поступает на компаратор 12.

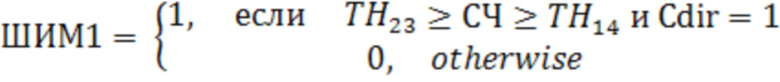

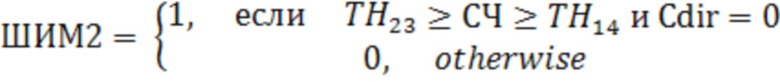

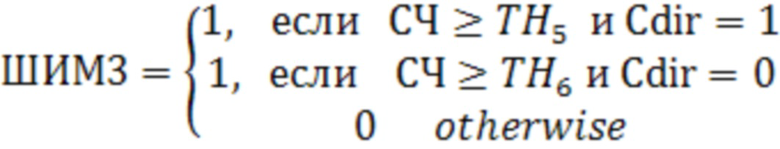

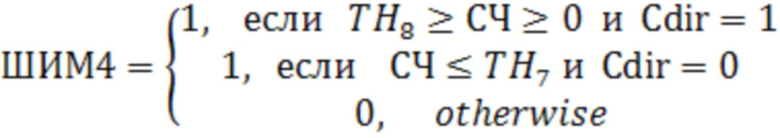

На компараторы поступают также сигналы с выходов Q0…Q15 текущего счета (СЧ) двоично - реверсивного счетчика 4. Например, рассмотрим первый компаратор 5. На его входы поступает сигнал ТН14 с выхода схемы вычисления опорных сигналов и порогов срабатывания 3, и сигнал текущего счета с выхода счетчика 4. В результате сравнения, например, при совпадении этих сигналов на первый вход элемента И 13 приходит 1, а на второй вход этого элемента приходит сигнал Cdir, который отражает направление счета. По логике работы элемента И, на выходе будет 1, если оба эти сигнала представляют 1. В результате сравнения сигналов на компараторах и логических операций на элементах И 13-16 и 19-22 при участии элемента НЕ 25 и работы триггеров 17, 18, 23, 24 формируются следующие сигналы управления ключами:

Как видно на фиг. 2, сигналы управления ключами ШИМ1 - ШИМ4 попарно сдвинуты по фазе, с автоматически вводимой бестоковой паузой и пока ФС находится на отрезке [БТП; ПС-БТП] (зона 1 фиг. 3), пороги срабатывания ФС+БТП, ФС-БТП, ПС-ФС+БТП; ПС-ФС-БТП все больше нуля и потому срабатывания компараторов гарантированы.

Кроме приведенного выше варианта, возможны ситуации, когда фазовый сдвиг ФС может находиться на всем диапазоне [0; ПС], в том числе на отрезках [ПС-БТП; ПС] (зона 2 фиг. 3) и [0; БТП] (зона 3 фиг. 3). Для этого случая предназначен второй вариант изобретения.

Устройство для генерации двух пар комплементарных ШИМ-сигналов по второму варианту, показанное на фиг.4 содержит все элементы, как и устройство на Фиг.1 с той же нумерацией, но внесены следующие изменения: во второй формирователь введены первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 26, 27, первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ с инверсией 28, 29. При этом выход элемента НЕ 25 соединен со вторыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 27 и ИСКЛЮЧАЮЩЕЕ ИЛИ с инверсией 29, выход схемы управления 2 соединен с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 26 и ИСКЛЮЧАЮЩЕЕ ИЛИ с инверсией 28. Выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 26 и ИСКЛЮЧАЮЩЕЕ ИЛИ с инверсией 28 соединены с вторыми входами логических элементов И 19, 20, соответственно, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 27 и ИСКЛЮЧАЮЩЕЕ ИЛИ с инверсией 29 соединены с вторыми входами элементов И 21 и 22. Схемы вычисления опорных сигналов и порогов срабатывания имеет два дополнительных выхода, седьмой и восьмой, являющимися выходами сигналов коррекции  и

и  , где седьмой выход соединен с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 26 и 27, а восьмой выход - с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с инверсией 28 и 29.

, где седьмой выход соединен с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 26 и 27, а восьмой выход - с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с инверсией 28 и 29.

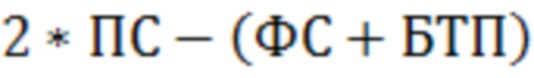

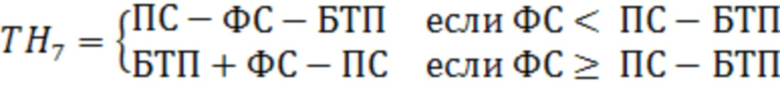

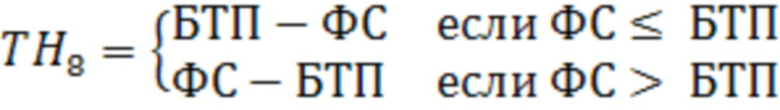

Работа устройства аналогична работе устройства по первому варианту, за исключением того, что при нахождении ФС на отрезке [ПС-БТП; ПС] (фиг. 5) значение порога срабатывания  становится больше предела счета и компаратор 9 не может сгенерировать корректный импульс управления. Для таких случаев, когда порог срабатывания превышает значение предела счета или становится меньше нуля предлагается ввести скорректированные пороги срабатывания. Для этого если продолжить линию графика значения счетчика СЧ при счете вверх до пересечения с порогом ФС+БТП (фиг. 5, прерывистая линия) и спроецировать точку пересечения на график счетчика СЧ при счете вниз, то скорректированное значение порога срабатывания будет равно

становится больше предела счета и компаратор 9 не может сгенерировать корректный импульс управления. Для таких случаев, когда порог срабатывания превышает значение предела счета или становится меньше нуля предлагается ввести скорректированные пороги срабатывания. Для этого если продолжить линию графика значения счетчика СЧ при счете вверх до пересечения с порогом ФС+БТП (фиг. 5, прерывистая линия) и спроецировать точку пересечения на график счетчика СЧ при счете вниз, то скорректированное значение порога срабатывания будет равно  , при этом условие Cdir = 1 должно быть изменено на Cdir = 0. Кроме того, для приведенного случая порог срабатывания

, при этом условие Cdir = 1 должно быть изменено на Cdir = 0. Кроме того, для приведенного случая порог срабатывания  становится меньше нуля и претерпевает идентичное математическое преобразование, то есть если продолжить линию графика значения счетчика СЧ при счет вниз до пересечения с порогом

становится меньше нуля и претерпевает идентичное математическое преобразование, то есть если продолжить линию графика значения счетчика СЧ при счет вниз до пересечения с порогом  (фиг. 5, прерывистая линия) и спроецировать точку пересечения на график счетчика при счет вверх, тогда скорректированное значение порога срабатывания равно БТП+ФС-ПС, и соответственно, условие Cdir = 0 должно быть изменено на Cdir = 1.

(фиг. 5, прерывистая линия) и спроецировать точку пересечения на график счетчика при счет вверх, тогда скорректированное значение порога срабатывания равно БТП+ФС-ПС, и соответственно, условие Cdir = 0 должно быть изменено на Cdir = 1.

При нахождении ФС на отрезке [0; БТП] (зона 3 фиг. 3) пороги срабатывания  и

и  ФС-БТП претерпевают похожие математические преобразования (фиг.6), при этом также происходит смена направления счета (изменяется условие Cdir). Таким образом, устройство коррекции порогов срабатывания 3 во втором варианте изобретения вычисляет пороги срабатывания следующим образом:

ФС-БТП претерпевают похожие математические преобразования (фиг.6), при этом также происходит смена направления счета (изменяется условие Cdir). Таким образом, устройство коррекции порогов срабатывания 3 во втором варианте изобретения вычисляет пороги срабатывания следующим образом:

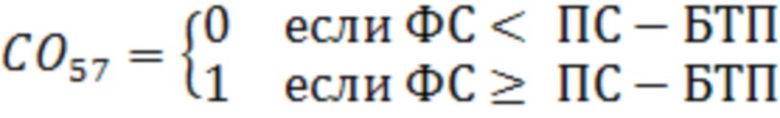

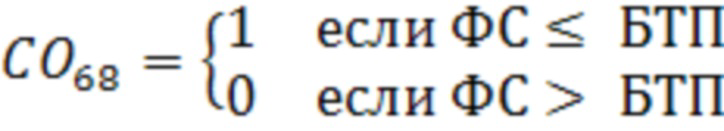

Смена условия Cdir (направление счета) происходит только для сигналов управления ШИМ3 и ШИМ4 в том случае, когда происходит коррекция порогов срабатывания, для этого схема 3 программируется на формирование двух дополнительных сигналов коррекции:

А в схему второго формирователя ШИМ-сигналов введены два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 26 и 27, и два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с инверсией 28 и 29.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ управления двунаправленным изолированным преобразователем мощности с поддержанием магнитного баланса | 2023 |

|

RU2811073C1 |

| Устройство для раздельного управления реверсивным тиристорным преобразователем | 1987 |

|

SU1503055A1 |

| Устройство для контроля ресурса коммутационных аппаратов | 1989 |

|

SU1656568A1 |

| ПРЕОБРАЗОВАТЕЛЬ ЛИНЕЙНЫХ ПЕРЕМЕЩЕНИЙ | 2000 |

|

RU2194946C2 |

| РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ ДЛЯ УПРАВЛЕНИЯ ЧЕТЫРЕХФАЗНЫМ ШАГОВЫМ ДВИГАТЕЛЕМ | 1998 |

|

RU2133550C1 |

| Интегральное устройство для управления вторичным источником питания | 1987 |

|

SU1538211A1 |

| Программно-временное устройство для автоматического управления и контроля системы смазки | 1986 |

|

SU1374180A1 |

| Устройство раздельного управления вентильными группами преобразователя частоты для асинхронного электропривода | 1988 |

|

SU1545305A1 |

| Устройство для заряда емкостного накопителя | 1986 |

|

SU1432795A1 |

| Устройство для измерения характеристик сверхпроводящих образцов | 1989 |

|

SU1675789A1 |

Изобретение относится к импульсной технике и предназначено для использования в ключевых генераторах, вторичных источниках электропитания. Конкретно, изобретение может быть использовано в фазоимпульсном модуляторе, генерирующем две пары парафазных сигналов, так, чтобы вторая пара имела регулируемый сдвиг (временную задержку) относительно первой. Техническим результатом изобретения является упрощение схемы с одновременным повышением надежности работы за счет введения бестоковой паузы, а также расширение арсенала средств, используемых для генерации смещенных по фазе ШИМ-сигналов, например, для фазоимпульсных модуляторов. Для достижения технического результата в устройство для генерации двух пар комплементарных ШИМ-сигналов, содержащее генератор тактовой частоты (1), мастер-счетчик (4), связанный с формирователями ШИМ-сигналов, содержащими компараторы, введены схема управления (2), схема вычисления опорных сигналов и порогов срабатывания (3) и элемент НЕ (25). Мастер-счетчик (4) выполнен в виде двоично-реверсивного счетчика. Схема управления (2) имеет четыре входа, предназначенных для подачи сигналов тактового генератора, сигнала предела счета, сигнала внешней синхронизации и сигнала значения регистра мастер-счетчика, и этим входом соединена с выходом мастер-счетчика. Два формирователя ШИМ-сигналов состоят из четырех компараторов (5-8 и 9-12), определенным образом соединенных с логическими элементами И (13-16 и 19-22). Логические элементы И (13-16 и 19-22) связаны с RS-триггерами (17, 18, 23, 24). Схема вычисления опорных сигналов и порогов срабатывания (3) имеет три входа, предназначенных для подачи сигналов предела счета, фазового сдвига и бестоковой паузы. Выходы схемы вычисления опорных сигналов и порогов срабатывания (3) определенным образом соединены с компараторами формирователей ШИМ-сигналов. Выходы RS-триггеров (17, 18, 23, 24) являются выходами ШИМ-сигналов. 2 н.п. ф-лы, 6 ил.

1. Устройство для генерации двух пар комплементарных ШИМ-сигналов, содержащее генератор тактовой частоты, мастер-счетчик, связанный с формирователями ШИМ-сигналов, содержащими компараторы, отличающееся тем, что в него введены схема управления, схема вычисления опорных сигналов и порогов срабатывания, и элемент НЕ, при этом мастер-счетчик выполнен в виде двоично-реверсивного счетчика, схема управления имеет четыре входа, предназначенных для подачи сигналов тактового генератора, сигнала предела счета, сигнала внешней синхронизации и сигнала значения регистра мастер-счетчика, и этим входом соединена с выходом мастер-счетчика, при этом первый формирователь ШИМ-сигналов состоит из первого, второго, третьего и четвертого компараторов, первого, второго, третьего и четвертого логических элементов И, где первые входы компараторов соединены с выходом мастер-счетчика, выходы компараторов соединены попарно с первыми входами указанных элементов И, выходы первого и второго элементов И соединены с входами первого RS –триггера, а выходы третьего и четвертого элементов И соединены с входами второго RS-триггера; второй формирователь ШИМ-сигналов состоит из пятого, шестого, седьмого и восьмого компараторов, пятого шестого, седьмого и восьмого элементов И, при этом первые входы указанных компараторов соединены с выходом двоично-реверсивного мастер-счетчика, выходы компараторов попарно соединены с первыми входами пятого, шестого, седьмого и восьмого элементов И, выходы пятого и шестого элементов И соединены с входами третьего RS-триггера, выходы седьмого и восьмого элементов И соединены со входами четвертого RS-триггера, вход элемента НЕ, являющегося общим элементом первого и второго формирователей, соединен с выходом схемы управления, а выход элемента НЕ соединен с вторыми входами третьего, четвертого, седьмого и восьмого логических элементов И; упомянутая схема вычисления опорных сигналов и порогов срабатывания имеет три входа, предназначенных для подачи сигналов предела счета, фазового сдвига и бестоковой паузы, первый выход указанной схемы вычисления опорных сигналов и порогов срабатывания соединен со вторыми входами первого и четвертого компараторов, второй выход – со вторыми входами второго и третьего компараторов, третий, четвертый и пятый и шестой выходы соединены с вторыми входами пятого, шестого, седьмого и восьмого компараторов, соответственно, выходы RS-триггеров являются выходами ШИМ-сигналов.

2. Устройство для генерации двух пар комплементарных ШИМ-сигналов, содержащее генератор тактовой частоты, мастер-счетчик, связанный с формирователями ШИМ-сигналов, содержащими компараторы, отличающееся тем, что в него введены схема управления, схема вычисления опорных сигналов и порогов срабатывания, и элемент НЕ, при этом мастер-счетчик выполнен в виде двоично-реверсивного счетчика, схема управления имеет четыре входа, предназначенных для подачи сигналов тактового генератора, сигнала предела счета, сигнала внешней синхронизации и сигнала значения регистра мастер-счетчика и этим входом соединена с выходом мастер-счетчика, при этом первый формирователь ШИМ-сигналов состоит из первого, второго, третьего и четвертого компараторов, первого, второго, третьего и четвертого логических элементов И, где первые входы компараторов соединены с выходом мастер-счетчика, выходы компараторов соединены попарно с первыми входами указанных элементов И, выходы первого и второго элементов И соединены с входами первого RS-триггера, а выходы третьего и четвертого элементов И соединены с входами второго RS-триггера; второй формирователь ШИМ-сигналов состоит из пятого, шестого, седьмого и восьмого компараторов, пятого, шестого, седьмого и восьмого элементов И, первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, а также первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с инверсией, при этом первые входы указанных компараторов соединены с выходом двоично-реверсивного мастер-счетчика, выходы компараторов попарно соединены с первыми входами пятого, шестого, седьмого и восьмого элементов И, выходы пятого и шестого элементов И соединены с входами третьего RS-триггера, выходы седьмого и восьмого элементов И соединены со входами четвертого RS-триггера, вход элемента НЕ, являющегося общим элементом первого и второго формирователей, соединен с выходом схемы управления, а выход элемента НЕ соединен с вторыми входами третьего, четвертого логических элементов И, а также со вторыми входами второго элемента исключающее ИЛИ и второго элемента исключающее ИЛИ с инверсией, кроме того, выход схемы управления соединен с первыми входами первого элемента ИСКЛЮЧЮЩЕЕ ИЛИ и первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с инверсией, выходы которых соединены со вторыми входами пятого и шестого логических элементов И, соответственно, выходы второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с инверсией соединены с вторыми входами седьмого и восьмого элементов И, соответственно; упомянутая схема вычисления опорных сигналов и порогов срабатывания имеет три входа, предназначенных для подачи сигналов предела счета, фазового сдвига и бестоковой паузы, первый выход указанной схемы вычисления опорных сигналов и порогов срабатывания соединен со вторыми входами первого и четвертого компараторов, второй выход – со вторыми входами второго и третьего компараторов, третий, четвертый и пятый и шестой выходы соединены с вторыми входами пятого, шестого, седьмого и восьмого компараторов, соответственно, седьмой выход указанной схемы соединен с первыми входами первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, а восьмой выход – с первыми входами первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с инверсией, выходы RS-триггеров являются выходами ШИМ-сигналов.

| US 8558632 B2, 15.10.2013 | |||

| СПОСОБ ЦИФРОВОГО ФОРМИРОВАНИЯ ШИРОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ ДЛЯ ГИДРОАКУСТИКИ | 2013 |

|

RU2594918C2 |

| Цифровой широтно-импульсный модулятор | 1987 |

|

SU1478316A1 |

| ДВУХТАКТНЫЙ ФАЗОИМПУЛЬСНЫЙ МОДУЛЯТОР | 1991 |

|

RU2013859C1 |

| US 7250740 B2, 31.07.2007 | |||

| US 6937084 B2, 30.08.2005 | |||

| US 8816621 B2, 26.08.2014. | |||

Авторы

Даты

2023-06-23—Публикация

2023-01-26—Подача