Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах ЭВМ. Известно устройство для вычитания содержащее два регистра, триггер,, три элемента И, два элемента ИЛИ и два элемента задержки i . Известен также одноразрядный двоичный вычитатель, содержащий троичные логические элементы, причем первый вход первой группы и первый вход второй группы первого троичного логического элемента соединены соответственно с шинами уменьшаемого и вычитаемого одноразрядного двоичного вычитателя, а выход соединен с первым входом первой группы второго и первым и вторым входами первой группы третьего троичных логических элементов. Выход третьего троичного логического элемента соединен с первым и вторым входами первой группы четвертого- троичного логического эле мента, выход которого соединен с выходной шиной разности одноразрядного двоичного вычитателя. Выход.второго троичного логического элемента соединен с первым входом первой груп пы пятого троичного логического элемента, выход которого подключен к шийе заема одноразрядного двоичного вычитателя и первому входу первой группы шестого троичного логического элемента, выход которого соединен с вторым входом Первой группы второго и первым входом второй группы третьего троичных логических элементов 2 Недостатком известных устройств является сложность конструкции. Цель изобретения - упрощение одноразрядного двоичного вычитателя. Поставленная цель достигается тем что в одноразрядном двоичном вычитателе содержащем троичные логические элементы, причем первый вход первой группы и первый вход второй группы

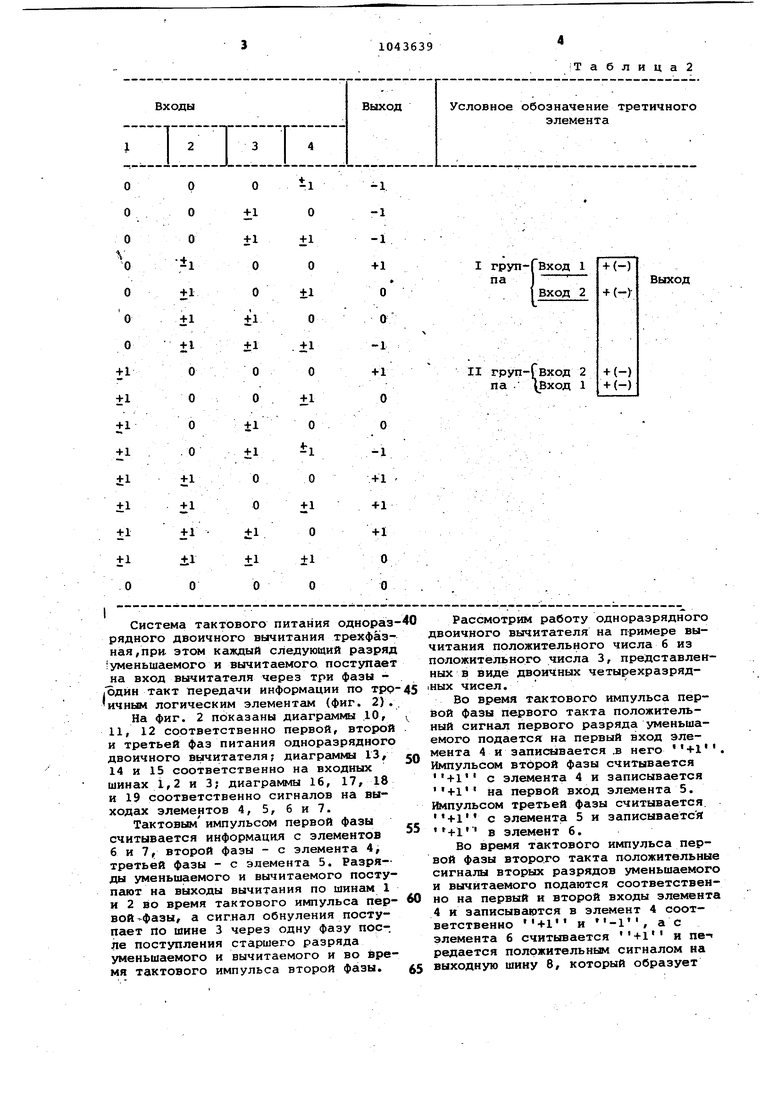

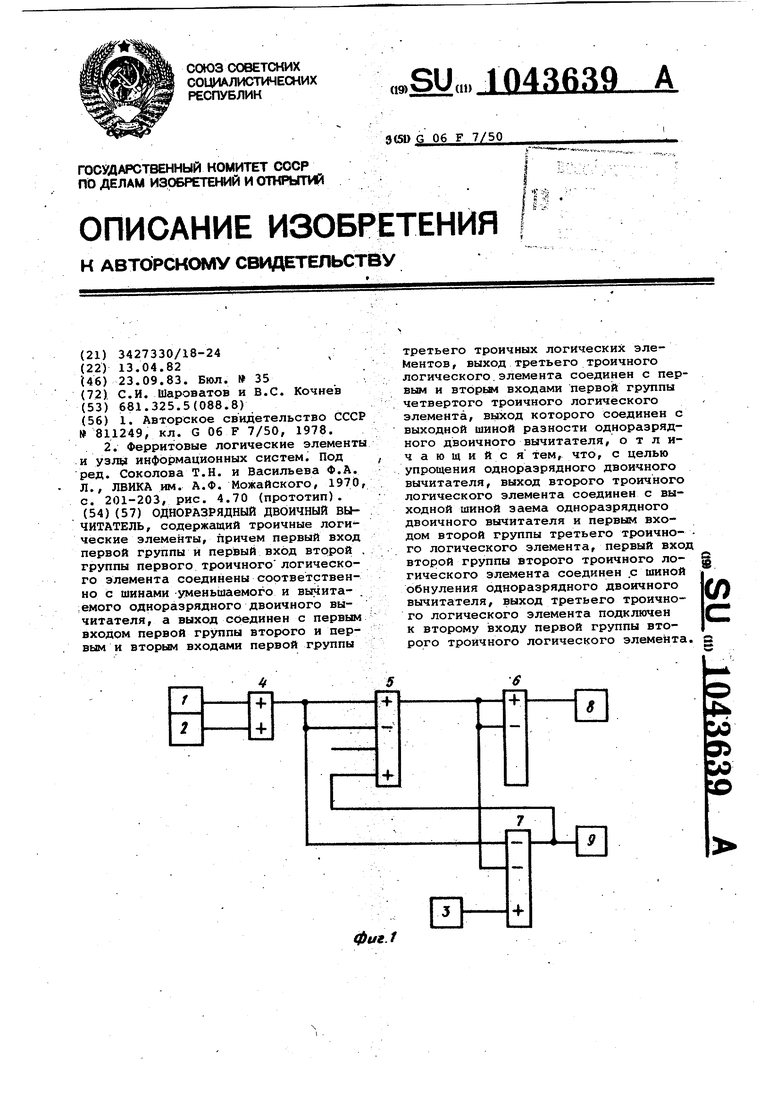

Таблица 1 первого троичного логического элемента соединены соответственно с шинами уменьшаемого и вычитаемого одноразрядного двоичного вычитателя, а выход соединен с первым входом первой группы второго и первым и вторым входами первой группы третьего троичных .логических элементов, выход третьего троичного логического элемента соединен с первым и вторым входами первой группы четвертого троичного логического элемента,, выход которого соединен с выходной шиной разности одноразрязно двоичного вычитателя,. выход второго троичного логического элемента соединен с выходной шиной заема одноразрядного двоичного вычитателя и первым входом второй группы третьего троичного логического элемента, первый вход второй группы второго троичного логического элемента соединен с шиной обнуления одноразрядного вычитателя, выход третьего троичного логического элемента подключен к второму входу первой группы второго троичного логического элемента. На фиг. 1 дана функциональная схема одноразрядного двоичного вычита- теля; на фиг. 2 - временная диаграмма работы одноразрядного двоичного вычитателя ч при вычитании положительного числа +6 из положительного числа +3. , Одноразрядный двоичный вычитатель содержит шины уменьшаемого 1 и вычитаемого 2, шину 3 обнуления, троичные логические элементы 4-7, шину 8 разности и 9 заема. Одноразрядный двоичный вычитатель выполнен на однс .двухвходовом и трех четырехвходовых троичных логических элементах, выполняющих троичные операции, описываемые соответственно в табл. 1 и 2. Указанные операции образуют функционально полную систему операций. .

Таблица2

| название | год | авторы | номер документа |

|---|---|---|---|

| Одноразрядный двоичный вычитатель | 1983 |

|

SU1124289A1 |

| Последовательный двоичный вычитатель | 1984 |

|

SU1171781A1 |

| Сумматор-вычитатель | 1984 |

|

SU1171782A1 |

| Сумматор по модулю три | 1982 |

|

SU1057941A1 |

| Реверсивный счетчик импульсов | 1986 |

|

SU1398092A1 |

| Реверсивный счетчик импульсов | 1985 |

|

SU1266000A1 |

| Реверсивный счетчик импульсов | 1985 |

|

SU1324109A1 |

| Реверсивный счетчик импульсов | 1986 |

|

SU1405110A1 |

| Реверсивный счетчик импульсов | 1986 |

|

SU1383496A1 |

| Преобразователь троичного кода 1,0,1 в двоичный код | 1982 |

|

SU1078423A1 |

ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ ВЫЧИТАТЕЛЬ, содержащий троичные логические элементы, причем первый вход первой группы и первый вход второй . группы первого троичного логического элемента соединены соответственно с шинами уменьшаемого и вычита;емого одноразрядного двоичного вычитателя, а выход соединен с первым входом первой группы второго и первым и вторым входами первой группы « -ь 4третьего троичных логических элементов , выход третьего троичного логического.элемента соединен с первым и вторым входами первой группы четвертого троичного логического элемента, выход которого соединен с выходной шиной разности одноразрядного двоичного вычитателя, о т л ич а ю щ и и с я тем, что, с целью упрощения одноразрядного двоичного вычитателя, выход второго троичного логического элемента соединен с выходной шиной заема одноразрядного двоичного вычитателя и первым входом второй группы третьего троично- го логического элемента, первый вход второй группы второго троичного логического элемента соединен с шиной обнуления одноразрядного двоичного вычитателя, выход третьего троичного логического элемента подключен к второму 1входу первой группы второго троичного логического элемента. 8 : :f : ;о фиг.1

+1

+1

+1

+1

±1

+1

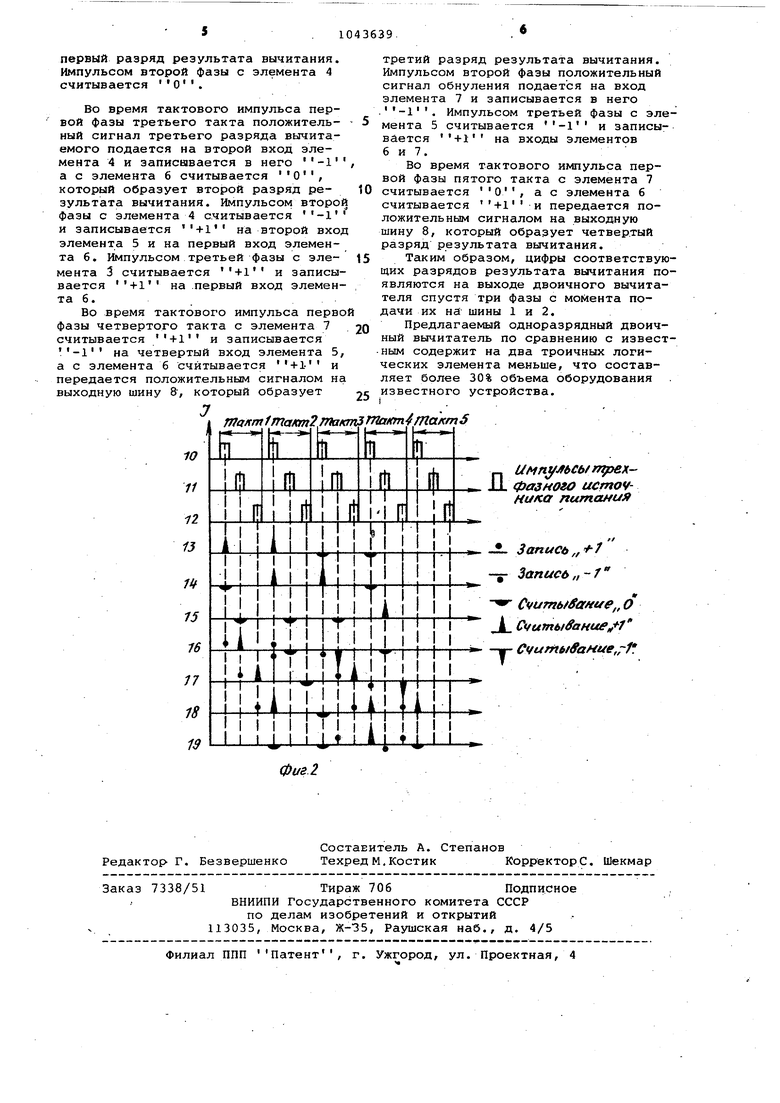

+ 1 Система тактового питания однораз рядного двоичного вычитания трехфазная,при этом каждый следующий разряд уменьшаемого и вычитаемого поступает на вход вычитателя через три фазы /один такт передачи информации по тро ичиым логическим элементам (фиг. 2). На фиг. 2 показаны диаграммы 10, 11, 12 соответственно первой, второй и третьей фаз питания одноразрядного двоичного вычитателя; диаграммы 13, 14 и 15 соответственно на входных шинах 1,2 и 3; диаграммы 16, 17, 18 и 19 соответственно сигналов на выходах элементов 4, 5, б и 7. Тактовым импульсом первой фазы считывается информация с элементов б и 7|г второй фазы - с элемента 4, третьей фазы - с элемента 5. Разряды уменьшаемого и вычитаемого поступают на выходы вычитания по шинам 1 и 2 во время тактового импульса первой фазы, а сигнал обнуления поступает по шине 3 через одну фазу пор-, ле поступления старшего разряда уменьшаемого и вычитаемого и во время тактового импульса второй фазы. Рассмотрим работу одноразрядного двоичного вычитателя на примере вычитания положительного числа б из положительного числа 3, представленных в виде двоичных четырехразряд|Ных чисел. Во время тактового импульса первой фазы первого такта положительный сигнал первого разряда уменьшаемого подается на первый вход элемента 4 и записывается .в него . Импульсом второй фазы считывается с элемента 4 и записывается на первой вход элемента 5. Импульсом третьей фазы считывается. с элемента 5 и записывается в элемент 6. Во время тактового импульса первой фазы второго такта положительные сигналы вторых разрядов уменьшаемого и вычитаемого подаются соответственно на первый к второй входы элемента 4 и записывсются в элемент 4 сооти , а с ветственно и пе-ч элемента б считывается редается положительным сигналом на выходную шину 8, который образует первый разряд результата вычитания. Импульсом второй фазы с элемента 4 считывается . Во время тактового импульса первой фазы третьего такта положительный сигнал третьего разряда вычитаемого подается на второй вход элемента 4 и записывается в него а с элемента 6 считывается О, который образует второй разряд результата вычитания. Импульсом второ фазы с элемента 4 считывается и записывается на второй вхо элемента 5 и на первый вход элемента 6. Импульсом третьей фазы с элемента 3 считывается и записы +1 на .первый вход элемен вается та 6.. Во время тактового импульса перв фазы четвертого такта с элемента 7 считывается и записывается на четвертый вход элемента 5 а с элемента б считывается и передается положительным сигналом н выходную шину В, который образует

импульсыгт иJLL фазного источника питания

г/

JL Запись ,ff-f -у Запись„-7

- Cvumbi6aHue,,d А Считывание +1 CvurfittfaHue,1. третий разряд результата вычитания. Импульсом второй фазы положительный сигнал обнуления подается на вход элемента 7 и записывается в него .. Импульсом третьей фазы с элемента 5 считывается и записывается на входы элементов 6 и 7. Во время тактового импульса первой фазы пятого такта с элемента 7 считывается О, ас элемента б считывается и передается положительным сигналом на выходную шину 8, который образует четвертый разряд результата вычитания. Таким образом, цифры соответствующих разрядов результата вычитания появляются на выходе двоичного вычитателя спустя три фазы с моМента подачи их на шины 1 и 2. Предлагаемый одноразрядный двоичный вычитатель по сравнению с известным содержит на два троичных логических элемента меньше, что составляет более 30% объема оборудования известного устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для вычитания | 1978 |

|

SU811249A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Ферритовые логические элементы и информационных систем | |||

| Под ред | |||

| Соколова Т.Н | |||

| и Васильева Ф.А | |||

| Л., ЛВИКА им | |||

| А.Ф | |||

| Можайского, 1970, с | |||

| Питательное приспособление к трепальным машинам для лубовых растений | 1922 |

|

SU201A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1983-09-23—Публикация

1982-04-13—Подача