Изобретение относится к вычислительной технике и может быть использовано в качестве мультиплексного канала ЦВМ для организации обмена информацией без прерывания работы ЦВМ и без, использования ЦВМ для выполнения подготовительных и заключительных операций по обмену.

Известно устройство обмена, которое содержит счетчик количества обкюнов (счетчик количества слбв), ресистр адреса с модификатором с1дреса (счетчик текущего гьдреса) , схему управления (блок управления), первый выход которого подключен к модификатору адреса, второй - к центральному процессору, а третий является выходом канала, управляющий вход схемы управления соединен с управляющим выходом центрального процессора. Такое устройство обмена называют селекторным каналом. Через селекторный канал к ЦВМ подключается одно ВУ или группа ВУ, работающих с разделением во времени. Операция ввода-вывода начинается в канале по запросу ЦВМ. Если канал не занят выполнением ранее поступившей команды ввода-вывод9 то программой ЦВМ в канал выдается командное слово, содержащее номер внешнего устройства, величину передаваемого массива, начальный адрес массива, код операции. На основании этих данных обеспечивается подключение селекторного канала к соответствующему ВУ и передача заданного массива информации .

Недостатком известного устройства является низкое быстродействие, обус10ловленное тем, что обмен осуществляется по инициативе ЦВМ, и если инициатором обмена в какой-либо си стеме является внешнее устройство, то оно . должно выдать -в ЦВМ сигнал внешнего

15 запроса тИпа прерывание, перевести ЦВМ на программу подготовки селекторного канала к обмену, т.е. время между запросом и началом обмена составляет : время реакции ЦВМ на внешний запрос тупа

20 прерывание и время выполнения программы подготовки селекторного каналаКроме этого, для передачи каждого -: слова из ВУ в ОЗУ ЦВМ требуется, как минимум, два рабочих цикла ЦВМ, по25скольку внешнее устройство работает с ЦВМ несинхронно.

Оргсшизация обмена между ЦВМ и ВУ через мультиплексный канал также ши.30 роко известна.

Наиболее близким к изобретению по совокупности существенных признаков является устройство обмена (мультиилексный канат), содержащее блок обработки запросов, шифратор, схему упрапен ия, элементы ИЛИ, регистр команды, модификатор адреса и счетчик крличества слов, первые входы блока обработки запросов являются входами гканала, первый выхоД схемы управления

подключен к модификатору адреса, вто рой - к центральному процессору (ЦП} а третий является выходом канала, управляющий вход cxeN«управления соединен с управляющим выходом ЦП. При организации обмена информацией между ЦВМ и внешними устройствами с помощью мультиплексного канала необходимо выполнить следующую последовательность операций:

-посылку из ЦВМ в канал адреса ячейки внутренней памяти, в которой

н аходит ся командное слово;

-формирование ЦВМ запроса на передачу командного слова/

-обработку запроса в канале (в схеме выбора запроса) ;

-выдачу командного слова в канал

-выдачу сигнала Начало работы в адресуемое ВУ;

-передачу информации и модифика,цию командного слова J

-перепись командного слова в область исполняемых командных слов внутренней памяти.

Мультиплексные каналы систем высокой производительности осуществляют передачу одного байта информации за время порядка 20-30 мкс при времени обращения в ОЗУ 1-2 мкс. По некоторым данным это время может достигать 100 мкс. Это время будет еще больше, если учесть время, расходуемое на передачу служебной и управляющей информации и передачу полноразрядных слов ( 3-4 байта 7. Причем данные о быстродействии приводятся для случая, когда инициатором обмена является проrpafiMa ЦВМ. Если же инициатором является внешнее устройство, то к указанному времени необходимо добавить время реакции ЦВМ на внешний запрос типа Прерывание, которое- при рабочем цикле ЦВМ ,6 мкс составляет . порядка 20 мкс, и время выполнения программы более высокого уровня приоритета по отношению к рассматриваемой программе запуска канала Г 2 1.

тУ-

Такое быстродействие обмена нельзя признать удовлетворительным для целого ряда внешних устройств и режимов работы отдельных управляющих вычислительных систем, что является недостатком мультиплексного канала.

Цель изобретения - повЕлчение быстродейсмвия.

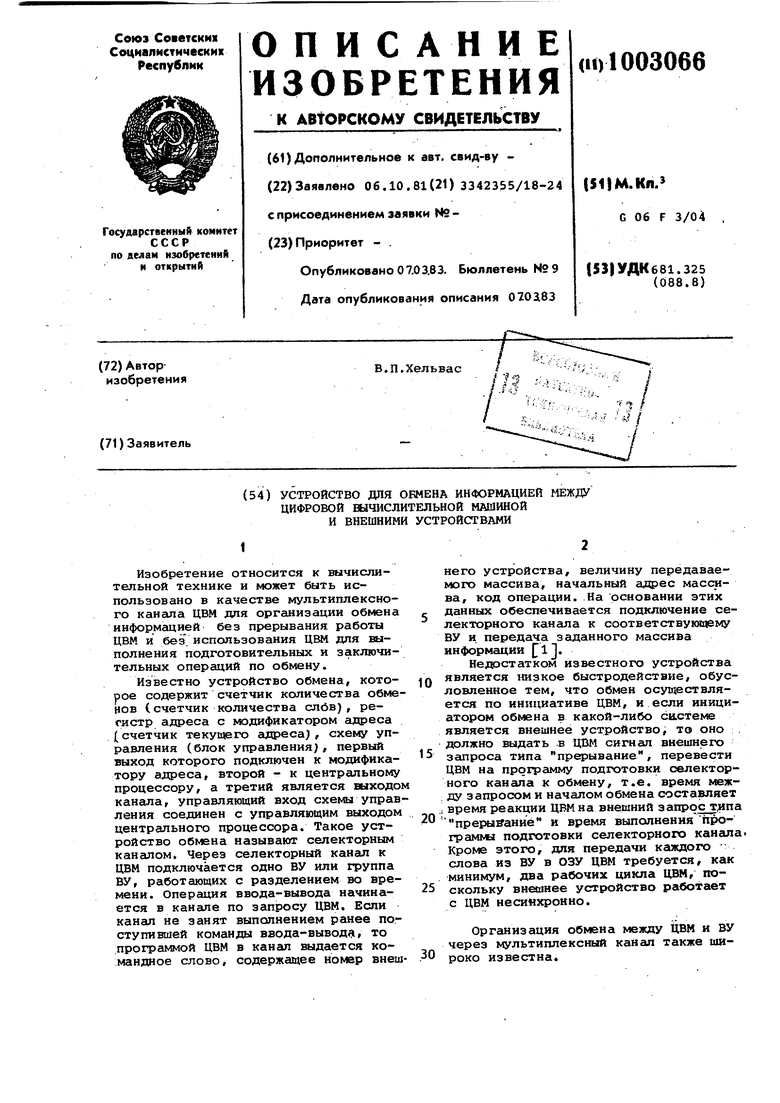

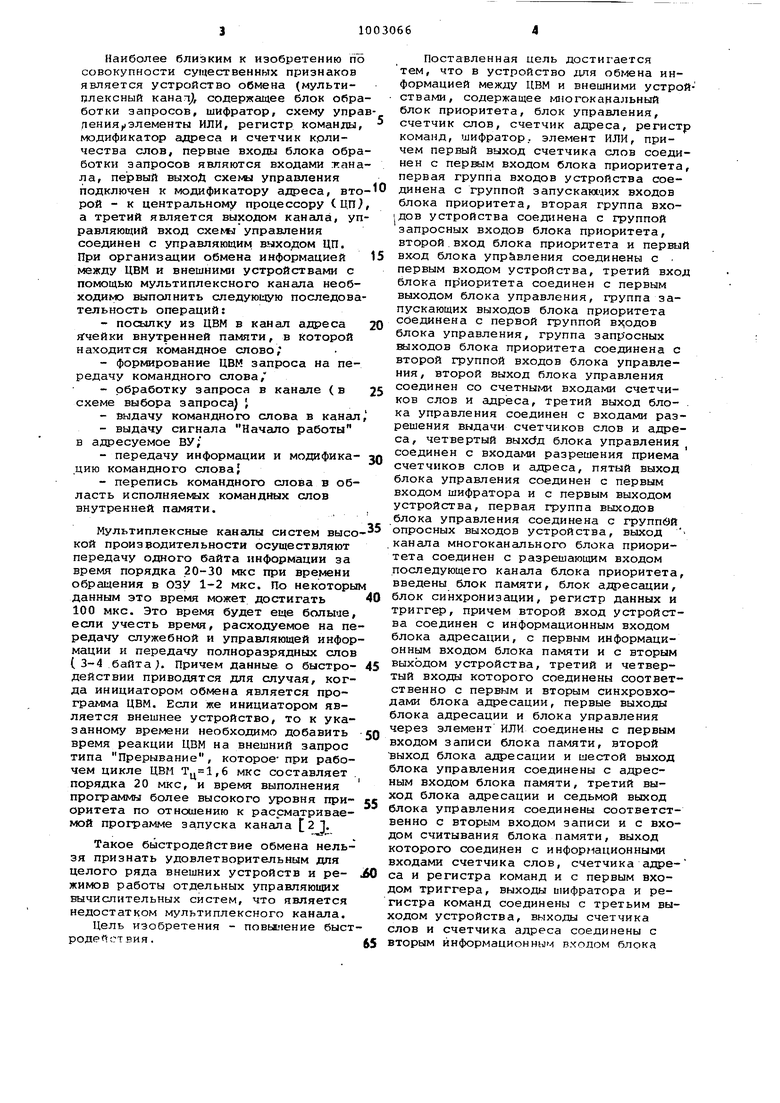

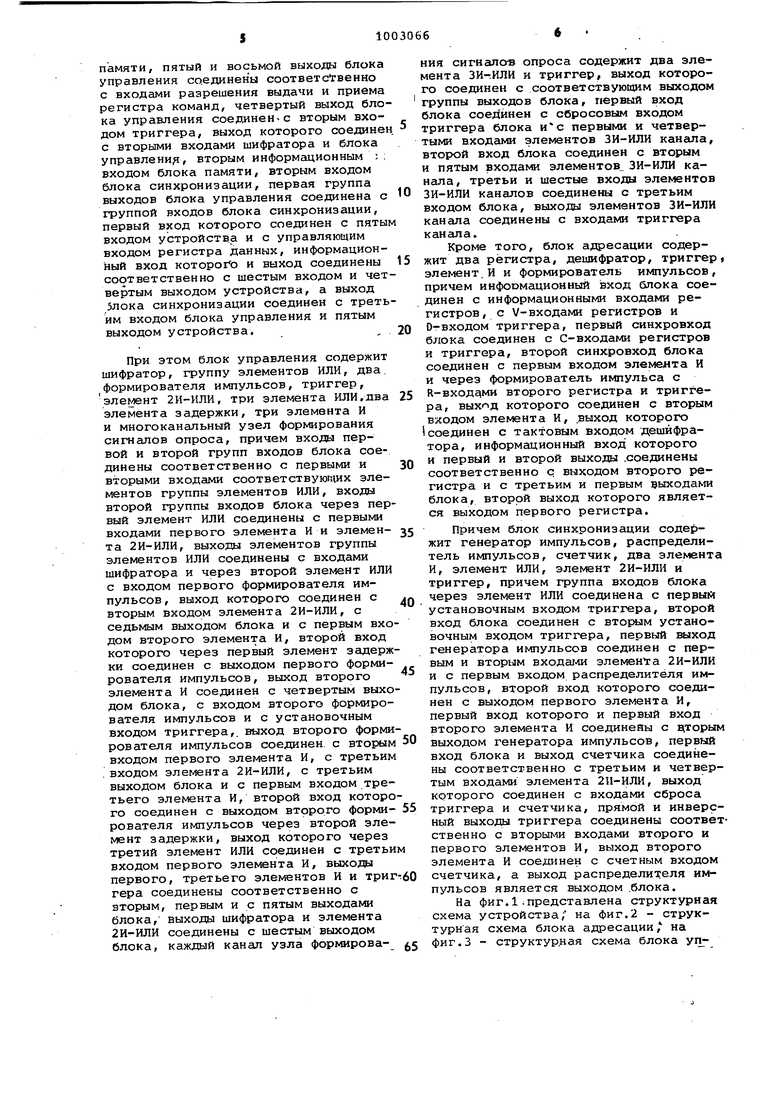

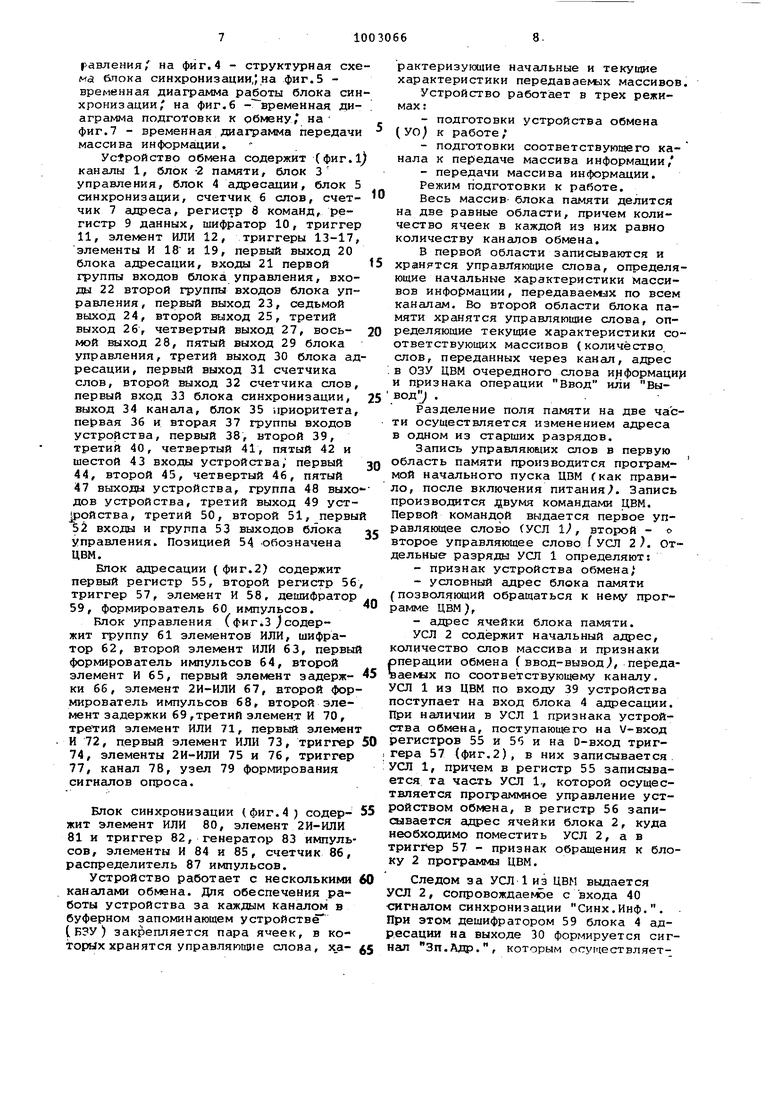

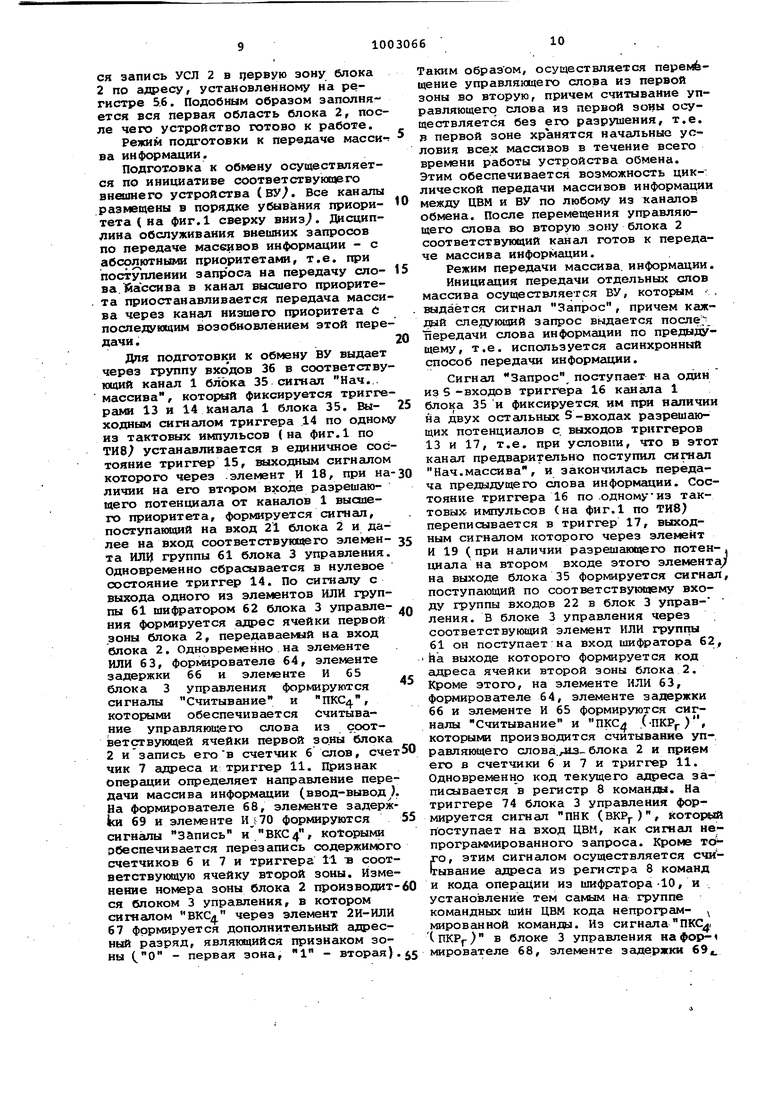

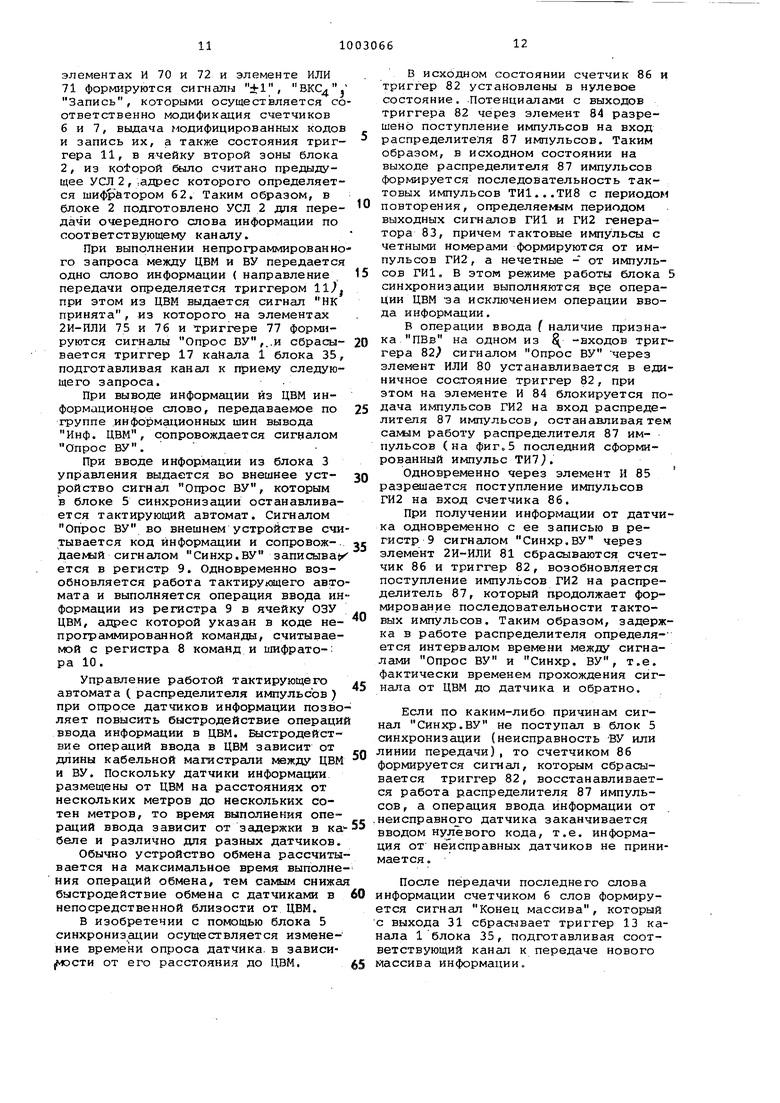

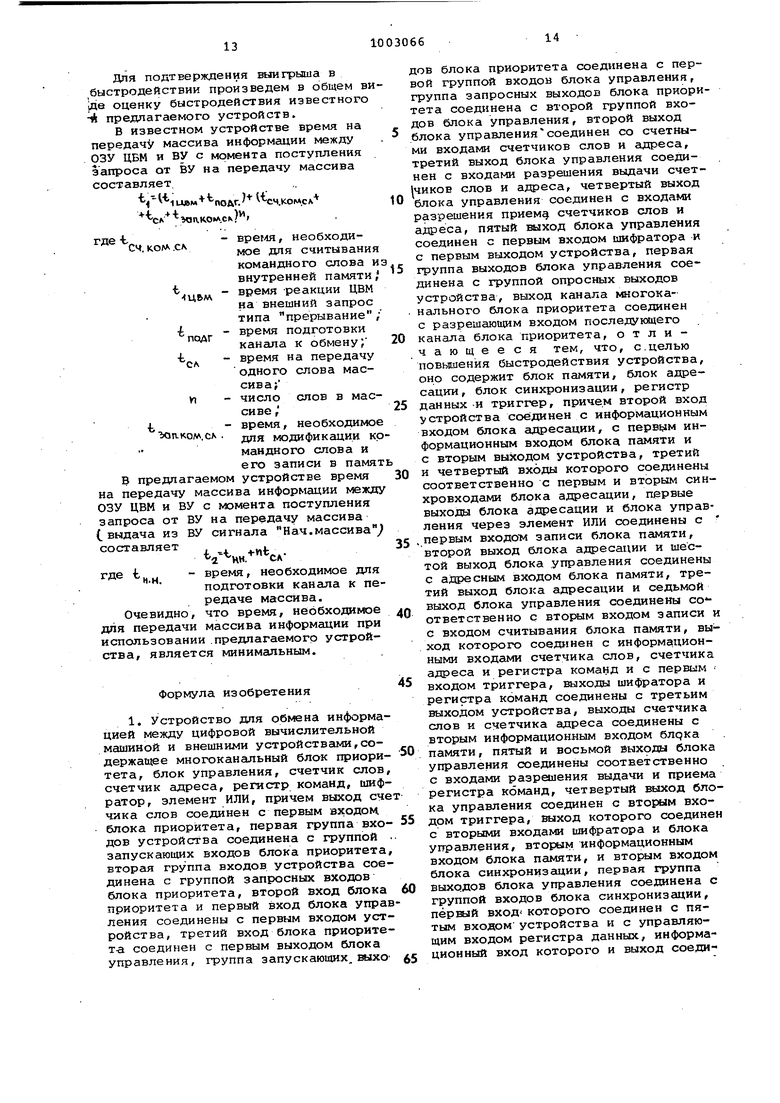

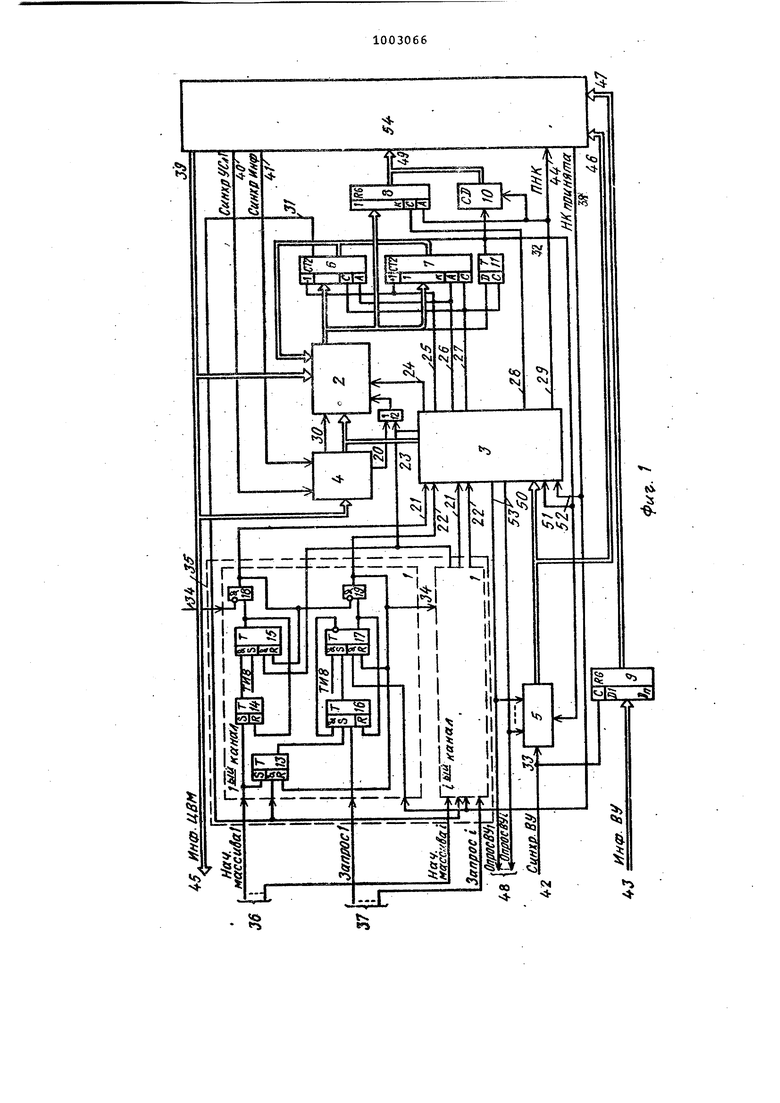

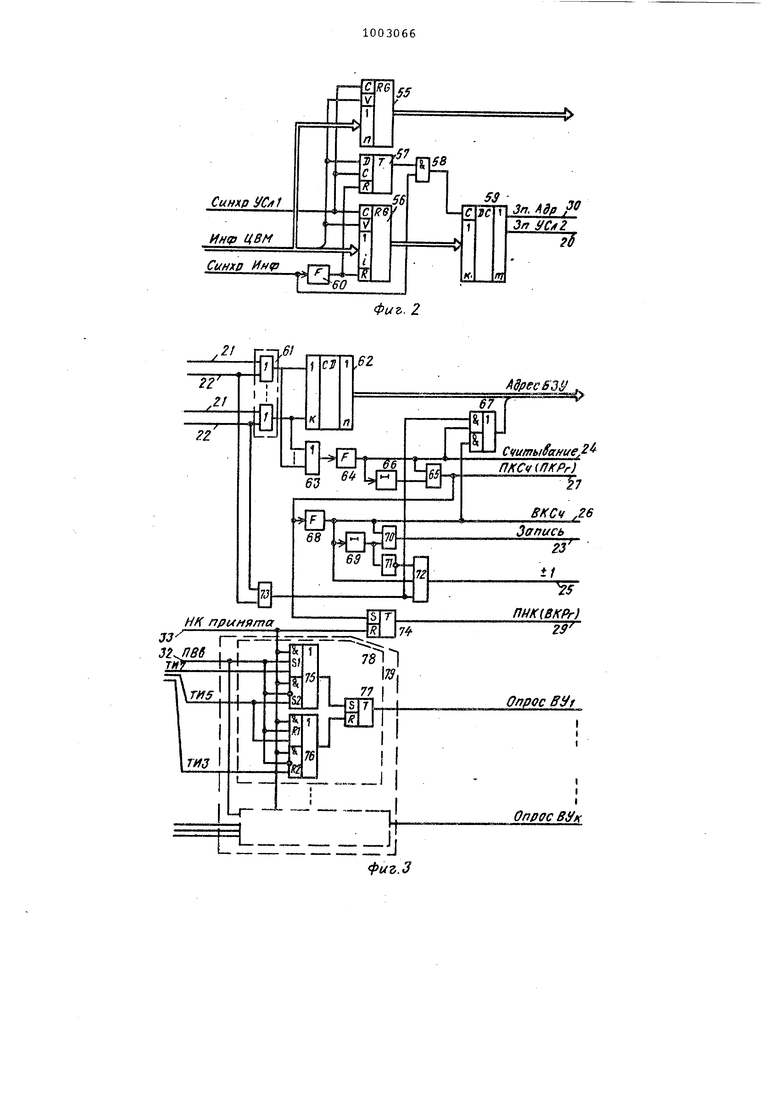

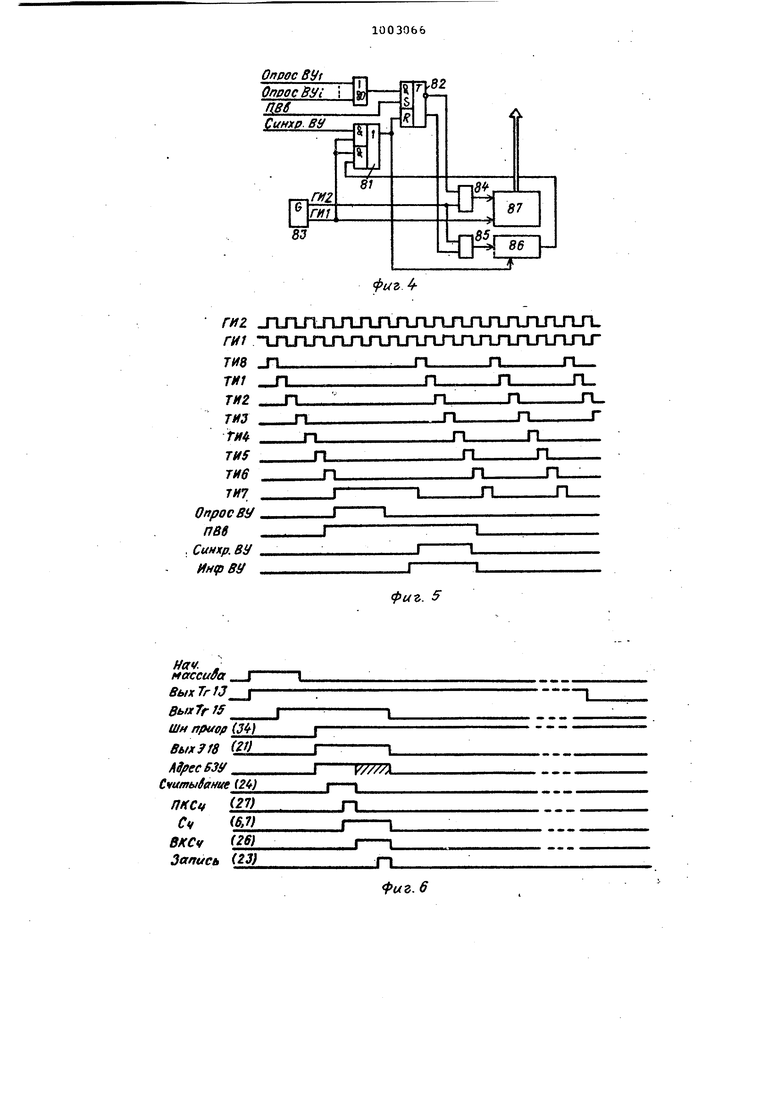

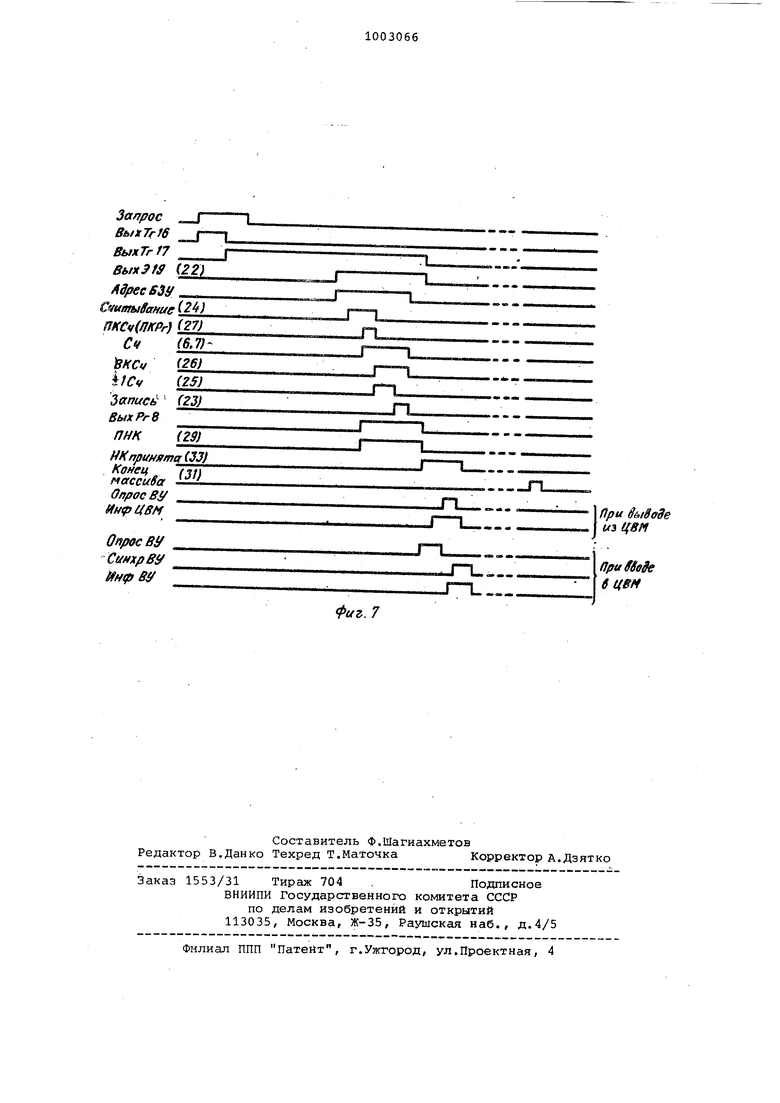

Поставленная цель достигается тем, что в устройство цля обелена информацией между ЦВМ и внешними устро ствами, содержащее мюгоканальный блок приоритета, блок управления, счетчик слов, счетчик адреса, регист команд, шифратор, элемент ИЛИ, причем первый выход счетчика слов соединен с первым входом блока приоритета первая группа входов устройства соединена с группой запускаюсиих входов блока приоритета, вторая группа вхо1ДОВ устройства соединена с группой запросных входов блока приоритета, второй.вход блока приоритета и первы вход блока управления соединены с . первым входом устройства, третий вхо блока пгэиоритета соединен с первым выходом блока управления, группа запускающих выходов блока приоритета соединена с первой группой блока управления, группа запросных выходов блока приоритета соединена с второй группой входов блока управления, второй выход блока управления соединен со счетными входами счетчиков слов и адреса, третий выход блока управления соединен с входами разрешения выдачи счетчиков слов и адреса, четвертый блока управления соединен с входг1ми разрешения приема счетчиков слов и адреса, пятый выход блока управления соединен с первым входом шифратора и с первым выходом устройства, первая группа выходов блока управления соединена с группвй опросных выходов устройства, выход канала многоканального блока приоритета соединен с разрешающим входом последующего канала блока приоритета введены блок памяти, блок адресации, блок синхронизации, регистр данных и триггер, причем второй вход устройства соединен с информационным входом блока адресации, с первым информационным входом блока памяти и с вторым выходом устройства, третий и четвертый входы которого соединены соответственно с первым и вторым синхровходами блока адресации, первые выходы блока адресации и блока управления через элемент ИЛИ соединены с первым входом записи блока , второй выход блока адресации и шестой выход блока управления соединены с адресным входом блока памяти, третий выход блока адресации и седьмой выход блока управления соединены соответственно с вторым входом записи и с входом считывания блока памяти, выход которого соединен с информационными входами счетчика слов, счетчика адреса и регистра команд и с первым входом триггера, выходы шифратора и регистра команд соединены с третьим выходом устройства, выходы счетчика слов и счетчика адреса соединены с вторым информационным входом блока памяти, пятый и восьмой выходы блока управления соединены соответственно с входами разрешения выдачи и приема регистра команд, четвертый выход бло ка управления соединение вторым входом триггера, выход которого соедине с вторыми входами шифратора и блока управление, вторым информационным ; : входом блока памяти, вторым входом блока синхронизации, первая группа выходов блока управления соединена с группой входов блока синхронизации, первый вход которого соединен с пяты входом устройства и с управляющим входом регистра данных, информационный вход которогЧэ и выход соединены соответственно с шестым входом и чет вертым выходом устройства, а выход Элока синхронизации соединен с треть им входом блока управления и пятым выходом устройства., При этом блок управления содержит шифратор, группу элементов ИЛИ, два. формирователя импульсов, триггер, элемент 2И-ИЛИ, три элемента ИЛИ.два элемента задержки, три элемента И и многоканальный узел формирования сигналов опроса, причем входы первой и второй групп входов блока соединены соответственно с первыми и вторыми входами соответствующих элементов группы элементов ИЛИ, входы второй группы входов блока через пер вый элемент ИЛИ соединены с первыми входами первого элемента И и элемента 2И-ИЛИ, выходал элементов группы элементов ИЛИ соединены с входами шифратора и через второй элемент ИЛИ с входом первого формирователя импульсов , выход которого соединен с вторым входом элемента 2И-ИЛИ, с седьмым выходом блока и с первым вхо дом второго элемента И, второй вход которого через первый элемент задерж ки соединен с выходом первого формирователя импульсов, выход второго элемента И соединен с четвертым выхо дом блока, с входом второго формирователя импульсов и с установочным входом триггера,, выход второго форми рователя импульсов соединен, с вторым входом первого элемента И, с третьим . входом элемента 2И-ИЛИ, с третьим выходом блока и с первым входом третьего элемента И, второй вход которо го соединен с выходом второго формирователя импульсов через второй элемент задержки, выход которого через третий элемент ИЛИ соединен с третьи входом первого элемента И, выходы первого, третьего элементов И и триг гера соединены соответственно с вторым, первым и с пятым выходами блока, выходы шифратора и элемента 2И-ИЛИ соединены с шестым выходом блока, каждый канал узла формирования сигношогв опроса содержит два элемента ЗИ-ИЛИ и триггер, выход которого соединен с соответствующим выходом группы выходов блока, первый вход блока соедйнен с сбросовым входом триггера блока ис первыми и четвертыми входами элементов ЗИ-ИЛИ канала, второй вход блока соединен с вторым и пятым входами элементов. ЗИ-ИЛИ канала, третьи и шестые входы элементов ЗИ-ИЛИ каналов соединены с третьим входом блока, выходы элементов ЗИ-ИЛИ канала соединены с входами триггера канала. Кроме Того, блок адресации содержит два регистра, дешифратор, триггер элемент,И и формирователь импульсов, причем информационный вход блока соединен с информационными входами регистров, с V-входами регистров и О-входом триггера, первый синхровход блока соединен с С-входами регистров и триггера, второй синхровход блока соединен с первым входом элемента И и череэ формирователь импульса с R-вход ми второго регистра и триггера, выхАд которого соединен с вторым входом элемента И, ..выход которого соединен с тактовым входом дешифратора, информационный вход которого и первый и второй выходы .соединены соответственно с. выходом второго регистра и с третьим и первым выходакт блока, второй выход которого является выходом первого регистра. Причем блок синхронизации содержит генератор импульсов, распределитель импульсов, счетчик, два элемента И, элемент ИЛИ, элемент 2И-ИЛИ и триггер, причем группа входов блока через элемент ИЛИ соединена с первый установочным входом триггера, второй вход блока соединен с вторым установочным входом триггера, первый выход генератора импульсов соединен с первым и вторым входш ш элемента 2И-ИЛИ и с первым входом распределителя импульсов, второй вход которого соединен с выходом первого элемента И, первый вход которого и первый вход второго элемента И соединены с дторым выходом генератора импульсов, первый вход блока и выход счетчика соединены соответственно с третьим и четвертым входами элемента 2И-ИЛИ, выход которого соединен с входами сброса триггера и счетчика, прямой и инверсный выходы триггера соединены соответственно с вторыми входами второго и первого элементов И, выход второго элемента И соединен с счетным входом счетчика, а выход распределителя импульсов является выходом .блока. На фиг.1 представлена структурная схема устройства; на фиг.2 - структурная схема блока адресации, на фиг.З - структурная схема блока управления, на фиг. 4 - структурная схе м,а блока синхронизации,) на фиг, 5 временная диаграмма работы блока син хронизации/ на фиг.6 - временная диаграмма подготовки к обмену, на фиг.7 - временная диаграмма передачи массива информации. Устройство обмена содержит (фиг,1 каналы 1, блок -2 памяти, блок 3 управления, блок 4 адресации, блок 5 синхронизации, счетчик 6 слов, счетчик 7 адреса, регистр 8 команд, регистр 9 данных, шифратор 10, триггер 11, элемент ИЛИ 12, триггеры 13-17, элементы И 18 и 19, первый выход 20 блока адресации, входы 21 первой группы входов блока управления, входы 22 второй группы входов блока управления, первый выход 23, седьмой выход 24, второй выход 25, третий выход 26, четвертый выход 27, восьмой выход 28, пятый выход 29 блока управления, третий выход 30 блока ад ресации, первый выход 31 счетчика слов, второй выход 32 счетчика слов, первый вход 33 блока синхронизации, выход 34 канала, блок 35 приоритета, первая 36 и вторая 37 группы входов устройства, первый 38, второй 39, третий 40, четвертый 41, пятый 42 и шестой 43 входы устройства/ первый 44, второй 45, четвертый 46, пятый 47 выходы устройства, группа 48 выхо дов устройства, третий выход 49 уст ройства, третий 50, второй 51, первы 52 входы и группа 53 выходов блока управления. Позицией 54 -обозначена ЦВМ. БЛОК адресации ( фиг,2) содержит первый регистр 55, второй регистр 56 триггер 57, элемент И 58, дешифратор 59, формирователь 60 импульсов, Нлок управления С фиг 3 J содержит группу 61 элементов ИЛИ, шифратор 62, второй элемент ИЛИ 63, первый формирователь импульсов 64, второй элемент И 65, первый элемент эадержки 66, элемент 2И-ИЛИ 67, второй формирователь импульсов 68, второй элемент задержки 69,третий элемент И 70, третий элемент ИЛИ 71, первый элемент И 72, первый элемент ИЛИ 73, триггер 74, элементы 2И-ИЛИ 75 и 76, триггер 77, канал 78, узел 79 формирования сигналов опроса. Блок синхронизации (фиг.4) содержит элемент ИЛИ 80, элемент 2И-ИЛИ 81 и триггер 82, генератор 83 импульсов, элементы И 84 и 85, счетчик 86, распределитель 87 импульсов. Устройство работает с несколькими каналами обмена. Для обеспечения работы устройства за каждым каналом в буферном запоминающем устройстве tБЗУ ) закрепляется пара ячеек, в которых хранятся управляющие слова, х.арактеризуюшие начальные и текугцие характеристики передаваемых массивов. Устройство работает в трех режимах:-подготовки устройства обмена (УО) к работе; -подготовки соответствующего канала к передаче массива информации, -передачи массива информации. Режим подготовки к работе. Весь массив блока памяти делится на две равные области, причем количество ячеек в каждой из них равно количеству каналов обмена, В первой области записываются и хранится управляющие слова, определяющие начальные характеристики массивов информации, передаваемых по всем каналам. Во второй области блока памяти хранятся управляющие слова, определяющие текущие характеристики соответствующих массивов (количество, слов, переданных через канал, адрес в ОЗУ ЦВМ очередного слова и|1формаци 1 и признака операции Ввод или Вывод .. Разделение поля памяти на две части осуществляется изменением адреса в одном из старших разрядов. Запись управляющих слов в первую область памяти производится программой начального пуска ЦВМ (как правило, после включения питания. Запись производится jцвyмя командами ЦВМ. Первой командой выдается первое управляющее слово (УСЛ 1}, второй - о второе управляющее слово ( УСЛ 2}. Отдельные разряды уел 1 определяют: -признак устройства обмена, -условный адрес блока памяти (ПОЗВОЛЯЮЩИЙ обращаться к нему программе ЦВМ), -адрес ячейки блока памяти. УСЛ 2 содержит начальный адрес, количество слов массива и признаки операции обмена f в вод-вывод ), передаBaeNMX по соответствующему каналу, УСЛ 1 из ЦВМ по входу 39 устройства поступает на вход блока 4 адресации. При наличии в УСЛ 1 признака устройства обмена, поступающего на V-вход регистров 55 и 56 и на D-вход триггера 57 (фиг,2), в них записывается УСЛ 1, причем в регистр 55 записывается та часть УСЛ 1-, которой осуществляется программное управление устройством обмена, в регистр 56 записывается адрес ячейки блока 2, куда необходимо поместить УСЛ 2, а в триггер 57 - признак обращения к блоку 2 программы ЦВМ. Следом за УСЛ 1 из ЦВМ выдается УСЛ 2, сопровождаемое с входа 40 сигналом синхронизации Синх.Инф.. При этом дешифратором 59 блока 4 адресации на выходе 30 формируется сигнал Зп.Адр., которым осуществляется запись УСЛ 2 в первую зону блока 2 по адресу, установленному на регистре 5,6. Подобным образом заполняется вся первая область блока 2, после чего устройство готово к работе.

Режим подготовки к передаче массива информёщии.

Подготовка к обмену осуществляется по инициативе соответствуюсцего внешнего устройства (ВУ. Все каналы размещены в порядке убывания приоритета ( на фиг.1 сверху вниз. Дисциплина обслуживания внешних запросов по передаче массивов информации - с абсолютными приоритетами, т.е. при поступлении запроса на передачу елова.йассива в канал высшего приоритета приостанавливается передача массива через канал низшего приоритета с последующим возобновлением этой передачи .

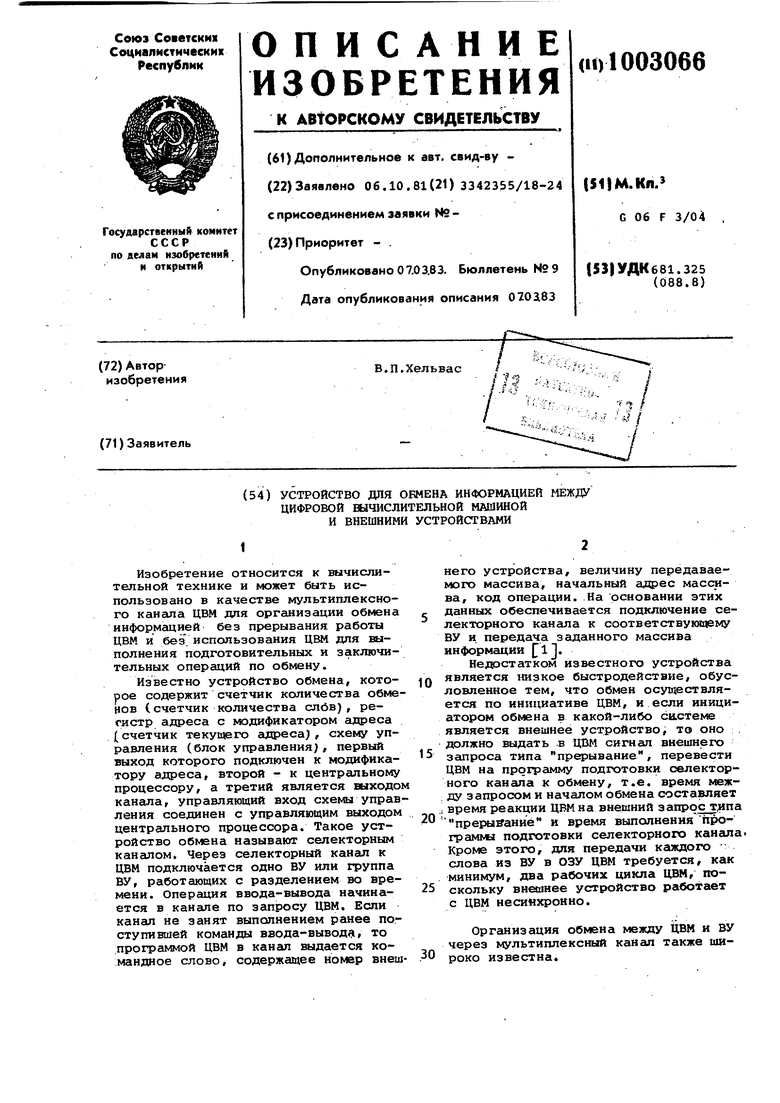

Для подготовкой к обмену ВУ выдает через группу входов 36 в соответствующий канал 1 блока 35 сигнал Нач... массива, который фиксируется триггерами 13 и 14 канала 1 блока 35. Выходным сигналом триггера 14 по одному из тактовых импульсов (на фиг.1 по ТИ87 устанавливается в единичное состояние триггер 15, к:1ходиым сигналом которого через .элемент И 18, при наличии на его втором входе разрешающего потенциала от каналов 1 высшего приорит ет а, формируется си гн ал, поступающий на вход 21 блока 2 и далее на вход соответствующего элемента ИЛИ группы 61 блока 3 управления. Одновременно сбрасывается в нулевое состояние триггер 14. По сигналу с выхода одного из элементов ИЛИ группы 61 шифратором 62 блока 3 управления формируется адрес ячейки первой зоны блока 2, передаваемый на вход блока 2. Одновременно на элементе ИЛИ 63, формирователе 64, элементе задержки 66 и И 65 блока 3 управления формируются сигналы Считывание и ПКС, которыми обеспечивается считывание управляющего слова из соответствующей ячейки первой зо.ны блока 2 и запись егов счетчик 6 слов, счет чик 7 адреса и триггер 11. Признак операции определяет направление передачи массива информации (ввод-вывод ). На формирователе 68, элементе задерж4си 69 и элементе формируются сигналы запись и которыми Обеспечивается перезапись содержимого счетчиков 6 и 7 и триггера 11 в соответствующую ячейку второй зоны. Изменение номера зоны блока 2 производится блоком 3 управления, в котором сигнёлом через элемент 2И-ИЛИ 67 формируется дополнительный адресный разряд, являющийся признаком зоны (0 - первая зона, 1 - вторая).

Таким образом, осуществляется перемещение управляйтего слова из первой зоны во вторую, причем считывание управляющего слова из первой зоны осуществляется без его разрушения, т.е. в первой зоне хранятся начальные условия всех массивов в течение всего времени работы устройства обмена. Этим обеспечивается возможность цик-: лической передачи массивов информации между ЦВМ и ВУ по любому из каналов обмена. После перемещения управляющего слова во вторую зону блока 2 соответствующий канал готов к передаче массива информации.

Режим передачи массива, информации.

Инициация передачи отдельных слов массива осуществляется ВУ, которым илдаётся сигнал Запрос, причем каждый спедуюсдай запрос выдается после, передачи слова информации по предыдащему, т.е. используется асинхронный способ передачи информации.

Сигнёш Запрос поступает на один из S -входов триггера 16 канала 1 блока 35 и фиксируется, им при наличии на двух остальных S-входах разрешающих потенциалов с. выходов триггеров 13 и 17, т.е. при условии, что в этот канал предварительно поступил сигнал Нач.массива, и закончилась передача предыдущего слова информации. Состояние триггера 16 по .одномуиз тактовых импульсов (на фиг.1 по ТИ8) переписывается в триггер 17, выходным сигналом которого через элемент И 19 (при наличии разрешающего потенциала на втором входе этого элемента на выходе блока 35 формируется сигнгш поступающий по соответствующему входу группы входов 22 в блок 3 управления. В блоке 3 управления через соответствующий элемент ИЛИ группы 61 он поступаетна вход шифратора 62

ha выходе которого формируется код адреса ячейки второй зоны блока 2. Кроме этого, на элементе ИЛИ 63, формирователе 64, элементе задержки 66 и элементе И 65 формируются сигналы Считывание и (-ПКРг), которыми производится считывание управляющего cлoвa.Jiз блока 2 и прием его в счетчики 6 и 7 и триггер 11. Одновременно код текущего адреса записывается в регистр 8 команды. На триггере 74 блока 3 управления формируется сигнал ПИК (ВКР ) , kOTOi поступает на вход ЦВМ, как сигнгш непрограммированного запроса. Кроме тсиго, этим сигналом осуществляется C4rf(тывание адреса из регистра 8 команд и кода операции из шифратора-10, и установление тем самым на группе командных шин ЦВМ кода непрограм- мированной команды. Из сигнала ПКС

(riKPf-) в блоке 3 управления на фор-ч мирователе 68, элементе задержки 69.

элементах И 70 и 72 и элементе ИЛИ 71 формируются сигналы ±1, Запись, которыми осуществляется соответственно модификащия счетчиков б и 7, вьодача модифицированных кодов и запись их, а также состояния триггера 11, в ячейку второй зоны блока 2, из которой было считано предыдущее УСЛ 2 , ;адрес которого определяется шифратором 62, Таким образом, в блоке 2 подготовлено УСЛ 2 для передачи очередного слова информации по соответствующему каналу.

При выполнении непрограммированного запроса между ЦВМ и ВУ передается одно слово информации ( направление передачи определяется триггером при этом из ЦВМ выдается сигнал НК принята, из которого на элементах 2И-ПЛИ 75 и 76 и триггере 77 формируются сигналы Опрос ВУ,..и сбрасывается триггер 17 каНала 1 блока 35, подготавливая канал к приему следующего запроса.

При выводе информации из ЦВМ информацион ое слово. Передаваемое по группе информационных шин вывода Инф. ЦВМ, сопровождается сигналом Опрос ВУ.

При вводе информации из блока 3 yпpiaвлeния выдается во внешнее устройство сигнал Опрос ВУ, которым в блоке 5 синхронизации останавливается тактирующий автомат. Сигналом Опрос ВУ во внешнем устройстве считывается код информации и сопровож-. даемый сигналом Синхр.ВУ эапксыва ется в регистр 9. Одновременно возобновляется работа тактируквдего автомата и выполняется операция ввода ИН формации из регистра 9 в ячейку ОЗУ ЦВМ, адрес которой указан в коде непрограммированной команды, считываемой с регистра 8 команд и шифрато-: ра 10.

Управление работой тактирующего автомата ( распределителя импульсов ) при опросе датчиков информации позволяет повысить быстродействие операций ввода информации в ЦВМ. Быстродействие операций ввода в ЦВМ зависит от длины кабельной магистрали между ЦВМ и ВУ. Поскольку датчики информации размещены от ЦВМ на расстояниях от нескольких метров до нескольких сотен метров, то время выполнения операций ввода зависит от задержки з ка беле и различно для разных датчиков.

Обычно устройство обмена рассчитывается на максимальное время выполнения операций обмена, тем самым снижая быстродействие обмена с датчиками в непосредственной близости от ЦВМ.

В изобретении с помощью блока 5 синхронизации осуществляется изменение времени опроса датчика, в зависи сти от его расстояния до ЦВМ.

В исходном состоянии счетчик 86 и триггер 82 установлены в нулевое состояние. Потенциалами с выходов триггера 82 через элемент 84 разрешено поступление импульсов на вход распределителя 87 импульсов. Таким образом, в исходном состоянии на выходе распределителя 87 импульсов формируется последовательность тактовых импульсов ТИ1...ТИ8 с периодом повторения, определяемым периодом выходных сигналов ГИ1 и ГИ2 генератора 83, причем тактовые импульсы с четными номерами формируются от импульсов ГИ2, а нечетные - от импульсов ГИ1, В этом режиме работы блока синхронизации выполняются вре операции ЦВМ за исключением операции ввода информсщии.

В операции ввода ( наличие признака ПВв на одном из -входов триггера 82 сигналом Опрос ВУ через элемент ИЛИ 80 устанавливается в единичное состояние триггер 82, при этом на элементе И 84 блокируется подача импульсов ГИ2 на вход распределителя 87 импульсов, останавливая Te самлм работу распределителя 87 импульсов (на фиг„5 последний сформированный импульс ТИ7.

Одновременно через элемент И 85 разрешается поступление импульсов ГИ2 на вход счетчика 86.

При получении информации от датчика одновременно с ее записью в регистр 9 сигналом Синхр.ВУ через элемент 2И-ИЛИ 81 сбрасываются счетчик 86 и триггер 82, возобновляется поступление импульсов ГИ2 на распределитель 87, который продолжает формирование последовательности тактовых импульсов. Таким образом, задержка в работе распределителя определяется интервалом времени между сигналами Опрос ВУ и Синхр. ВУ, т.е. фактически временем прохождения сигнала от ЦВМ до датчика и обратно.

Если по каким-либо причинам сигнал Синхр.ВУ не поступал в блок 5 синхронизации (неисправность ВУ или линии передачи), то счетчиком 86 формируется сигнал, которым сбрасывается триггер 82, восстанавливается работа распределителя 87 импульсов , а операция ввода информации от .неисправно го датчика заканчивается вводом нулевого кода, т.е. информация от неисправных датчиков не принимается.

После передачи последнего слова информации счетчиком 6 слов формируется сигнал Конец массива, который с выхода 31 сбрасывает триггер 13 канала 1 блока 35, подготавливая соответствующий канал к передаче нового массива информации. Для подтверждения выигрыша в быстродействии произведем в общем ви |Дв оценку быстродействия известного -А предлагаемого устройств. В известном устройстве время на передачу массива информации между ОЗУ ЦВМ и ВУ с момента поступления запроса от ВУ на передачу массива составляет. . СЧ.|СОМ.СА .KOlACIk -Bpet«i, необходиСч. ком. .с мое для считывания командного слова и внутренней памяти tUbM -реакции ЦВМ на внешний запрос типа прерывание i - время подготовки кансша к обмену; -время на передачу одного слова массива;-число слов в массиве , -время, необходамое ьоп.ком ел . для модификации ко мандного слова и его записи в памят В предлагаемом устройстве время на передачу массива информации между ОЗУ ЦВМ и ВУ с кюмента поступления запроса от ВУ на передачу массива С выдача из ВУ сигнала Нач,массива составляет , .сл- время, необходимое для подготовки канала к передаче массива. Очевидно, что время, необходимое для передачи массива информации при использовании .предлагаемого устройства, является минимальным. Формула изобретения 1. Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами,содержащее многоканальный блок приоритета, блок управления, счетчик слов счетчик адреса, рюгистр команд, шифратор, элемент ИЛИ, причем выход сче чика слов соединен с первым входон блока приоритета, первгш группа входов устройства соединена с группой запускающих входов блока приоритета вторая группа входов устройства соединена с группой запросных входов блока приоритета, второй вход блока приоритета и первый вход блока управ ления соединены с первым входом устройства, третий вход блока приоритета соединен с первым выходом блока управления, группа запускающих, выхо дов блока приоритета соединена с первой группой входов блока управления, группа запросных выходов блока приоритета соединена с второй группой входов блока управления, второй выход блока управлениясоединен со счетными входами счетчиков слов и адреса, третий выход блока управления соединен с входами разрешения выдачи счетчиков слов и адреса, четвертый выход блока управления соединен с входами разрешения приему счетчиков слов и адреса, пятый выход блока управления соединен с первым входом шифратора и с первым выходом устройства, первая группа выходов блока управления соединена с группой опросных выходов устройства, выход канала многоканального блока приоритета соединен с разрешающим входом последующего канала блока приоритета, отличающееся тем, что, с.целью повышения быстродействия устройства, оно содержит блок памяти, блок адресации, блок синхронизации, регистр данных-и триггер, причем второй вход устройства соединен с информационным входом блока адресации, с первым информационным входом блока памяти и с вторым выходом устройства, третий и четвертый входы которого соединены соответственно с первым и вторым синхровходами блока адресации, пэрвые выходы блока адресации и блока управления через элемент ИЛИ соединены с первым входом записи блока памяти, второй выход блока адресации и шестой выход блока управления соединены с адресным входом блока памяти, третий выход блока адресации и седьмой выход блока управления соединены соответственно с вторым входом записи и с входом считывания блока пелшти, выход которого соединен с информационными входами счетчика слов, счетчика адреса и регистра команд и с первым входом триггера, выходы шифратора и регистра команд соединены с третьим выходом устройства, выходы счетчика слов и счетчика адреса соединены с вторым информационным входом блрка памяти, пятый и восьмой выхртел блока управления соединены соответственно с входами разрешения выдачи и приема регистра команд, четвертый ийход блока управления соединен с вторым входом триггера, выход которого соединен с вторыми входами шифратора и блока управления, вторым информационным входом блока памяти, и вторым входом блока синхронизсщии, первая группа выходов блока управления соединена с группой входов блока синхронизации, первый ВХОД которого соединен с пятым входом устройства и с управляющим входом регистра данных, информационный вход которого и выход соедийены соответственно с шестым входом и с четвертым выходом устройства, а выход блока синхронизации соединен третьим входом блока управления и с пятым выходом устройства. 2. Устройство по п.1, о т л и ч ю щ е е с я тем, что блок управления содержит шифратор, группу элеме тов ИЛИ, два формирователя импульсо триггер, элемент 2И-ИЛИ, три элемен та ИЛИ, два элемента задержки, три элемента И и многоканальный узел фор мирования сигналов опроса, причем входы первой и второй групп входов блока соединены соответственно с пер выми и вторыми входами соответствую щих элементов группы элементов ИЛИ, входы второй группы входов блока через первый элемент ИЛИ соединены с первыми входами первого элемента И и элемента 2И-ИЛИ, выходы элементов группы элементов ИЛИ соединены с входами шифратора и через второй эле мент ИЛИ с входом первого формирователя импульса, выход которого соединен с вторым входом элемента 2И-ИЛИ с седьмым выходом блока и с первым входом второго элемента И, второй вход которого Через первый элемент задержки соединен с выходом первого формирователя импульсов, выход второго элемента И соединен с четвертым йыходом блока, с входом второго формирователя импульсов и с установочным входом триггера, выход второго формирователя импульсов соединен с Вторым входом первого элемента И, с .третьим входом элемента 2И-ИЛИ, с третьим входом блока и с первым входом третьего элемента И, второй вход которого соединен с выходом второго формирователя импульсов через второй задержки, выход которого через третий элемент ИЛИ соединен с третьим входом первого элемента И, выходы первого, третьего элементов И и триггера соединены соответственно с вторым, первым и с пятым выходами блока, выходы шифратора и элемента 2И-ИЛИ соединены с шестым выходом блока, каждый канал узла формирования сигналов опроса содержит два эле мента ЗИ-ИЛИ и триггер, выход которо го соединен с соответствующим выходо группы выходов блока, первый вход блока соединен с сбросовым входом триггера и с первыми и четвертыми входами элементов ЗИ-ИЛИ канала, вто рой вход блока соединен с вторым и пятым входами элементов ЗИ-ИЛИ канала, третьи и шестые входы элементов ЗИ-ИЛИ каналов соединены с третьим входом блока, выходы элементов ЗИ-ИЛ канала соединены с входами триггера канала. 3.Устройство по п.1, отличающееся тем, что блок адресации содержит два регистра, дешифратор, триггер,- элемент И и формирователь имп-ульсов, причем информационный вход блока соединен с информационными входами регистров, с V-входами регистров и D-входом триггера, первый синхровход блока соединен с С-входами регистров и триггера, второй синхровход блока соединен с первым входом элемента И и через формирователь импульса с R-входами второго регистра и триггера, выход которого соединен с вторым входом элемента-И, выход которого соединен с тактовым входом дешифратора, информационный вход кото рого и первый и второй выходы соединены соответственно с выходом второго регистра и с третьим и первым выходам ми блока, второй выход которого является выходом первого регистра. 4.Устройство ПОП.1, отлича ю щ е е с я тем, что блок синхронизации содержит генератор импульсов, распределитель импульсов, счетчик, два элемента И, элемент ИЛИ, элемент 2И-ИЛИ и триггер, причем группа входов блока через элемент ИЛИ соединена с первым установочным входом триггера, второй вход блока соединен с вторым установочным входом триггера, первый выход генератора импульсов соединен с первым и вторым входами элемента 2И-ИЛИ и с первым входом распределителя импульсов, второй вход которого соединен с выходом первого элекйнта.И, первый вход которого и первый вход второго элемента И соединейы с вторым выходом генератора импульсов, первый вход блока и выход счетчика соединены соответственно с третьим и четвертым входами элемента 2И-Ш1И, выход которого соединен с входами сброса триггера и счетчика, прямой и инверсный, выходы триггера ;соединены соответственно с вторыми входЕвет второго и первого элементов И, выход второго элемента И соединен .с счетным входом счетчика, а выход распределителя импульсов является выходом блока. Источники й1 формацйи, принятые во внимание при экспертизе 1.Дроздов Е.А. и др. Электронные вычислительные машины Единой системы. М., Машиностроение, 1976, с. 455, рис. 13.5. 2.Карцев М.А.Архитектура цифровых вычислительных машин. М., Наука 1978, с. 265, рис. 3,9.

Фи&. 2

p

Т

л

&.-:.

ОпросВУк

фиг. У

Опрос ВУ(

83

фиг

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Устройство для обмена информацией между ЦВМ и внешними устройствами | 1980 |

|

SU907537A1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1982 |

|

SU1062681A2 |

| Устройство для сопряжения вычислительной машины с магистралью | 1981 |

|

SU980088A2 |

| Устройство для ввода информации | 1982 |

|

SU1130854A1 |

| Устройство для сопряжения цифровой вычислительной машины с общей магистралью | 1980 |

|

SU907536A1 |

| Устройство для обмена информацией управляющей вычислительной машины с объектами управления | 1979 |

|

SU783782A2 |

| Имитатор абонентов | 1983 |

|

SU1291987A1 |

| Устройство для ввода информации | 1987 |

|

SU1432544A1 |

| Устройство для сопряжения цифровойВычиСлиТЕльНОй МАшиНы C ВНЕшНиМиуСТРОйСТВАМи | 1979 |

|

SU849190A1 |

фиг. 5

Hav. ftaccuffa Г

Вых Тг /J |Bbix7f}5

Шм nfMop (3ft) 21) AipecSSy

читыйание (2)

HKCif (27)

Сч (6Л)

ВКСч (2S}

Запись (23)

Y////A.

TL

1 при в1,1воЗе ЛигЦВ

npufSe9e 6 цен

фиг. 7

Авторы

Даты

1983-03-07—Публикация

1981-10-06—Подача