ЬФ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1981 |

|

SU1003066A1 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Устройство для ввода информации | 1982 |

|

SU1130854A1 |

| Устройство для сопряжения вычислительной машины с магистралью | 1981 |

|

SU980088A2 |

| Буферное запоминающее устройство | 1988 |

|

SU1583938A1 |

| Устройство для сопряжения вычислительнойМАшиНы C ТЕРМиНАлАМи | 1979 |

|

SU798786A1 |

| Устройство для обмена информацией между ЦВМ и внешними устройствами | 1980 |

|

SU907537A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Устройство для сопряжения ЭВМ с внешним устройством | 1986 |

|

SU1401470A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЯ | 1994 |

|

RU2108623C1 |

Изобретение относится к вычислительной технике и может быть использовано для построения управляющих вычислительных систем. Цель изобретения - повышение быстродействия устройства при опросе датчиков информации за счет снижения времени, необходимого для ввода информации в ЦВМ от датчиков. Устройство для ввода информации содержит блок 1 Hav.ycman. управления, блок 2 адресации внецг- него устройства, блок 3 обращения, буферное запоминающее устройство 4, группу информационных тин 5 ЦВМ, группу адресных шин 8 внешнего устройства, группу информационных шин 9 внешнего устройства, шину 10 чтения ЦВМ, шину 11 готовности, шину 12 записи блока адресации, rpjmny шин 13 адреса блока адресации, шину 14 чтения блока адресации, шину 15 синхронизации адреса внешнего устройства, шину 16 тактов, иину 17 синхронизации информации внешнего устройства, группу шин 18 адреса б5п|)ерного запоминающего устройства, группу шин S 19 данных буферного запоминающего устройства, шину 20 записи буферного запоминающего устройства, шину 21 чтения буферного запоминающего устройства, шину 22 записи ЦВМ и шину 23 сброса. 2 з„п. ф-лы, 5 ил.

Изобретение относится к области вычислительной техники и может быть использовано для построения управ- ляюи;их вычислительных системо

Цель изобретения - повьпиение быстродействия устройства

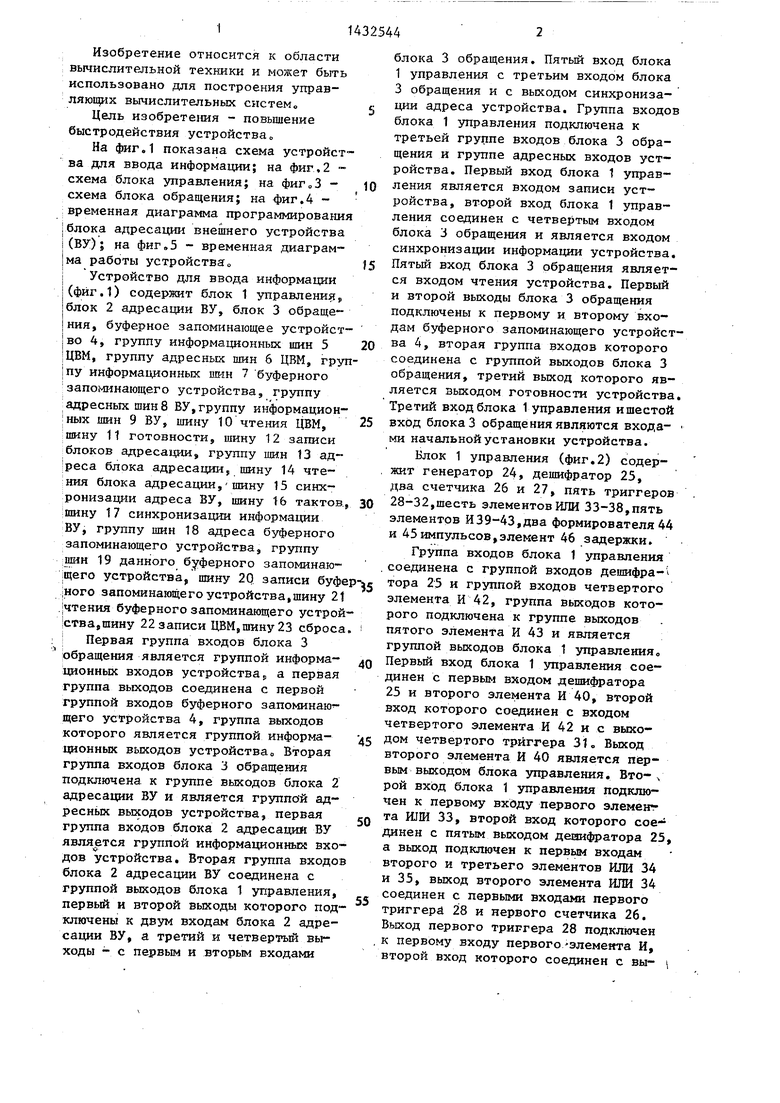

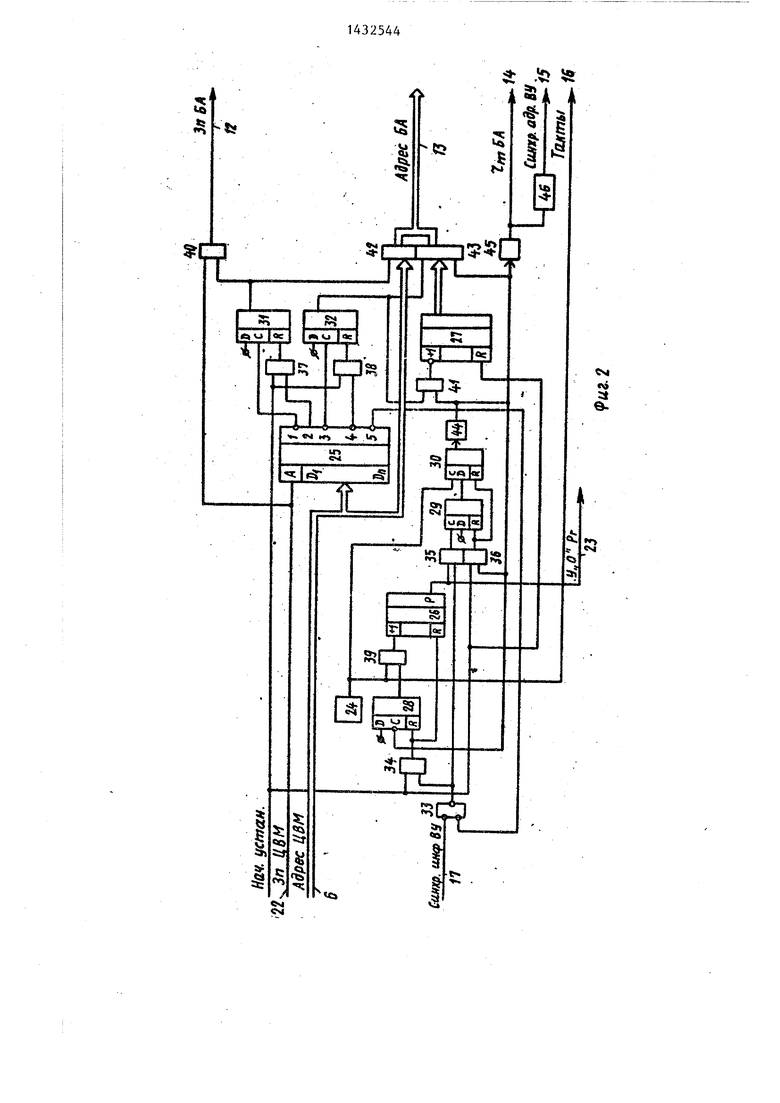

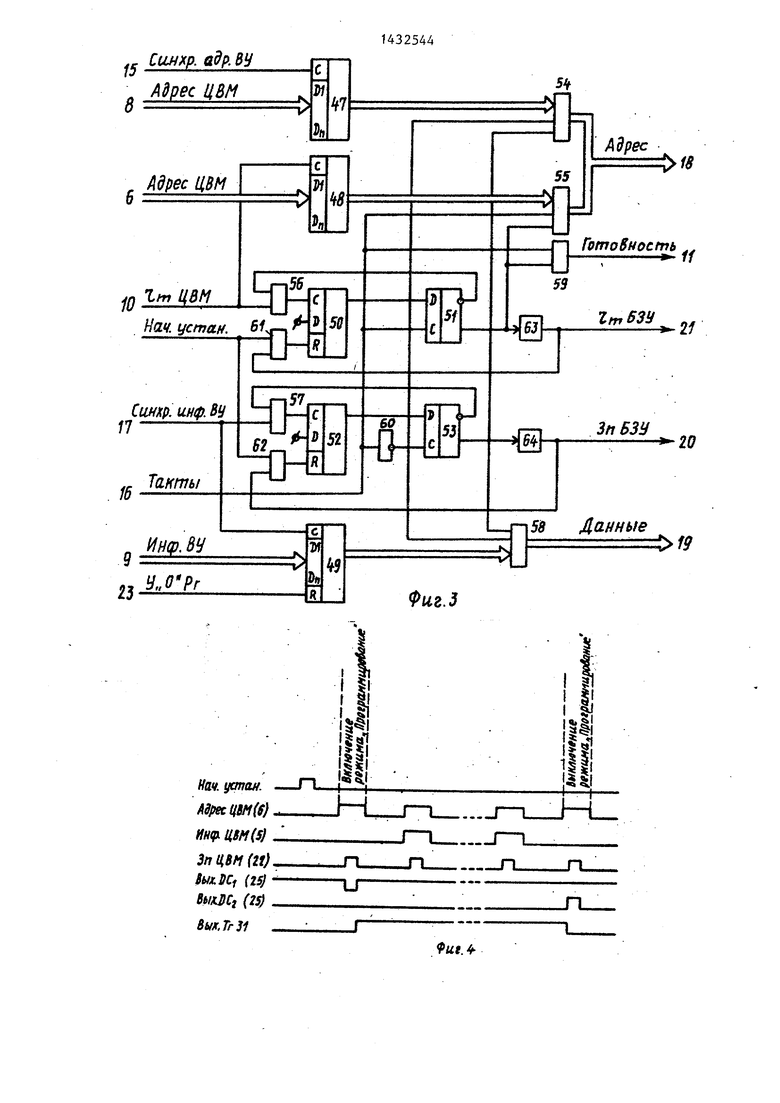

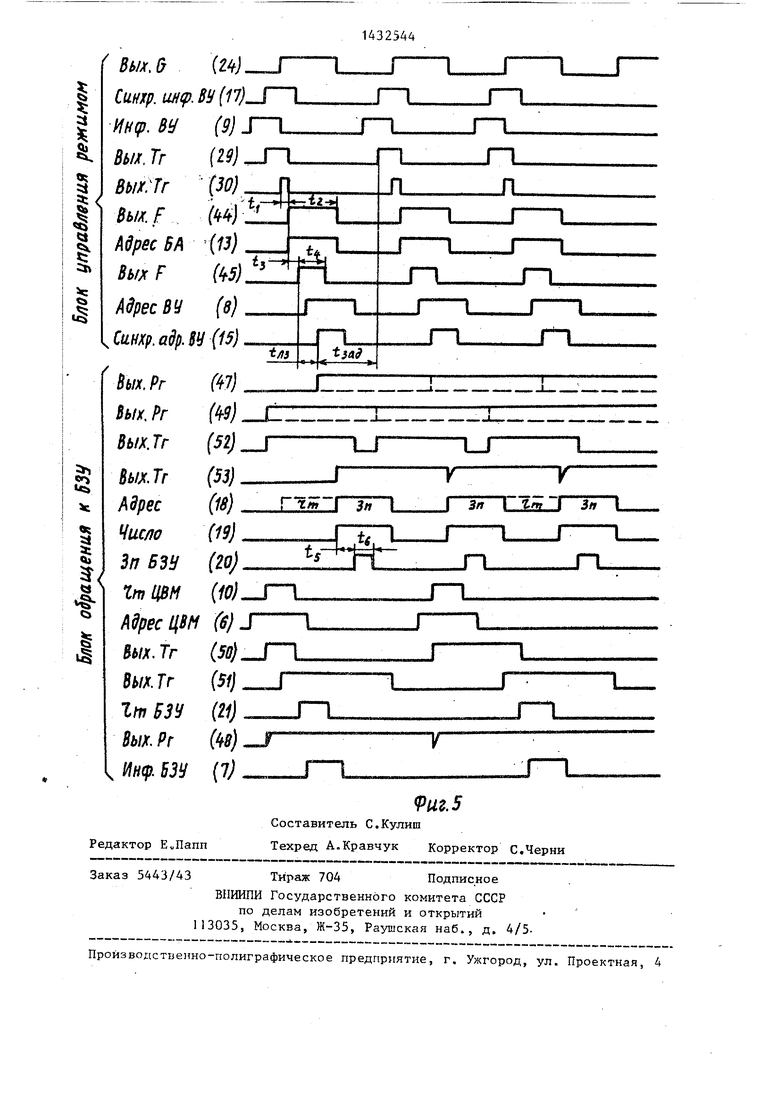

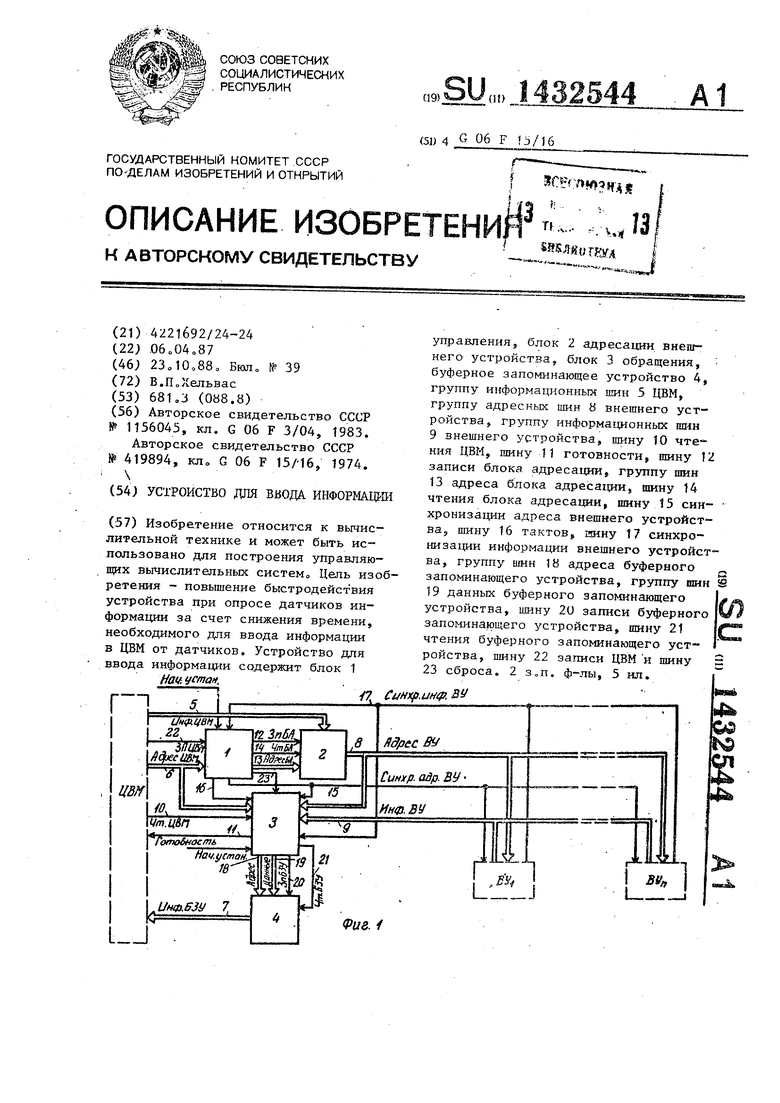

На фиг.1 показана схема устройства для ввода информации; на фиг,2 - схема блока управления; на фиГоЗ - схема блока обращения; на фиг.4 - ;временная диаграмма программирования I блока адресации внешнего устройства I(ВУ); на фиг.5 - временная диаграм- |ма работы устройства

I Устройство для ввода информации I (фиг. 1) содержит блок 1 управление, блок 2 адресации ВУ, блок 3 обращеI

|ния, буферное запоминающее устройст- |во 4, группу информационньпс шин 5 |ЦВМ, группу адресных шин 6 ЦВМ, груп 1пу информационных шин 7 буферного запоминающего устройства, группу адресных шин 8 ВУ,группу информацион шин 9 ВУ, шину 10 чтения ЦВМ, ;шину It готовности, шину 12 записи блоков адресации, группу шин 13 ад- реса блока адресации, шину 14 чте- ;ния блока адресации, шину 15 синхронизации адреса ВУ, шину 16 тактов., ;шину 17 синхронизации информации ВУ, группу шин 18 адреса буферного запоминающего устройства, группу ;шин 19 данного буферного запоминаю- 1щего устройства, шину 20 записи буфе jHoro запоминающего устройства,шину 2t .|чтения буферного запоминающего устрой ства,шину 22 записи ЦВМ,шину 23 сброса : Первая группа входов блока 3 обращения является группой информа- ционных входов устройства,, а первая группа выходов соединена с первой группой входов буферного запоминаю щего устройства 4, группа выходов которого является группой информа- ционных выходов устройствао Вторая группа входов блока 3 обращения подключена, к группе выходов блока 2 адресации ВУ и является грзтпо й ад- ресньгх выходов устройства, первая группа входов блока 2 адресаций ВУ является группой информационных вхо ДОН устройства. Вторая группа входо блока 2 адресации ВУ соединена с группой выходов блока 1 управления, первый и второй выходы которого подключены к двум входам блока 2 адресации ВУ, а третий и четвертьй выходы - с первым и вторым входами

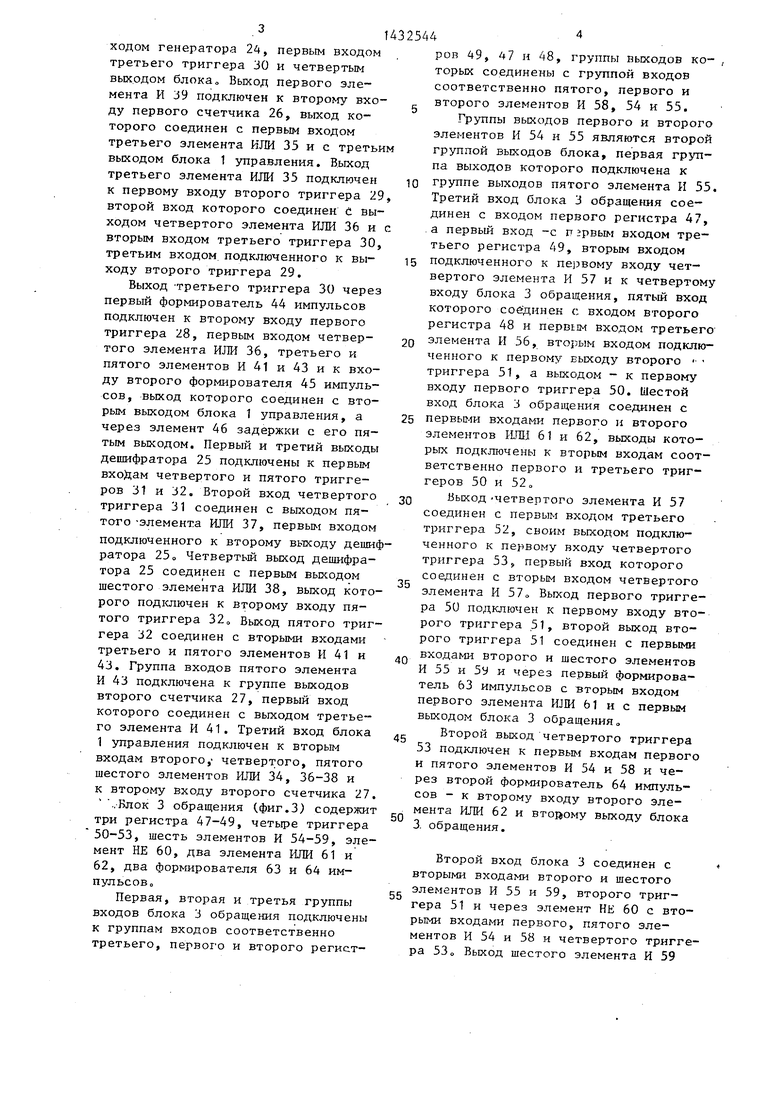

лока 3 обращения. Пятый вход блока 1 управления с третьим входом блока 3 обращения и с выходом синхронизаии адреса устройства. Группа входов блока 1 зшравления подключена к третьей группе входов блока 3 обращения и группе адресных входов устойства. Первый вход блока 1 управения является входом записи устройства, второй вход блока 1 управения соединен с четвертым входом блока 3 обращения и является входом синхронизации информации устройства. ятый вход блока 3 обращения является входом чтения устройства. Первый и второй выходы блока 3 обращения подключены к первому и второму входам буферного запоминающего устройства 4, вторая группа входов которого соединена с группой выходов блока 3 обращения, третий выход которого является выходом готовности устройства. Третий вход блока 1 управления ишестой вход блока 3 обращения являются входа- ми начальной установки устройства. Блок 1 управления (фиг.2) содержит генератор 24, дешифратор 25, два счетчика 26 и 27, пять триггеров 28-32,шесть элементов ШШ 33-38,пять элементов И39-43,два формирователя 44 и 45 импульсов,элемент 46 задержки. Группа входов блока 1 управления

соединена с группой входов дешифра-i тора 25 и группой входов четвертого элемента И 42, группа выходов которого подключена к группе вьпсодов пятого элемента И 43 и является группой выходов блока 1 управления. Первый вход блока 1 управления соединен с первым входом дешифратора 25 и второго элемента И 40, второй вход которого соединен с входом четвертого элемента И 42 и с выходом четвертого триггера 31, Выход второго элемента И 40 является niep- вым выходом блока управления. Вто-, рой вход блока 1 управления подключен к первому вхбду первого элеменг- та ШШ 33, второй вход которого соединен с пятым выходом деиифратора 25, а выход подключен к первым входам второго и третьего элементов ИЛИ 34 и 35, выход второго элемента ШШ 34 соединен с первыми входами первого триггер 28 и первого счетчика 26. Вькод первого триггера 28 подключен

к первому входу первого -элемеита И, второй вход которого соединен с вы- i

ходом генератора 24, первым входом третьего триггера 30 и четвертым выходом блока Выход первого элемента И 39 подключен к второму вхоу первого счетчика 26, выход которого соединен с первым входом третьего элемента ИЛИ 35 и с третьим выходом блока 1 управления. Выход третьего элемента ИЛИ 35 подключен к первому входу второго триггера 29, второй вход которого соединен t выходом четвертого элемента ИЛИ 36 и с вторым входом третьего триггера 30, третьим входом подключенного к выходу второго триггера 29.

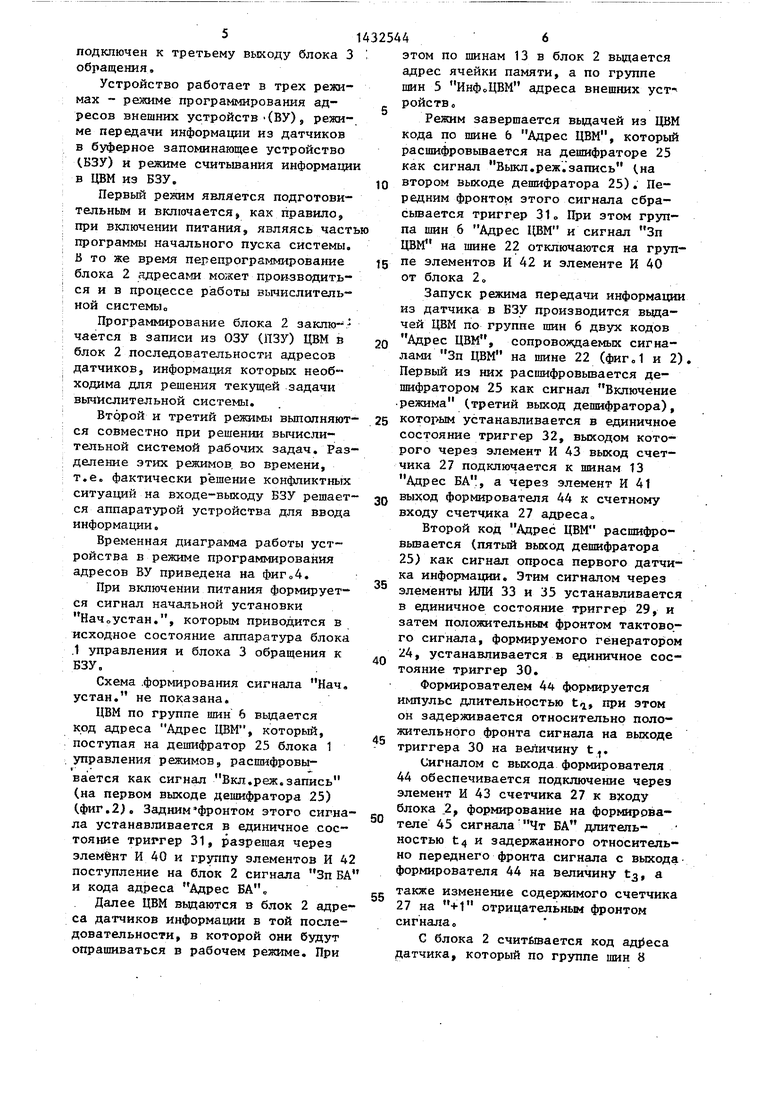

Выход третьего триггера 30 через первый формирователь 44 импульсов подключен к второму входу первого триггера Z8, первым входом четвертого элемента ИЛИ 36, третьего и пятого элементов И 41 и 43 и к входу второго формирователя 45 импульсов, выход которого соединен с вторым выходом блока 1 управления, а через элемент 46 задержки с его пя- тьм выходом. Первый и третий выходы дешифратора 25 подключены к первым вхо)5;ам четвертого и пятого триггеров 31 и 32. Второй вход четвертого триггера 31 соединен с вькодом пятого -элемента ИЛИ 37, первым входом подключенного к второму выходу дешифратора 25„ Четвертый выход дешифратора 25 соединен с первым выходом шестого элемента ИЛИ 38, выход которого подключен к второму входу пятого триггера 32 Выход пятого триггера 32 соединен с вторыми входами третьего и пятого элементов И 41 и 43. Группа входов пятого элемента И 43 подключена к группе выходов второго счетчика 27, первый вход которого соединен с выходом третьего элемента И 41. Третий вход блока 1 управления подключен к вторым входам второго, четвертого, пятого шестого элементов ИЛИ 34, 36-38 и к второму входу второго счетчика 27. ..Блок 3 обращения (фиг.З) содержит три регистра 47-49, четыре триггера 50-53, шесть элементов И 54-59, элемент НЕ 60, два элемента ИЛИ 61 и 62, два формирователя 63 и 64 импульсов

Первая, вторая и третья группы входов блока 3 обращения подключены к группам входов соответственно третьего, первого и второго регист0

5

0

5

0

5

0

5

0

5

ров 49, 47 и 48, группы выходов ко- , торых соединены с группой входов соответственно пятого, первого и второго элементов И 58, 54 и 55.

Группы выходов первого и второго элементов И 54 и 55 являются второй группой выходов блока, первая группа выходов которого подключена к группе выходов пятого элемента И 55. Третий вход блока 3 обращершя соединен с входом первого регистра 47, а первый вход -с пэрвым входом третьего регистра 49, вторым входом подключенного к пе)звому входу четвертого элемента И 37 и к четвертому входу блока 3 обращения, пятый вход которого сочинен с входом второго регистра 48 и первьм входом третьего- элемента И 56, вторым входом подключенного к первому выходу второго триггера 51, а выходом - к первому входу первого триггера 50. Шестой вход блока 3 обращения соединен с первыми входами первого и второго элементов ИЛИ 61 и 62, выходы которых подключены к вторым входам соответственно первого и третьего триггеров 50 и 52о

Выход -четвертого элемента И 57 соединен с первым входом третьего триггера 52, своим выходом подключенного к пе}5Вому входу четвертого триггера 53, первый вход которого соединен с вторым входом четвертого элемента И 57 Вьпсод первого триггера 50 подключен к первому входу второго триггера 51, второй выход второго триггера 51 соединен с первыми входами второго и шестого элементов И 55 и 5У и через первый формирователь 63 импульсов с вторым входом первого элемента ИЛИ 61 и с первым выходом блока 3 обращения

Второй выход четвертого триггера 53 подключен к первым входам первого и пятого элементов И 54 и 58 и через второй формирователь 64 импульсов - к второму входу второго элемента ИЛИ 62 и второму выходу блока 3. обращения.

Второй вход блока 3 соединен с вторыми входами второго и шестого элементов И 55 и 59, второго триггера 51 и через элемент НЕ 60 с вторыми входами первого, пятого элементов И 54 и 58 и четвертого триггера 53 Выход шестого элемента И 59

подключен к третьему выходу блока 3 обращения.

Устройство работает в трех режимах - режиме программирования адресов внешних устройств (ВУ), режи-, ме передачи информации из датчиков в буферное запоминающее устройство ЧБЗУ) и режиме считьшания информации в ЦВМ из ВЗУ.

Первый режим является подготовительным и включается как правило, при включении питания, являясь часть программы начального пуска системы. В то же время перепрограммирование блока 2 адресами может производиться и в процессе р1аботы вычислительной системы

Программирование блока 2 заклю--. чается в записи из ОЗУ (ПЗУ) ЦВМ в блок 2 последовательности адресов датчиков, информация которых необходима для рещения текущей задачи вычислительной системы.

Второй и третий режимы выполняются совместно при решении вычислительной системой рабочих задач. Разделение этих режимов, во времени, т.е. фактически решение конфликтных ситуаций на входе-выходу БЗУ решается аппаратурой устройства для ввода информации.

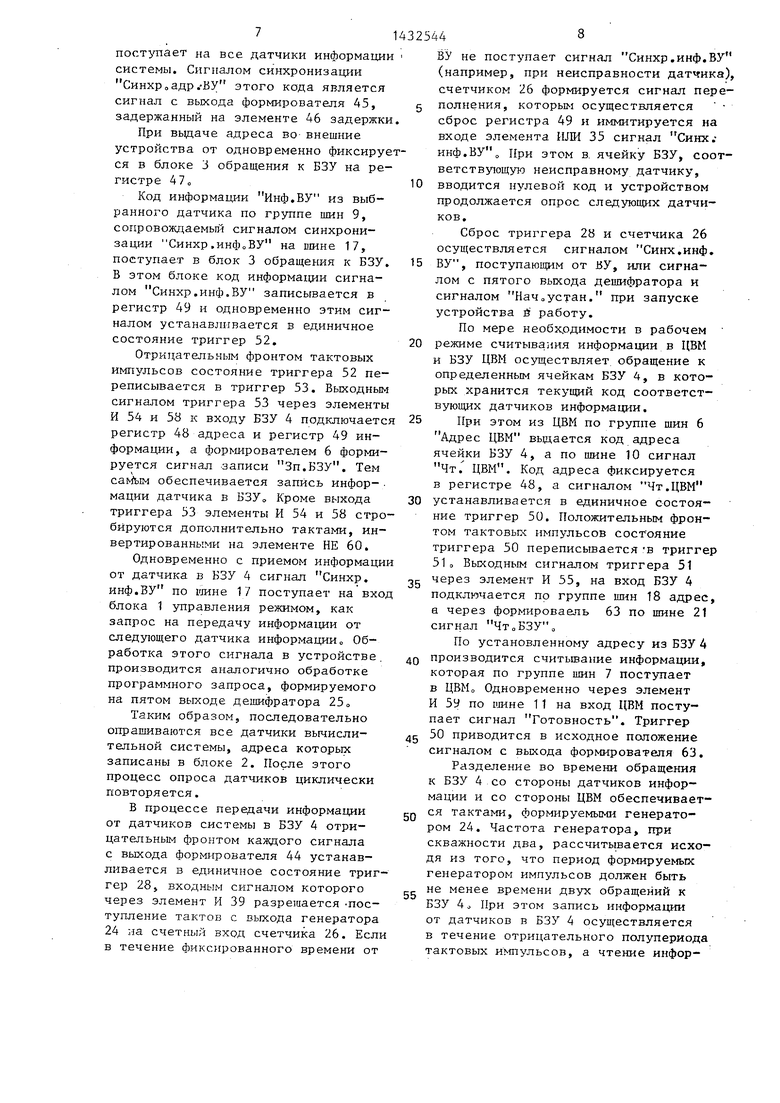

Временная диаграмма работы устройства в режиме программирования адресов ВУ приведена на фиГо4. При включении питания формируется сигнал начальной установки Начоустан., которым приводится в исходное состояние аппаратура блока .1 управления и блока 3 обращения к ВЗУ,

Схема .формирования сигнала Нач. устан. не показана.

ЦВМ по группе шин 6 вьщается код адреса Адрес ЦВМ, который, поступая на дешифратор 25 блока 1 управления режимов расшифровывается как сигнал Вкл.раж.запись (на первом выходе дешифратора 25) (фиг.2. Задним фронтом этого сигнала устанавливается в единичное состояние триггер 31, разрешая через элемент И 40 и группу элементов И 4 поступление на блок 2 сигнала Зп ВА и кода адреса Адрес

Далее ЦВМ выдаются в блок 2 адреса датчиков информации в той последовательности, в которой они будут опрашиваться в рабочем режиме. При

5

0

5

0

5

0

5

0

5

этом по шинам 13 в блок 2 вьщается адрес ячейки памяти, а по группе шин 5 ИнфоЦВМ адреса внешних уст-

рОЙСТВв

Режим завершается выдачей из ЦВМ кода по шине 6 Адрес ЦВМ, который расшифровьшается на дешифраторе 25 как сигнал Выкл.реж.запись (.на втором выходе дешифратора 25). Передним фронтов этого сигнала сбра- сьшается триггер 31 При этом группа шин 6 Адрес ЦВМ и сигнал Зп ЦВМ на шине 22 отключаются на группе элементов И 42 и элементе И 40 от блока 2с,

Запуск режима передачи информации из датчика в БЗУ производится вьща- чей ЦВМ по группе шин 6 двух кодов Адрес ЦВМ, сопровождаемых сигналами Зп ЦВМ на шине 22 (фиг,1 и 2). Первый из них расшифровывается дешифратором 25 как сигнал Включение режима (третий выход дешифратора), которым устанавливается в единичное состояние триггер 32, выходом которого через элемент И 43 выход счетчика 27 подключается к шинам 13 Адрес ВА, а через элемент И 41 выход формирователя 44 к счетному входу счетчика 27 адреса.

Второй код Адрес ЦВМ расшифро- вьюается (пятый выход дешифратора 25) как сигнал опроса первого датчика информации. Этим сигналом через элементы ИЛИ 33 и 35 устанавливается в единичное состояние триггер 29, и затем положительным фронтом тактового сигнала, формируемого генератором 24, устанавливается в единичное состояние триггер 30.

Формирователем 44 формируется импульс длительностью ti, при этом он задерживается относительно положительного фронта сигнала на выходе триггера 30 на величину t.,.

Сигналом с выхода формирователя 44 обеспечивается подключение через элемент И 43 счетчика 27 к входу блока 2f формирование на формирователе 45 сигнала Чт ВА длительностью t4 и задержанного относительно переднего фронта сигнала с выхода формирователя 44 на величину t, а

также изменение содержимого счетчика 27 на +1 отрицательным фронтом сигналао

С блока 2 считбгоается код ад|4еса датчика, который по группе шин Ь

7

поступает на все датчики информации системы. Сигналом синхронизации Синхр„адр. ВУ этого кода является сигнал с выхода формирователя 45, задержанный на элементе 46 задержки

При вьщаче адреса во внешние устройства от одновременно фиксируеся в блоке 3 обращения к БЗУ на регистре 47о

Код информации Инф.ВУ из выбранного датчика по группе шин 9, сопровождаемый сигналом синхронизации Синхр.инфоВУ на вшне 17, поступает в блок 3 обращения к БЗУ. В этом блоке код информа1щи сигналом Синхр,ИНФ.ВУ записывается в регистр 49 и одновременно этим сигналом устанавливается в единичное состояние триггер 52.

Отрицательным фронтом тактовых импульсов состояние триггера 52 переписывается в триггер 53. Выходным сигнгшом триггера 53 через элементы И 54 и 58 к входу БЗУ 4 подключаетс регистр 48 адреса и регистр 49 информации, а формирователем 6 формируется сигнал записи Зп.БЗУ. Тем обеспечивается запись инфор- мации датчика в БЗУ„ Кроме выхода триггера 53 элементы И 54 и 58 стро бИруются дополнительно тактами, инвертированными на элементе НЕ 60.

Одновременно с приемом информаци от датчика в БЗУ 4 сигнал Синхр. ИНФ.ВУ по 1 шне 17 поступает на вхо блока 1 управления режимом, как запрос на передачу информации от следующего датчика информации Обработка этого сигнала в устройстве. производится аналогично обработке программного запроса, формируемого на пятом выходе дешифратора 25о

Таким образом, последовательно опрашиваются все датчики вьгчисли- тельной системы, адреса которых записаны в блоке 2. После этого процесс опроса датчиков циклически повторяется.

В процессе передачи информации от датчиков системы в БЗУ 4 отрицательным фронтом каждого сигнала с выхода формирователя 44 устанавливается в единичное состояние триггер 28, входным сигналом которого через элемент И 39 разрешается пос- тупление тактов с выхода генератора 24 иа счетный вход счетчика 26. Если в течение фиксированного времени от

25448

ВУ не поступает сигнал Синхр.инф.ВУ (например, при неисправности датчика), счетчиком 26 формируется сигнал пере5 полнения, которым осуществляется сброс регистра 49 и иммитируется на входе элемента ШШ 35 сигнал Синх.- ИНФ. При этом в. ячейку БЗУ, соответствующую неисправному датчику,

0 вводится нулевой код и устройством продолжается опрос следующих датчиков.

Сброс триггера 28 и счетчика 26 осуществляется сигналом Синх.инф.

15 ВУ, поступающим от БУ, или сигналом с пятого выхода дешифратора и сигналом НаЧоустан. при запуске устройства S работу.

По мере необходимости в рабочем

0 режиме считыва;шя информации в ЦВМ и ВЗУ ЦВМ осуществляет обращение к определенным ячейкам БЗУ 4, в которых хранится текущий код соответствующих датчиков информации.

25 При этом из ЦВМ по группе шин 6 Адрес ЦВМ вьиается код адреса ячейки БЗУ 4, а по шине 10 сигнал Чт. ЦВМ. Код адреса фиксируется в регистре 48, а сигналом Чт.ЦВМ

30 устанавливается в единичное состояние триггер 50. Положительным фронтом тактовых импульсов состояние триггера 50 переписывается -в триггер 51 о Выходным сигналом триггера 51

од через элемент И 55, на вход БЗУ 4 подключается по группе шин 18 адрес, а через формироваель 63 по шине 21 сигнал ЧтоБЗУ о

По установленному адресу из БЗУ 4

0 производится считьшание информации, которая по группе шин 7 поступает в ЦВМо Одновременно через элемент И 5У по г жне 11 на вход ЦВМ поступает сигнал Готовность. Триггер

4g 50 приводится в исходное положение сигналом с выхода формирователя 63. Разделение во времени обращения к БЗУ 4 со стороны датчиков информации и со стороны ЦВМ обеспечиваетQ ся тактами, формируемыми генератором 24. Частота генератора, при скважности два, рассчитывается исходя из того, что период формируемых генератором импульсов должен быть не менее времени двух обращений к БЗУ 4 При этом запись информации от датчиков в БЗУ 4 осуществляется в течение отрицательного полупериода тактовых и тульсов, а чтение инфор-

55

нации со стороны ЦВМ - в течение положительного полупериода тактовьк импульсов.

На приведена временная диа-

грамма совместного выполнения режи- ;мов передачи информа1щи из датчиков ;В БЗУ и записи в ЦВМ из БЗУ. : Устройство отличается от извест™ ных более высокой производительностью достигнутой за счет снижезшя време- ни, необходимого для ввода информа- ;ции датчиков в ЦВМо

Формула изобретения

i 1. Устройство для ввода информа- |ции,содержащее буферное запоминаю- ее устройство и блок обращения, рпервая группа входов которого явля- :ется первой группой информационных фходов устройства5 а первая группа выходов соединена с первой группой рходов буферного запоминающегоуст- |ройства, группа выходов которого |является группой, информационных вы- Ходов устройства, о т л и ч а rota е е с я тем, что, с цепью повыше- Шя. быстродействия устройства, в него введены блок управления и блок |адресации внешнего устройства, вто- рая группа входов блока обращения подключена к группе выходов блока Адресации внешнего устройства и яв- иется группой адресных выходов уст- )ойства, первая группа входов блока адресации внешнего устройства является второй группой информационных входов устройства, вторая группа Ьходов блока адресации внешнего устройства соединена с группой выходов блока управления, первый и второй йыходы которого подключены к двум входам блока адресации внешнего устройства, а третий и четвертьй выходы - к первому и второму входам блока обращения, пятый вькод блока уп Правления соединен с третьим входом блока обращения и является выходом синхронизации адреса устройства, группа входов блока управления подключена к третьей группе входов блока обращения и является адресными входами устройства, первый вход блока управления является входом запис устройства, второй вход блока управ ления соединен с четвертым входом (5лока обращения и является входом синхронизации информации устройства

..

D

ю510

15

и-, .

20

25

43254410

пятый вход блока обращения является входом чтения устройства, первый и второй вьжоды блока обращения подключены к первому и второму входам буферного запоминающего устройства, вторая группа входов которого соединена с группой выходов блока обращения, третий выход которого является выходом готовности устройства, третий вход блока управления и шестой вход блока обращения являются входом начальной установки устройства.

2 о Устройство по п.1, отличающееся тем, что блок управления содержит генератор, дешифратор, два счетчика, пять триггеров, шесть элементов ИЛИ, пять элементов

И, два формирователя импульсов, элемент задержки, причем группа входов блока управления соединена с группой входов дешифратора и группой входов четвертого элемента И, группа выходов которого подключена к группе выходов пятого элемента И и является группой выходов блока, первый вход блока соединен с первыми входами дешифратора и второго элемента И, второй вход которого соединен с входом четвертого элемента И и с йыхо- дом четвертого триггера, выход второго элемента И является первым выходом блока, второй вход блока подключен к первому входу первого элемента ИЛИ, второй вход которого соединен с выходом дешифратора, а выход подключен к первым входам второго и третьего элементов ИЛИ, выход второго элемента ИЛИ соединен с первыми входами первого триггера и первого счетчика, выход первого триггера -подключён к первому входу первого элемента И, второй вход которого соединен с выходом генератора, первым входом третьего триггера и четвертым выходом блока, выход первого элемента И подключен к второму входу первого счетчика, выход которого соединен с первым входом третьего элемента ИЛИ и с третьим вькодом-, блока, выход третьего элемента ИЛИ подключен к первому входу второго триггера, второй вход которого соединен с выходом четвертого элемента ИЛИ и с втбрым входом третьего триггера, третьим входом подключенного к выходу второго триггера, выход третьего триггера через первый формирователь импульса подключен к вто30

35

40

45

50

55

рому входу первого триггера, первым входом четвертого элемента ШШ, третьего и пятого элементов И и к входу второго формирователя импульсов, выход которого соединен с вторым выходом блока, а через элемент задержки - с его пятым выходом, первый и третий выходы дешифратора подключены к первым входам четвертого и пятого триггеров, второй вход четвертого триггера соединен с выходом пятого элемента ИЛИ, первым входом подключенного к второму выходу дешифратора, четвертый выход дешифратора соединен с первым входом шестого элемента ИЛИ, выход которого подключен к второму входу пятого триг- i гера, выход пятого триггера соединен ;с вторыми входами третьего и -пятого элемента И, группа входов пятого ; элемента И подключена к группе выхо- Iдов второго счетчика, первый вход которого соединен с выходом третьего элемента И, третий вход блока подключен к вторым входам второго, четвертого, пятого, шестого элеме нтов ИЛИ и к второму входу второго счетчика.

0

ключена к группе выходов пятого элемента И, третий вход блока соединен с входом первого регистра, а первый вход - с первым входом третьего регистра, вторым входом подключенного к первому входу четвертого элемента И и к четвертому входу блока, пятый вход которого соединен с входом второго регистра и первым входом третьего элемента И, вторым входом подключенного к первому выходу второго триггера, а выходом - к первому входу первого триггера, шестой g вход блока соединен с первыми входами первого и второго элементов ИЛИ, выходы которых подключены к вторым BxoJiaM соответственно перво го и,третьего триггеров, выход чет-. вертого элемента И соединен с первым входом третьего триггера, своим выходом подключенного к первому вхо ду четвертого триггера, первый выход которого соединен с вторым входом четвертого элемента И, выход первого триггера подключен к первому входу второго триггера, второй выход второго триггера соединен с первыми входами второго и шестого элементов И и через первый формирователь импульсов - с вторым входом первого элемента ИЛИ и с первым выходом блока, второй выход четвертого триггера подключен к первым входам первого и пятого элементов И и через второй формирователь-импульсов - с вторым входом второго элемента ИЛИ и вторым выходом блока, второй вход блока соединен с вторыми входами второго и шестого элементов И, второго триггера и через элемент НЕ - с вторыми входами первого, пятого элементов И и четвертого триггера, выход шестого элемента И подключен к третьему выходу блока

5

0

5

0

| Устройство для синхронизации системы обмена информацией | 1983 |

|

SU1156045A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1971 |

|

SU419894A1 |

Авторы

Даты

1988-10-23—Публикация

1987-04-06—Подача