Изобретение относится к вычислительной технике и может найти применение в вычислительных системах.

Известны устройства для обмена информацией, содержащие регистры, блок управления, счетчики слоев выдачи и приема, блок анализа режимов, блок управления 1.

Недостаток этих устройств состоит в их низком быстродействии.

Наиболее близким к изобретению по сущности технического решения является устройство для сопряжения, содержащее регистр информации, соединенный первыми входом и выходом, соответственно с информационными входом и выходом устройства, управляющим входом - с первым выходом блока синхронизации, а вторыми входом и выходом - соответственно с входом и выходом, коммутатора информации, группы входов и выходов которого соединены с информационными выходами и входами подканалов, управляющие входы и выходы которых подключены к выходам блока синхронизации и соответствующим входам и выходам устройства, блок приоритета, регистр готовности программы, блок управления обменом и блок контроля по модулю,- причем каждый подканал включает узел у11р,айления, регистр служебных сигналов, регистр обмена, узел обработки запросов, выходы и йходы которого соединены соответственно с входом и выходом узла управления и выходом и входом подканала, коммутатор, и узел готовности подканала, соединенный входами и выходами соответственно с входом и выходом подканала и выходом и входом узла управления 2.

Недостатком данного устройства являются большие аппаратурные затраты, Цель иаобретения - сокращение аппаратурных затрат.

Поставленная цель достигается тем, что в устройство, содержащее регистр информации, информационные вход и выход которого являются соответственно информационными входом и выходом устройства, а управляющий вход соединен с синхронизирующим входом устройства и входом блока синхронизации, и группу каналов обмена, каждый из

25 которьи включает блок обработки запросов, блок подготовки канала и блок управления, причем в каждом канале обмена группа входов блока обработки запросов соединена с группой выходов

30 блока синхронизации, первый вход

является соответствующим входом из группы входов запроса устройства, а первый, второй и третий выходы соединены соответственно с первым, вторым и третьим входами блока управления, четвертый вход которого является соответствующим входом из группы входов признака направления передачи устройства, первый выход соединен с соответствующим выходом группы выходов опроса устройства и входом из первой группы входов блока синхронизации, а пятый вход - с первым выходом блока подготовки канала, первый вход которого является входом из группы входов признака начала массива устройства, введены шифратор и элемент ИЛИ, а в каждый канал обмена - счетчик текущего адреса и счетчик слов, причем в каждом кана-ле обмена группа входов блока подготовки канала соединена.с группой входов блока управления и группой выходов блока синхронизации, второй и третий входы и первый и второй выходы - соответственно с первым и вторым выходами и третьим и вторым входами блока обработки запросов, четвертый вход которого соединен с входом признака отработки непрограммированной команды устройства,третий выход блока подготовки канала соединен с первыми входами счетчиков текущего адреса и слов, вторые входы которых подключены к второму выходу блока управления, третьим выходом соединенного с третьим входом счетчика текущего гщреса, группа выходов шифратора и группа выходов счетчиков текущего адреса каналов обмена являются группой выходов непрограммированной команды устройства, первая группа входов шифратора соединена с второй группой входов блока синхронизации и группой входов признака направления передачи устройства, вторая группа входов - с четвертыми выходами блоков подготовки каналов, а третья группа входов - с первыми выходами блоков обработки запросов и группой входов элемента ИЛИ, группы входов счетчиков . слова и счетчиков текущего адреса соединены с группой информационных входов устройства, выход элемента ИЛИ является выходом признака приостановки программы устройства, пятый вход блока обработки запросов i-ro канала обмена (,n) соединен с первым выходом блока обработки запросов i-1-го канала обмена, а также тем, что блок обработки запросов содержит четыре .триггера, три элемента И, элемент НЕ причем первый вход первого триггера соединен с первым входом блока и входом элемента НЕ, выход - с первым входом первого элемента И, второй вход - с выходом элемента НЕ, третий вход - с выходом второго триггера

и первым входом второго элемента И, а четвертый вход - с третьим входом блока и вторым входом первого элемента И, подключенного выходом к первому входу второго триггера, второй вход которого соединен с вторым входом блока, третий вход - с четвертым входом блока и первым входом третьего элемента И, а четвертый вход с выходом третьего триггера, первы м входом четвертого триггера и третьим выходом блока, второй вход второго элемента И подключен к пятому входу блока, а выход - к первому выходу блока и второму входу третьего элемента И, выходом соединенного с первым входом третьего триггера, выход четвертого триггера является вторым выходом блока, третьи входы первого и третьего элементов И, вторые входы третьего и четвертого триггеров и пятый вход второго триггера подключены к группе входов блока, и тем, что блок управления содержит четыре элемента И, элемент ИЛИ и элемент НЕ причем первые входы элементов И соединены с пятым входом блока, второй и третий входы первого элемента И подключены соответственно к первому и четвертому входам блока, второй и третий входы второго элемента И соединены соответственно с вторым вхдом блока и через элемент НЕ с четвертым входом блока, вторые входы третьего и четвертого элементов И подключены соответственно к третьему и второму входам блока, а выходы соответственно к второму и третьему выходам блока, выходы первого и второго элементов И соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого является первым выходом блока, четвертые входы первого и второго элементов И и третьи входы третьего и четвертого элементов соединены с группой входов блока, и тем, что блок подготовки канала содержит два триггера и три элемента И, причем первые входы триггеров соединены с первым входом блока, первый выход второго триггера подключен к первым входам элементов И, второй вход первого элемента И соединен с вторым входом блока, а выход - с вторым входом первого триггера и с четвертым выходом блока, выход первого триггера подключен к второму входу второго элемента И, выход которого соединен с вторым выходом блока, вторые входы второго триггера и третьего элемента И соединены с третьим входом блока, выход третьего элемента И соединен с третьим выходом блока, второй выход второго триггера подключен к первому выходу блока, третьи входы второго триггера и второго элемента И соединены с группой входов блока,, и тем, что блок синхронизации содержит

группу элементов И, генератор, триггер, счетчик, распределитель импульсов, два элемента И, элемент И-ИЛИ и элемент ИЛИ, причем первый выход генератора соединен с первым входом распределителя импульсов, с первыми входами элементов И группы, первым и вторалм входами элемента И-ИЛИ, второй выход генератора подключен к первым входам первого и второго элементов И, вторые входы которых соединены с соответствующими выходами триггера, первый вход которого соединен с выходом элемента ИЛИ, входы элемента ИЛИ подключены к выходам соответствующих элементов И группы, второй вход триг1;ера соединен с выходом элемента И-ИЛИ и первым входом счетчика, второй вход которого подключен к выходу первого элемента И, а выход - к третьему входу элемента И-ИЛИ, выход второго элемента И соединен с вторым входом распределителя импульсов,группа выходов которого является группой выходо блока, вторые и третьи входы элементов И группы и четвертый вход элемента И-ИЛИ подключены .соответственно к первой и второй группам входов блока и входу блока.

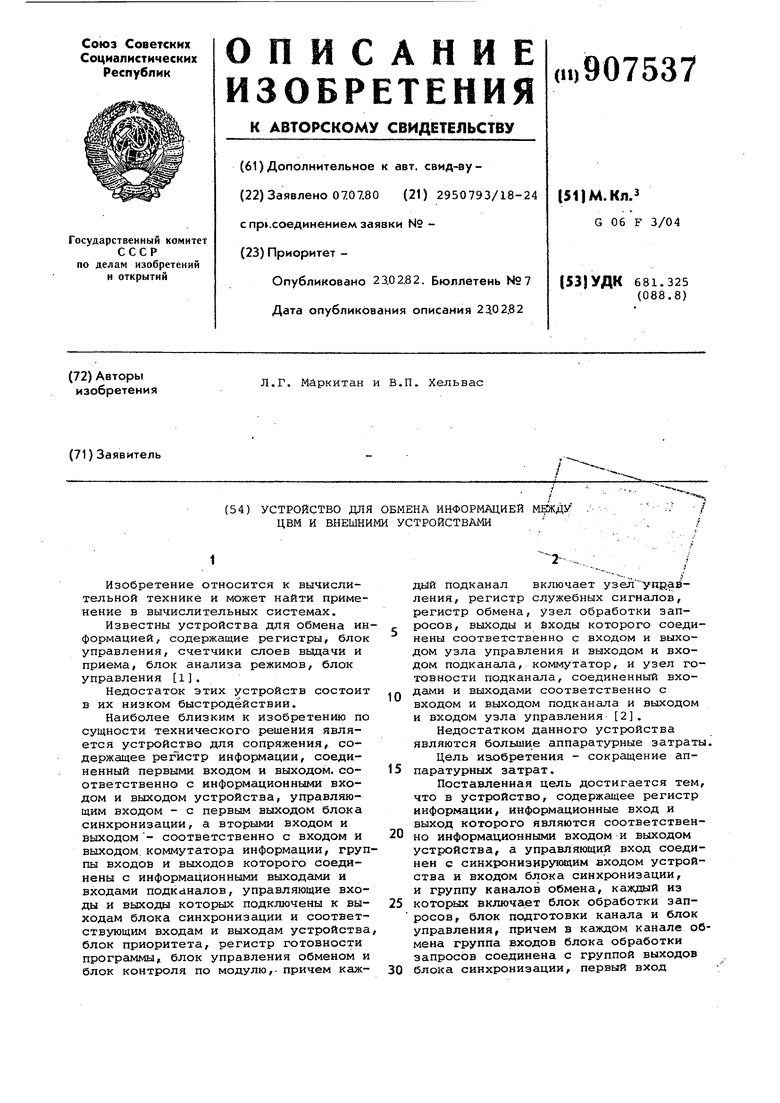

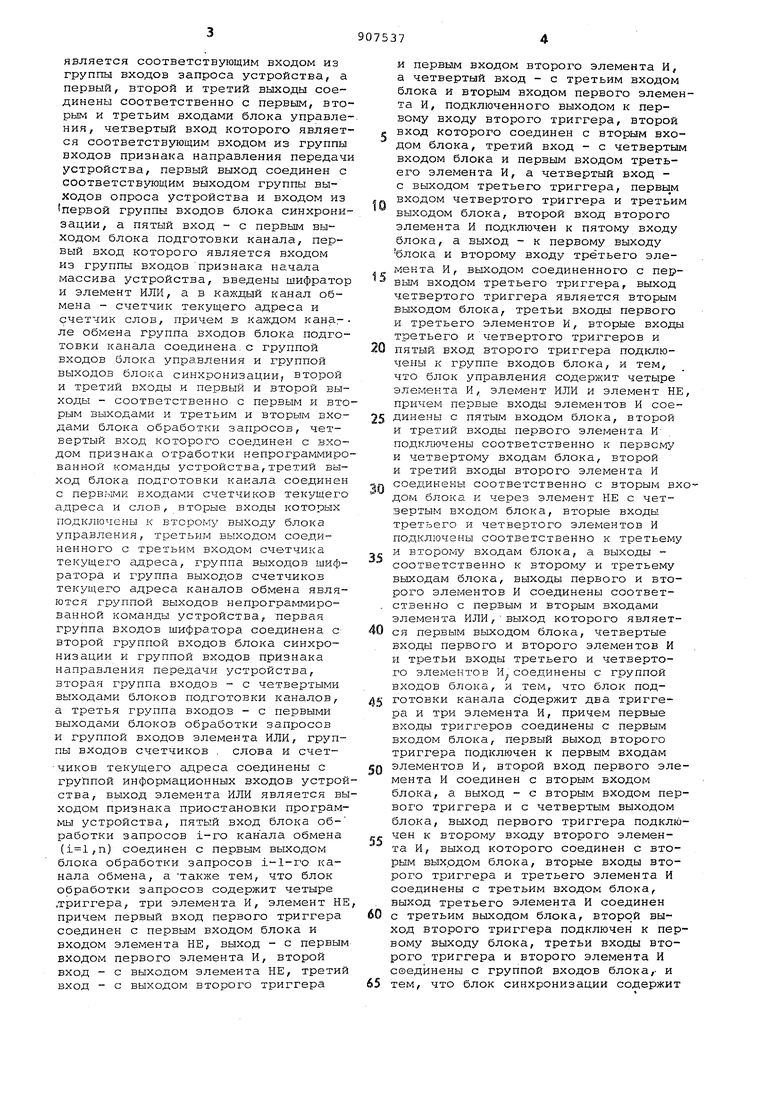

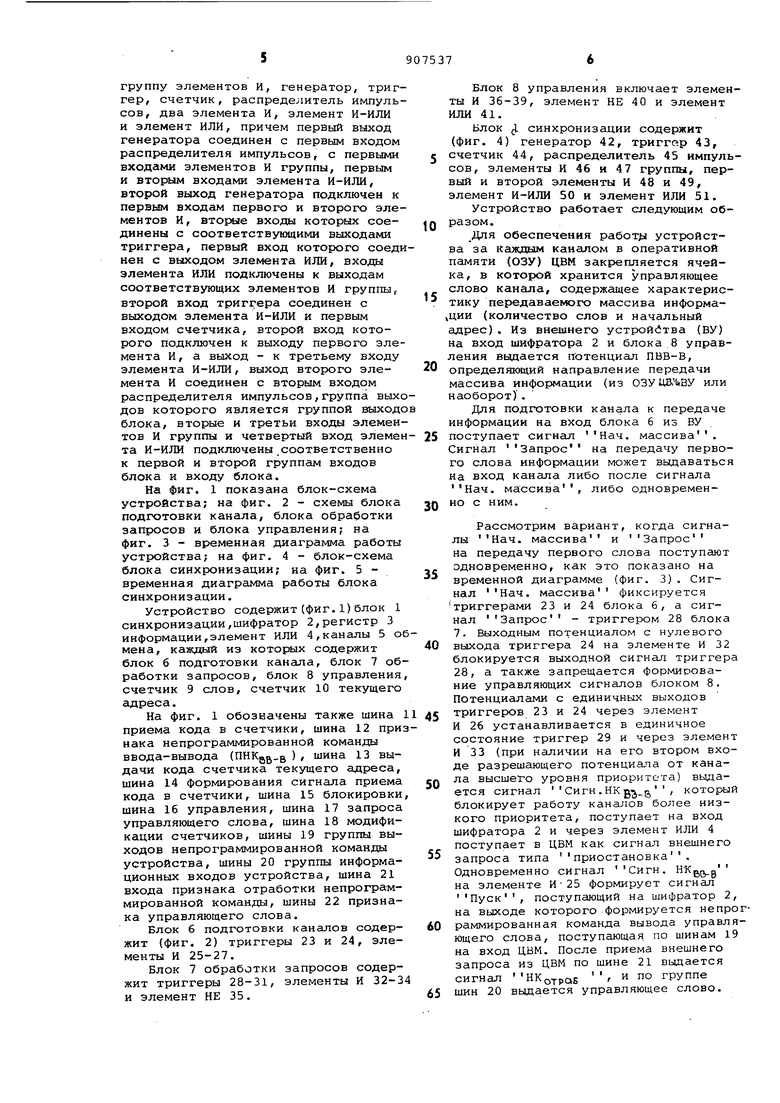

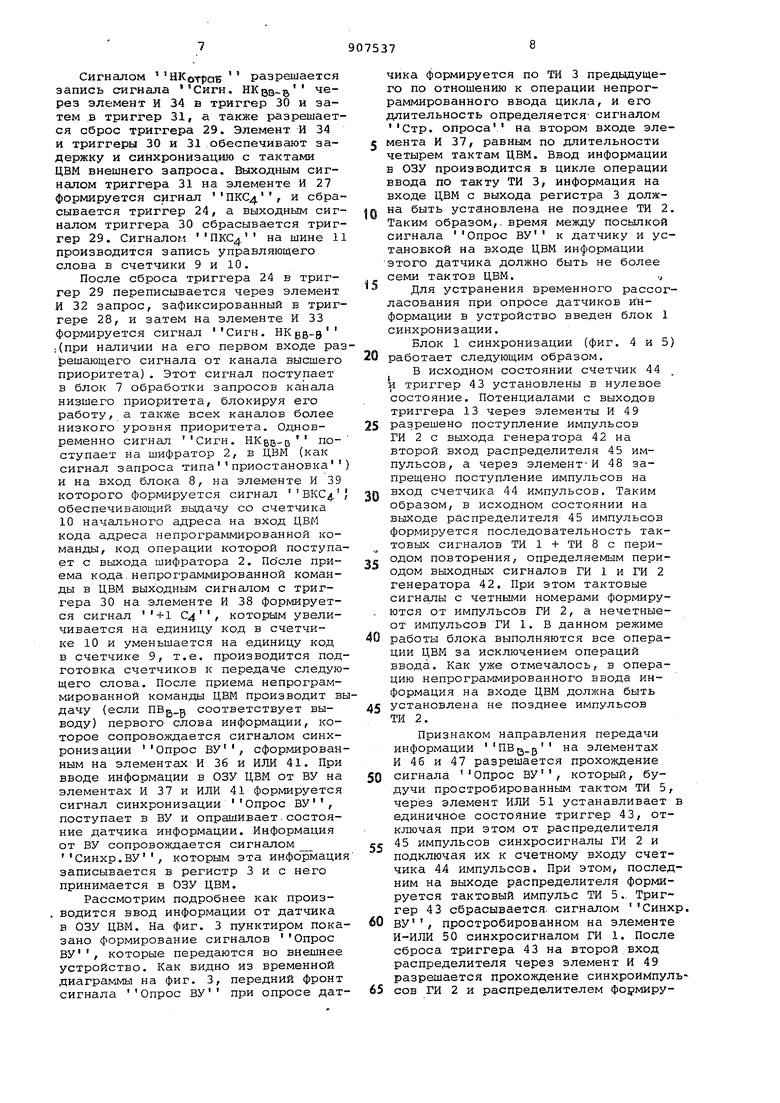

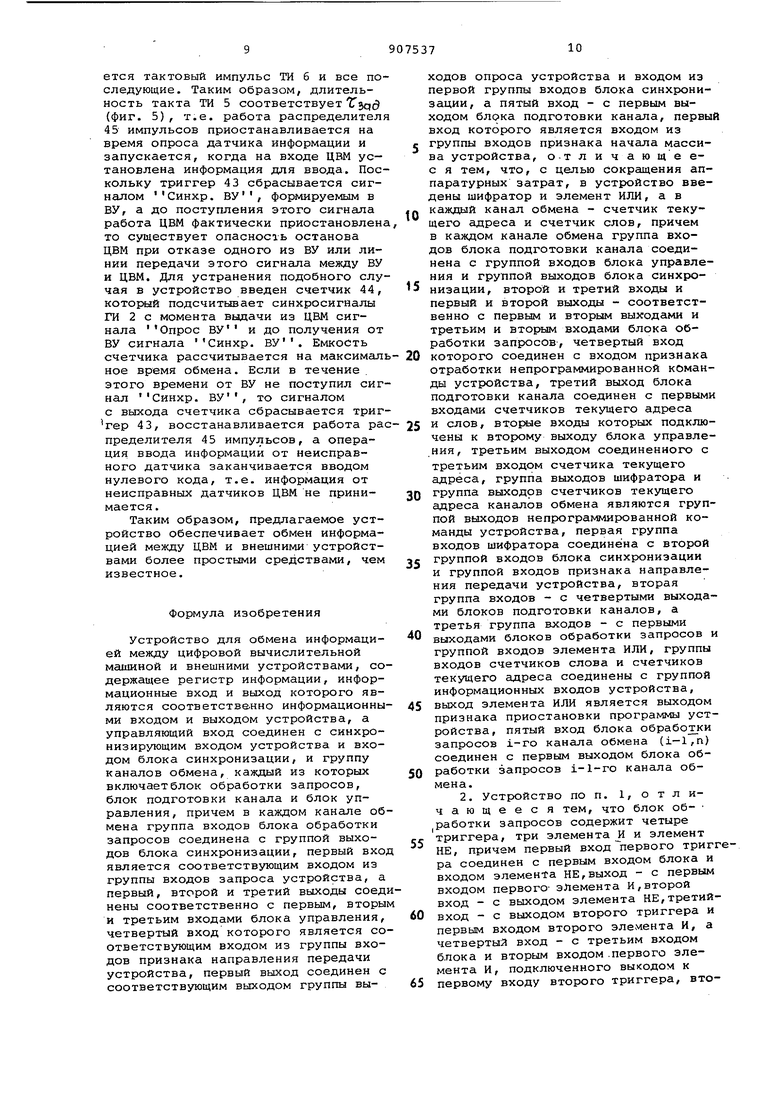

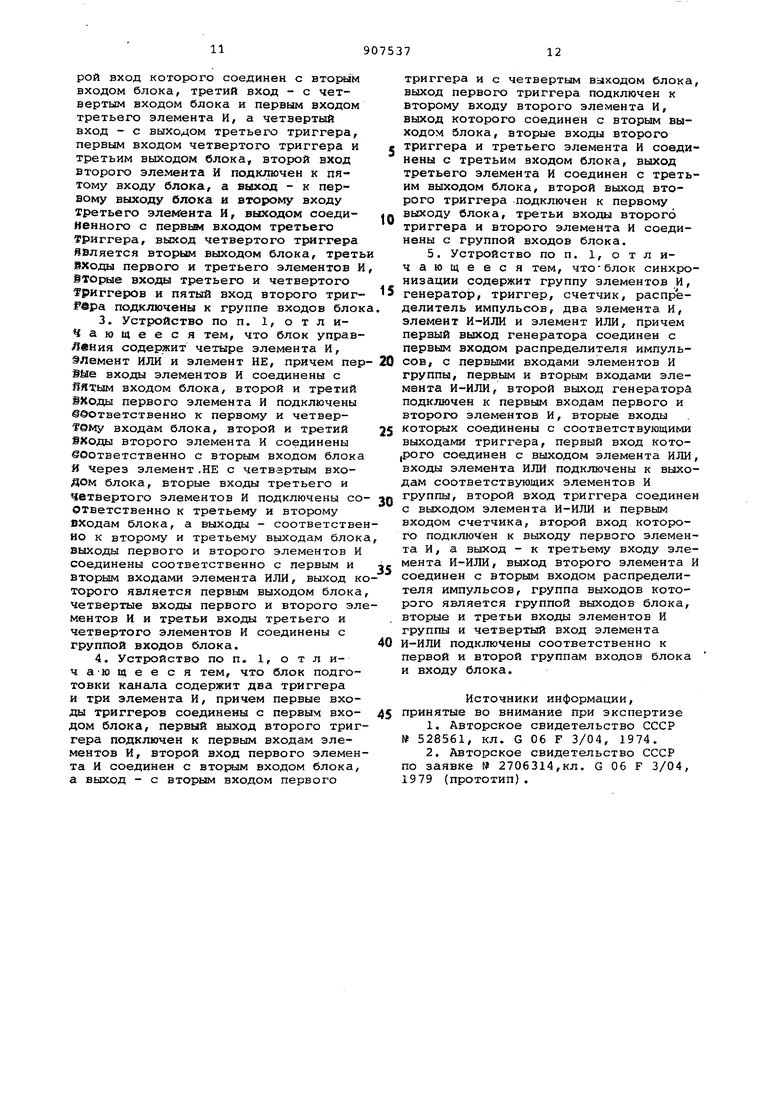

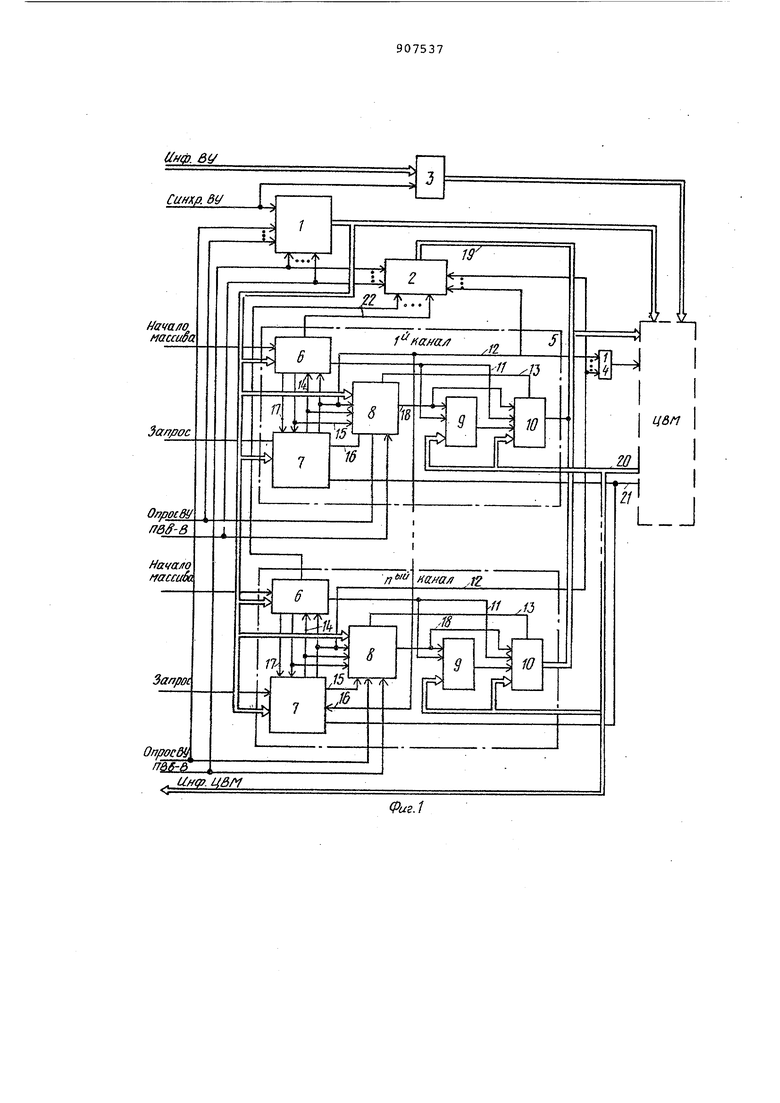

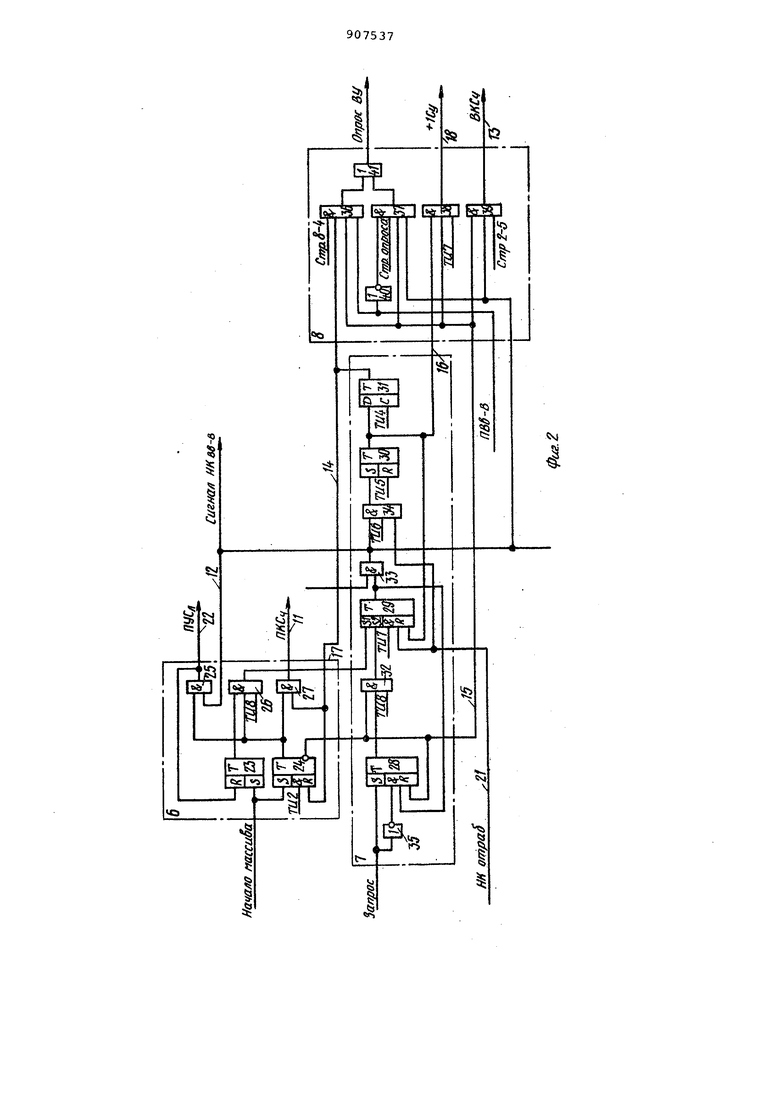

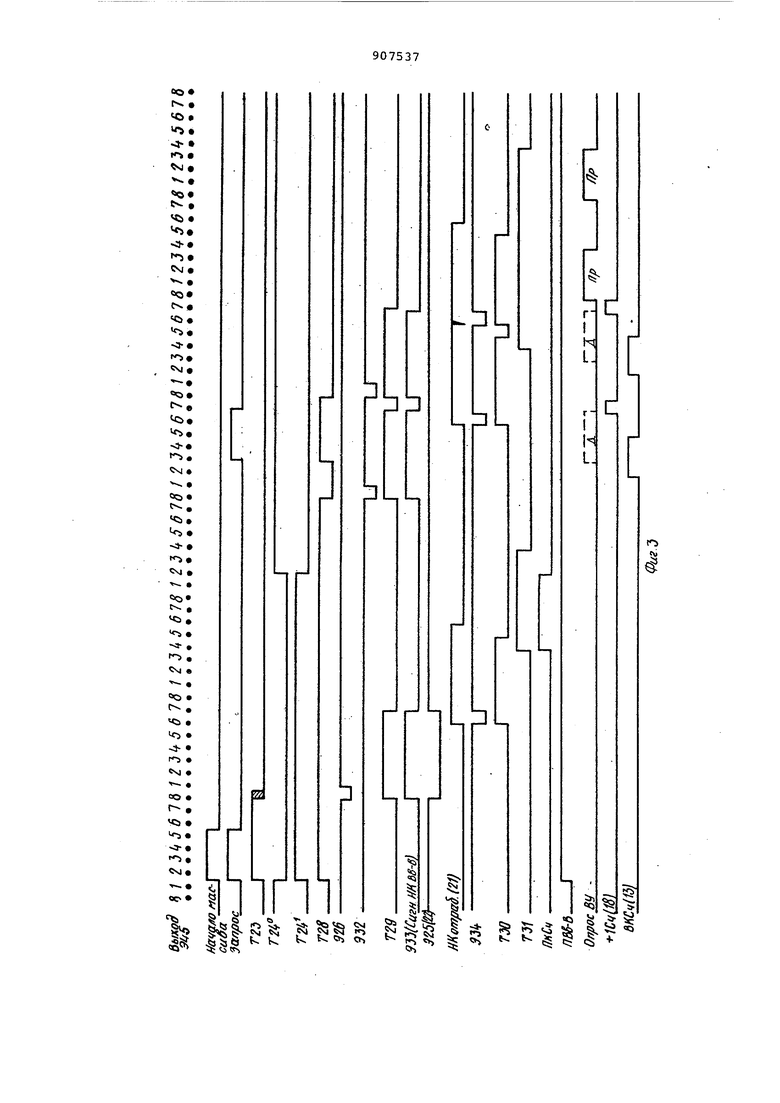

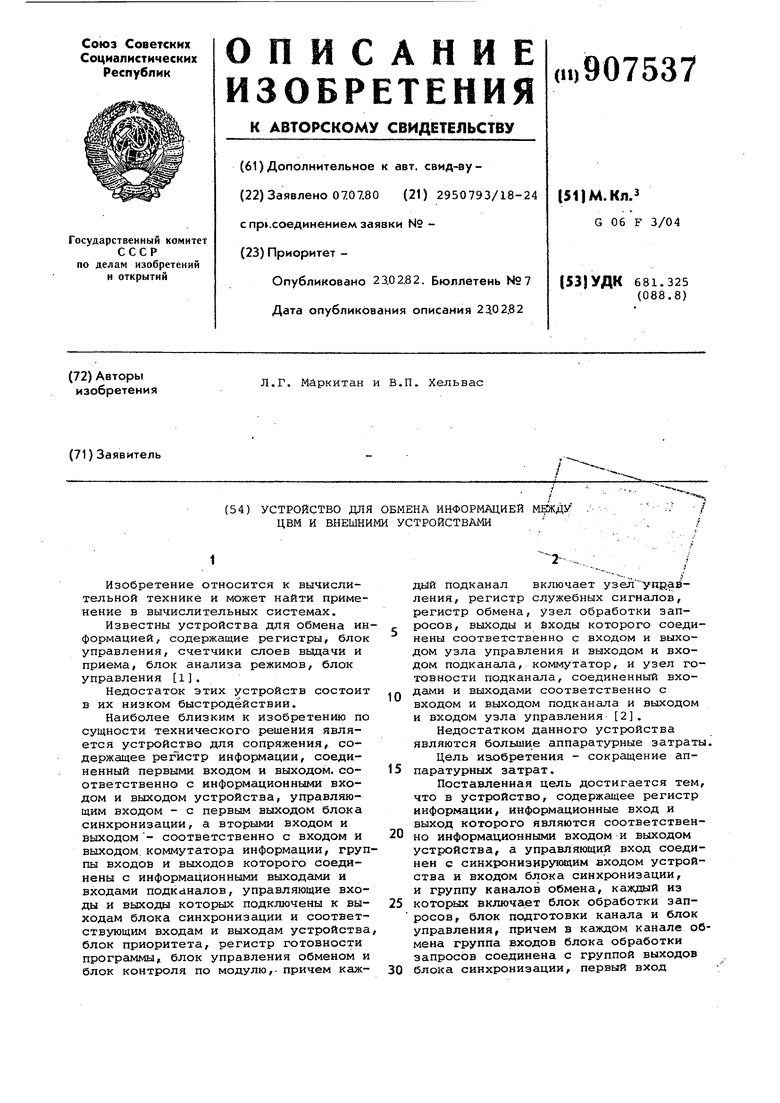

На фиг. 1 показана блок-схема устройства; на фиг. 2 - схемы блока подготовки канала, блока обработки запросов и блока управления; на фиг. 3 - временная диаграмма работы устройства; на фиг. 4 - блок-схема блока синхронизации; на фиг. 5 временная диаграмма работы блока синхронизации.

Устройство содержит (фиг.1)блок 1 синхронизации,шифратор 2,регистр 3 информации,элемент ИЛИ 4,каналы 5 обмена, каждый иэ которых содержит блок 6 подготовки канала, блок 7 обработки запросов, блок 8 управления счетчик 9 слов, счетчик 10 текущего адреса.

На фиг. 1 обозначены также шина 1 приема кода в счетчики, шина 12 признака непрограммированной команды ввода-вывода (ПИКц.ц ), шина 13 выдачи кода счетчика текущего адреса, шина 14 формирования сигнала приема кода в счетчики, шина 15 блокировки шина 16 управления, шина 17 запроса управляющего слова, шина 18 модификации счетчиков, шины 19 группы выходов непрограммированной команды устройства, шины 20 группы информационных входов устройства, шина 21 входа признака отработки непрограммированной команды, шины 22 признака управляющего слова.

Блок 6 подготовки каналов содержит (фиг. 2) триггеры 23 и 24, элементы И 25-27.

Блок 7 обработки запросов содержит триггеры 28-31, элементы И 32-34 и элемент НЕ 35.

Блок 8 управления включает элементы И 36-39, элемент НЕ 40 и элемент ИЛИ 41.

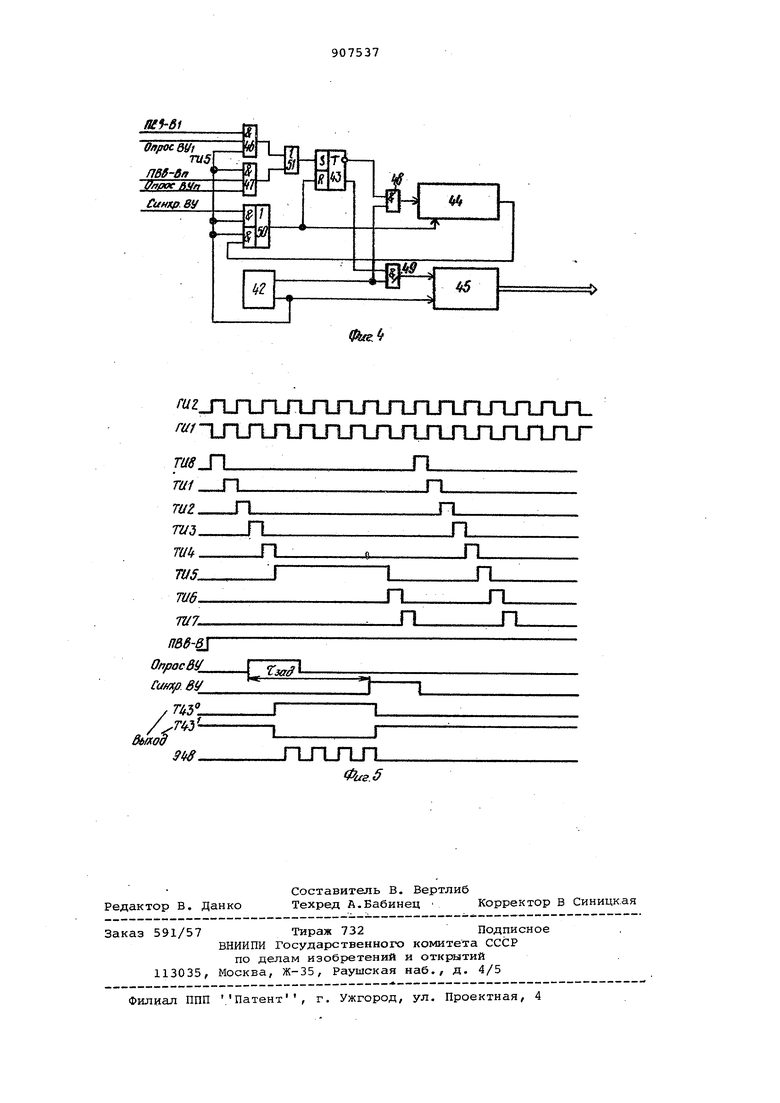

БЛОК (I синхронизации содержит (фиг. 4) генератор 42, триггер 43, 5 счетчик 44, распределитель 45 импульсов, элементы И 46 и 47 группы, первый и второй элементы И 48 и 49, элемент И-ИЛИ 50 и элемент ИЛИ 51.

Устройство работает следующим обQ разом.

Для обеспечения работяг устройства за каждым каналом в оперативной памяти (ОЗУ) ЦВМ закрепляется ячейка, в которой хранится управляющее слово канала, содержащее характеристику передаваемого массива информа ции (количество слов и начальный адрес). Из внешнего устройства (НУ) на вход шифратора 2 и блока 8 управления выдается потенциал ПВВ-В, определяющий направление передачи массива информации (из ОЗУ изЬВУ или наоборот).

Для подготовки канала к передаче информации на вход блока 6 из ВУ 5 поступает сигнал Нач. массива . Сигнал Запрос на передачу первого слова информации может выдаваться На вход канала либо после сигнала Нач. массива , либо одновременQ НО с ним.

Рассмотрим вариант, когда сигналы Нач. массива и Запрос на передачу первого слова поступают одновременно, как это показано на

5 временной диаграмме (фиг. 3). Сигнал Нач. массива фиксируется триггерами 23 и 24 блока б, а сигнал Запрос - триггером 28 блока 7. Выходным потенциалом с нулевого

0 выхода триггера 24 на элементе И 32 блокируется выходной сигнал триггера 28, а также запрещается формирование управляющих сигналов блоком 8. Потенциалами с единичных выходов

с триггеров 23 и 24 через элемент И 26 устанавливается в единичное состояние триггер 29 и через элемент И 33 (при наличии на его втором входе разрешающего потенциала от канала высшего уровня приоритета) выда0

ется сигнал Сигн .НК ) , который блокирует работу каналов более низкого приоритета, поступает на вход шифратора 2 и через элемент ИЛИ 4 поступает в ЦВМ как сигнал внешнего

5 запроса типа приостановка.

Одновременно сигнал Сигн. HKp jyg на элементе И25 формирует сигнал Пуск, поступающий на шифратор 2, на выходе которого формируется непрог0 раммированная команда вывода управляющего слова, поступающая по шинам 19 на вход ЦВМ. После приема внешнего запроса из ЦВМ по шине 21 выдается сигнал НКотраЕ ° группе

5 шин 20 выдается управляющее слово.

Сигналом НКотраВ разрешается запись сигнала Сигн, HKus-s через элемент И 34 в триггер 30 и затем в триггер 31, а также разрешается сброс триггера 29. Элемент И 34 и триггеры 30 и 31 обеспечивают задержку и синхронизацию с тактами ЦВМ внешнего запроса. Выходным сигналом триггера 31 на элементе И 27 формируется сигнал ПКСд/ и сбрасывается триггер 24, а выходным сигналом триггера 30 сбрасывается триггер 29. Сигналом ПКС4 на шине 11 производится запись управляющего слова в счетчики 9 и 10.

После сброса триггера 24 в триггер 29 переписывается через элемент И 32 запрос, зафиксированный в триггере 28, и затем на элементе И 33 формируется сигнал Сигн. :(при наличии на его первом входе разрешающего сигнала от канала высшего приоритета). Этот сигнал поступает в блок 7 обработки запросов канала низшего приоритета, блокируя его работу, а также всех каналов более низкого уровня приоритета. Одновременно сигнал Сигн. НКев-в поступает на шифратор 2, в ЦВМ (как сигнал запроса типаприостановка и на вход блока 8, на элементе И 39 которого формируется сигнал BKC/i. обеспечивающий выдачу со счетчика 10 начального адреса на вход ЦВМ кода адреса непрограммированной команды, код операции которой поступает с выхода шифратора 2. После приема кода.непрограммированной команды в ЦВМ выходным сигналом с триггера 30 на элементе И 38 формируется сигнал +1 , которым увеличивается на единицу код в счетчике 10 и уменьшается на единицу код в счетчике 9, т.е. производится подготовка счетчиков к передаче следующего слова. После приема непрограммированной команды ЦВМ производит выдачу (если соответствует выводу) первого слова информации, которое сопровождается сигналом синхронизации Опрос ВУ, сформированным на элементах И 36 и ИЛИ 41. При вводе информации в ОЗУ ЦВМ от ВУ на элементах И 37 и ИЛИ 41 формируется сигнал синхронизации Опрос ВУ, поступает В ВУ и опрашивает.состояние датчика информации. Информация

от ВУ сопровождается сигналом

Синхр.ВУ , которым эта информация записывается в регистр 3 и с него принимается в ОЗУ ЦВМ.

Рассмотрим подробнее как производится ввод информации от датчика в ОЗУ ЦВМ. На фиг. 3 пунктиром показано формирование сигналов Опрос ВУ, которые передаются во внешнее устройство. Как видно из временной диаграммы на фиг. 3, передний фронт сигнала Опрос ВУ при опросе датчика формируется по ТИ 3 предыдущего по отношению к операции непрограммированного ввода цикла, и его длительность определяется- сигналом Стр. опроса на втором входе элемента И 37, равным по длительности четырем тактам ЦВМ. Ввод информации в ОЗУ производится в цикле операции ввода по такту ТИ 3, информация на входе ЦВМ с выхода регистра 3 должна быть установлена не позднее ТИ 2 Таким образом,, время между посылкой сигнала Опрос ВУ к датчику и установкой на входе ЦВМ информации этого датчика должно быть не более семи тактов ЦВМ..

Для устранения временного рассогласования при опросе датчиков информации в устройство введен блок 1 синхронизации.

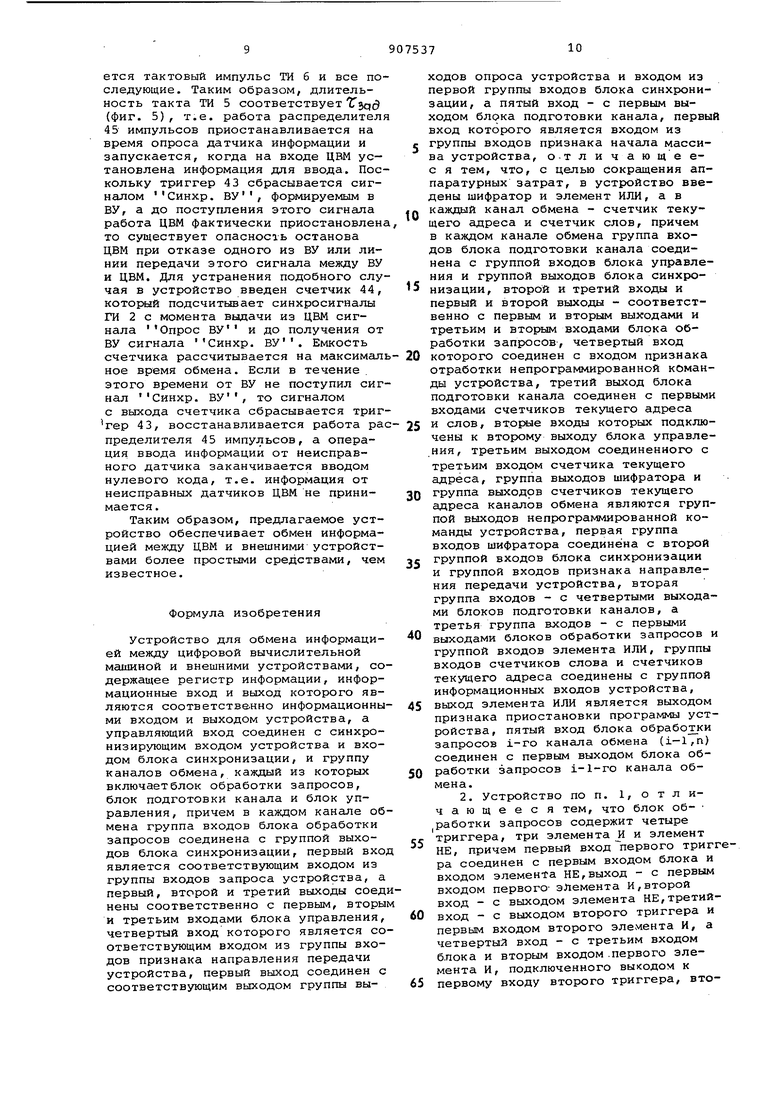

Блок 1 синхронизации (фиг. 4 и 5 работает следующим образом,

В исходном состоянии счетчик 44 и триггер 43 установлены в нулевое состояние. Потенциалами с выходов триггера 13 через элементы И 49 разрешено поступление импульсов ГИ 2 с выхода генератора 42 на второй вход распределителя 45 импульсов, а через элемент-И 48 запрещено поступление импульсов на вход счетчика 44 импульсов. Таким образом, в исходном состоянии на выходе распределителя 45 импульсов формируется последовательность тактовых сигналов ТИ 1 + ТИ 8 с периодом повторения, определяемым периодом выходных сигналов ГИ 1 и ГИ 2 генератора 42. При этом тактовые сигналы с четными номерами формируются от импульсов ГИ 2, а нечетныеот импульсов ГИ 1. В данном режиме работы блока выполняются все операции ЦВМ за исключением операций ввода.. Как уже отмечалось, в операцию непрограммированного ввода информация на входе ЦВМ должна быть установлена не позднее импульсов ТИ 2.

Признаком направления передачи информации nBjj.g на элементах И 46 и 47 разрешается прохождение сигнала Опрос ВУ, который, будучи простробированным тактом ТИ 5, через элемент ИЛИ 51 устанавливает в единичное состояние триггер 43, отключая при этом от распределителя 45 импульсов синхросигналы ГИ 2 и подключая их к счетному входу счетчика 44 импульсов. При этом, последним на выходе распределителя формируется тактовый импульс ТИ 5.. Триггер 43 сбрасывается, сигналом Синхр,

0 ВУ, простробированном на элементе И-ИЛИ 50 синхросигналом ГИ 1. После сброса триггера 43 на второй.вход распределителя через элемент И 49 разрешается прохождение синхроимпульсов ГИ 2 и распределителем фО5 мируется тактовый импульс ТИ 6 и все последующие. Таким образом, длительность такта ТИ 5 соответствует Тзо(5 (фиг. 5), т.е. работа распределителя 45 импульсов приостанавливается на время опроса датчика информации и запускается, когда на входе ЦВМ установлена информация для ввода. Поскольку триггер 43 сбрасывается сигналом Синхр. ВУ, формируемым в ВУ, а до поступления этого сигнала работа ЦВМ фактически приостановлена то существует опасность останова ЦВМ при отказе одного из ВУ или линии передачи этого сигнала между ВУ и ЦВМ. Для устранения подобного случая в устройство введен счетчик 44, который подсчитьтает синхросигналы ГИ 2 с момента выдачи из ЦВМ сигнала Опрос ВУ и до получения от ВУ сигнала Синхр. ВУ. Емкость счетчика рассчитывается на максималь ное время обмена. Если в течение этого времени от ВУ не поступил сигнал Синхр. ВУ, то сигналом с выхода счетчика сбрасывается триггер 43, восстанавливается работа рас пределителя 45 импульсов, а операция ввода информации от неисправного датчика заканчивается вводом нулевого кода, т.е. информация от неисправных датчиков ЦВМ не принимается.

Таким образом, предлагаемое устройство обеспечивает обмен информацией между ЦВМ и внешними устройствами более простыми средствами, чем известное.

Формула изобретения

Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами, содержащее регистр информации, информационные вход и выход которого являются соответственно информационными входом и выходом устройства, а управляющий вход соединен с синхронизирующим входом устройства и входом блока синхронизации, и группу каналов обмена, каждый из которых включает блок обработки запросов, блок подготовки канала и блок управления, причем в каждом канале обмена группа входов блока обработки запросов соединена с группой выходов блока синхронизации, первый вход является соответствующим входом из группы входов запроса устройства, а первый, второй и третий выходы соединены соответственно с первым, вторым и третьим входами блока управления, четвертый вход которого является соответствующим входом из группы входов признака направления передачи устрюйства, первый вьоход соединен с соответствующим выходом группы выходов опроса устройства и входом из первой группы входов блока синхронизации, а пятый вход - с первым выходом блока подготовки канала, первы вход которого является входом из группы входов признака начала массива устройства, о-тл и ч а юще ес я тем, что, с целью сокращения аппаратурных затрат, в устройство введены шифратор и элемент ИЛИ, а в каждый канал обмена - счетчик текущего адреса и счетчик слов, причем в каждом канале обмена группа входов блока подготовки канала соединена с группой входов блока управления и группой выходов блока синхронизации, второй и третий входы и первый и второй выходы - соответственно с первым и вторым выходами и третьим и вторым входами блока обработки запросов, четвертый вход которого соединен с входом признака отработки непрограммированной команды устройства, третий выход блока подготовки канала соединен с первыми входами счетчиков текущего адреса и слов, вторые входы которых подключены к второму выходу блока управления, третьим выходом соединенного с третьим входом счетчика текущего адреса, группа выходов шифратора и группа выходов счетчиков текущего адреса каналов обмена являются группой выходов непрограммированной команды устройства, первая группа входов шифратора соединена с второй группой входов блока синхронизации и группой входов признака направления передачи устройства, вторая группа входов - с четвертыми выходами блоков подготовки каналов, а третья группа входов - с первыми выходами блоков обработки запросов и группой входов элемента ИЛИ, группы входов счетчиков слова и счетчиков текущего адреса соединены с группой информационных входов устройства, выход элемента ИЛИ является выходом признака приостановки программы устройства, пятый вход блока обработки запросов i-ro канала обмена (i-1,п) соединен с первым выходом блока обработки запросов i-1-го канала обмена.

2. Устройство по п. 1, о т л ичающееся тем, что блок об- работки запросов содержит четыре триггера, три элемента J1 и элемент НЕ, причем первый вход первого тригра соединен с первым входом блока и входом элемента НЕ,выход - с первым входом первого- элемента И,второй вход - с выходом элемента НЕ,третийвход - с выходом второго триггера и первым входом второго элемента И, а четвертый вход - с третьим входом блока и вторым входом .первого элемента И, подключенного выходом к первому входу второго триггера, второй вход которого соединен с вторым входом блока, третий вход - с четвертым входом блока и первым входом третьего элемента И, а четвертьой вход - с выходом третьего триггера, nepBfcjM входом четвертого триггера и третьим выходом блока, второй вход второго элемента И подключен к пятому входу блока, а выход - к первому выходу блока и второму входу третьего элемента И, выходом соедиНенного с первым входом третьего триггера, выход четвертого триггера является вторым выходом блока, треть входы первого и третьего элементов И Вторые входы третьего и четвертого триггеров и пятый вход второго тригРвра подключены к группе входов блок

3.Устройство по п. 1, отличающееся тем, что блок управления содержит четыре элемента И, элемент ИЛИ и элемент НЕ, причем перВЫе входы элементов И соединены с Яятым входом блока, второй и третий входы первого элемента И подключены соответственно к первому и четвертому входам блока, второй и третий входы второго элемента И соединены соответственно с вторым входом блока

Я через элемент .НЕ с четвертым входом блока, вторые входы третьего и четвертого элементов И подключены соответственно к третьему и второму входам блока, а выходы - соответственно к второму и третьему выходам блока выходы первого и второго элементов И соединены соответственно с первым и вторым входами элемента ИЛИ, вьдход которого является первым выходом блока Четвертые входы первого и второго элементов И и третьи входы третьего и четвертого элементов И соединены с группой входов блока.

4.Устройство по п. 1, о т л ичаЮщееся тем, что блок подготовки канала содержит два триггера

и три элемента И, причем первые входы триггеров соединены с первьлм входом блока, первый выход второго триггера подключен к первым входам элементов И, второй вход первого элемента И соединен с вторым входом блока, а выход - с вторым входом первого

триггера и с четвертым выходом блока выход первого триггера подключен к второму входу второго элемента И, выход которого соединен с вторым выходом блока, вторые входы второго триггера и третьего элемента И соединены с третьим входом блока, выход третьего элемента И соединен с третьим выходом блока, второй выход второго триггера подключен к первому выходу блока, третьи входы вторюго триггера и второго элемента И соединены с группой входов блока.

5, Устройство по п. 1, о т л ичающееся тем, что-блок синхронизации содержит группу элементов И, генератор, триггер, счетчик, распределитель импульсов, два элемента И, элемент И-ИЛИ и элемент ИЛИ, причем первый выход генератора соединен с первым входом распределителя импульсов, с первыми входами элементов И группы, первым и вторым входами элемента И-ИЛИ, второй выход генератора подключен к первым входам первого и второго элементов И, вторые входы которых соединены с соответствующими выходами триггера, первый вход которого соединен с выходом элемента ИЛИ входы элемента ИЛИ подключены к выходам соответствующих элементов И группы, второй вход триггера соедине с выходом элемента И-ИЛИ и первым входом счетчика, второй вход которого подключен к выходу первого элемента И, а выход - к третьему входу элемента И-ИЛИ, выход второго элемента соединен с вторым входом распределителя импульсов, группа выходов которого является группой выходов блока, вторые и третьи входы элементов И группы н четвертый вход элемента И-ИЛИ подключены соответственно к первой и второй группам входов блока и входу блока.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 1 528561, кл. G 06 F 3/04, 1974.

2.Авторское свидетельство СССР по заявке 2706314,кл. G 06 F 3/04, 1979 (прототип). . ву Нача/10 масшоа Запрос ОпросвУ mff-8 Начало ffacca&i Запрос Опросд /7вб-В

/- jiJiJiJijrTJTJTJTJTJ OJlJTnJlJlJrTJlJTrUlJ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1982 |

|

SU1062681A2 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1981 |

|

SU1003066A1 |

| Устройство для сопряжения цифровой вычислительной машины с общей магистралью | 1980 |

|

SU907536A1 |

| Устройство для обмена информацией управляющей вычислительной машины с объектами управления | 1979 |

|

SU783782A2 |

| Устройство для сопряжения вычислительной машины с магистралью | 1981 |

|

SU980088A2 |

| Устройство для ввода информации | 1982 |

|

SU1130854A1 |

| Многоканальное устройство для обмена информацией | 1984 |

|

SU1359781A1 |

| Устройство для сопряжения процессоров с внешними абонентами | 1978 |

|

SU750472A1 |

| Устройство для ввода информации | 1987 |

|

SU1432544A1 |

Авторы

Даты

1982-02-23—Публикация

1980-07-07—Подача