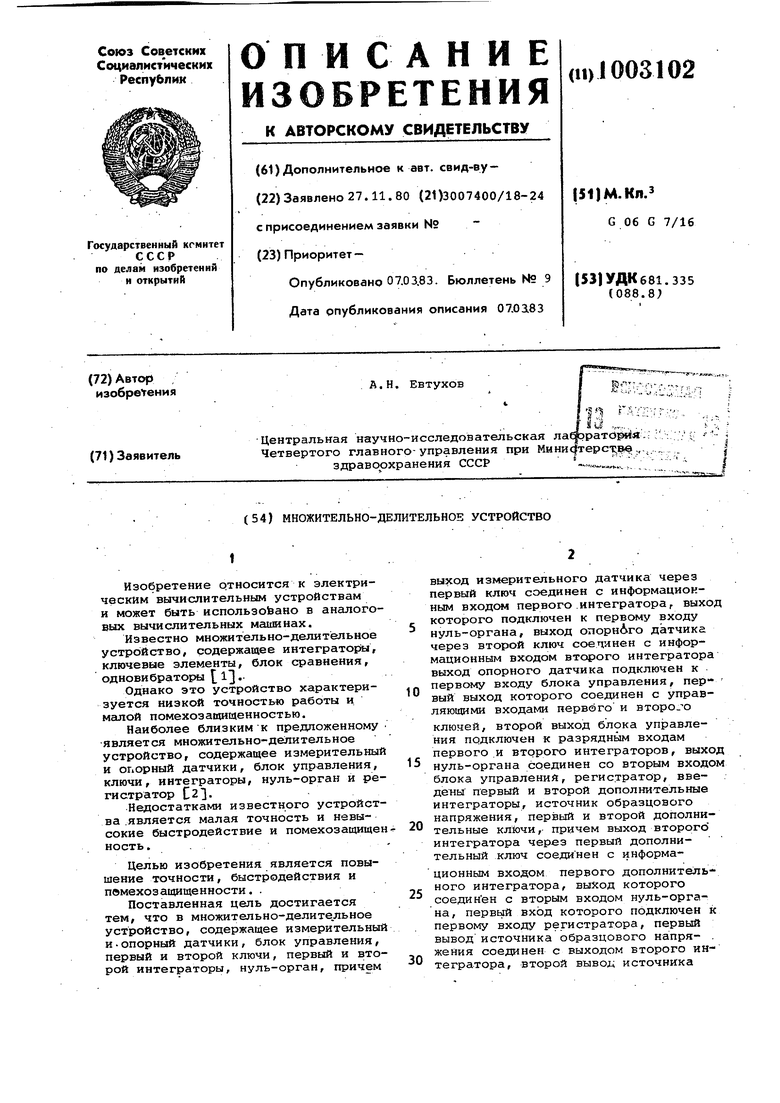

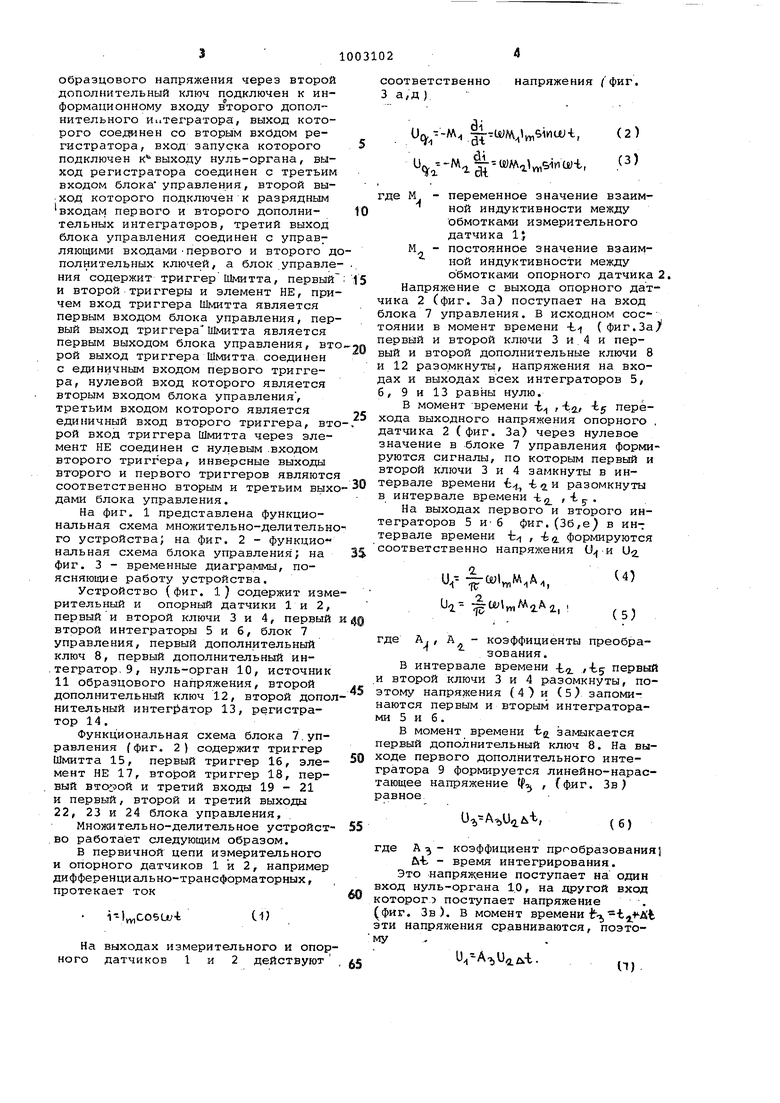

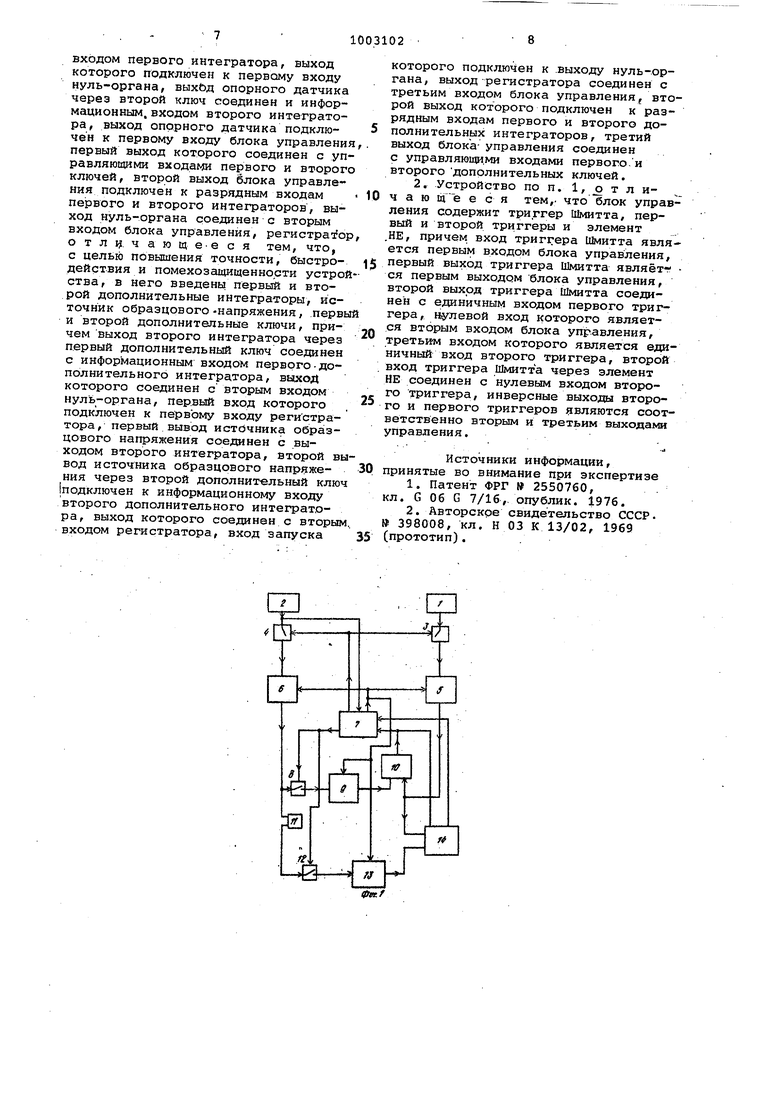

Изобретение относится к электрическим вычислительным устройствам и может быть использоЬано в аналоговых вычислительных машинах. Известно множительно-делительное устрЬйство, содержащее интеграторы, ключевые элементы, блок сравнения, одновибраторы 1. Однако это устройство характеризуется низкой точностью работы и малой помехозащищенностью. Наиболее близким к предложенному является множительно-делительное устройство, содержащее измерительный и опорный датчики, блок управления, ключи, интеграторы, нуль-орган и регистратор С21. Недостатками известного устройства .является малая точность и невысокие быстродействие и помехозащите ностъ. . Целью изобретения является повышение точности, быстродействия и помехозащищенности. . Поставленная цель достигается тем, что в множительно-делите.льное устройство, содержащее измерительный и.опорный датчики, блок управления, первый и второй ключи, первый и второй интеграторы, нуль-орган, причем выход измерительного датчика через первый ключ соединен с информационным входом первого .интегратора, выход которого подключен к первому входу нуль-органа, выход опорного датчика через второй ключ соединен с информационным входом второго интегратора выход опорного датчика подключен к первому входу блока управления, первый выход которого соединен с управляющими входами первого и второ.о ключей, второй выход блока управления подключен к разряднь1м входам первого и второго интеграторов, выход нуль-органа соединен со вторым входом блока управлений, регис.тратор, введены первый и второй дополнительные интеграторы, источник образцового напряжения, первый и второй дополнительные ключи,- причем выход второго интегратора через первый дополнительный ключ соединен с информационным входом первого дополнительного интегратора, выход которого соединен с вторым входом нуль-органа, первьЕй вход которого подключен к первому входу регистратора, первый вывод источника образцового напря- . жения соединен с выходом второго интегратора, второй источника образцового напряжения через второй дополнительный ключ подключен к информационному входу второго дополнительного Интегратора, выход которого соединен со вторым входом регистратора, вход запуска которого подключен к выходу нуль-органа, выход регистратора соединен с третьим входом блока управления, второй выход которого подключен к разрядным входам первого и второго дополнительных интеграторов, третий выход блока управления соединен с управ ляющими входамипервого и второго д полнительных ключей, а блок управле НИН содержит триггерШмитта, первый и второй триггеры и элемент НЕ, при чем вход триггера Шмитта является первым входом блока управления, пер вый выход триггера Шмитта является первым выходом блока управления, вт рой выход триггера Шмитта соединен с единичным входом первого триггера, нулевой вход которого является вторым входом блока управления, третьим входом которого является единичный вход второго триггера, вт рой вход триггера Шмитта через элемент НЕ соединен с нулевым .входом второго триггера, инверсные выходы второго и первого триггеров являютс соответственно вторым и третьим вых дами блока управления. На фиг. 1 представлена функциональная схема множительно-делительн го устройства; на фиг. 2 - функцио нальная схема блока управления; на фиг. 3 - временные диаграммы, поясняющие работу устройства. Устройство (фиг. 1) содержит изм рительный и опорный датчики 1 и 2, первый и второй ключи 3 и 4, первый второй интеграторы 5 и б, блок 7 управления, первый дополнительный ключ 8, первый дополнительный ин.тегратор.Э, нуль-орган 10, источник 11 образцового напряжения, второй дополнительный ключ 12, второй допо нительный интег1)атор 13, регистратор 14. Функциональная схема блока 7. управления (фиг. 2) содержит триггер Шмитта 15, первый триггер 16, элемент НЕ 17, второй триггер 18, первый и третий входы 19 - 21 и первый, второй и третий выходы 22, 23 и 24 блока управления, Множительно-делительное устройст во работает следующим образом. В первичной цепи измерительного и опорного датчиков 1 и 2, например дифференциально-трансформаторных, протекает ток ilvviCoeijft На выходах измерительного и опор ного датчиков 1 и 2 действуют напряжения (фиг. соответственно 3 а,д ) . . (2) V-W -iWMa sintjyi, (3) где M - переменное значение взаим ной индуктивности между обмотками измерительного датчика 1) М - постоянное значение взаимной индуктивности между обмотками опорного датчика 2, Напряжение с выхода опорного датчика 2 (фиг. За) поступает на вход блока 7 управления. В исходном состоянии в момент времени -t ( фиг. первый и второй ключи 3 и,4 и первый и второй дополнительные ключи 8 и 12 разомкнуты, напряжения на входах и выходах всех интеграторов 5, 6, 9 и 13 равны нулю. В момент времени -t , ., -ig перехода выходного напряжения опорного , датчика 2 (фиг. За) через нулевое значение в блоке 7 управления формируются сигналы, по которым первый и второй ключи 3 и 4 замкнуты в интервале времени t, разомкнуты в интервале времени -t. t 5- На выходах первого и второго интеграторов 5 и-6 фиг. (36,е) в интервале времени t/j , -t формируются соответственно напряжения ( Ug. ,А,, г-- , где А,, А - коэффициенты преобразования. В интервале времени -t/z. /-tj первьй и второй ключи 3 и 4 разомкнуты, поэтому напряжения (4) и (5) запоминаются первым и вторым интеграторами 5 и 6 . В момент времени Ьд замыкается первый дополнительный ключ 8. На выходе первого дополнительного интегратора 9 формируется линейно-нарастающее напряжение Ч , Гфлг. Зв) равное , АЗ коэффициент преобразования) &-Ь - время интегрирования. Это напряжение поступает на один вход нуль-органа 10, на другой вход которого поступает напряжение . (фиг. Зв). В момент времени-t -t + At эти напряжения сравниваются, поэтому .. .

Из рапенства t. 7 ) следует, что интервал времени равен

(8) г Ua т.е. интервал времени (фиг. За,в) ,--ta gj пропорционален отношению выходных напряжений первого и второго интегр торов 6 .и 5. Одновременно в момент времени -Ь/з, замыкается второй дополнительный ключ 12, который также замкнут и в интервале времени Л . На выходе второго дополнительног интегратора 13 формируется напряжение, равное и4 А4СЕ-и2.Ы, tie) где А. коэффициент преобразовани напряжение источника 11 образцового напряжения, включенного встречно выход ному напряжению второго интегратора б, причем выби рается Е 7/ 1, . С учетом равенств (8), (10) полуV.-feu-u.). Таким образом, выходное напряжение дополнительного интегратора il3 пропорционально произведению отношения выходных напряжений первого и второго интеграторов 5 и б на раз ность напряжений источника 11 образцового напряжения и второго интегратора б. В момент времени -Ь первый и второй дополнительные ключи 8 и 12 размыкаются и запоминаются выходные напряжения первого и второго дополнительных интеграторов (фиг. Зв,г,ж В интервале времени-t,,,, t выходные напряжения первого интегратора 5 и второго дополнительного интегратора 13 суммируются на входе регистратора 14, где формируется напряжения равное 5- ч первый и второй дополнительные интеграторы 9 и 13 выбираются так, чтобы

(13)

1

(J

С учетом (13) получим Uga Е(14) Равенство (14) показывает, что это напряжение представляет собой произведение, напряжения источника 11 образцового напряжения на отношение выходных напряжений первого и второго интеграторов 5 и б. С учетом

(4) и ( 5 ) равенство (14) можно записать в виде

Лч 1 . ,;,. I с

С15)

Ма

Формула изобретения

1. Множительно-делительное устройство, содержащее измерительный и опорный датчики, блок управления, первый и второй ключи, первый и второй интеграторы, нуль-орган, причем выход измерительного датчика через пер вый ключ соединен с информационным Первый и второй интеграторы 5 и б выбираются , так, чтобы. Тогда величина напряжения U (фиг. Зй) примет вид 5--,. (17 где А - - коэффициент преобразо вания. Т.е. напряжение Ug пропорционально переменной взаимной индуктивности измерительного датчика 1. Величина взаимной индуктивности пропорциональна параметру, регистрируемому измерительным датчиком 1. Как следует из (17), результат преобразования не зависит от изменений напряжения в сети, питающей измерительный и-опорный датчики 1и2, В интервале времени Ь г 4- напряжение и поступает на регистратор 18, в качестве которого может использоваться например цифровой вольтметр. В момент времени -Ьъ на регистратор 18 поступает команда на считывание результата преобразования. В интервале времени -fcj , производится (фиг. 3 кодирование напряжения. Вмомент времени i регистрация заканчивается. Из регистратора 18 в .блок 7 автоматического управления поступает команда Конец кодирования. В блоке 7 автоматического управления формируются сигналы на разряд всех интеграторов. В момент времени -tj в блоке .7 управления формируются сигналы, подготавливающие интеграторы к следующему циклу работы, котогйлй протекает аналогичным образом. Время преобразования равно одному периоду тока питающей сети. По сравнению с известным предложенное множительно-делительное устройство обладает Солее высокой точностью, помехозащищенностью и быстродействием. входом первого интегратора, выход которого подключен к первому входу нуль-органа, выхЬд опорного датчика через второй ключ соединен и информационным, входом второго интегратора, выход опорного датчика подключен к первому входу блока управлени первый выход которого соединен с уп равляющими входами первого и второг ключей, второй выход блока управления подключен к разрядным входам первого и второго интеграторов, выход нуль-органа соединен с вторым входом блока управления, регистрато о тлч. ч ающе-е ся тем, что, с целью повышения точности, быстродействия и помехозаашщенности устро ства, в него введены первый и второй дополнительные интеграторы, источник образцового-напряжения, .перв и второй дополнительные ключи, причем выход второго интегратора через первый дополнительный ключ соединен с информационным входом первого-дополнительного интегратора, выход которого соединен с вторым входом нуль-органа, первый вход которого подключен к первому входу регистратора, первый вывод источника образцового напряжения соединен с выходом второго интегратора, второй в вод источника образцового напряжеНИН через второй дополнительный клю {подключен к информационному входу второго дополнительного интегратора, выход которого соединен с вторы входом регистратора, вход запуска которого подключен к .выходу нуль-органа, выход регистратора соединен с третьим входом блока управления, второй выход которого подключен к разрядным входам первого и второго дополнительных интеграторов, третий выход блока- управления соединен с управляющи.ми входами первого.и второгодополнительных ключей. 2, Устройство по п. 1, о т л ич а ю щ е е с я тем,- что блок управления содержит триггер Шмитта, первый и второй триггеры и элемент НЕ, причем вход триггера Шмитта является первым входом блока управления, первый выход триггера Шмитта являётг ся первым выходом блока управления, второй выход триггера Шмитта соединен с единичным входом первого триггера, нулевой вход которого является вторым входом блока управления, третьим входом которого является единичный вход второго триггера, второй вход триггера Шмитта через элемент НЕ соединен с нулевым входом второго триггера, инверсные выходы второго и первого триггеров являются соответственно вторым и третьим выходами управления. Источники информации, принятые во внимание при экспертизе 1.Патент ФРГ 2550760, кл. G Об G 7/16, опублик. 1976. 2.Авторскре свидетельство СССР. 398008, кл. Н 03 К 13/02, 1969 (прототип). .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения вихревого компонента скорости потока | 1982 |

|

SU1016746A1 |

| Измеритель энергии искры | 1982 |

|

SU1078347A1 |

| Аналого-цифровое множительно-делительное устройство | 1973 |

|

SU449445A1 |

| Устройство для измерения вихревого компонента скорости потока | 1984 |

|

SU1265619A1 |

| Многоканальный автономный прибор для исследования скважин в процессе бурения | 1981 |

|

SU983261A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ИНТЕРВАЛЫ ВРЕМЕНИ | 2014 |

|

RU2552605C1 |

| Устройство измерения отклонения сопротивления от заданного значения | 1990 |

|

SU1737360A1 |

| Цифровой омметр | 1979 |

|

SU847224A1 |

| Множительно-делительное устройство | 1977 |

|

SU696444A1 |

| Устройство для определения оценок амплитудно-частотных характеристик | 1987 |

|

SU1439537A1 |

Авторы

Даты

1983-03-07—Публикация

1980-11-27—Подача