(54) ЦИФРОВОЙ ЧАСТОТОМЕР

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой частотомер | 1980 |

|

SU940082A1 |

| Цифровой частотомер | 1980 |

|

SU1035529A1 |

| Следящий частотомер | 1983 |

|

SU1210104A1 |

| Цифровой частотомер | 1979 |

|

SU838602A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕЦИЗИОННЫЙ ЧАСТОМЕР ПРОМЫШЛЕННОГО НАПРЯЖЕНИЯ | 2006 |

|

RU2333501C1 |

| Измерительный двухфазный генератор | 1987 |

|

SU1442931A1 |

| Устройство для регистрации и контроля измеряемых параметров | 1982 |

|

SU1068711A1 |

| Цифровой следящий частотомер | 1980 |

|

SU892335A1 |

| Цифровой частотомер | 2019 |

|

RU2730047C1 |

| Способ определения частотной характеристики испытуемого объекта и устройство для его осуществления | 1984 |

|

SU1223074A1 |

1

Изобретение относится к автоматике и информационно- измерительной технике и лредиазначается для автоматического измерения частоты с выдачей результатов измерения в ш«|фрвом коде, пригодном; для ввода в электронную цифрочвую вычислительную машину.

Известен цифровой частотомер, содержа1аий генератор эталонной частоты, счетчик импульсов эталриной частоты, Q формирователь импульсов измеряемой частоты, а также различные вспсжюгательные схемы Ci 1

Недостатком известного частотомера является его низкое быстродействие, is

Наиболее близким к предлагаемому изобретению является ус1Гр Лство, содержащее генератор эталонной частоты, первый и второй деявтвпи частоты, упра&аяемые от разрядного регистра, пося. 20 довательно соединенные первый и второй блоки задержки, счетчик импульсов измеряемой частоты, линейку вентилей, закольцованный сдвиговый регистр, последовательно соединенные блок антв совпадений,блок задержки и элемент ИЛИ, второй вход которого подключен к выходу формирователя импульсов, пер. вому входу схемы антисоЕшайений и суммирующему входу реверсивного счетчика, вычитающий вход которого соединен с 9Ь1ходом пнфрового интег-. ратор вхрй koTOporo соединен с выходом второго делителя частоты. Постедовательно соединенные блоки- антисовпадений, блок задержки и элемент ИЛИ, служат для исключения потери импульса измеряемой частоты при установке счетчика измеряемой частоты в ноль и представляпот собой одну из возможных реализаций блока исключения пот ,ри импульсов измеряемой частоты С21 ,

Недостатки известногоч устройствабольшой объем обаруцовеазия при большой : частоте снятия результата и высокой точности измерения частоты, а также небольшой диапазон измеряемых чаотот при заданной точности и частоте снятия результата.

Цель изобретения - повышение надежности..

Поставленная Цепь достигается тем, что в вдфровой частотомер, содержащий формирователь импульсов, реверсивный с%етчик, счетчик импульсов измеряемой частоты, регистр, преобразователь Koj -частота, первый и второй дешигели частоты, разр5юный регистр, генератор эталсжной частоты, выход которого подкшочен к входам и второго делктепей частоты, вторые входы которых подключены соответственно k первому я второму выходам реи вдного регистра, выход второго делителя частоты с первым входом преобразователя код- частота, второй вход которого подключен к выходу регистра, вход формирователя импульсов подключея к входной иогае усаройств1а, а выход формирователя ЕМ1 льсов, - к суммирующему входу реверсивного счетчика, блок исключения потери импульса, запоминающее устройство, блок управления, триггер, элемент И, счетчик адреса запоминающего устройства (ЗУ), первый вход которого соединен с входом блока управления и с выходом пёртого делите;. частоты, установочные входы счетчика адреса запомзшаюшего устройства соединены с первым входом триггера, с устансявочными входами реверсивного счетчика и с ишной установки начального состояния устрсЛства, первый выход счетчика адреса запо минающего устройства подключен к входу триггера, а второй выход счетчика адреса запоминающего устройства подключен к первому входу запоминающего устройства, второй вход которого соединен с первым выходом блока управления, третий вход запоминающего устройства соединен с выходом счетчика импульсов измеряемо частоты, а выход запоминающего устройства соединен с первым входом регистра, второй вход которого подключен к второму выходу блока управления, третий выход которого соединен с первым входом счетчика импульсов измеряемой частоты, а четвертый выход блока управления соедкшен с nepBbnvi входом блока исключения потери импульса, второй вход которого соединен: с выходом формирователя импульсов,а вых блока исключения потери импульса соединен с вторым входом счетчика импульсов теля код-частота подключен к первому входу элемента И, второй вход которого соединен с выходом триггера, а выход

элемента И соединен с вычитающим вхо. дом реверсивного счетчика, -причем второй вход счетчика адреса запоминающего устройства подключен к шине установки коэффициента пересчета устройства.

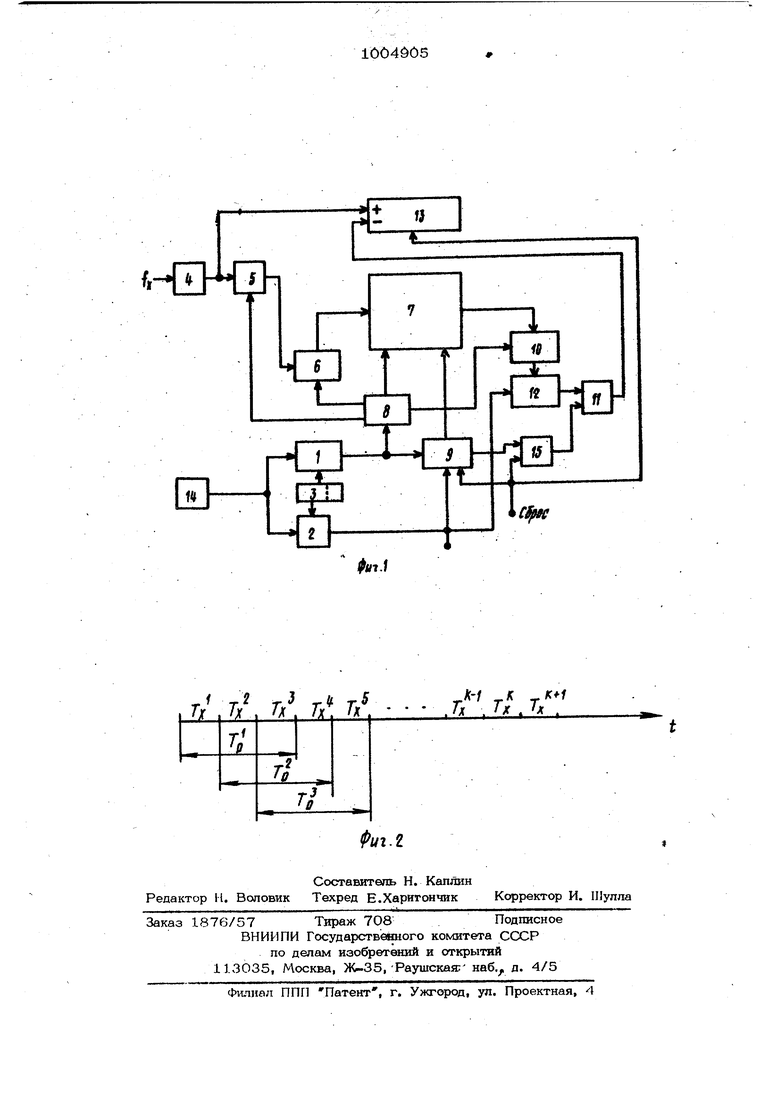

На фиг. 1 изображена блок- схема цифрового частотомера; на фиг. 2 - диаг рамма, поясняющая принцип действия устройства.

Цифровой частотомер содержит первый и второй делители 1 и 2 частоты, разрядный регистр 3, формирователь 4 импульсов, блок 5 исключения потери нмпульса измеряемой частоты, счетчик 6

импульсов измеряемой частоты, запоминающее, устройство 7, блок 8 управления, счетчик 9 адреса запоминающего устройства, регистр 10, элемент 11 И, преобразователь 12 код - частота,

реверсивный счетчик 13, генерйтор 14 эталонной частоты и триггер 15.

- Устройство работает следующим образом.

Принцип действия частотомера поясняется фиг. 2, на которой через TQ обозначен образцовый интервал врем&ни TO при к- ом измерении частоты у , через Tj - последовательность следующих друг за другсм равных интервалов

vpeMewit причем (7lToгдe m - число п - разрядных чисел, записанных. в запоминающем устройстве 7. На фиг. 2 т 3, сумма импульсов частоты f на интервале времени Тр , т.е. к-ом измерении. Чтобы получить первый результат измерения, необходимо Подсчитать сумму импульсов частоты f j( на интервале времени Т Q , т.е. М . Для того, чтобы получить результат второго измерения, нужно на суммь импульсов N вычесть число импульсо&г прищедщих за интервал времени Т и прибавить число импульсов частоты f прищедщих за интервал време1Ш Т J . Для получения К+ 1 -го измерения нужно из суммы импульсов N вычесть число мипульсов, пришедших за интервал времени Т,. и прибавить число импульсов, пркщедишх на интервале, т.е на интервале времени Т, который следует после интервала Т х через время Тд

Перед .началом работы частотомера триггер 15, счетчики 6 и 9 и реверв нощ В разрядный регистр 3 записывается число, определяющее длительност интервала времени Т, также при необходимости устанавливается нужный коэф фициент пересчета счетчика адреса 9. Во время работы устройства счетчик 6 считает сумму импульсов частоты на ка5кдом интервале Ту , а в моменты окончания этих интервалов по сигналу с выхода первого делителя 1 частоты содержимое счетчика 6 переписывается в запоминающее устройство 7, причем блок 8. управления сначала выдает сигнал на считывание информации из ячеек запсжшнающего устройст ва 7 в регистр 1О, а затем на записгь информации из счетчика 6 в эти же ячейки. Блок 5 исключения потери импульса измеряемой частоты управляет- ся от блока 8 управления и служит для исключения потери импульса измеряемой частоты на входе счетчика 6 при его совпадешш с икшульссял сброса счет чика 6 в ноль, а также для синхронизации подсчета импульсов счетчиком 6 С записью информацив в запоминаю{щее устройство 7. Когда запоминающее устройство 7 полностью заполниться, вместо суммы импульсов на интервале Tj записывается сумма импульсов на интервале Т j вместо суммы импульсов на TV записывается сумма импульсов наТ„ и т.д. Сигнал переполнения счетчика 9 адреса, свйдетельствующий о заполнении запоминающего устройства 7 нужной информацией, устанавливает-триггер 15 в едини цу, что разрешает прохождение через элемент 11 И последовательности импульсов с преобразователя 12 на реверсивный счетчик 13. Преобразователь 12 преобразует подаваемый на него код в последовательность равномерно расста&ленных на интервале времени Tj( тлггут сов, расположение которых при небольших интервалах времени или медленно мен ющейся частоте х подобно расположению импульсов измеряемой частоты на срсу ветствующем интервале времени. Поэтому с реверсивного счетчика 13 можно снимать результат не только через моменты времени Т, но и непрерывно. В обоих режимах измеряемая частот будет тропорцнонаяьна числу, записанному в реверсивном счетчике 13, т.е МN ,ном счетчике 13; число, записанное в разрадном регистре 3; IT - период следования импульсов генератора 14. При необходимости изменять коэф Я циент пересчета счетчика адреса, уста новочные вхо;цы счетчика 9 адреса подключается к первой дополнительной входной шине установки начального . состояния устройства. Запоминающее устройство при необходимости имегпь большую частоту снятия результата и -йысокую точность измерения частсуты, запоминает большой объем информации, цоступаюшей со счетчика измеряемой частоты, что щишощгг к теплу, что оснош1ан часть оборудования приходится на сдвиговой регистр. Поокольку степень ннтеграшш эап(жшнак щих устройств гораздо выше степени интеграции микросхем, на кгтрык строятся сдвшгювые регистры, применение запоминающего устройства даёт оущест венное уменьшение объема абордгповакия, требуемого для построения предлагавмого цифрового частот(Ж1ера с помощью изменения коэффициента пересчета счет чика адреса можно менять т , т.е. число запоминаемых чясеп. Это дает возможность измерять частоты в щи- :роком диапазоне при сохранении точности и частоты снятия результата. Формула изобретения Цифровой частотомер, содержащий формирователь импульсов, реверсивный счетчик, счетчик импульсов, измеряемой частоты регистр, преобразователь код- частота, первый и второй делители частоты, разрядный регистр, генератор эталонной частоты, выход которого подюшчен к первым входам первого и второго делителей частоты, вторые входы которых подключены соответст вевно к первому и второму выходам разрядного регистра, выход второго делителя частоты соединен с первым входом преобразователя код-частота, второй вход которого подключен к выходу регистра, вход формирователя импульсов подключен к входной шине устройства, а выход формирователя Импульсов - к суммирующему входу реверсивного счетчика, о т л и ч а ющ и .и с я тем, что, с целью повыше-

ния надежности, в него вве;аены блок исключения потери импульса, запсжишак шее устройство 6jiOK управления, триггер, элемент И, счетчик адреса запоминающего устройства, пе|рвый вход KOTOp го соеоинен с входом блока упра вления и с вьрсодом первого делителя частоты, установочные взводы счетчика адр&са запоминающего .устройства соед иены, с первыми входом триггера/с установочными входами реверсивного счетчика и с шиной установки началы ного состояния устройства, первый выход счетчика адреса запоминающего устройства подключен к второму твходу триггера, а второй вьЬсод счетчика адрёЬа запоминающего устройства подключе к перврму входу запоминающего устройства, второй вход которого со&динен с первым выходом блока управления, третий вход запоминающего устройства соединен с выходом счет чика импульсов измеряемой частоты, а вь1ход запоминающего устройства соединен с первым входом регистра, второй вход которого подключен к второ му выходу блока управления, третий

выход KOffoporo Соединен с пе1жым входом счетчика импульсов измеряемой частоты, а четвертый выход блока управления соединен с первым ъкоаом

блока исключения потери импульса, вто-1 рой вход которого соединен с выходс формирователя импульсов, а выход бло ка исключения потерю импульса соединен с вторым входс 4 счётчика импульсов

измеряемой частоты, выход преобразователя ко частота подключен к перво му входу И, второй вход которого соединен с, выходом триггера, а выход элемента И соединен с вычитающим

входом реверсивного счетчика. .

2, Часгот ер по п. 1, о т л и чающийся Тем, что второй вход счетчика адреса запоминающего устройства подключен к шине установки коэ({ь.

фициента пересчета устройства. Источники информации, принятые во внимание при экспертизе

/,

га

1 о

Авторы

Даты

1983-03-15—Публикация

1980-07-10—Подача