(Sk) ЦИФРОВОЙ ЧАСТОТОМЕР

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой частотомер | 1979 |

|

SU838602A1 |

| Цифровой частотомер | 1980 |

|

SU1004905A1 |

| Цифровой частотомер | 1980 |

|

SU1035529A1 |

| Следящий частотомер | 1983 |

|

SU1210104A1 |

| Цифровой частотомер | 2019 |

|

RU2730047C1 |

| Цифровой частотомер | 1975 |

|

SU530263A1 |

| Цифровой частотомер | 1980 |

|

SU918873A1 |

| Цифровой частотомер | 1980 |

|

SU930143A1 |

| Устройство для решения задач оптимального управления | 1985 |

|

SU1327135A1 |

| Функциональный преобразователь | 1985 |

|

SU1249547A1 |

1

Изобретение относится к измерительной технике и предназначается для автоматического измерения с выдачей результатов измерения в цифровом коде.

Известен цифровой частотомер, содержащий генератор эталонной частоты, счетчик импульсов эталонной частоты, формирователь импульсов измеряемой частоты, счетчик импульсов измеряемой,Q частоты, а также различные вспомогательные схемы fij.

Недостаток устройства - низкое быстродействие.

Наиболее близким по технической сущности к предлагаемому является устройство, содержащее генератор эталонной частоты, первый и второй делители частоты, управляемые от разрядного регистра, последовательно соеди-20 ненные первый и второй блоки задержки, счетчик импульсов измеряемой частоты, линейку вентилей, закольцованный сдвиговый регистр, последовательно соединенные блок антисовпадений, блок задержки и элемент ИЛИ, второй вход которого подключен к выходу формирователя импупьсов, первому входу схемы антисовпадений и суммирующему входу реверсивного счетчика, вычитающий вход которого соединен с выходом цифрового интегратора, вход которого соединен с выходом второго делителя частоты 21.

Недостаток известного устройства небольшой диапазон измеренных частот при заданной точности и частоте снятия результата.

Цель изобретения - расширение диапазона измеряемых частот.

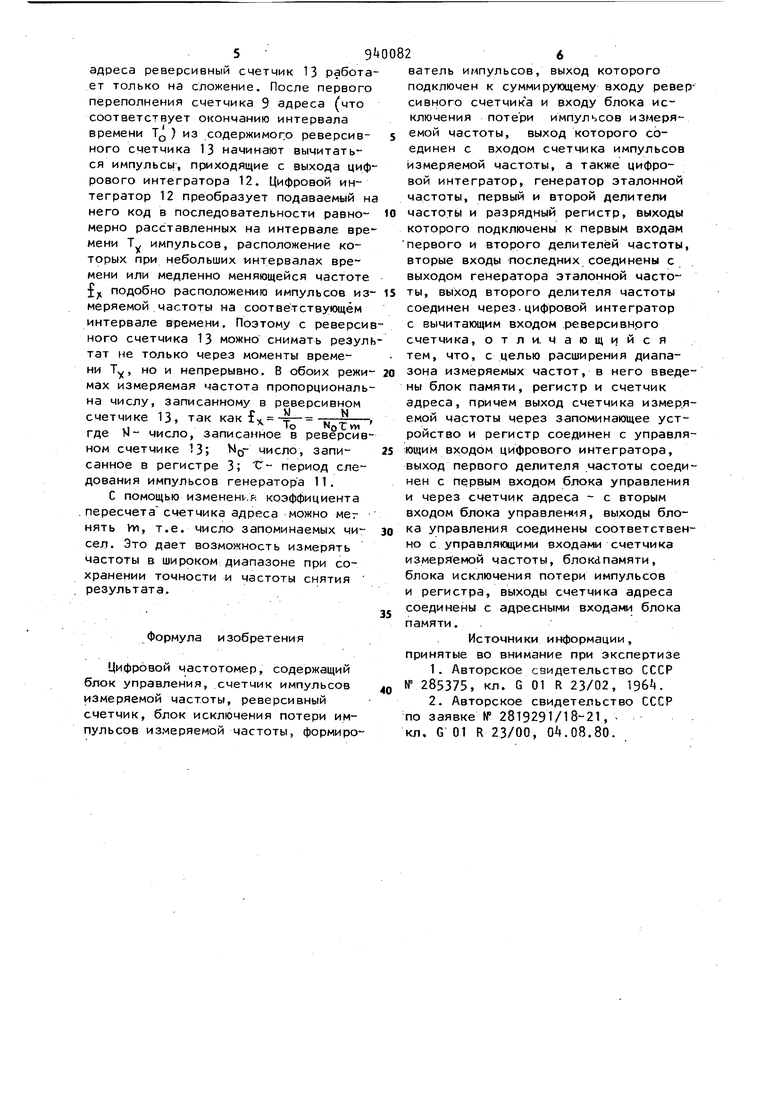

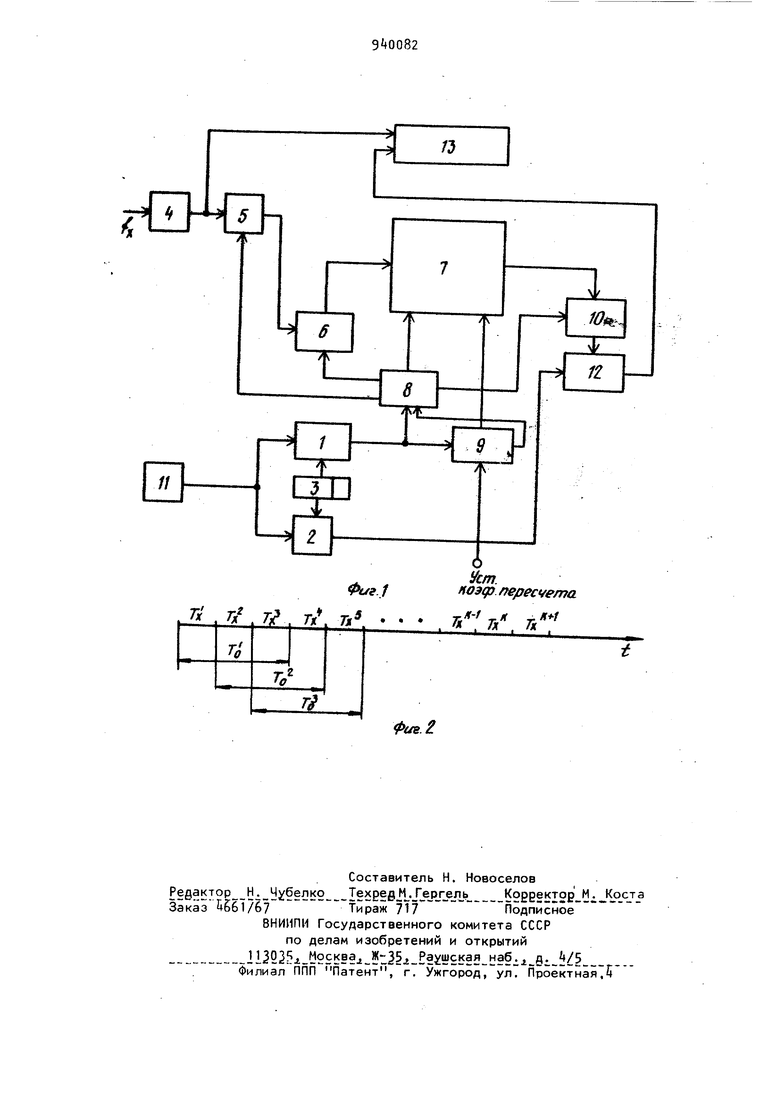

Указанная цель достигается тем, что в цифровой частотомер, содержащий блок управления, счетчик импульсов измеряемой частоты, реверсивный счетчик, блок исключения потери импульсов измеряемой частоты, формирователь импульсов, выход которого подключен к суммирующему входу реверсив3ного сметчика и входу блока исключе ния потери импульсов измеряемой час тоты, выход которого соединен с входом счетчика импульсов измеряемой частоты, а также цифровой интеграто генератор эталонной частоты, первый и второй делители частоты и разрядны регистр, выходы которого подключены к первым входам первого и второго делителей частоты, вторые входы последних соединены с выходом генератора эталонной частоты, выход второго делителя частоты соединен через цифровой интегратор с вычитающим входом реверсивного счетчика, введен блок памяти, регистр и счетчик адреса, причем выход счетчика измеряемой частоты через запоминающее устройство и регистр соединен с управляющим входом цифрового интегратора, выход первого делителя частоты соединен с первым входом блока управления и через счетчик адреса - с вто рым входом блока управления, выходы которого соединены соответственно с управляющими входами счетчика из-меряемой частоты, блока памяти, блока исключения потери импульса и регистра, выходы счетчика адреса соединены с адресными входами блока памяти,, На фиг. 1 изображена блок-схема цифрового частотомера; на фиг. 2 диаграмма, поясняющая принцип действия устройства. Цифровой частотомер содержит дели тели 1 и 2 частоты, разрядный регистр 3 формирователь импульров, блок 5 исключения потери импульсов измеряемой частоты, счетчик 6 импуль сов измеряемой частоты, блок 7 памяти, блок 8 управления, счетчик 9 адреса запоминающего устройства, ре- . гистр 10, генератор 11 эталонной час тоты, цифровой интегратор 12, реверсивный счетчик 13. Устройство работает следующим образом. Принцип действия частотомера поJ - образясняется на фиг. 2, где цовый интервал времени tj, при k-ом измерении частоты f Т - последовательность следующих друг за другом разных интервалов времени, причем т-Т Тр, где п - число п-разрядных чисел, написанных в блоке 7 памяти. На, фиг. 2 п 3. N у, - сумма импульсов частоты у, на интервале времени TJ/, т.е. при k--OM измерении. Чтобы 2 получить первый результат измерения, необходимо подсчитать сумму импульfx на интервале времечастотысов f . Для того, чтобы получить результат второго измерения, нужно из суммы импульсов N. вычесть число импульсов, пришедших за интервал времени Т, И прибавить число импульсов частоты fx , пришедших за интервал времени TJ. Для получения k+1-го измерения нужно из суммы имN. пульсов N вычесть число импульсов, пришедших за интервал времени Т , и прибавить число импульсов, пришедших на интервале, т.е. на интервале времени который следует после интервала Т через время Т.. . Перед началом работы частотомера регистр 10, счетчики 6, 9 и 13 устанаеливаю.тся- на ноль. В регистре 3 записывается число, определяющее длительность интервала времени Т , а также при необходимости устанавливается нужный коэффициент пересчета счетчика 9 адреса. Во время работы, устройства счетчик Ь считает сумму импульсов частоты f, на каждом интервале Ту, а в моменты окончания этих интервалов по сигналу с выхода делителя 1 частоты содержимое счетчика 6 переписывается в блок 7 памяти, причем на начальном интервале работы частотомера (в течение времени JQ ) на каждый импульс с выхода де-лителя 1 частоты блок 8 управления выдает сиг- нал только на запись информации в блок 7 памяти. В момент окончания . первого интервала времени Тр в блок 8 управления приходит импульс переполнения счетчика 9 адреса. После этого блок 8 управления на каждый импульс с.выхода делителя 1 частоты выдает сначала сигнал на-считывание информации из ячеек блока 7 памяти в регистр 10, а затем на записьинформации из счетчика 6 в эти же ячейки. БЛОК 5 исключенияпотери импульсов измеряемой частоты управляется от блока 8 управления и служит для исключения потери импульса измеряемой частоты на входе счетчика 6 при егосовпадении с импульсом сброса счетчика 6 в ноль, а также для синхронизации подсчета импульсов счетчиком 6 с записью информации в блок 7 памяти. Таким образом, на первом интервале TO до переполнения счетчика 9 5 9 адреса реверсивный счетчик 13 работает только на сложение. После первого переполнения счетчика 9 адреса (что соответствует окончанию интервала времени TQ ) из содержимого реверсивного счетчика 13 начинают вычитаться импульсь , приходящие с выхода цифрового интегратора 12. Цифровой интегратор 12 преобразует подаваемый на него код в последовательности равномерно расставленных на интервале времени Т импульсов, расположение которых при небольших интервалах времени или медленно меняющейся частоте fji подобно расположению импульсов измеряемой частоты на соответствующем интервале в ремени. Поэтому с реверсив ного счетчика 13 можно снимать резуль тат не только через моменты времени Ту, но и непрерывно. В обоих режи- 20 мах измеряемая частота пропорционал на числу, записанному в реверсивном счетчике 13, так как f -т щ где М- число, записанное в реверсив ном счетчике 13; NQ- число, записанное в регистре 3; период следования импульсов генератора 11. С помощью измeнeн,: коэффициента . пересчетасчетчика адреса можно мег нять Vr, т.е. число запоминаемых чисел. Это дает возможность измерять частоты в широком диапазоне при сохранении точности и частоты снятия результата. Формула изобретения Цифровой частотомер, содержащий блок управления, .счетчик импульсов измеряемой частоты, реверсивный счетчик, блок исключения потери импульсов измеряемой частоты, формиро2выход которого ватель импульсов, подключен к суммирующему входу реверсивного счетчика и входу блока исключения потери импульсов измеряемой частоты, выход которого соединен с входом счетчика импульсов измеряемой частоты, а также цифровой интегратор, генератор эталонной частоты, первый и второй делители частоты и разрядный регистр, выходы которого подключены к первым входам первого и второго делителей частоты, вторые входы последних соединены с выходом генератора эталонной частоты, выход второго делителя частоты соединен через - цифровой интегратор с вычитающим входом реверсивнрго счетчика, отличающийся тем, что, с целью расширения диапазона измеряемых частот, в него введены блок памяти, регистр и счетчик адреса, причем выход счетчика измеряемой частоты через запоминающее устройство и регистр соединен с управляющим входом цифрового интегратора, выход первого делителя частоты соединен с первым входом блока управления и через счетчик адреса - с вторым входом блока управления, выходы блока управления соединены соответственно с управляющими входами счетчика измеряемой частоты, блокЛпамяти, блока исключения потери импульсов и регистра, выходы счетчика адреса соединены с адресными входами блока памяти. . Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 285375, кл. G 01 R 23/02, 196. 2.Авторское свидетельство СССР по заявке№ 2819291/18-21, кл. G 01 R 23/00, 04.08.80.

О

Уст.

Фиг.) коздз пересчета

Авторы

Даты

1982-06-30—Публикация

1980-12-30—Подача