к третьему входу коммутатора записи-считывания, а четвертый, пятый и шестой выходы блока обработки информации подключены -хгоответственно к. третьему входу коммутатора адреса, к второму входу четвертого распределительного блока и к второму

входу управлякядего триггера, а к .второму, третьему и четвертому входам блока обработки информации подключены соответственно выход второго эапоминаклдего блока, выход делителя частоты и выход блока запуска.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена данными в многопроцессорной вычислительной системе | 1983 |

|

SU1136143A1 |

| Многоканальная система измерения и регистрации | 1988 |

|

SU1707546A1 |

| Запоминающее устройство | 1983 |

|

SU1116458A1 |

| Запоминающее устройство | 1985 |

|

SU1259336A2 |

| Устройство для вычисления скользящего спектра | 1981 |

|

SU1027733A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1278980A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Микропрограммное устройство для приоритетного обслуживания группы абонентов | 1984 |

|

SU1302277A1 |

| Устройство для аппаратурной трансляции | 1983 |

|

SU1144108A1 |

УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ И КОНТРОЛЯ ИЗМЕРЯЕМЫХ ПАРАМЕТРОВ, содержащее датчики измеряемых параметров, счетчик импульсов, управляющий триггер, кварцевый генератор, подключенный к делителю частоты, блок управления, блок запуска, блок регистрации, отлич ающеес я тем, что, с целью повышения экономической эффективности устройства, в него введеныmвходных формирователей, п выходных усилителей, мультиплексор, дешифратор шин, блок выдачи адреса, регистр, первый и второй-запоминающие блоки, первый, второй, третий и четвертый распределительные блоки, коммутатор записи-считывания, коммутатор адреса, блок обработки информации, программный блок и блок выдачи информации на регистрацию, причем датчики измеряемых параметров вклют чены в узлы матрицы размером mxn, на шины п которой включены выходные усилители, а на шины m - входные формирователи, выходы которых подсоединены к входам мультиплексора, на вход которого также подключен выход блока выдачи адреса, соединенный с первым .входом первого запоминаквдего блока, первым входом коммутатора адреса и с дешифратором шин выходы которого подключены к входам выходных усилителей, к входу блока выдачи адреса .оодсоединен первый выход блока управления, к первому входу которого подк лючен выход кварцевого генератора, к второму - выход управляющего триггера, соединенного также с коммутатором записи и считывания и коммутатором адреса, а к входу первого распределительного блока подключен выход регистра, подключенного также к второму входу первого запоминающего блока, к второму выходу блока управления и к выходу мультиплексора, тре тий выход блока управления соединен с третьим входом первого запоминающего блока,выход которого соединен с третьим входом регистра, при этом выход коммутатора адреса подключен к первому вход второгр запоминаю- J щего блока, выход которого соединен л с первым входом счетчика импульсов, соединенного вторым входом через второй распределительный блок с выходом первого распределительного блока, а к второму входу второго распределительного блока подключен четвертый выход блока управления, пятый выход которого соединен с третьим входом счетчика импульсов, С35 00 подключенного выходом через третий распределительный блок к второму вхо ду второго запоминаквдего блока, на третий вход которого подключен выход коммутатора записи-считывания, соединенного с шестым выходом блока управления, первый выход которого подключен также к первому входу четвёртого распределительного блока, .соединенного выходом с первым входом управляющего триггера, выход которого соединен с вторым входом третьего распределительного блока, а к входу блока регистрации через блок выдачи информации на регистрацию подключен первый выход блока обработки информации, второй выход которого и вход соединены соответственно с входом и выходом программного блока, третий выход подключен;

1

Изобретение относится к информационно-измерительной технике и может быть использовано для измерения регистрации и контроля параметров режима технологического процесса либо параметров изучаемого многопараметрического процесса, в частности в системах сбора, учета и контроля энергоносителей (газа, воды, тепловой энергии, электрической энергии);

Известно многоканальное устройство цифрового измерения и регистрации, содержащее аналого-цифровой преобразователь, реверсивный счетчик, блок запуска, коммутатор и регистратор tl 1.

Однако в данном устройстве на каждый канал связи применен счетчик импульсов, что повьниает аппара турные затраты, и, кроме того, оно имеет ограниченные возможности по контролю измеряемых параметров.

Наиболее близким по технической сущности к изобретению является устройство для измерения и регистрации информации, содержащее датчики технологических параметров, распределительные схемы И, счетчики импульсов, задатчйк временных интервалов, кварцевый генератор,, подключенный к делителю частоты, управляющий триггер, регистр опроса, .счетчик текущего времени, блок управления, блок регистрации, схемы объедикения ИЛИ, дешифратор, усилитель, блок запуска 2.

Недостатком данного устройства является наличие на каждый датчик индивидуальной линии связи и аппаратурная избыточность (на каждый измеряемый канал примерно по два счетчика импульсов), что повышает стоимость устройства.

Цель изобретения - повышение экономической эффективности устройства

Поставленная цель достигается тем, что в устройство, содержащее датчики измеряемых параметров, счетчик импульсов, управляющий триггер.

кварцевый генератор, подключенный к делителю частоты, блок управления, блок запуска, блок регистрации, введены гп входных формирователей,п выходных усилителей, мультиплексор, дешифратор шин, блок выдачи адреса, регистр, первый и второй запоминающие блоки, первый, второй, третий и четвертый распределительные блоки,

O коммутатор записи-считывания, коммутатор адреса, блок обработки информации, программный блок и блок выдачи информации на регистрацию, при,чем датчики измеряемых параметров

с включены в узлы матрицы размером т хп, на шины п которой включены выходные усилители, а на шины m - входные формирователи, выходы которых соединены с входами мультиплексора, на вход которого также подключен вы0 ход блока выдачи адреса, соединенный с первым входом первого запоминающего блока, первым входом коммутатора адреса и с дешифратором шин, выходы которого подключены к входам выход5 ных усилителей, к входу блока выдачи адреса подсоединен первый выход блока управления, к первому входу которого подключен выход кварцевого генератора, к второму - выход управ0 ляющего триггера, соединенного также с коммутатором записи и считывания и коммутатором адреса, к входу первого распределительного блока подключен выход регистра, подключенного

5 также к второму входу первого запоминающего блока, к второму вькоду блока управления и к выходу мультиплексора, третий выход блока управления соединен с третьим .входом перQ вого запоминагаДего блока, выход которого соединен с треть-им входом регистра, при этом выход коммутатора адреса подключен к первому входу второго запоминающего блока, выход которого соединен,с первым входом

счетчика импульсов, соединенного вторым входом через второй распределительный блок с выходом первого

распределительного блока, а к второму входу второго распределительного блока подключен четвертый выход блока управления, пятый выход которого соединен с третьим входом счетчика импульсов, подключенного выходом через третий распределительный блбк к второму входу второго запоминающего блока, на третий вход которого подключен выход коммутатора записисчитывания, соединенного с шестым выходом блока управления, первый выход которого подключен также к первому входу четвертого распределительного блока, соединенного выходом с первым входом управляющего триггера выход которого соединен с вторым входом третьего распределительного блока, а к входу блока регистрации через блок вьщачи информации на регистрацию подключен первый выход блока обработки информации, второй выход которого и вход соединены соответственно с входом и выходом программного блока, третий выход, подключен к третьему входу коммутатора записи-считывания, а четвертый, пятый и шестой выходы блока обработки информации подключены соответственно к третьему вхоДу коммутатора адреса к второму входу четвертого распределительного блока и к второму вхоДУ управляющего триггера, а к второму, третьему и четвертому входам блока обработки информации подключены соответственно выход второго запоминающего блока, выход делителя частоты и выход блока запуска.

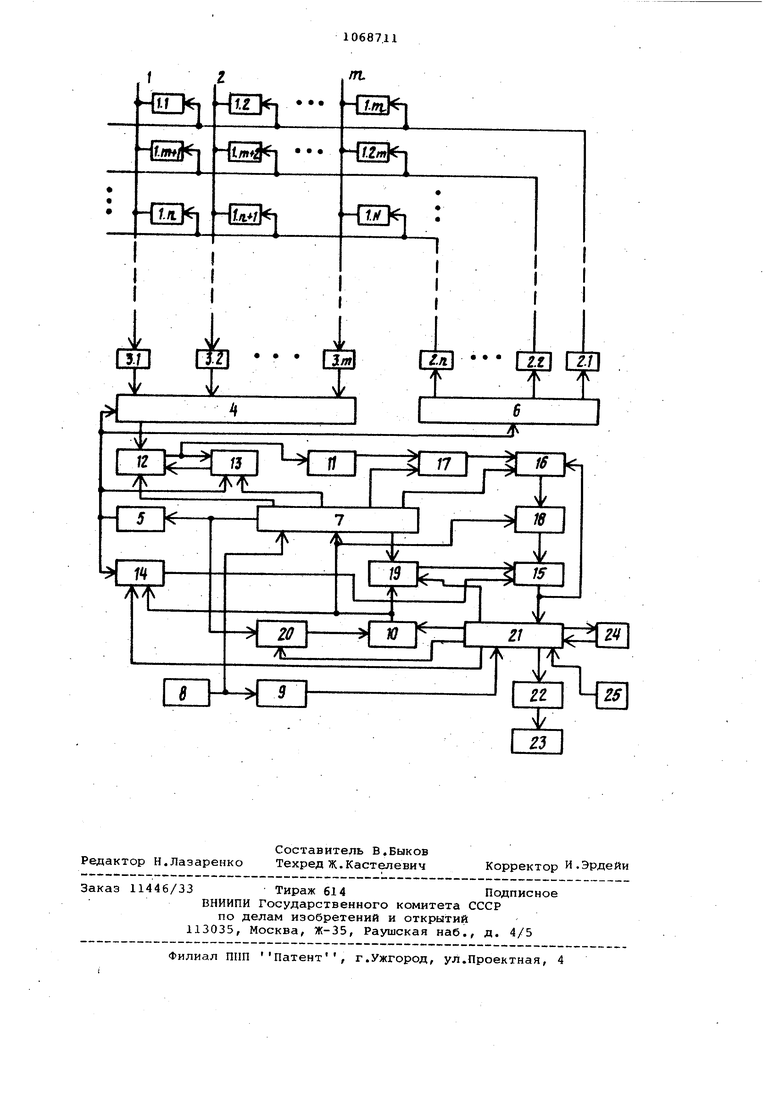

На чертеже представлена блок-схема устройства для регистрации и контроля измеряемых параметров.

Устройство содержит датчики , 1.1, ..., 1.N измеряемых параметров включенные в узлы матрицы размером mxn, на шины п которой включены выходные усилители 2.1, ..., 2.п, а на шины ГТ1 включены входные формирователи 3.1, ..., З.т, представляющие собой транзисторные ключи для преобразования уровня входных сигналов. Входные формирователи 3.1,..., З.т подключены к входам мультиплексора 4 (в качестве которого можно использовать микросхему мультиплексора К155КП1), на вход которого также подключен выход .блока 5 вьщачи адреса, представляющего собой К- разрядный двоичный счетчик, подключенный также к дешифратору б шин, выходы которого подключены к входам выходных усилителей 2.1, ..., 2п. К входу блока 5 выдачи адреса подключен первый вЕлход .блока 7 управления, представляющего собой многофазный генератор импульсов, состоящий из счетчика импульсов и дешифратора К первому входу блока 7 управления подключен, выход кварцевого генератора 8, подключенного к делителю 9 частоты. К второму входу блока 7 управления подключен выход управляющего триггера 10. К входу первого распределительного блока 11, представляющего собой г-входовую логику И-НЕ, подключен вьЛход регистра 12, подключенного также к первому входу первого запоминающего блока (ЗБ) 13, к второму входу которого подключен второй выход блока 7 управления, третий выход которого подключен к первому входу регистра 12, к второму входу которого подключен выход мультиплексора 4, а к третьему входу регистра 12 подключен выход первого запоминающего блока 13, к третьему входу которого подключен выход блока 5 вьздачи адреса. Выход блока 5 вьщачи адреса подключен к первому входу коммутатора 14 адреса, выход которого подключен к первому входу второго запоминающего блока (ЗВ) 15. Выход последнего подключен к первому входу счетчика 16 импульсов, к второму входу которого подключен выход второго распределительного блока 17, представляющего собой набор двухвходовых логических схем И-НЕ. К входу второго распределительного блока 17 подключен выход первого распределительного блока 11. К второму входу второго распределительного блока 17 и к третьему входу счетчика 16 им.пульсов подключены соответственно четвертый и пятый выходы блока 7 управления. Выход счетчика 16импульсов подключен к первому входу третьего ра спределительного блока 18, представляющего собой набор двухвходовых логических схич И-НЕ, выход которого подключен к второму входу второго запоминающего блока 15. На третий вход второго запоминающего блока 15 подключен выход коммутатора 19 записи-считывания, к первому входу которого подключен шестой выход блока 7 управления, первый выход которого подключен к первому входу четвертого распределительного блока 20 (двухвходовая схема И-НЕ), выход которого подключен к первому входу управляющего триггера 10,подключенного к второму входу коммутатора записи-считывания 19, второму входу ко:лмутатора 14 адреса и к второму входу третьего распределительного блока 18. Выход второго запоминающего блока 15 подключен к второму входу блока 21 обработки информации (в качестве блока обработки информации можно использовать любую микро-ЭВМ, например Электроника СБ-12, Электроника С5-21, Электроника С5-31, состоящие из микропроцессора, оперативного запоминающего устройства, постоянного запоминающего устройства, устройств ввода-вывода, генератора тактовых импульсов и логических схем управления) . Первый выход блока 21 обработки информации подключен к блоку 22 вьадачи информации на регистрацию, представляющему собой стандартные адаптеры связи с регистрирующими устройствами, например адаптеры связи микро-ЭВМ Электроника С5-12 с телеграфным аппаратом (адаптер Электроника С5-124) с перфоратором (даптер Электроника С5-123) или другие адаптеры, обеспечивакмдие выдачу информации на регистрацию. к выходу блока 22 выдачи информации на регистрацию подключен вход блока 23 регистрации. Второй выход блока 21 обработки информации подключен к входу программного блока 24, представляющего собой ячейки постоя ного запоминающего устройства или репрограммируемого постоянного запоминающего устройства,К первому,трет ему и четвертому входам блока 21 обработки информации подключены выходы программного блока,24, делители 9 частоты и блока 25 запуска (пульта управления). Третий, четвертый, пятый и шестой выходы блока 21 обработки информации подключены соответственно к третьему входу коммутатора 19 записи-считывания, третьему входу коммутатора 14 адреса, к второму входу четвертого распределительного блока, 20 и к второму входу управляющего триггера 10. Устройство для регистрации и конт роля измеряемых параметров работает следующим образом. Дешифратор б шин, на вход которого поступает начальный адрес с блока Ь вьщачи адреса, через выходной усилитель 2.1 выдает сигнал на первую из п шин для опроса состояния первой группы датчиков 1.1,..,, 1 .т. В результате, через входные формирователи 3.1, ..., 3.IT1 к входам мультиплексора 4 подключаются первые m датчики 1.1, ..., 1.П1. Так как блоком 5 выцачи адреса установлен начальный адрес, то на вход h -разрядного регистра 12 через мультиплексор 4 п.оступает информация о состоянии первого датчика 1.1. На входы данных регистра 12 из первого ЗБ 13 поступает информация о состоянии дат чика 1.1 в предыдущих циклах опроса датчиков. По сигналу блока 7 управления информации о состоянии датчика 1.1 в предьщущих г циклах опроса датчиков, хранящиеся в первом ЗБ 13, записывается в регистр 12 и по сигналу блока 7 управления регистр производит сдвиг информации на один разряд вправо. В результате в первом разряде регистра 12 находится информация о состоянии датчика 1.1 в момент опроса. По сигналу блока 7 управления в первом ЗБ 13 по начальному адресу записываются выходные данные регистра 12 и, кроме того, эти данные поступают на вход первого распределительного блока 11, на выходе которого появляется сигнал только в том случае, когда код входного сигнала соответствует коду полезного сигнала. Такая организация приема информации позволяет не только получить полезный сигнал, но и отфильтровать кратковременные помехи, которые наводятся в линии связи, что повьлиает помехоустойчивость и достоверность приема информации. По начальному адресу, поступающему с блока 5 выдачи адреса через коммутатор 14 адреса, информация второго ЗБ 15 поступает на входы данных счетчика 16 импульсов и по сигналу блока 7 управления записывается в счетчик 16 импульсов. Далее выходная информация первого распределительного блока 11 через второй распределительный блок 17 по сигналу.блока 7 управления суммируется с содержимым счетчика 16 импульсов. По сигналу блока 7 управлени.я через коммутатор 19 записисчитывания во второй ЗБ 15 по начальному адресу, задаваемому блоком 5 выдачи адреса, записываются выходные данные счетчика 16 импульсов, поступающие на входы данных второго ЗБ 15 через третий распределительный блок 18. С приходом последнего сигнала с блока 7 управления, блок 5 выдачи адреса формирует адрес для опроса состояния датчика 1.2. Процесс опроса датчика 1.2 аналогичен ранее описанному. После опроса пёрвых гп датчиков (1.1,. ..., 1 .т) блоком 5 вьщачи адреса через дешифратор 6 шин и через выходной усилитель 2,2 выдается сигнал на вторую из п шин дЛя опроса состояния следующих m датчиков. Работой б.лока 7 управления (следовательно, частотой опроса датчиков) управляет кварцевый генератор 8. По истечении времени 4t , формируемого кварцевым генератором 8 и делителем 9 частоты и вырабатываемого блоком 21 обработки информации, с выхода последнего на вход четвертого распределительного блока 20 поступает сигнал. После прихода сигнала с блока 7 управления на второй вход четвертого распределительного блока 20 управляющий триггер 10 изменяет свое состояние, в результате, блокируется блок 7 управления и третий распределительный блок 18, а на входы коммутатора 14 адреса и коммутатора 19 записи-считывания с выхода управляющего триггера 10 поступает сигнал, переключающий коммутаторы 14 и 19 на работу от выходов блока 21 обработки информации. По адресам и сигналам записи-считывания, формируемым блоком 21 обработки информации, поступающим на вхо ды второго ЗБ 15 через коммутатор -14 адреса и коммутатор 19 записи-считывания, данные из второго ЗБ 15 переписываются в ячейки памяти блока 21 обработки информации, а содержимое второго ЗБ 15 обнуляется. После этого сигналом с блока 21 обработки информации триггер 10 переключается, в результате деблокируется блок 7 управления и третий распределительный блок 18, а коммутатор 14 адреса и коммутатор 19 записи-считывания переключается для работы соответственно от блока 5 выдачи адреса и от блока 7 управления. Алгоритм обработки входной информации записан в постоянном запоминающем устройстве (ПЗУ) блока 21 обработки информации. В ПЗУ блока 21 записан также алгоритм выработки текущего времени по временным меткам поступающим с кварцевого генератора 8 через делитель 9 частоты. Коэффициенты приведения входной информации к единым нормированным величинам, признаки совместимости информации, а также метки времени, в которые необходимо вьщавать информацию на регистрацию, записаны в программном блоке 24. Обработанная в блоке 21 информация через заданные промежутки времени поступает на входы блока 22 выдачи информации на регистрацию и регистрируется в блоке 23. Кроме того, имеется возможность регистрации информации по вызову с помощью блока 25 запуска (пульта управления). По заданному алгоритму блоком 21 обработки информации вычисляется прогнозное значение измеряемого параметра с заданным шагом упреждения и сравнение прогнозного значения с контрольными величинами, обеспечивая опережающий контроль измеряемого параметра. Предлагаемая схема устройства для регистрации и контроля измеряемых параметров является более экономичной по сравнению с известной. При этом увеличение даже количества датчиков измеряемых параметров (в два раза) в предлагаемом устройстве ведет к незначительному увеличению его стоимости (от 12 до 20% в зависимости от длинь линий связи) в то время, как увеличение датчиков в известном устройстве ведет к увеличению его стоимости в 95-101%.

UD

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Многоканальное устройство цифрового измерения и регистрации | 1973 |

|

SU462991A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Подогреватель воды паром | 1924 |

|

SU767A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1984-01-23—Публикация

1982-07-08—Подача