1

Изобретение относится к способам и устройствам преобразования аналогового сигнала в цифровой коц и используемым в системах преобразования формы информации в измерительной и вычислительной технике.

По основному авт. св. № 892704 известен способ преобразования аналогового сигнала в цифровой код, включающий генерирование вспомогательного сигнала, модулирование этим сигналом уров ней квантования преобразуемого сигнала, одновременно квантование преобразуемого и вспомогательного сигналов и одновременное считывание цифровых значений квантованных величин преобразуемого и вспомогательного сигналов в моменты пересечения преобразуемым сигналом любого из модулированных уровней квантования преобразуемого сигаала С1 3

Недостатком этого спосоВа является низкая-точность при преобразовании сигналов, в которых есть участки измене-

ния, синфазные изменениям вспомогательного сигнала.

Известно устройство преобразования аналогового сигнала в цифровой код по авт. св. СССР № 892704, содержащее блок задания эталонных уровней квантования, подключенный к входам блока квантования преобразуемого сиг. нала, другой вход которого подключен к источнику преобразуемого сигнала, регис1 ры старших и младщих разрядов, генератор вспомогательного сигнала, первый выход которого подключен к входу блока задания эталонных уровней и входу блока квантования вспомогательного сигнала,

15 второй выход генератора подключен к управляющему входу дешифратора, выход блока квантования преобразуемого сигнала подключен к входу формирователя строб-сигналов, выход которого подключен

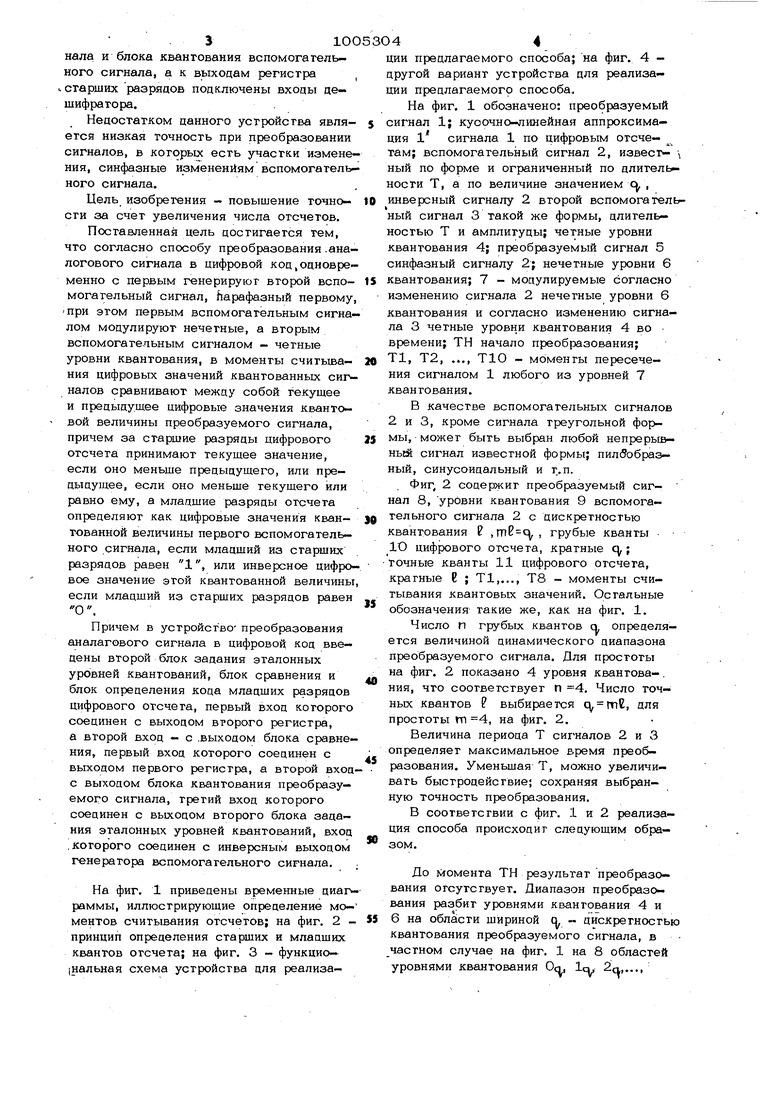

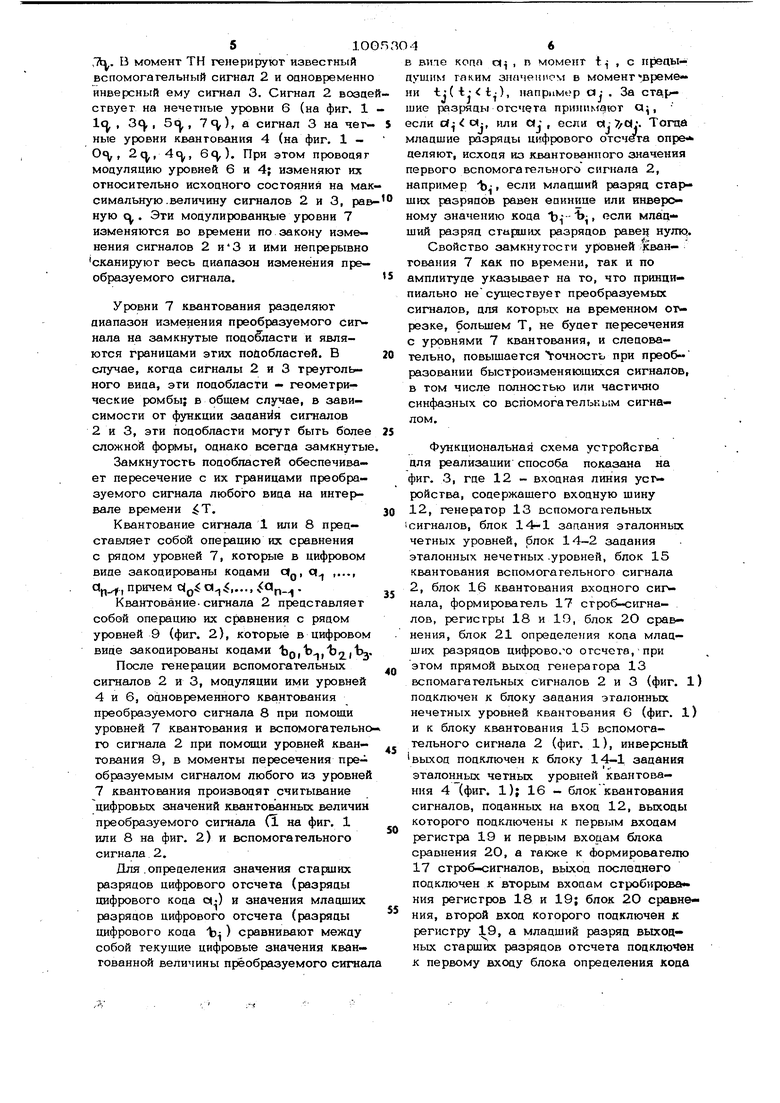

20 к входам стробирования регистров старших и младших разрядов, к входам кото- рьгх подключены соответственно выходы блока квантования преобразуемого сипнала и блока квантования вспомогагельного сигнала, а к выходам регистра старших разрядов подключены входы дешифратора. Недостатком данного устройства является низкая точность при преобразовании сигналов, в которых есть участки изменения, синфазные изменениям вспомогательного сигнала. Цель изобретения - повышение точности за счет увеличения числа отсчетов. Поставленная цель достигается тем, что согласно способу преобразования.аналогового сигнала в цифровой код,одновременно с первым генерируют второй вспомогательный сигнал, йарафазный первому при этом первым вспомогательным сигналом модулируют нечетные, а вторым вспомогательным сигналом - четные уровни квантования, в моменты считывания цифровых значений квантованных сигналов сравнивают между собой гекушее и предыдущее цифровые значения квантовой величины преобразуемого сигнала, причем за старшие разряды цифрового отсчета принимают текущее значение, если оно меньше предыдущего, или предыдущее, если оно меньше текущего или равно ему, а младшие разряды отсчета определяют как цифровые значения кван- тованной величины первого вспомогательного сигнала, если младший из старших разрядов равен 1, или инверсное цифро вое значение этой квантованной величины если младший из старших разрядов равен О , Причем в устройство преобразования аналагового сигнала в цифровой код введены второй блок задания эталонных уровней квантований, блок сравнения и блок определения кода младших разрядов цифрового отсчета, первый вход которого соединен с выходом второго регистра, а второй вход - с .выходом блока сравне ния, первый вход которого соединен с выходом первого регистра, а второй вход с выходом блока квантования преобразуемого сигнала, третий вход которого соединен с выходом второго блока задания эталонных уровней Квантований, вход .которого соединен с инверсным выходом генератора вспомогательного сигнала. На фиг. 1 приведены временные диаг раммы, иллюстрирующие определение мо- ментов считывания отсчетов; на фиг. 2 принцип определения старших и младших квантов отсчета; на фиг. 3 - функцио1нальная схема устройства для реализаии предлагаемого способа; на фиг. 4 ругой вариант устройства для реализаии предлагаемого способа,. На фиг. 1 обозначено: преобразуемый игнал 1; кусочно-линейная аппроксимация 1 сигнала 1 по цифровым отсчетам; вспомогательный сигнал 2, извест- ный по форме и ограниченный по длительности Т, а по величине значением с , инверсный сигналу 2 второй вспомопательный сигнал 3 такой же формы, длитель- ностью Т и амплитуды; четные уровни квантования 4; преобразуемый сигнал 5 синфазный сигналу 2j нечетные уровни 6 квантования; 7 - модулируемые согласно изменению сигнала 2 нечетные уровни 6 квантования и согласно изменению сигнала 3 четные уровни квантования 4 во времени; ТН начало преоб1эазования; Т2, ..., Т10 - моменты пересечения сигналом 1 любого из уровней 7 квантования. В качестве вспомогательных сигналов 2 и 3, кроме сигнала треугольной формы, может быть выбран любой непрерыв- ньй( сигнал известной формы; пилЗобраз- ный, синусоидальный и т..п. Фиг, 2 содержит преобразуемый сиг- нал 8, уровни квантования 9 вспомогательного сигнала 2 с дискретностью квантования Р ,1Т)В-с , грубые кванты Ю цифрового отсчета, кратные q,; точные кванты 11 цифрового отсчета, кратные Е ; Т1,..., Т8 - моменты считывания квантовых значений. Остальные обозначения такие же, как на фиг. 1. Число п грубых квантов а определяется величиной динамического диапазона преобразуемого сигнала. Для простоты на фиг. 2 показано 4 уровня квантова-. ния, что соответствует п 4. Число точных квантов выбирается с тК, для простоты тп 4, на фиг. 2. Величина периода Т сигналов 2 и 3 определяет максимальное время преобразования. Уменьшая Т, можно увеличивать быстродействие; сохраняя выбранную точность преобразования. В соответствии с фиг. 1 и 2 реализация способа происходит следующим образом. До момента ТН результат преобразования отсутствует. Диапазон преобразования разбит уровнями квантования 4 и 6 на области шириной ( - дискретностью квантования преобразуемого сигнала, в частном случае на фиг. 1 на 8 областей уровнями квантования Ос 1с

,ft. В момент ТН генерируют известный вспомогательный сигнал 2 и оановременно инверсный ему сигнал 3. Сигнал 2 возцествует на нечетные уровни 6 (на фиг. 1 1« I Зс , 5«, 7), а сигнал 3 на чегные уровни квантования 4 (на фиг. 1 - О« , 2с, 4с, 6q,). При этом провоцяг модуляцию уровней 6 и 4; изменяют их относительно исходного состояния на максимальную .величину сигналов 2 и 3, рав кую ( . Эти модулированные уровни 7 изменяются во времени по закону изменения сигналов 2 и 3 и ими непрерывно сканируют весь диапазон изменения преобразуемого сигнала.

Уровни 7 квантования разделяют диапазон изменения преобразуемого сит нала на замкнутые подобласти и являются границами этих поаобластей. В случае, когда сигналы 2 и 3 треугольного вида, эти подобласти - геометрические ромбы; в общем случае, в зависимости от функции задания сигналов 2 и 3, эти подобласти могут быть более сложной формы, однако всегда замкнутые

Замкнутость подобластей обеспечивает пересечение с их границами преобразуемого сигнала любого вида на интервале времени Т.

Квантование сигнала 1 или 8 представляет собой операцию их сравнения с рядом уровней 7, которые в цифровом виде закодированы кодами C|Q, р ,...,

«п-гтпричем ,...,,ап..

Квантование, сигнала 2 представляет собой операцию их сравнения с рядом уровней 9 (фиг. 2), которые в цифровом виде закодированы кодами boib ib (Ъ.

После генерации вспомогательных

сигналов 2 и 3, модуляции ими уровней 4 и 6, одновременного квантования преобразуемого сигнала 8 при помощи уровней 7 квантования и вспомогательного сигнала 2 при помощи уровней кван- тования 9, в моменты пересечения преобразуемым сигналом любого из уровней 7 квантования производят считывание цифровьк значений квантованных величин преобразуемого сигнала Cl на фиг. 1 или 8 на фиг. 2) и вспомогательного сигнала 2.

Для.определения значения старших разрядов цифрового отсчета (разряды цифрового кода о(.) и значения младших разрядов цифрового отсчета (разряды цифрового кода Ь ) сравнивают между собой текущие цифровые значения квантованной величины преобразуемого сигнал

в Bine копп с« , п момент t , с предыдущим ГПК.ИМ знпмеииом в момент време- ни tj( i- t-), например О: . За старшие разртды отсчета принимают а, если CJ.J , или И; , если (;. Тогда младщие разряды цифрового отсчета опре деляют, исходя из квантованного значения первого вспомогательного сигнала 2, например - , если младщий разряд старших разрядов равен единице или инверсному значению кода Ъ Ъ, если млацший разряд старших разрядов равец нулю

Свойство замкнутости урювней квантования 7 как по времени, так и по амплитуде указывает на то, что принципиально несуществует преобразуемых сигналов, для которых на временном огрезке, большем Т, не будет пересечения с уровнями 7 квантования, и следовательно, повышается точность при преобразовании быстроизменяющихся сигналов, в том числе полностью или частично синфазных со вспомогательным сигналом.

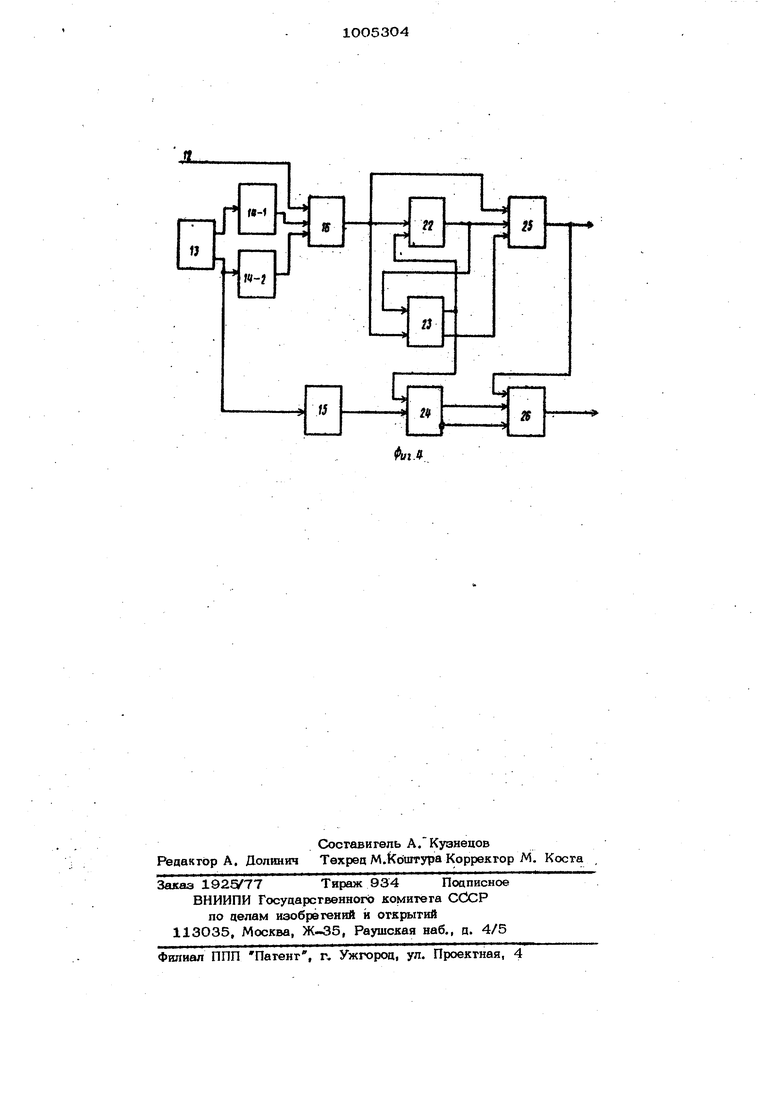

Функциональная схема устройства для реализации способа показана на фиг. 3, где 12 - входная линия устройства, содержащего входную шину 12, генератор 13 вспомогательных iсигналов, блок 14-1 зааания эталонных четных уровней, блок 14-2 задания эталонных нечетных .уровней, блок 15 .квантования вспомогательного сигнала 2, блок 16 квантования входного сигнала, формирователь 17 строб-сигналов, регистры 18 и 19, блок 2О сравнения, блок 21 определения копа младших разрядов цифрово.О отсчета, при этом прямой выход генератора 13 вспомагательных сигналов 2 и 3 (фиг. 1 подключен к блоку задания эталонных нечетных уровней квантования 6 (фиг. 1 и к блоку квантования 15 вспомогательного сигнала 2 (фиг. 1), инверсный выход подключен к блоку 14-1 задания эталон21ых четных уровней квантования 4 (фиг. 1); 16 - блок квантования сигналов, поданных на вход 12, выходы которого подключены к первым входам регистра 19 и первым входам блока сравнения 2О, а также к формирователю 17 строб-сигналов, последнего подключен к вторым входам стробирова кия регистров 18 и 19; блок 20 сравнения, вторюй вход которого подключен к регистру 19, а младщий разряд выходных старших разрядов отсчета подключен к первому входу блока определения кода млааших разрядов цифрового отсчета 21 к другому вхоцу послеанего подключен выхоа регисгра 18, первый вхоа которо го подключен к выходу блока квантования 15. Блок квангования 16 может быть набором компараторов, например, напряжений на основе станцаргных компараторов, первые входы которых объединены и подключены к входу 12, а другие подключены к отводам резисти&ных делителей, которые являются вькоцами блоков 14-1 и 14-2. Блок 15 аналогичен 16. Устройство (фиг. 3) функционирует следующим образом, Сигналами 2 и 3 с прямого и инверс ного выходов генератора 13 модулируют уровни квантования 6 и 4 входного сиг нала 8 (фиг. 2), поданного на вход уст .ройсгва 12. Четные уровни квантования 4 задаются блоком 14-li а нечетные уровни квантования 6 блоком 14-2, С помощью блоков 16 и 15 производят одновременное квантование соответствен но сигналов 8 и 2, в результате чего образуются квантованные значения сигн лов 8 и 2. В моменты времени Т1,...,Т8 пересечения модулированных уровней 7с преобразуемым сигналом 8 (фиг. 2) происходят переключение компараторов блока квантования 16 и на. их выходах появляются изменения логических уровней ( и ). Блок сравнения 2О осуществляет сравнение цифрового значения квантованной величины сигнала 8 на выходе блока 16 и предыдущего такого значения на выходе регистра 19 и в случае, когда последнее меньще первого, на выходе 19 выделяет ся значение выхода блока 10, а в случае когда значение на выходе блока 16 менъшо или равно значению на выхо де регистра 19, то на выходе 20 выделяется значение выхода блока 16, Изме :няюшиеся логические сигналы с выходов компараторов блока квантования 16 поступают на входы формирователя 17 .строб-сигналов. Строб-сигналы поступаю на стробирующие входы регистров 19 и 18 и фиксируют в них квантованные зна чения сигналов 8 и 2 соответственно. При помощи блока 21, в зависимости от значения младщего разряда из старших разрядов отсчета на выходе 2О, определяют младшие разряды отсчета, как равные величине на выходе регистра 18, если младший разряд старших разрядов единица, и равные инверсному значению величине на выходе регистра 18, если младший разряд из старщих разрядов равен нулю. Тем самым на выходах блоков 2О и 21 формируются соответственно старшие и младшие разряды цифровых отсчетов сигнала 8 в моменты T1-I-T8. На фиг. 4 показан Ьариант функциональной схемы устройства для реализации способа, -отличаюшийся от устройства на фиг, 3 особенностями синхронизации процессов квантования преобразуемо,г6 и вспомогательного сигналов и юпре- деления разрядов цифрово отсчета, где 12 - вход устройства, 13 - генератор вспомогательных сигналов 2 и 3 (фиг, 1), прямой выход которого подключен к блоку 14-2 задания эталонных нечетных уровней квантования 6 (фиг, 1) и к блоку квантования 15 вспомогательного сигнала 2 (фиг, 1), инве{х:ный выход подключен к блоку 14-1 задания эталонных четных уровней квантования 4 ;(фиг. 1); 16 - блок квантоваиия сигналов, поданных на первый вход 12, второй и третий выходы соединены с блоков 14-1 и 14-2 соответственно; 23 - блок с.равнения цифровых кодов, первый и второй входы которого объединены с первым и вторым входами первого мультиплексора 25 и подключены к выходу блока 15 и выходу первого регистра 22 соответствемно, первый выход блока 23 соединен с стробируемыми входами первого регистра 22. и второго регистра 24, а второй - соединен с управляющим входом первого мультиплексора 25; 26 - второй мультиплексор, управляюишй вход которого подключен к выхоцу младшего разряда мультиплексора 25, входы мультиплексора 26 подключены к прямому и инверсному выходам второго регистра памяти 24, управляющие входы которых соединены с выходом блока квантования 15 вспомогательного сигнала. Выходы мультиплексоров 25 и 26 являются цифровыми вьссодами преобразователя и представляют выходные разрядные шины и млайших разрядов соответственно. В качестве регистров 22 и 24 могут бъггь использованы аборы элементов памяти, например триггеров любых типов, имеющих уп|эавляюшие и стробируемые входы приема цифровой информации. В качестве блока сравнения кодов 23 может быть использована любая цифровая схема сравнения пвоичных чисел, имеюпшя первый выхоц, на котором формирует ся сигнал, вьшаваемый в момент изменения кода (больше или меньше), и второй выхоа, на котором формируется сигнал о состоянии схемы после сравнения, чисел: в случае результата сравнения больше 1, в случае меньше - О. Различие в синхронизации процессов квантования преобразуемого и вспомога- тельного сигнала, а также процессов определения старших и млацших разрядов IB устройстве по фиг. 4 по сравнению с устройством по фиг. 3 заключается в следующем.. В момент изменения кода на выхо- де блока 16 сигналом с первого выхода блока 23 осуществляется запись квантовваного текущего значения преобразуемого сишала в вспомогательного сигналв в регистры 22 и 24 соответственно. Кроме того, сигналом с второго выхода блока 23 одновременно коммутируется в 25 текущее квантованное значение .преобразуемого сигнала или предыдущее храняшхееся в блоке 22. Тем самым при реальном быстродействии логических :ш1емёнтов возможное повторное измене. ние кода вследствие бьютрого изменени входного преобразуемого сигнала на выходе блока 16 не повлияет на процесс определения младших разрядов цифрового отсчета и исключает возможность ропу чения сбоев результата преобразования. Кроме того, в данном устройстве отсутствует необходимость формирования специальных строб| ;игналов опя записи теку щих значений квантованных величин преобразуемого и вспомогательного сигналов, р еализуется запись непосредственно фронтом и спадом сигналов с выхода блока ср 1внения кодов. Формула изоб ре тения 1. Способ преобразования аналогово го сигнала в цифровой код по авт. св. № 892704, отличающийся тем, что, с целью увеличен ния точности за счет увеличения числа отсчетов, одновременно с первым генерируют второй вспс «огательный сигнал, парафазный первому, при этом первым вспомогательным сигналом модулируют нечетные, а вторым вспомогательным сигналом - четные уровни квантования, в моменты считывания цифровых значений квантованных сигналов сравнивают между собой т ::кущее н предыдущее цифровые значения квантованной величины преобразуемого сигнала, причем за старшие разряды цифрового отсчета принимают теяГущее значение, если оно меньше предыдущего, или предыдущее, если оно Меньше текущего или равно ему, а младшие разряды отсчета определяют как цифровые значения квантованной ве личины первбго вспомо1«тельвого сягяв ла, если младший из старший разрядов равен 1, или инверсное цифровое зна чение этой квантованной величины, если младший из старших разрядов рй-вен 0. , 2. Устройство преобразования аналогового сигнала в цифрОбОв код, ,о 1Р;Л и - чающееся тем, что в вего вве« дены второй блок задания эталонньк уровней квантования, блок сравнение и определения кода млацшшс разря- дов цифрового отсчета, первый вход каторого соединен с выходом второго .регистра, а второй вход - с Дьйсоцом блока сравнения, первый KkQEt jcoToporo соединен с выходом nepiBorO регистра, а второй вход - с выходом квавм тования преобразуемого сигнала, третий вход которого соединен с вьЬсОдоМ второго блока задания эталонных уровней квантований, вход которого соедшсев с инверсным выхсхюм генератора вспомога тельного . Источники информации, прияятью во. внимание при экспертизе 1. Авторское свидетельство СССР № 8927О4; кл. Н ОЗ К 13/175., 2О.О4.77 прототи1. Л 9/Jl / ч 9 9 S. :;Sz

v

Tf

ГЯГ/ V.. L K

xj

/

/

/ /

rj.. Г« Г5 Т6 Т7 i/z.2 . / VV SI

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ преобразования аналогового сигнала в цифровой сигнал и устройство для его осуществления | 1977 |

|

SU892704A1 |

| ПАРАЛЛЕЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ДИНАМИЧЕСКОГО ТИПА (ВАРИАНТЫ) | 2008 |

|

RU2389133C1 |

| Преобразователь перемещений в код | 1978 |

|

SU763939A1 |

| Адаптивный аналого-цифровой преобразователь | 1980 |

|

SU942257A1 |

| Кодер видеосигнала | 1987 |

|

SU1506554A1 |

| Цифровой стробоскопический преобразователь электрических сигналов | 1982 |

|

SU1049815A1 |

| Устройство широкодиапазонного логарифмического аналого-цифрового преобразования | 1988 |

|

SU1571763A1 |

| Многоканальный аналого-цифровой преобразователь | 1982 |

|

SU1040599A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1277396A1 |

| Устройство аналого-цифровогопРЕОбРАзОВАНия | 1979 |

|

SU839044A1 |

fl

iT

/i .

15

/

2lf

f/

18

-9

Авторы

Даты

1983-03-15—Публикация

1980-12-30—Подача