Изобретение относится к вычислительной технике и технике передачи изображений и может быть использовано в системах цифровой передачи телевизионных сигналов, например, в спутниковых системах.

Цель изобретения - повышение точности кодера.

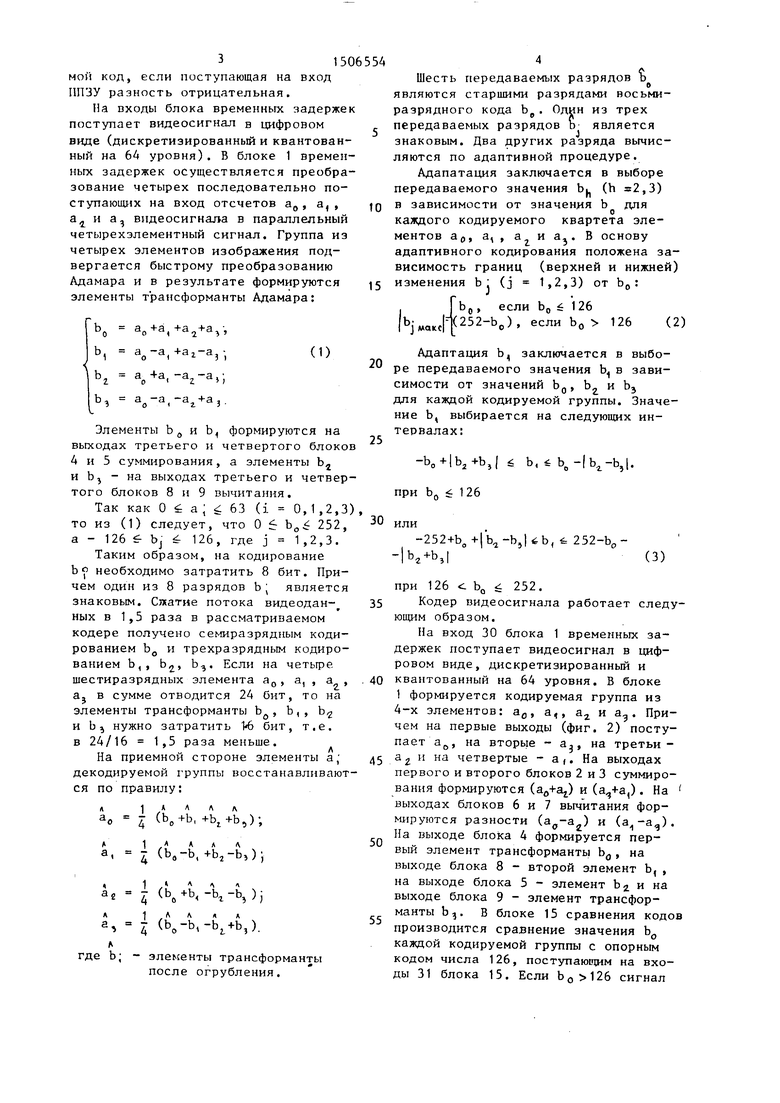

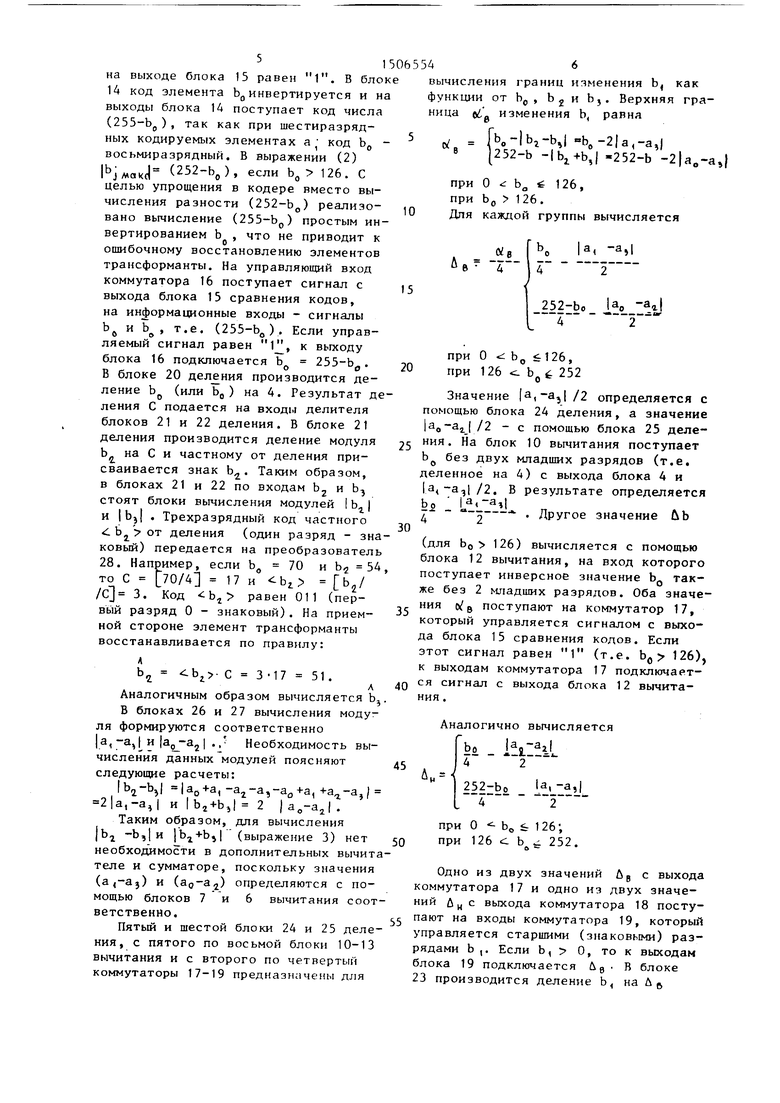

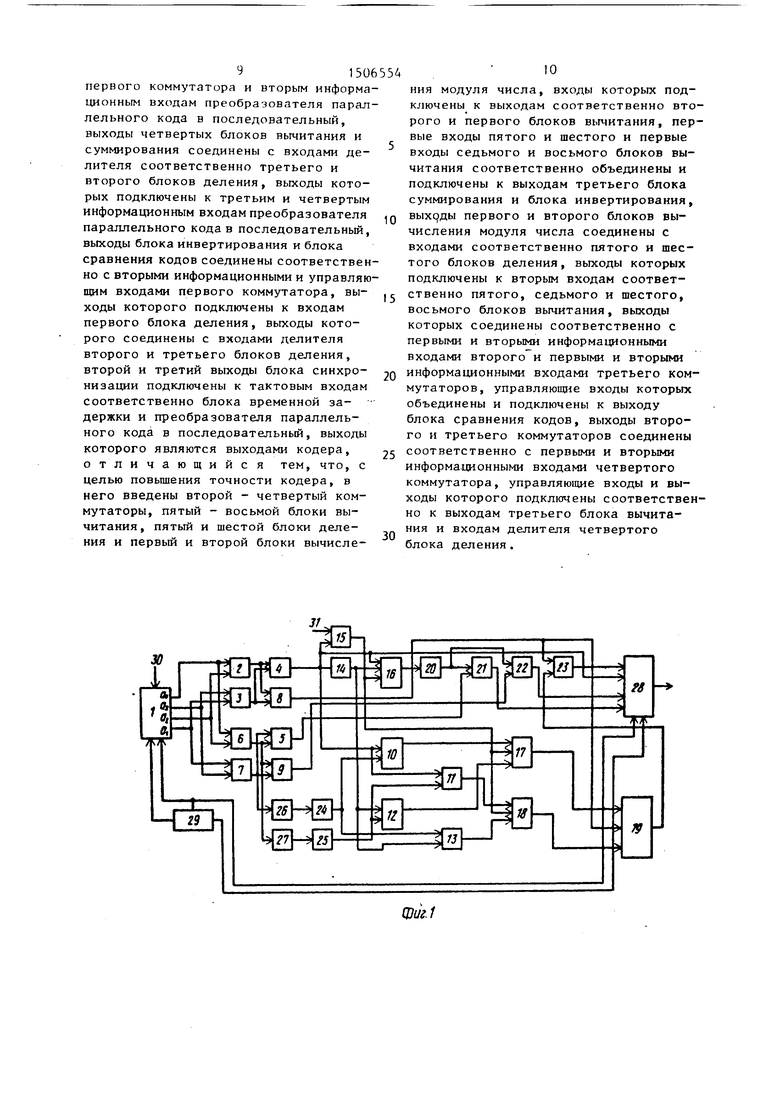

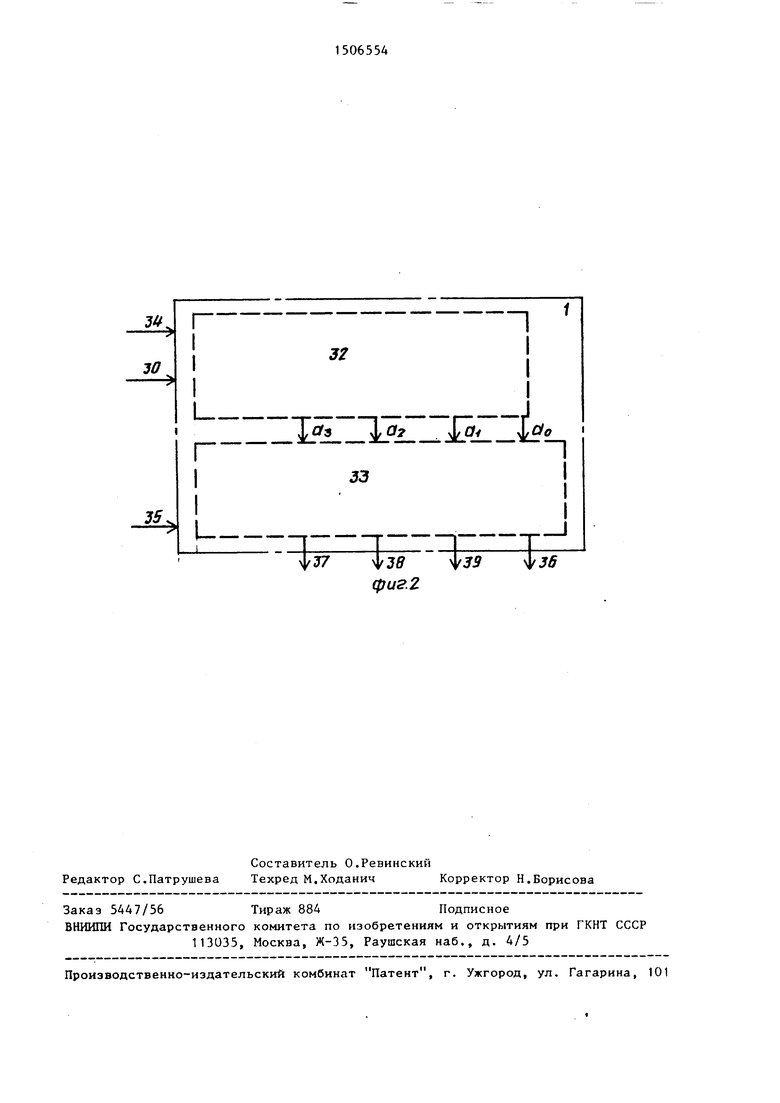

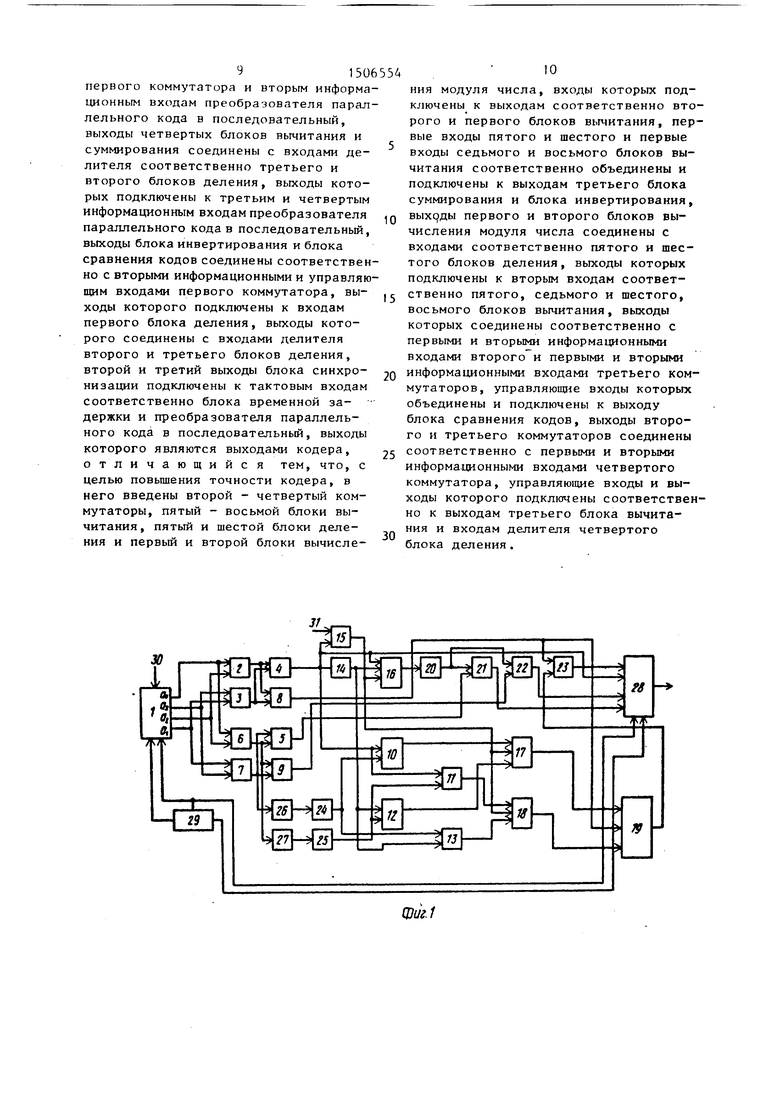

На фиг. 1 приведена функциональная схема кодера видеосигналаi на фиг. 2 - блок временных задержек.

Кодер видеосигнала содержит блок 1 временных задержек, первый - четвертый блоки 2-5 суммирования, первый - восьмой блок 6-13 вычитания, блок 14 инвертирования, блок 15 сравнения кодов, первый - четвертый коммутаторы 16-19, первыГ - шестой блоки 20-25 деления, первый и второй блоки 26 и 27 вычисления модуля числа, преобразователь 28 параллельного кода в последовательный и блок 29 синхронизации. На фиг. 1 обозначены информационные входы 30 и входы 31 опорного кода.

Блок 1 временной задержки может быть выполнен (фиг. 2) на регистре 32 сдвига и буферном регистре 33.

На фиг. 2 обозначены тактовый вход 34, вход 35 синхронизации и первые - четвертые выходы 36-39.

Блоки 26 и 27 вычисления модуля можно реализовать на программируемых тту. осуществляющих преобразование дополнительного кода разности в пряел

о

Од 01

СП

413

3150655А

мой код, если поступающая на вход ППЗУ разность отрицательная.

На входы блока временных задержек поступает видеосигнал в цифровом виде (дискретизированный и квантованный на 6А уровня). В блоке 1 временных задержек осуществляется преобразование четырех последовательно поступающих на вход отсчетов а

о

Ч

а и

a.j видеосигнала в параллельный четырехэлементный сигнал. Группа из четырех элементов изображения подвергается быстрому преобразованию Адамара и в результате формируются элементы т рансформанты Адамара:

bo а„+а,,,

Ь,,-1-а,-а,,,;

.,.

Элементы b и Ь,

формируются на выходах третьего и четвертого блоков 4 и 5 суммирования, а элементы Ь и Ь - на выходах третьего и четвертого блоков 8 и 9 вычитания.

Так как О 6 а ; 63 (i 0,1,2,3) то из (1) следует, что О : b(,i 252, а - 126 bj 126, где j 1,2,3.

Таким образом, на кодирование Ь необходимо затратить 8 бит. Причем один из 8 разрядов b является знаковым. Слатие потока видеодан- ных в 1,5 раза в рассматриваемом кодере получено семиразрядным кодированием Ьд и трехразрядным кодиро- b rt , b а rt а. . а

ванием Ь,, Ь, Ь,. Если на четьфе

шестиразрядных элемента а, а, , а , а. в сумме отводится 2А бит, то на элементы трансформанты Ь, Ь,, Ъ и Ь нужно затратить 1 бит, т.е. в 24/16 1,5 раза меньше.

На приемной стороне элементы а, декодируемой группы восстанавливаются по правилу:

(Ь„+ь,+b,+b,);

1 л л А Л

Т (b,-b, +b,-b,))

, ) А л л

аг Ч- -Ьг-Ц);

А IА А Л Л

д(Ь„-Ь,,).

где Ь; - элегЕенты трансформанты после огрубления.

5

Шесть передаваемых разрядов Ъ являются старшими разрядами восьмиразрядного кода bj. Один из трех передаваемых разрядов Ь- является знаковым. Два других разряда вычисляются по адаптивной процедуре.

Адапатация заключается в выборе передаваемого значения bj (h 2,3)

в зависимости от значения Ь для

о

каждого кодируемого квартета элементов а, а,, а и а. В основу адаптивного кодирования положена зависимость границ (верхней и нижней) изменения Ь (j 1,2,3) от

jbj, если bo 6 126 |bj J(232-b,), если bo 126 (2)

0

5

5

0

5

0

5

0

Адаптация Ь, заключается в выборе передаваемого значения Ц в зависимости от значений bg, Ь- и Ь, для каждой кодируемой группы. Значение Ь, выбирается на следующих интервалах:

-bo-t-|b,+b,( 6 Ь, (,l. при bo 126

или

-252+Ь„+|Ь -Ь,иЬ,б252-Ь,- -|Ьг+Ь,|(3)

при 126 1 Ц 252.

Кодер видеосигнала работает следующим образом.

На вход 30 блока 1 временных задержек поступает видеосигнал в цифровом виде, дискретизированный и квантованный на 64 уровня. В блоке 1 формируется кодируемая группа из 4-х элементов: а, а,, а. Причем на первые выходы (фиг. 2) поступает а,, на вторые - а, на третьи - а 2 и на четвертые - а,. На выходах первого и второго блоков 2 и 3 суммирования формируются () и (,). На выходах блоков 6 и 7 вычитания формируются разности () и (). Па выходе блока 4 формируется первый элемент трансформанты Ьд, на выходе блока 8 - второй элемент Ь,, на выходе блока 5 - элемент b-j и на выходе блока 9 - элемент трансформанты Ь. В блоке 15 сравнения кодов производится сравнение значения Ь каждой кодируемой группы с опорным кодом числа 126, поступающим на входы 31 блока 15. Если сигнал

на выходе блока 15 равен 1. В блок 14 код элемента Ь инвертируется и на выходы блока 14 поступает код числа (255-Ьр) , так как при шестиразрядных кодируемых элементах а код Ь,, - восьмиразрядный. В выражении (2) |bJM3Kcl (252-Ь„), если Ь, 126. С целью упрощения в кодере вместо вычисления разности (252-Ьд) реализовано вычисление (255-Ьр) простым инвертированием b , что не приводит к ошибочному восстановлению элементов трансформанты. На управляющий вход коммутатора 16 поступает сигнал с выхода блока 15 сравнения кодов, на информационные входы - сигналы Ь и Ь , т.е. (255-Ьд). Если управляемый сигнал равен 1, к выходу блока 16 подключается Ь 255--Ъд. В блоке 20 деления производится деление Ъ (или Ьд) на 4. Результат деления С подается на входы делителя блоков 21 и 22 деления. В блоке 21

вычисления границ изменения Ь, как функции от Ьр , bj и Ь,. Верхняя граница ei изменения Ь, равна

сх:,

bo-lb -b,| b,-2|a,-a,)

J252-b ,| «252-b -2|а„-а,|

при О Ь„ 126,

при Ьд 1 26.

Для каждой группы вычисляется

15

приО Ьд ,

при 126 -Ь 252

Значение |(э,| /2 определяется с помощью блока 24 деления, а значение /2-е помощью блока 25 деле

| название | год | авторы | номер документа |

|---|---|---|---|

| Кодер видеосигнала | 1989 |

|

SU1667256A2 |

| Устройство сжатия полосы частот видеосигнала | 1986 |

|

SU1394466A1 |

| Кодер сигнала изображения | 1989 |

|

SU1644389A1 |

| Устройство для кодирования и декодирования телевизионного сигнала | 1988 |

|

SU1649674A1 |

| Устройство для эффективного кодирования изображений | 1988 |

|

SU1559412A1 |

| Устройство передачи и приема цифрового телевизионного сигнала | 1987 |

|

SU1506592A2 |

| Устройтво передачи и приема цифрового телевизионного сигнала | 1986 |

|

SU1394465A1 |

| Дифференциальный импульсный кодер телевизионного сигнала | 1986 |

|

SU1424125A1 |

| Устройство для деления двоичных чисел | 1980 |

|

SU1048472A1 |

| Дифференциальный импульсный кодер телевизионного сигнала | 1987 |

|

SU1481900A2 |

Изобретение относится к вычислительной технике и технике передачи изображений. Его использование в системах (например спутниковых) цифровой передачи телевизионных сигналов позволяет повысить точность кодера. В кодере осуществляются быстрое преобразование Адамара для четырех последовательных отсчетов цифрового видеосигнала и адаптивное кодирование полученных элементов трансформанты. При этом за счет выбора значения второго элемента в зависимости от значений остальных элементов интервал его квантования меньше, чем в прототипе, за счет чего и достигается повышение точности кодирования. 2 ил.

деления производится деление модуля 25 На блок 10 вычитания поступает b на С и частному от деления присваивается знак Ь. Таким образом, в блоках 21 и 22 по входам Ь и Ь, стоят блоки вычисления модулей и |bj| . Трехразрядный код частного

Ь без двух младших разрядов (т.е. деленное на 4) с выхода блока 4 и |а,-а,1/2. В результате определяется Ьо ,l

1 bj от деления (один разряд - зна30

. Другое значение

Ckb

(для Ьо 126) вычисляется с помощью блока 12 вычитания, на вход которого поступает инверсное значение Ь также без 2 младших разрядов. Оба значековый) передается на преобразователь

то С 70/4 17 и bi bj/

/С 3. Код Ь, равен 011 (пер- „„ поступают на коммутатор 17,

вый разряд О - знаковый). На прием- 35 р, управляется сигналом с выхода блока 15 сравнения кодов. Если этот сигнал равен 1 (т.е. Ь, ; 126), к выходам коммутатора 17 подключает- д ся сигнал с выхода блока 12 вычитаной стороне элемент трансформанты восстанавливается по правилу:

Аналогично вычисляется

Ди

Ьо 4

|3,-ai|

М.-1..

252-bo la, -а,|

b С 3 -17 51.

Аналогичным образом вычисляется b,. ния.

В блоках 26 и 27 вычисления модуля формируются соответственно |a,-aj и ( I . , Необходимость вычисления данных модулей поясняют д5 следующие расчеты:

Ibj-b | |ag+a, -а2-а,-ао+а, ,/ 2|а, и |bj-bb,| 2 ) .

Таким образом, для вычисления Ib b,| и (выражение 3) нет необходимости в дополнительных вычита- теле и сумматоре, поскольку значения (а,-Я}) и (aQ-aj) определяются с помощью блоков 7 и 6 вычитания соответственно. пают на входы коммутатора 19, который

Пятый и шестой блоки 24 и 25 деле- управляется старшими (знаковыми) раз- ния, с пятого по восьмой блоки 10-13 вычитания и с второго по четверть коммутаторы 17-19 предназначены для

50

при О Ьо г 126; при 126 .с b 252.

&

Одно из двух значений up с выхода коммутатора 17 и одно из двух значений Лц с выхода коммутатора 18 постурядами b ,. Если Ь, О, то к выходам блока 19 подключается Лд В блоке 23 производится деление Ь на Л

25 На блок 10 вычитания поступает

Ь без двух младших разрядов (т.е. деленное на 4) с выхода блока 4 и |а,-а,1/2. В результате определяется Ьо ,l

30

. Другое значение

Ckb

(для Ьо 126) вычисляется с помощью блока 12 вычитания, на вход которого поступает инверсное значение Ь также без 2 младших разрядов. Оба значе„„ поступают на коммутатор 17,

Аналогично вычисляется

Ьо 4

|3,-ai|

М.-1..

252-bo la, -а,|

пают на входы коммутатора 19, который

при О Ьо г 126; при 126 .с b 252.

&

Одно из двух значений up с выхода коммутатора 17 и одно из двух значений Лц с выхода коммутатора 18 постууправляется старшими (знаковыми) раз-

рядами b ,. Если Ь, О, то к выходам блока 19 подключается Лд В блоке 23 производится деление Ь на Л

или

Л„ и

трехразрядиый код «ib, передается в преобразователь 28 параллельного кода в последовательный, на выходе которого для каждого кодируемого блока из четырех шестиразряд ных элементов формируется шестнадцатиразрядное кодовое слово,т.е. осуществляется 1,5-кратное сжатие потока. Такое же сжатие достигается и при использовании известного кодера. В предлагаемом кодере точность rtpeo6- разования видеосигнала повышается за счет использования более эффективной стратегии квантования Ь(. Покажем это на примере. Пусть Ь г - Ь 10 и Ь, -5. Тогда С АО/4 10, Ц bj/C 2, b, b,/C 1. в прототипе : b, b /CJ О и на приемной стороне значение Ь приравнивается 0. В данном кодере для Ъ -5 «с О вычисляется значение (ь |), равное 10. Затем определяется С, 10/4 2 и, наконец Ьр Ь,/С, 2. На приемной стороне восстановленное

-

равно 4, что точнее, чем

значение

в известном кодере.

Для пояснения этого обстоятельства рассмотрим, в каких пределах мо1

жет изменяться мере.

Из (1) следует, что

в приведенном Ь, Ь, Ь, Ь.

20 20 20 20

10 5 10 S 10

.;

+ 10 S О

70 50 10 30

О

О

О Ь,

О Ь,

- 10 30

Совместное решение этих неравенств дает следующий интервал изменения by : 45

- 10 Ь,

Подставляя Ь , bj и b в (3), тот же самый интервал изменения Ь

получим ( : 50

- 40 (20 + 10)bbi 40 - (20 - -10), так как Ь 126, - 10 Ь, бЗО.

Т.е. вьфажение (3) является справедливым для любой кодируемой группы.

Из выражения (3) с (2) видно, что интервал изменения Ь, , зависящий от

Ь

меньше, чем интервал из- только от Ь„.

3

зависящий

5

to

15

20

25

30

35

40

в : 45

м 50

- .

. 55

-

Следовательно при переходе к шкале квантования Ь, зависящей от Ь, Ь и bj, интервал квантования уменьшается на величину

wL I b,t-bj |b,,+b,| . В предлагаемом кодере на квантование Ь, отводится столько же двоичных единиц, сколько и в известном кодере, но за счет того, что интервал квантования Ь меньше, чем в известном кодере, точность кодирования возрастает. В результате при восстановлении повышается качество изображений наклонных контуров и текстурных участков при том же самом коэффициенте сжатия потока. Формула изобретения

Кодер видеосигнала, содержащий блок временной задержки, инф рмацион- ные входы которого являются информационными входами кодера, первый - четвертый блоки суммирования, первый - четвертый блоки вычитания, первый - четвертый блоки деления, блок инвертирования, первый коммутатор, преобразователь параллельного кода в последовательный, блок синхронизации и блок сравнения кодов, первые входы которого являются входами опорного кода кодера, первый выход блока синхронизации соединен с входами синхронизации преобразователя параллельного кода в последовательный и блока временной задержки, первые и вторые выходы которого подключены к первьм входам соответственно первых и вторых блоков суммирования и вычитания, третьи и четвертые выходы блока временной задержки соединены с вторыми входами соответственно первых и вторых блоков суммирования и вычитания, выходы первого и второго блоков суммирования подключены соответственно к первым и вторым входам третьих блоков cyм иpoвaния и вычитания, выходы первого и второго блоков вычитания соединены соответственно с первыми и вторыми входами четвертых блоков суммирования и вычитания, выходы третьего блока вычитания подключены к входам делимого четвертого блока деления, выходы которого соединены с первыми информационными входами преобразователя параллельного кода в последовательный, выходы третьего блока суммирования подклю- чены к вторым входам блока сравнения кодов, входам блока инвертирования , первым информационным входам

1506

первого коммутатора и вторым информационным входам преобразователя параллельного кода в последовательный, выходы четвертых блоков вычитания и суммирования соединены с входами де- лителя соответственно третьего и второго блоков деления, выходы которых подключены к третьим и четвертым информационным входам преобразователя параллельного кода в последовательный, выходы блока инвертирования и блока сравнения кодов соединены соответственно с вторыми информационными и управляющим входами первого коммутатора, выходы которого подключены к входам первого блока деления, выходы которого соединены с входами делителя второго и третьего блоков деления, второй и третий выходы блока синхронизации подключены к тактовым входам соответственно блока временной задержки и преобразователя параллельного кода в последовательньй, выходы которого являются выходами кодера.

отличающийся тем, что, с целью повьшения точности кодера, в него введены второй - четвертый коммутаторы, пятый - восьмой блоки вычитания, пятый и шестой блоки деления и первый и второй блоки вычисле0

5А

0

5

0

10

ния модуля числа, входы которых подключены к выходам соответственно второго и первого блоков вычитания, первые входы пятого и шестого и первые входы седьмого и восьмого блоков вычитания соответственно объединены и подключены к выходам третьего блока суммирования и блока инвертирования, выходы первого и второго блоков вычисления модуля числа соединены с входами соответственно пятого и шестого блоков деления, выходы которых подключены к вторым входам соответственно пятого, седьмого и шестого, восьмого блоков вычитания, выходы которых соединены соответственно с первыми и вторыми информационными входами второго и первыми и вторыми информационными входами третьего коммутаторов, управляющие входы которых объединены и подключены к выходу блока сравнения кодов, выходы второго и третьего коммутаторов соединены соответственно с первыми и вторыми информационными входами четвертого коммутатора, управляющие входы и выходы которого подключены соответственно к выходам третьего блока вычитания и входам делителя четвертого блока деления.

фиг.2

| Цифровое кодирование телевизионных изображений./Под ред | |||

| И.И.Цук- кермана, М.: Радио и связь, 1981, с | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Методы передачи изображений./Под ред | |||

| У.К | |||

| Прэтта | |||

| М.: Радио и связь, 1983, с | |||

| Способ подготовки рафинадного сахара к высушиванию | 0 |

|

SU73A1 |

| IEEE Transactions on Conmunicati- on Technique, 1971, v | |||

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

| Приспособление для охлаждения газовых турбин | 1922 |

|

SU957A1 |

| Устройство сжатия полосы частот видеосигнала | 1986 |

|

SU1394466A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-09-07—Публикация

1987-10-06—Подача