Изобретение относится к автоматике, вычислительной, преобразовательной и измерительной технике и может быть использовано в различных устройствах (в том числе селективных, с преобразованием частоты) полуавтоматического и автоматического измерения и допускового контроля уровней напряжения, амплитудно-частотных характеристик в логарифмическом масштабе в широком динамическом диапазоне уровней с малой погрешностью и улучшенной разрешающей способностью.

Цель изобретения - расширение области применения за счет увеличения

динамического диапазона преобразуемых сигналов, уменьшение погрешности преобразования, увеличение разрешающей способности.

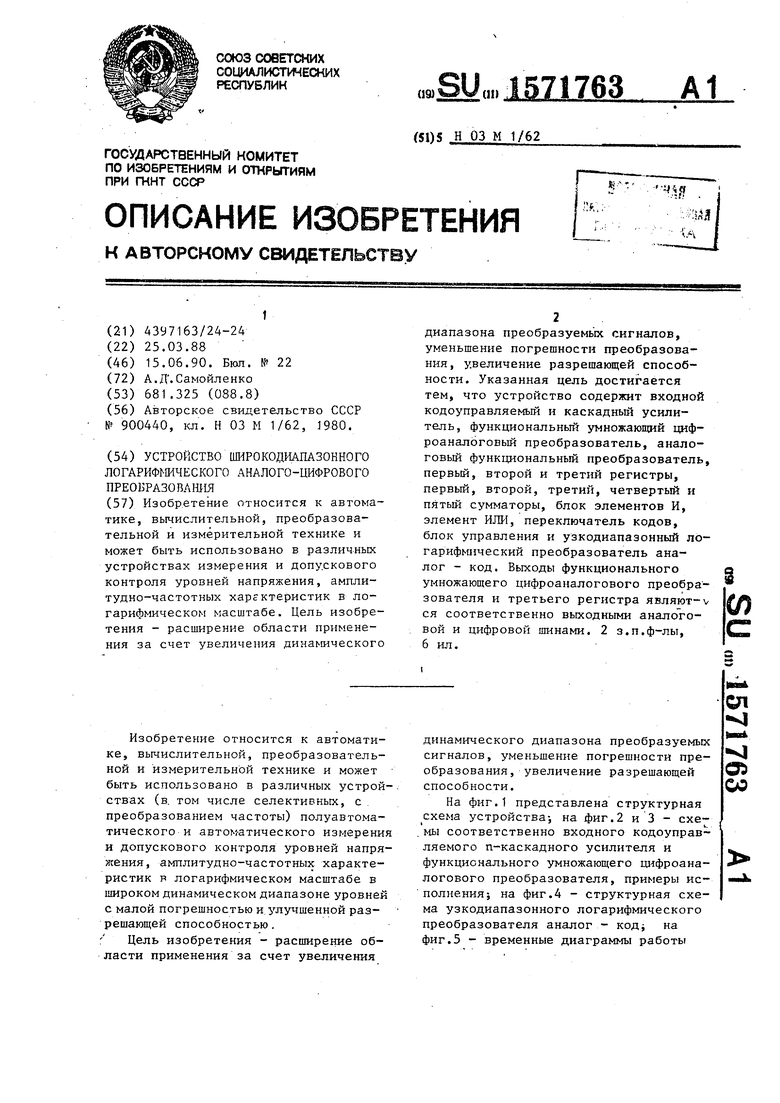

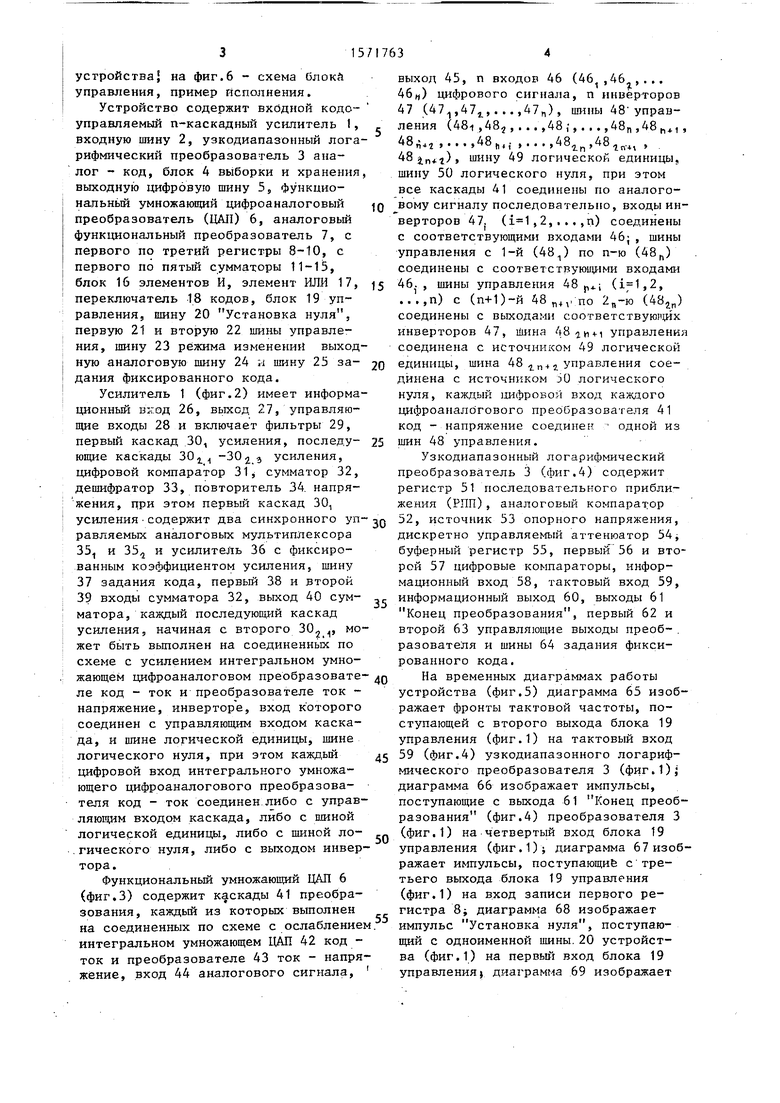

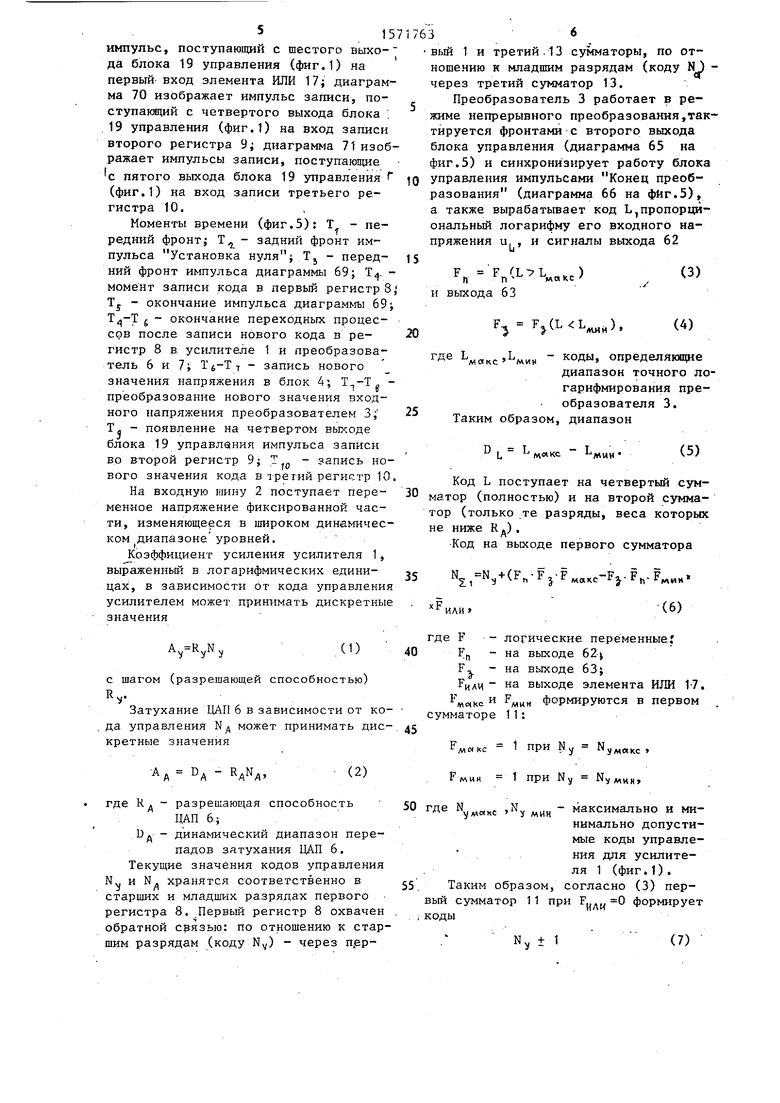

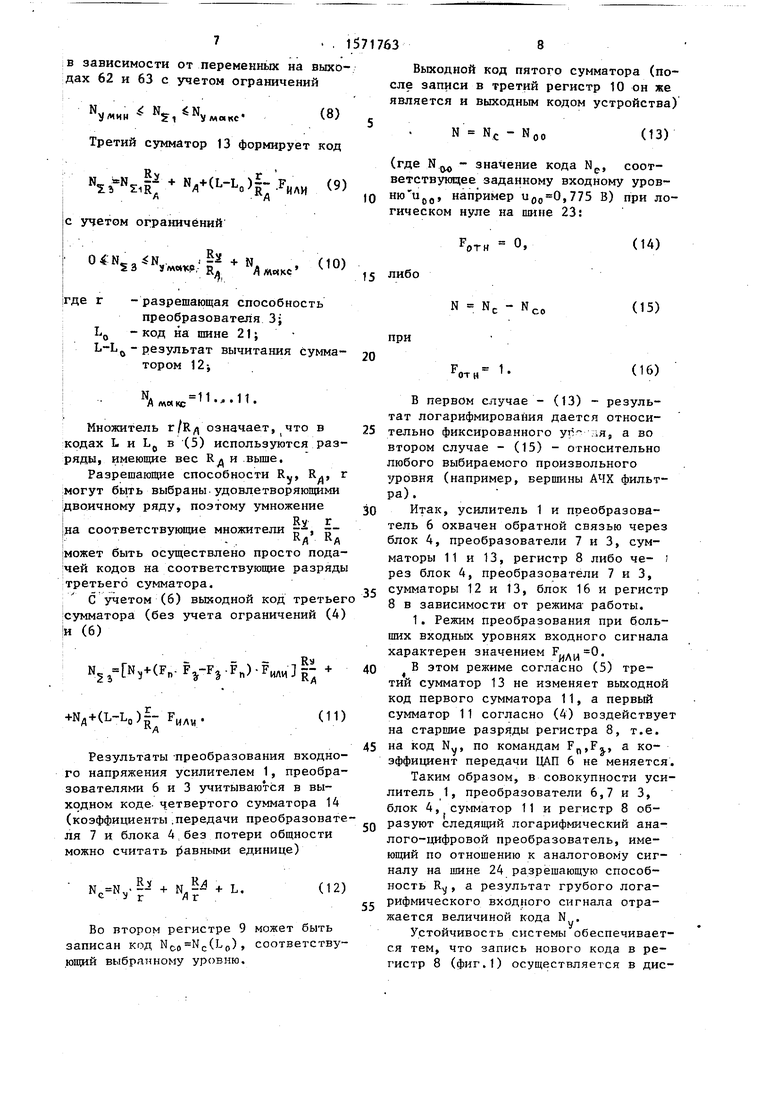

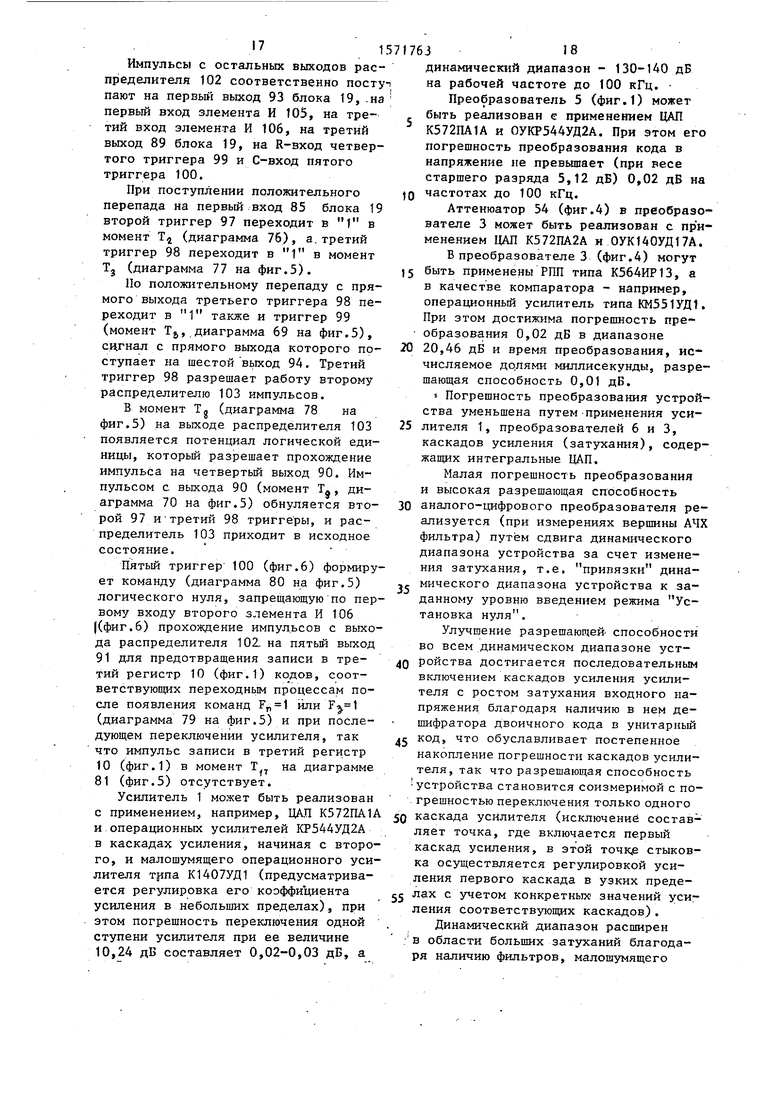

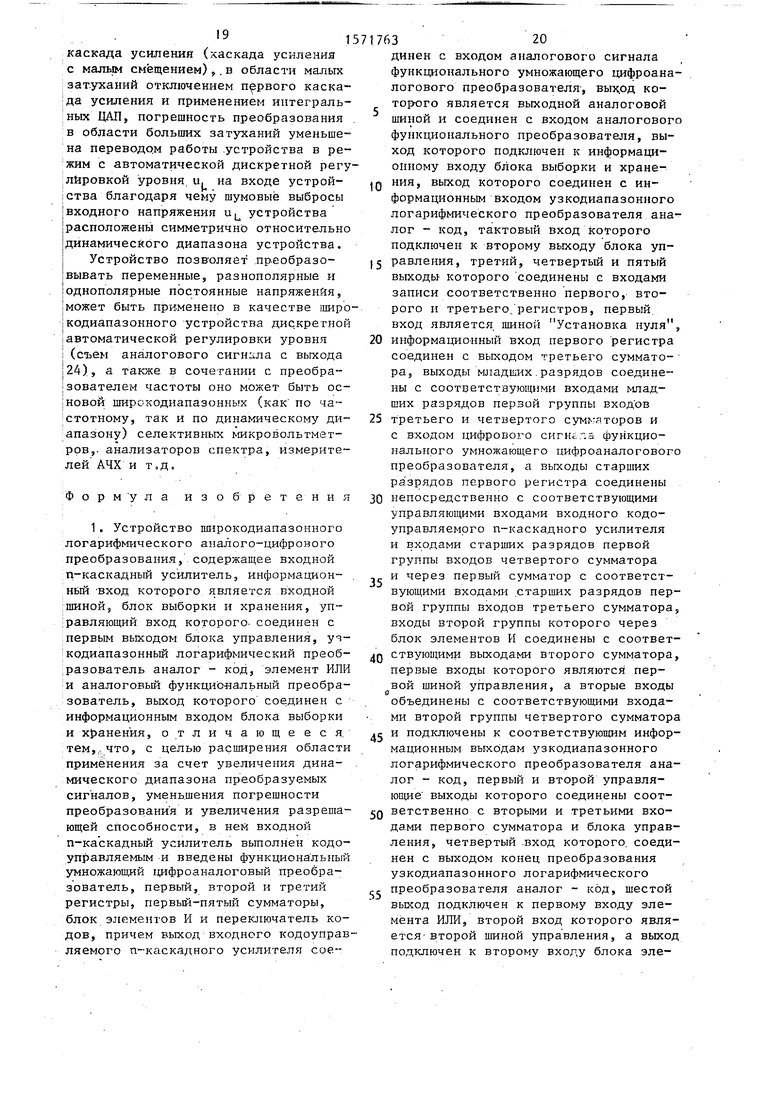

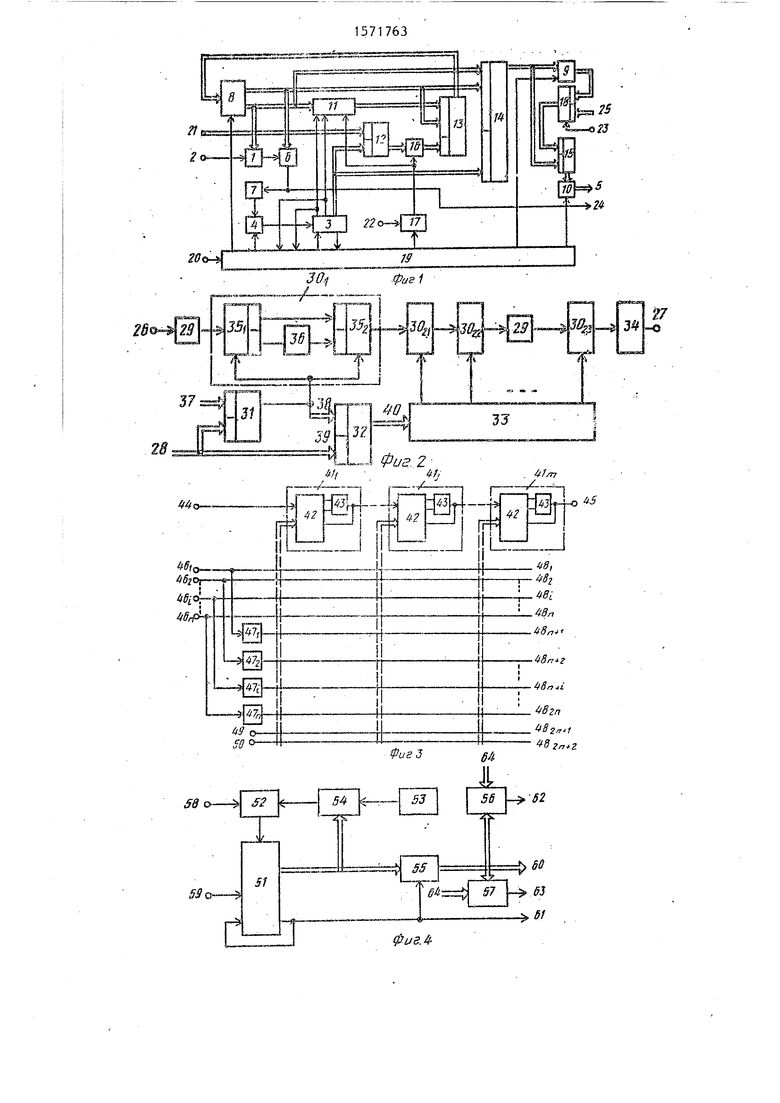

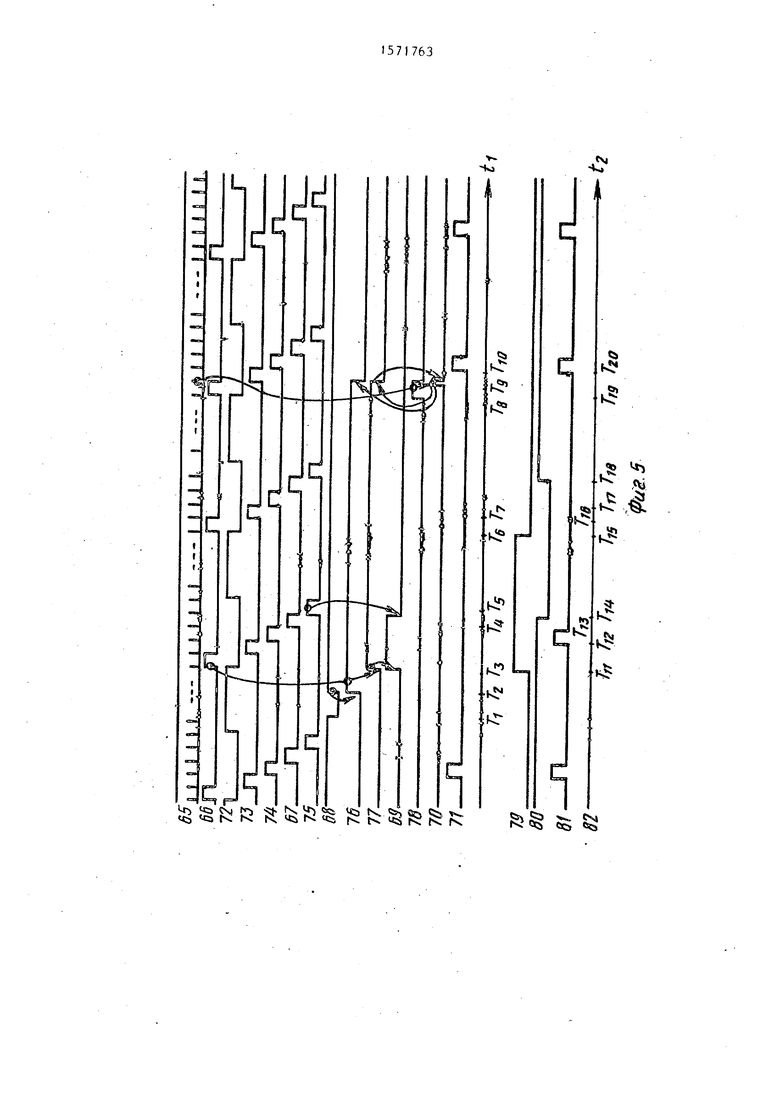

На фиг.1 представлена структурная схема устройства-, на фиг.2 и 3 - схемы соответственно входного кодоуправ- ляемого n-каскадного усилителя и функционального умножающего цифроаналогового преобразователя, примеры исполнения; на фиг.4 - структурная схема узкодиапазонного логарифмического преобразователя аналог - код; на фиг.5 - временные диаграммы работы

ел ч

И sl

СЈ СО

устройства на фиг.6 - схема блоки управления, пример исполнения.

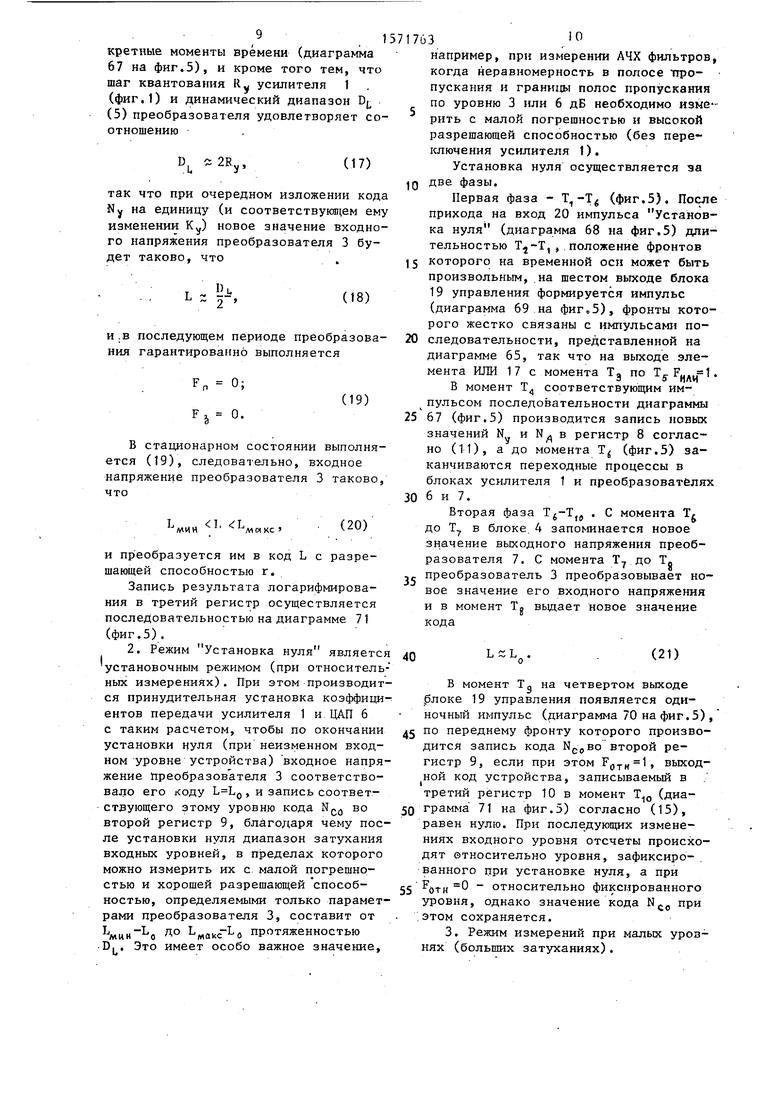

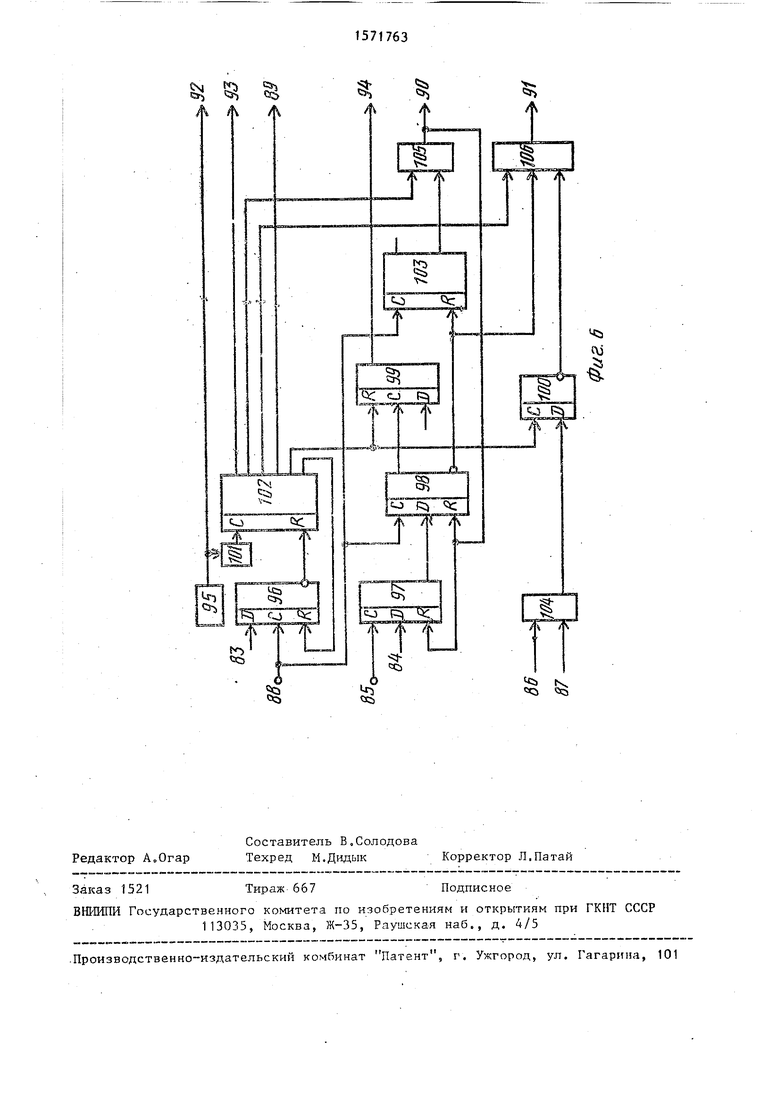

Устройство содержит входной кодо- управляемый n-каскадный усилитель 1, входную шину 2, узкодиапазонный логарифмический преобразователь 3 аналог - код, блок 4 выборки и хранения, выходную цифровую шину 55 Функциональный умножающий цифроаналоговый преобразователь (ЦАП) 6, аналоговый функциональный преобразователь 7, с первого по третий регистры 8-10, с первого по пятый сумматоры 11-15, блок 16 элементов И, элемент ИЛИ 17, переключатель 18 кодов, блок 19 управления, шину 20 Установка нуля, первую 21 и вторую 22 шины управления, шину 23 режима изменении выходную аналоговую шину 24 п шину 25 за- дания фиксированного кода.

Усилитель 1 (фиг.2) имеет информационный НУод 26, выход 27, управляющие входы 28 и включает фильтры 29, первый каскад 30, усиления, последу- ющие каскады 30г1 -3023 усиления, цифровой компаратор 31, сумматор 32, дешифратор 33, повторитель 34 напряжения, при этом первый каскад 30, усиления содержит два синхронного уп- равляемых аналоговых мультиплексора 35, и 35.J и усилитель 36 с фиксированным коэффициентом усиления, шину 37 задания кода, первый 38 и второй 39 входы сумматора 32, выход 40 сум- матора, каждый последующий каскад усиления, начиная с второго , может быть выполнен на соединенных по схеме с усилением интегральном умножающем цифроаналоговом преобразовате- ле код - ток и преобразователе ток - напряжение, инверторе, вход которого соединен с управляющим входом каскада, и шине логической единицы, шине логического нуля, при этом каждый цифровой вход интегрального умножающего цифроаналогового преобразователя код - ток соединен либо с управляющим входом каскада, либо с шиной логической единицы, либо с шиной ло- гического нуля, либо с выходом инвертора.

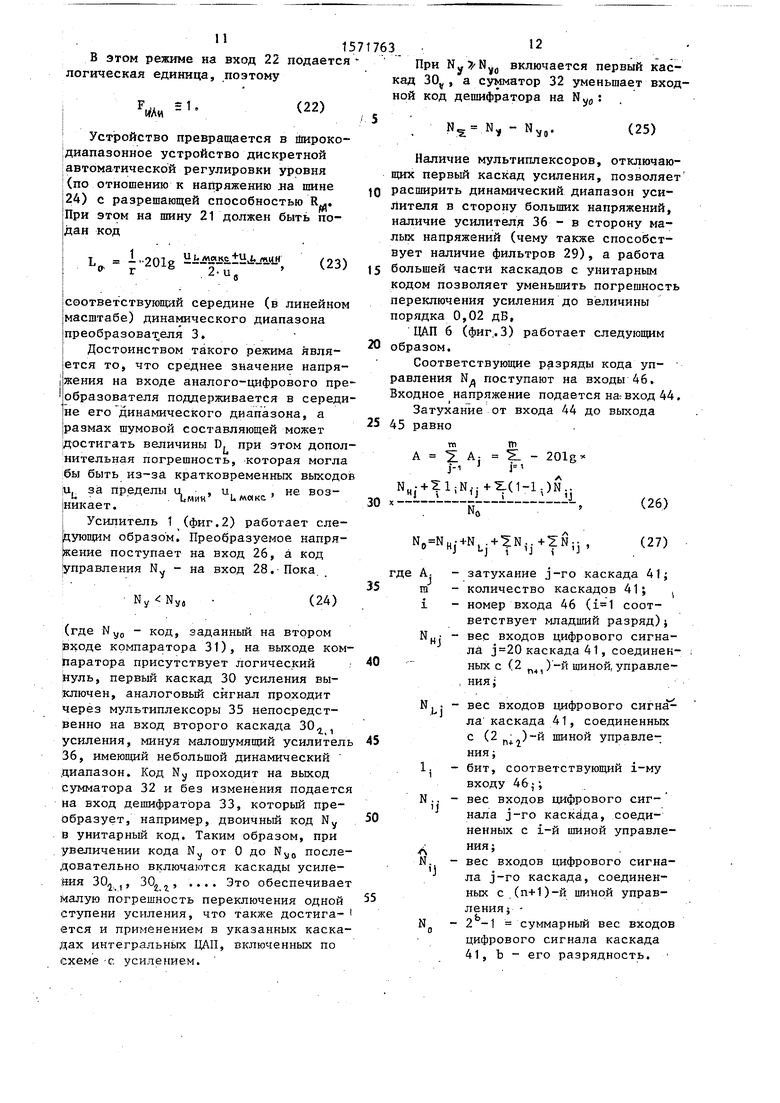

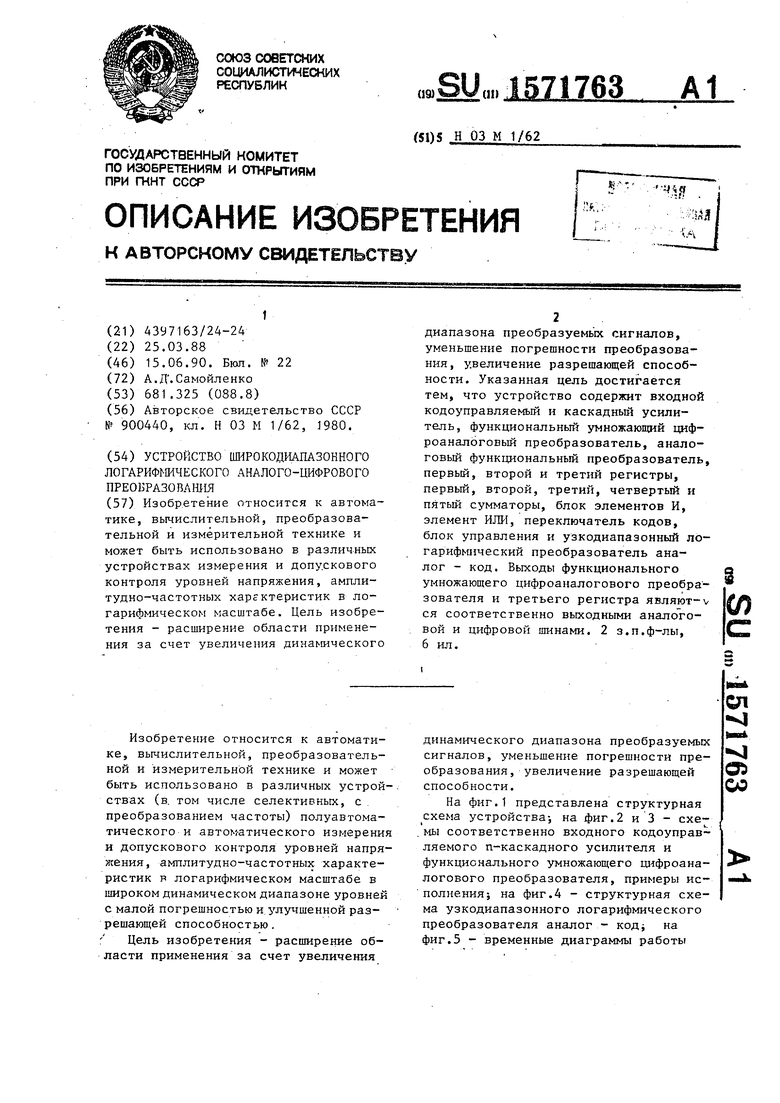

Функциональный умножающий ЦАП 6 (фиг.З) содержит каскады 41 преобразования, каждый из которых выполнен на соединенных по схеме с ослаблением интегральном умножающем ЦАП 42 код - ток и преобразователе 43 ток - напряжение, вход 44 аналогового сигнала,

выход 45, п входов 46 (461,46г,...

46н) цифрового сигнала, п инверторов

47(471,471,. ..,47П), шины 48 управления (48-, ,482, . ..,48;48n,48h + 1

48,,,48lnM ,

48in+i) шину 49 логической единицы, шину 50 логического нуля, при этом все каскады 41 соединены по аналого вому сигналу последовательно, входы инверторов 47, ( ,2, . .. ,п) соединены с соответствующими входами 46; , шины управления с 1-й (48л) по п-ю (48„) соединены с соответствующими входами 46 шины управления 48 pii (,2, ...,п) с (п+1)-й 48 „м, по 2,,-ю (48гп) соединены с выходами соответствующих инверторов 47, шина 48.jm-i управлени соединена с источником 49 логической единицы, шина 48гп+г управления соединена с источником jO логического нуля, каждый цифровой вход каждого цифроаналогового преобразователя 41 код - напряжение соединен одной из шин 48 управления.

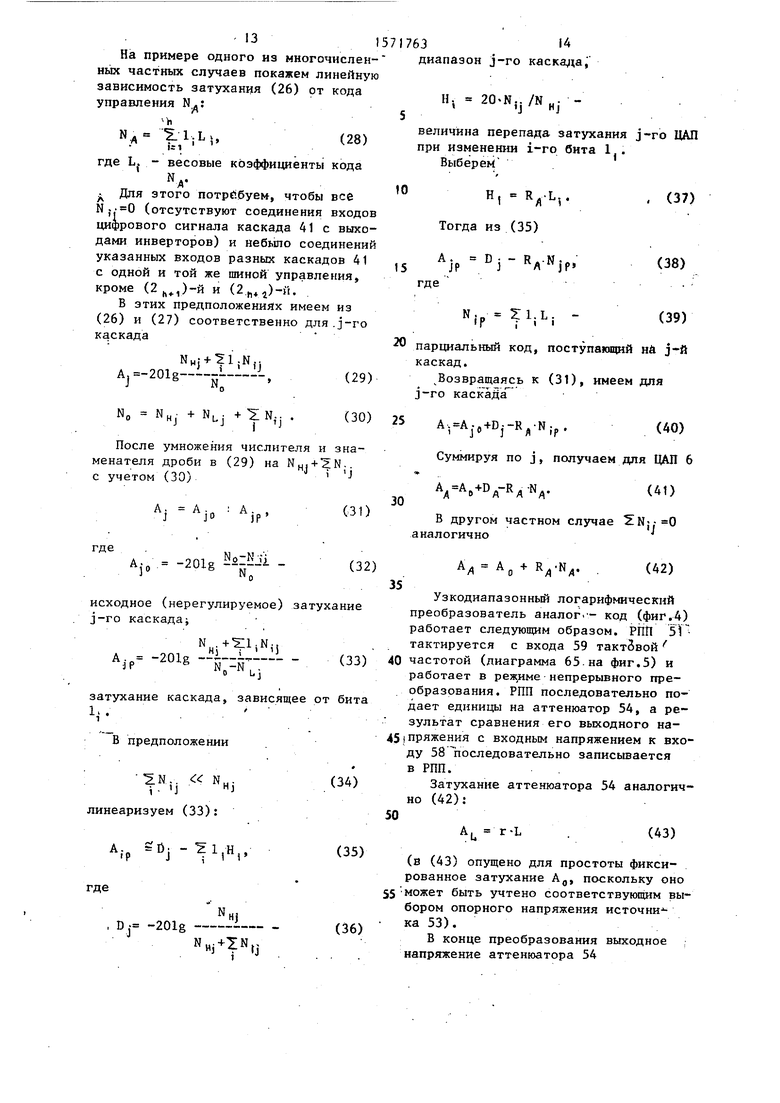

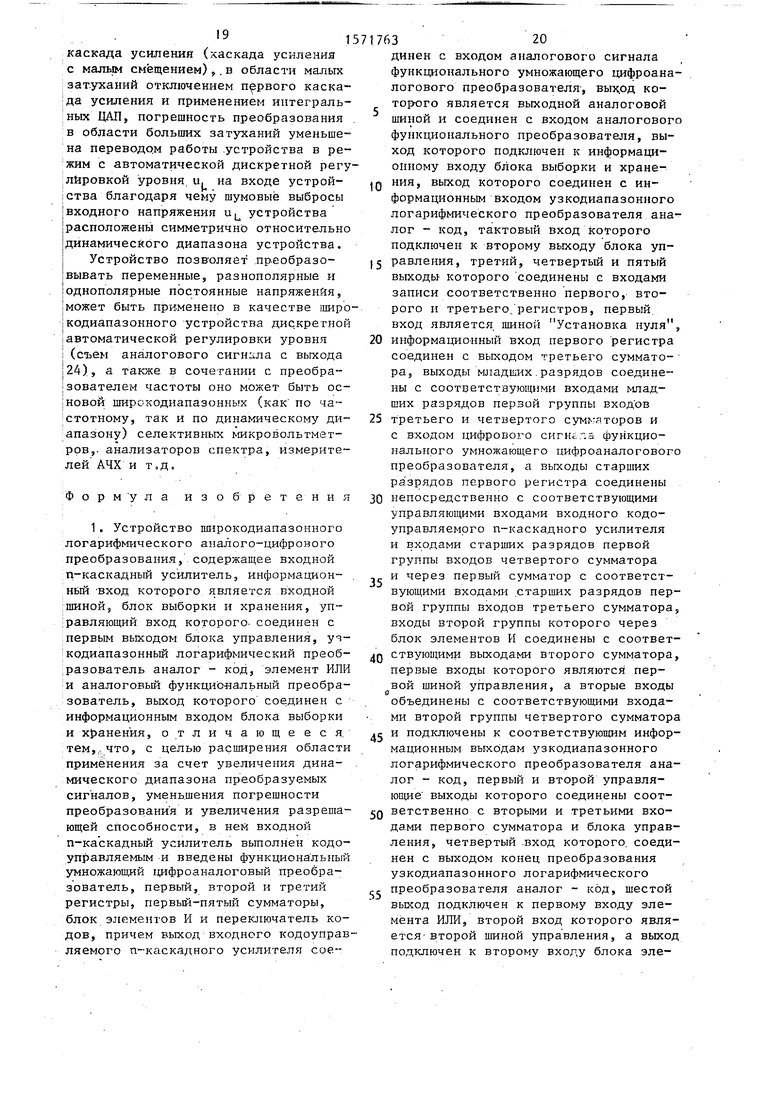

Узкодиапаэонный логарифмический преобразователь 3 (фиг.4) содержит регистр 51 последовательного приближения (РПП), аналоговый компаратор 52, источник 53 опорного напряжения, дискретно управляемый аттенюатор 54, буферный регистр 55, первый 56 и второй 57 цифровые компараторы, информационный вход 58, тактовый вход 59, информационный выход 60, выходы 61 Конец преобразования, первый 62 и второй 63 управляющие выходы преобразователя и шины 64 задания фиксированного кода.

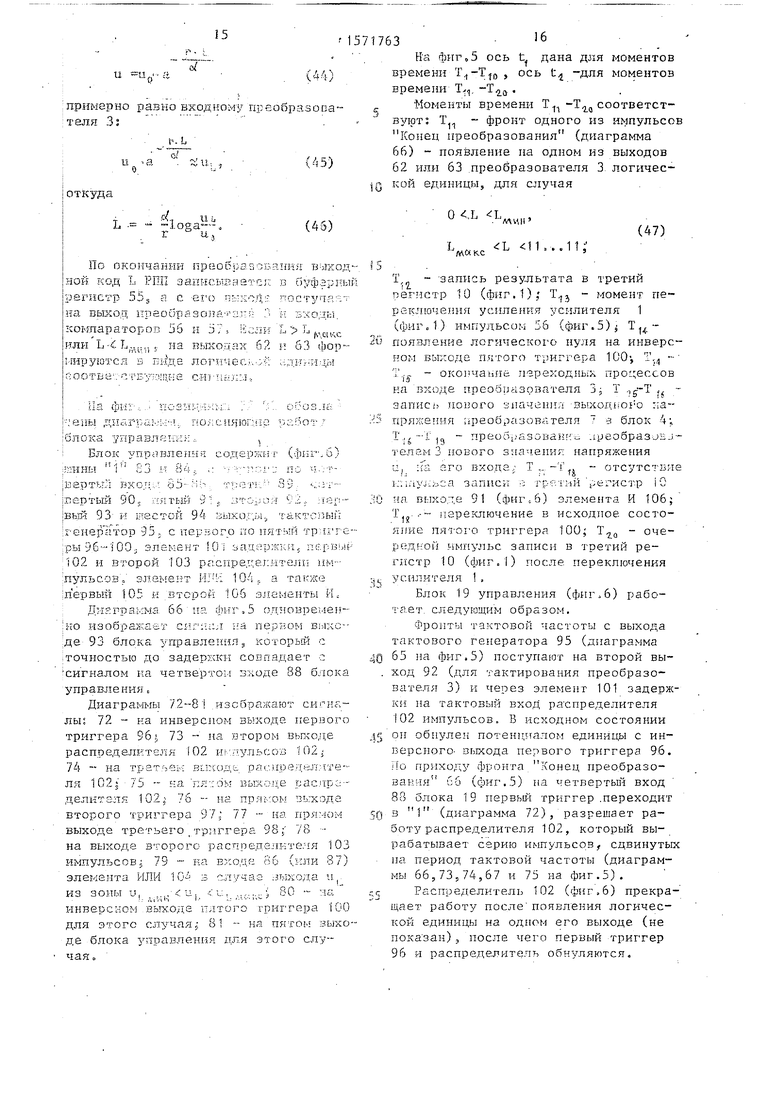

На временных диаграммах работы устройства (фиг.5) диаграмма 65 изображает фронты тактовой частоты, поступающей с второго выхода блока 19 управления (фиг.1) на тактовый вход 59 (фиг.4) узкодиапазонного логарифмического преобразователя 3 (фиг.1); диаграмма 66 изображает импульсы, поступающие с выхода 61 Конец преобразования (фиг.4) преобразователя 3 (фиг.1) на четвертый вход блока 19 управления (фиг.1); диаграмма 6 7 изображает импульсы, поступающие с третьего выхода блока 19 управления (фиг.1) на вход записи первого регистра 8; диаграмма 68 изображает импульс Установка нуля, поступающий с одноименной шины 20 устройства (фиг.1) на первый вход блока 19 управления} диаграмма 69 изображает

515

импульс, поступающий с шестого выхо- да блока 19 управления (фиг.1) на первый вход элемента ИЛИ 17; диаграмма 70 изображает импульс записи, поступающий с четвертого выхода блока 19 управления (фиг.1) на вход записи второго регистра 9; диаграмма 71 изображает импульсы записи, поступающие с пятого выхода блока 19 управления Г (фиг.1) на вход записи третьего регистра 10.

Моменты времени (фиг.5): Т - передний фронт; Тг - задний фронт импульса Установка Т3 - передний фронт импульса диаграммы 69; Т - момент записи кода в первый регистр 8, Т5 - окончание импульса диаграммы 69; - окончание переходных процессов после записи нового кода в регистр 8 в усилителе 1 и преобразователь 6 и 7; Т6-ТТ - запись нового значения напряжения в блок 4; - преобразование нового значения входного напряжения преобразователем 3, Т- - появление на четвертом выходе блока 19 управления импульса записи во второй регистр 9; Т Q - запись нового значения кода в третий регистр 10.

На входную миьу 2 поступает переменное напряжение фиксированной части, изменяющееся в широком динамическом диапазоне уровней.

Коэффициент усиления усилителя 1, выраженный в логарифмических единицах, в зависимости от кода управления усилителем може принимать дискретные значения

1763

вый 1 и третий 13 сумматоры, по отношению к младшим разрядам (коду Ю - через третий сумматор 13.

Преобразователь 3 работает в режиме непрерывного преобразования,тактируется фронтами с второго выхода блока управления (диаграмма 65 на фиг.5) и синхронизирует работу блока

jg управления импульсами Конец преобразования (диаграмма 66 на фиг.5), а также вырабатывает код L,пропорциональный логарифму его входного на

пряжения и, , и сигналы выхода 62

Fn

Fn(.

макс

(3)

и выхода 63

20

F3 .

(4)

где Ьмякс,ЬМИ1) - коды, определяющие диапазон точного логарифмирования преобразователя 3.

Таким образом, диапазон

Г) - Т Т

L ьмин

(5)

Код L поступает на четвертый сум- матор (полностью) и на второй сумматор (только те разряды, веса которых не ниже Кд) ,

Код на выходе первого сумматора

+ (Fh Fj FMaKC-F Fh Рмии

xF

или

(6)

| название | год | авторы | номер документа |

|---|---|---|---|

| Широкодиапазонный логарифмический аналого-цифровой преобразователь | 1988 |

|

SU1580557A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1996 |

|

RU2114501C1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU884127A1 |

| Устройство для измерения средней мощности огибающей узкополосного процесса | 1986 |

|

SU1325373A1 |

| Аналого-цифровой преобразователь | 1978 |

|

SU748863A1 |

| Логарифмический аналого-цифровой преобразователь | 1987 |

|

SU1481803A1 |

| Ультразвуковой дефектоскоп | 1989 |

|

SU1619169A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1589395A1 |

| Устройство для измерения оптической плотности изображения | 1982 |

|

SU1042046A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С ПЛАВАЮЩЕЙ ЗАПЯТОЙ | 1991 |

|

RU2007024C1 |

Изобретение относится к автоматике, вычислительной, преобразовательной и измерительной технике и может быть использовано в различных устройствах измерения и допускового контроля уровней напряжения, амплитудно-частотных характеристик в логарифмическом масштабе. Цель изобретения - расширение области применения за счет увеличения динамического диапазона преобразуемых сигналов, уменьшение погрешности преобразования, увеличение разрешающей способности. Указанная цель достигается тем, что устройство содержит входной кодоуправляемый и каскадный усилитель, функциональный умножающий цифроаналоговый преобразователь, аналоговый функциональный преобразователь, первый, второй и третий регистры, первый, второй, третий, четвертый и пятый сумматоры, блок элементов И, элемент ИЛИ, переключатель кодов, блок управления и узкодиапазонный логарифмический преобразователь аналог-код. Выходы функционального умножающего цифроаналогового преобразователя и третьего регистра являются соответственно выходными аналоговой и цифровой шинами. 2 з.п. ф-лы, 6 ил.

(D

с шагом (разрешающей способностью)

R

V

Затухание ЦАП 6 в зависимости от кода управления N может принимать дискретные значения

Ад Вд - КЛНЛ,

(2)

где К. - разрешающая способность

ЦАП 6,

Dfl - динамический диапазон перепадов затухания ЦАП 6. Текущие значения кодов управления

N

.. и N. хранятся соответственно в

j л

старших и младших разрядах первого регистра 8. Первый регистр 8 охвачен обратной связью: по отношению к старшим разрядам (коду Nv) - через ПЈргде F - логические переменные 40Fn - на выходе 62 &

F, - на выходе 63; Рилц - на выходе элемента ИЛИ 17. (KC и FMKH Формируются в первом сумматоре 11: 45

FWC.KC 1 при Ny N,MeiK,

FMHH 1 ПРИ Nv NVMMH,

где N акс ,Му мин - максимально и минимально допустимые коды управления для усилителя 1 (фиг.1).

Таким образом, согласно (3) первый сумматор 11 при F. 0 формирует

коды

ИЛИ

Nv ± 1

(7)

в зависимости от переменных на выходах 62 и 63 с учетом ограничений

«„„ N HNV«««c(8)

Третий сумматор 13 формирует код

+ V(L-LO)

лКА

S S:IR: T ил- чь ьо 5-.или (9)

с учетом ограничений

,&

53 меиФ Ј

г - разрешающая способность преобразователя 3;

L0 - код на шине 21;

результат вычитания сумматором 12-,

N,

А мм кс

Множитель г/Кд означает,|что в кодах L и LO в (5) используются разряды, имеющие вес Кд и выше.

Разрешающие способности К„, R, r могут быть выбраны удовлетворяющими двоичному ряду, поэтому умножение

на соответствующие множители

RЈ Г

V

R,

может быть осуществлено просто подачей кодов на соответствующие разряды третьего сумматора.

С учетом (6) выходной код третьег сумматора (без учета ограничений (4) и (6)

(FD. FrFrFn)-F

lЈ- +

ИЛИ J р .

RA

+N, + (L-L0) F

R,

ил«

(11)

Результаты преобразования входного напряжения усилителем 1, преобразователями 6 и 3 учитываются в выходном коде четвертого сумматора 14 (коэффициенты передачи преобразователя 7 и блока 4 без потери общности можно считать равными единице)

,.f- + N + L.

(12)

Во втором регистре 9 может быть записан кпд (L0), соответствующий выбранному уровню.

Выходной код пятого сумматора (после записи в третий регистр 10 он же является и выходным кодом устройства)

N Nc - N

оо

(13)

(где Nм - значение кода Мс, соответствующее заданному входному уров- Ю , например ,775 В) при логическом нуле на шине 23:

fOTH

О,

(14)

j 5 либо

N Nc - Nco

(15)

при

20

FOTH 1

(16)

5

0

5

0

5

0

В первом случае - (13) результат логарифмирования дается относительно фиксированного уг я, а во втором случае - (15) - относительно любого выбираемого произвольного уровня (например, вершины АЧХ фильтра) .

Итак, усилитель 1 и преобразователь 6 охвачен обратной связью через блок 4, преобразователи 7 и 3, сумматоры 11 и 13, регистр 8 либо че- ; рез блок 4, преобразователи 7 и 3, сумматоры 12 и 13, блок 16 и регистр 8 в зависимости от режима работы.

Таким образом, в совокупности усилитель 1, преобразователи 6,7 и 3, блок 4, сумматор 11 и регистр 8 образуют следящий логарифмический аналого-цифровой преобразователь, имеющий по отношению к аналоговому сигналу на шине 24 разрешающую способность Ry, а результат грубого логарифмического входного сигнала отражается величиной кода N.

Устойчивость системы обеспечивается тем, что запись нового кода в регистр 8 (фиг.1) осуществляется в дис,9157

кретные моменты времени (диаграмма 67 на фиг.5), и кроме того тем, что

шаг квантования R,

1

ky усилителя (фиг.1) и динамический диапазон DL (5) преобразователя удовлетворяет соотношению

D. s 2F.

(17)

так что при очередном изложении кода Ny на единицу (и соответствующем ему изменении Ку) новое значение входного напряжения преобразователя 3 будет таково, что

L

Ь

(18)

и в последующем периоде преобразования гарантированно выполняется

Fn 0;

(19)

Fs 0.

В стационарном состоянии выполняется (19), следовательно, входное напряжение преобразователя 3 таково, что

МИН Т ЛМХКС

(20)

и преобразуется им в код L с разрешающей способностью г.

Запись результата логарифмирования в третий регистр осуществляется последовательностью на диаграмме 71 (фиг.5).

U

З10

например, при измерении АЧХ фильтров, когда неравномерность в полосе пропускания и границы полос пропускания по уровню 3 или 6 дБ необходимо измерить с малой погрешностью и высокой разрешающей способностью (без переключения усилителя 1).

Установка нуля осуществляется за

две фазы.

Первая фаза - Т,, -16 (фиг.5). После прихода на вход 20 импульса Установка нуля (диаграмма 68 на фиг.5) длительностью Т2-Т,, положение фронтов

которого на временной оси может быть произвольным, на шестом выходе блока 19 управления формируется импульс (диаграмма 69 на фиг.5), фронты которого жестко связаны с импульсами последовательности, представленной на диаграмме 65, так что на выходе элемента ИЛИ 17 с момента Тэ по ТуРИАИ 1.

В момент Т4 соответствующим им- пульсом последовательности диаграммы

67 (фиг.5) производится запись новых значений N и Nfl в регистр 8 согласно (11), а до момента 1t (фиг.5) заканчиваются переходные процессы в блоках усилителя 1 и преобразователях

6 и 7.

Вторая фаза . С момента Т до Т в блоке 4 запоминается новое значение выходного напряжения преобразователя 7. С момента Т до Т.

преобразователь 3 преобразовывает новое значение его входного напряжения и в момент Т выдает новое значение

О

кода

40

LsL.

(21)

В момент Тд на четвертом выходе блоке 19 управления появляется одиночный импульс (диаграмма 70 на фиг.5) ,

по переднему фронту которого производится запись кода NCOBO второй регистр 9, если при этом , выходной код устройства, записываемый в третий регистр 10 в момент Т10 (диаграмма 71 на фиг.5) согласно (15), равен нулю. При последующих изменениях входного уровня отсчеты происходят относительно уровня, зафиксированного при установке нуля, а при

FOTH относительно фиксированного уровня, однако значение кода NCo при этом сохраняется.

111571763

В этом режиме на вход 22 подается - логическая единица, поэтому

к

1Ми

1

(22)

Устройство превращается в Широкодиапазонное устройство дискретной автоматической регулировки уровня (по отношению к напряжению ла шине 24) с разрешающей способностью R.. При этом на шину 21 должен быть подан код

L - 201g H J&Jukffltf(23)

Г2.- u s

соответствующий середине (в линейном масштабе) динамического диапазона преобразователя 3.

Достоинством такого режима является то, что среднее значение напряжения на входе аналого-цифрового пре- Iобразователя поддерживается в середине его динамического диапазона, а размах шумовой составляющей может достигать величины D, при этом дополнительная погрешность, которая могла бы быть из-за кратковременных выходов

и. за пределы

мин

U MCKKC

не воз никает.

Усилитель 1 (фиг.2) работает следующим образом. Преобразуемое напряжение поступает на вход 26, а код Управления Му - на вход 28. Пока

(24)

(где Nуо - код, заданный на втором Входе компаратора 31), на выходе компаратора присутствует логический Нуль, первый каскад 30 усиления выключен, аналоговый сигнал проходит через мультиплексоры 35 непосредственно на вход второго каскада 30а ., усиления, минуя малошумящий усилител 36, имеющий небольшой динамический диапазон. Код Ny проходит на выход сумматора 32 и без изменения подаетс на вход дешифратора 33, который преобразует, например, двоичный код Ny В унитарный код. Таким образом, при

увеличении кода довательно включаются

NV от 0 до

N

яо

после№я 30„

3Q,

каскады усиле- Это обеспечивает

Ч..1 г.г малую погрешность переключения одной ступени усиления, что также достига- ется и применением в указанных каскадах интегральных ЦАП, включенных по схеме г усилением.

12

При (J включается первый кад 3CL , а сумматор 32 уменьшает Jv

ной код дешифратора на N

УО

N N, N

vo(25)

5

Наличие мультиплексоров, отключающих первый каскад усиления, позволяет расширить динамический диапазон усилителя в сторону больших напряжений, наличие усилителя 36 - в сторону малых напряжений (чему также способствует наличие фильтров 29), а работа большей части каскадов с унитарным кодом позволяет уменьшить погрешность переключения усиления до величины порядка 0,02 дБ,

ЦАП 6 (фиг.З) работает следующим образом.

Соответствующие разряды кода управления Мд поступают на входы 46. Входное напряжение подается на вход 44.

Затухание от входа 44 до выхода

45 равно

т

А X

m

Ai

Е. - 20lg

J-1 - I Ни,- + М«,,нч

; t

(26)

NO NHJ+NL..J+P;. ,

(27)

где A, m

HJ

затухание j-ro каскада 41; количество каскадов 41; ( номер входа 46 ( соответствует младший разряд); вес входов цифрового сигнала каскада 41, соединенных с (2 ) -и шиной, управления;

5

N

И

5

0

/

ч

N.

вес входов цифрового сигнала каскада 41, соединенных с (2 П4.,)-й шиной управления;

бит, соответствующий i-му входу 46-;

вес входов цифрового сигнала j-ro каскада, соединенных с i-й шиной управления;

вес входов цифрового сигнала j-ro каскада, соединенных с (п-Н)-й шиной управления; 2Ь-1 суммарный вес входов цифрового сигнала каскада 41, Ъ - его разрядность.

- 131571763I

На примере одного из многочислен- диапазон j-ro каскада, иых частных случаев покажем линейную

зависимость затухания (26) от кода „ п „ /м управления , « u%nij /ы н

Чп

5

величина перепада затух при изменении 1-го бита Выберем:

N Z.l.L,,

IS1

(28)

где L. - весовые коэффициенты кода

Для этого потребуем, чтобы все

N,. (отсутствуют соединения входов цифрового сигнала каскада 41 с выходами инверторов) и небыло соединений указанных входов разных каскадов 41 с одной и той же шиной управления, кроме (2h.,)-8 и (2h+1)-ii.

В этих предположениях имеем из (26) и (27) соответственно для.j-ro каскада

Aj 2018-

NHi + l.NfJ

NO NHJ + Nuj .

После умножения числителя и знаменателя дроби в (29) на Nui+ ZN..

J II

с учетом (30)

А. А. : А. ,

(31)

где

д. -201s - Ajo2Uig N

исходное (нерегулируемое) затухание j-ro каскада;

(33

AiP -20I8 N.-NL.

j

,

затухание каскада, зависящее от бита

/

В предположении

,j « NHJ(34)

(33)

линеаризуем (33): А,-Р DJ ,

(35)

где

, Dj -201g

Hj

NHj+lNtj

(36)

,

5

величина перепада затухания j-ro ЦАП при изменении 1-го бита 1 . Выберем:

10

Н

W

(37)

Тогда из (35)

15

V DJ-RA-NJP

(38)

где

и,,ь, (39)

з -ro

20 парциальный код,

каскад.

(29) Возвращаясь к

j-ro каскада

(30) 25 A A- +D--R -NA;-Aje+uj КЛ N ip

(40)

Суммируя по j, получаем для ЦАП 6

AA AB+DA-RA NA(41)

В другом частном случае 2Nj. аналогично

(32)

А/ Ао +

(42)

35

Узкодиапазонный логарифмический преобразователь аналог.- код (фиг.4) работает следующим образом. РГШ 51 тактируется с входа 59 тактовой f 40 частотой (диаграмма 65 на фиг.5) и работает в режиме непрерывного преобразования. РПП последовательно подает единицы на аттенюатор 54, а результат сравнения его выходного на- 45 пряжения с входным напряжением к входу 58 последовательно записывается в РПП.

Затухание аттенюатора 54 аналогично (42):

50

(43)

Au- r-L

(в (43) опущено для простоты фиксированное затухание А0, поскольку оно

может быть учтено соответствующим выбором опорного напряжения источни4ка 53).

В конце преобразования выходное напряжение аттенюатора 54

15

el

(44)

:примерно равно входному преобразооа- теля 3:

t. L

uo-a . 2uL,

откуда

L - -loga™--, . r ° ц.

(45)

iio окончании преобразования выходной код L РП.П эагшеынаетск в буфзрный

.на выход преобразовала: ;;: /и входы, компараторов 56 и 57 йслиL L fi,HKC или L-i LjVU;. s на выходах 62и 63 формируются в ВИДЕ логический ди-т-щы Р:оотве -.--С ГЕ..ие с-нгпгшм,

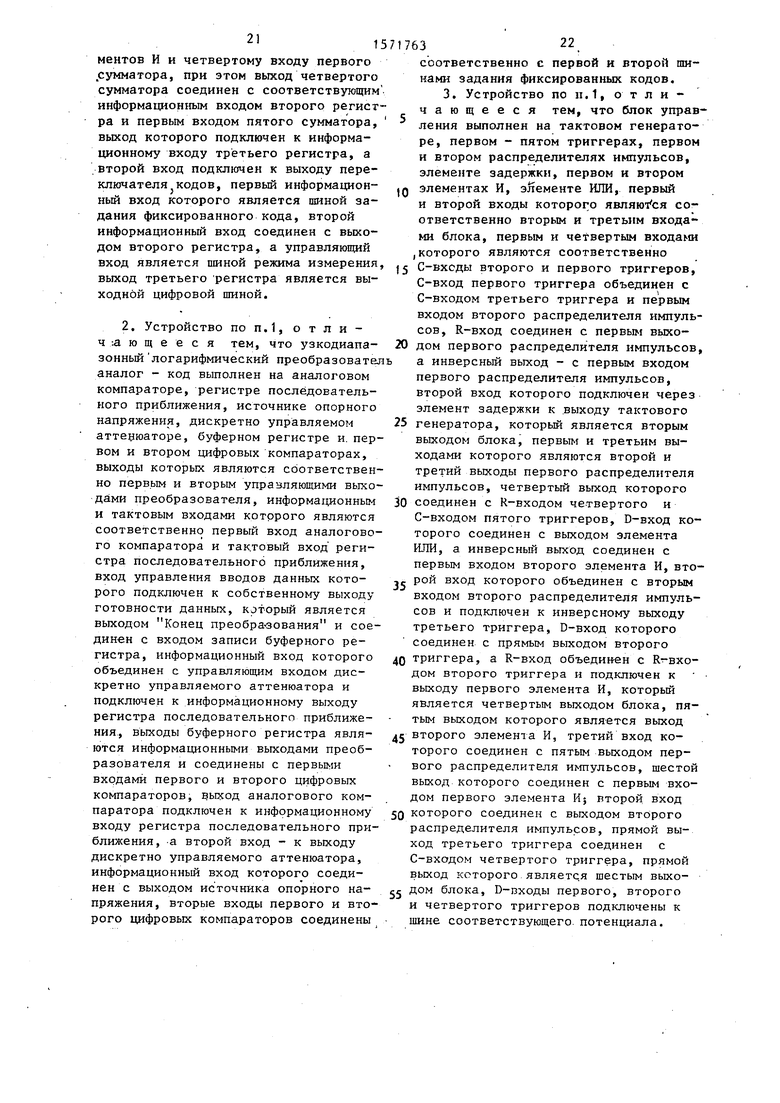

| Па фиг,. позннпмь;::, ;. ; обозли heiib диагра;..; : , по;;е щюг.:.1р ркбот ,7 ;блока управлении,. , Блок управления содержит (фпг,6) ;;1шны ИЗ ;-т 84;, ,: ;-;-:1:;;.1:; по п. :т|ВерТЪ Л БХОД;.: о5- Mh T l-OTI/ 89 s;:;.; тертый 90, пятый 9 s иторон v.if у ар- 1в1мй 93 и игестой 94 аыхо.г;ы,, тактовый ;генер атор 95 - с первого по пятый трчгге ;рь 96--1003 элемент 0 i ьадйр:ккн5 псрвыр 102 и второй 103 распредепителп им- :пульсова элемент 10 и а также п ервый 105 и второй 105 элементы И

Диаграмма 66 па фиг ,5 ол.новремеи- |ко изображает сигнал на первом выходе- 93 блока управления,, которьм с точностью до задержки совпадает с сигналом на четвертом входе 88 блока управления.

Диаграммы 72-81 .изображают сигналы; 72 - на инверсном выходе первого триггера 96 г, 73 - на втором выходе распределителя 102 иклульсов 102; 74 - на третьем выходt. раснрецеллте- ля 102; 75 - на пл-.:ом выходе распределителя 102; 76 - на прямом выходе второго триггера 97; 77 - на прямом выходе третьего i триггера 98; /8 на выходе второго распределителя 103 импульсов; 79 - ка входе об (или 87) элемента ИЛИ 104 з случае выхода и( из зоны и, ..., i l.;, ,.,...cj 80 - ла инверсном выходе пятого триггера 100

для этого случая,; о

«1

на пятом выходе блока управления для этого случая .

1571763

16

Н а фиг о 5 ось t. дана для моментов времени , ось Ц -для моментов времени Т.,.,, .

Моменты времени Т... -Т0 соответствуют; Тп - фронт одного из импульсов Конец преобразования (диаграмма 66) - появление на одном из выходов 62 или 63 .преобразователя 3. логичес- кой единицы, для случая

О ,L L

ЛЛ-ИН ;

(47)

L 11 .-. .11 ,J

tЈ - отсутствие гре.тий регистр 10

I запись результата в третий регистр 10 (фиг.1), T.J3 - момент переключения усиления усилителя 1 (фиг.1) импудьсом 56 (фиг.5), появление логического нуля на инверсном выходе пятого триггера 100-, Т. - Т., - окончание переходных процессов на входе преобразователя 3; Т ,1С--Т ,,

Э

запись нового значения -выходного напряжения преобразователя 7 з блок 4; I,, --Т 1ч - преобразование луеобразив.)- телем3 нового значения напряжения u, :ia аго входа,; Т ,.. - Т к:ичуо ;ьс;-.а записи на выходе. 91 (фиг 6) элемента И 106; Т)Г .-- переключение в исходное состояние пятого триггера 100; Тго - очередной импульс записи в третий регистр 10 (фиг.1) после переключения усилителя ,

Блок 19 управления (фиг,6) работает, следующим образом.

Фронты тактовой частоты с выхода тактового генератора 95 (диаграмма 65 на фиг.5) поступают на второй выход 92 (для тактирования преобразователя 3) и через элемент 101 задержки на тактовый вход распределителя 102 импульсов. В исходном состоянии он обнулен потенциалом единицы с инверсного- выхода первого триггера 96. По приходу фронта Конец преобразования 56 (фиг.5) на четвертый вход 88 блока 19 первый триггер .переходит з 1 (диаграмма 72), разрешает работу распределителя 102, который вырабатывает серию импульсов, сдвинутых па период тактовой частоты (диаграммы 66573574,67 и 75 на фиг.5).

Распределитель 102 (фиг.6) прекращает работу после появления логической единицы на одном его выходе, (не показан), после чего первый триггер 96 и распределитель обнуляются.

Импульсы с остальных выходов распределителя 102 соответственно посту пают на первый выход 93 блока 19, на первый вход элемента И 105, на третий вход элемента И 106, на третий выход 89 блока 19, на R-вход четвертого триггера 99 и С-вход пятого триггера 100.

При поступлении положительного перепада на первый вход 85 блока 19 второй триггер 97 переходит в 1 в

момент Т4 (диаграмма 76), а третий триггер 98 переходит в 1 в момент Т3 (диаграмма 77 на фиг.5).

По положительному перепаду с прямого выхода третьего триггера 98 переходит в 1 также и триггер 99 (момент Т&, диаграмма 69 на фиг.5), сигнал с прямого выхода которого поступает на шестой выход 94. Третий триггер 98 разрешает работу второму распределителю 103 импульсов.

В момент Tg (диаграмма 78 на фиг.5) на выходе распределителя 103 появляется потенциал логической единицы, который разрешает прохождение импульса на четвертый выход 90. Импульсом с выхода 90 (момент Т, диаграмма 70 на фиг.5) обнуляется второй 97 и третий 98 триггеры, и распределитель 103 приходит в исходное состояние.

Пятый триггер 100 (фиг.6) формирует команду (диаграмма 80 на фиг.5) логического нуля, запрещающую по первому входу второго элемента И 106 ((фиг.б) прохождение импульсов с выхода распределителя 102. на пятый выход 91 для предотвращения записи в третий регистр 10 (фиг.1) кодов, соответствующих переходным процессам после появления команд Fp 1 или F. 1 (диаграмма 79 на фиг.5) и при последующем переключении усилителя, так что импульс записи в третий регистр 10 (фиг.1) в момент Tf7 на диаграмме 81 (фиг.5) отсутствует.

Усилитель 1 может быть реализован с применением, например, ДАЛ К572ПА1А и операционных усилителей КР544УД2А в каскадах усиления, начиная с второго, и малошумящего операционного усилителя типа К1407УД1 (предусматривается регулировка его коэффициента усиления в небольших пределах), при этом погрешность переключения одной ступени усилителя при ее величине 10,24 дБ составляет 0,02-0,03 дБ, а

0

0

динамический диапазон - 130-140 дБ на рабочей частоте до 100 кГц.

Преобразователь 5 (фиг.1) может быть реализован е применением ЦДЛ К572ПА1А и ОУКР544УД2А. При этом его погрешность преобразования кода в напряжение не превышает (при весе старшего разряда 5,12 дБ) 0,02 дБ на

Q частотах до 100 кГц.

Аттенюатор 54 (фиг.4) в преобразователе 3 может быть реализован с пр и- менением ЦАП К572ПА2А и ОУК140УД17А. В преобразователе 3 (фиг.4) могут

5 быть применены РПП типа К564ИР13, а в качестве компаратора - например, операционный усилитель типа КМ551УД1. При этом достижима погрешность преобразования 0,02 дБ в диапазоне 20,46 дБ и время преобразования, исчисляемое долями миллисекунды, разрешающая способность 0,01 дБ.

Погрешность преобразования устройства уменьшена путем применения уси5 лителя 1, преобразователей 6 и 3,

каскадов усиления (затухания), содержащих интегральные ЦАП.

Малая погрешность преобразования и высокая разрешающая способность аналого-цифрового преобразователя реализуется (при измерениях вершины АЧХ фильтра) путем сдвига динамического диапазона устройства за счет изменения затухания, т.е. привязки динамического диапазона устройства к за5

0

5

данному уровню введением режима Установка нуля.

Улучшение разрешающей способности во всем динамическом диапазоне устройства достигается последовательным включением каскадов усиления усилителя с ростом затухания входного напряжения благодаря наличию в нем дешифратора двоичного кода в унитарный код, что обуславливает постепенное накопление погрешности каскадов усилителя, так что разрешающая способность устройства становится соизмеримой с погрешностью переключения только одного каскада усилителя (исключение составляет точка, где включается первый каскад усиления, в этой стыковка осуществляется регулировкой усиления первого каскада в узких пределах с учетом конкретных значений усиления соответствующих каскадов).

Динамический диапазон расширен в области больших затуханий благодаря наличию фильтров, малошумящего

19

157

каскада усиления (каскада усиления с малым смещением), в области мапых затуханий отключением первого каскада усиления и применением интегральных ДАЛ, погрешность преобразования в области больших затуханий уменьшена переводом работы устройства в режим с автоматической дискретной регулировкой уровня и, на входе устройства благодаря чему шумовые выбросы входного напряжения и ц устройства расположены симметрично относительно |динамического диапазона устройства. Устройство позволяет преобразовывать переменные, разнополярные и однополярные постоянные напряжения, может быть применено в качестве широкодиапазонного устройства дискретной автоматической регулировки уровня (съем аналогового сигнала с выхода ,24), а также в сочетании с преобразователем частоты оно может быть основой ширсходиапазонных (как по частотному, так и по динамическому диапазону) селективных микровольтмег- ров, анализаторов спектра, измерителей АЧХ и т,д.

Формула изобретения

динен с входом аналогового сигнала функционального умножающего цифроана- логового преобразователя, выход которого является выходной аналоговой шиной и соединен с входом аналогового функционального преобразователя, выход которого подключен к информационному входу блока выборки и хранения, выход которого соединен с информационным входом узкодиапазонного логарифмического преобразователя аналог - код, тактовый вход которого подключен к второму выходу блока уп5 равления, третий, четвертый и пятый выходы которого соединены с входами записи соответственно первого, второго и третьего регистров, первый вход является шиной Установка нуля,

0 информационный вход первого регистра соединен с выходом третьего сумматора, выходы младн,их разрядов соединены с соответствующими входами младших разрядов первой группы входов

5 третьего и четвертого сумкяторов и с входом цифрового сигнс .а функционального умножающего цифроаналогового преобразователя, а выходы старших разрядов первого регистра соединены

0 непосредственно с соответствующими управляющими входами входного кодо- управляемого n-каскадного усилителя и входами старших разрядов первой группы входов четвертого сумматора

,. и через первый сумматор с соответствующими входами старших разрядов первой группы входов третьего сумматора, входы второй группы которого через блок элементов И соединены с соответQ ствующими выходами второго сумматора, первые входы которого являются первой шиной управления, а вторые входы объединены с соответствующими входами второй группы четвертого сумматора

с и подключены к соответствующим информационным выходам узкодиапазонного логарифмического преобразователя аналог - код, первый и второй управляющие выходы которого соединены соотQ ветственно с вторыми и третьими входами первого сумматора и блока управления, четвертый вход которого соединен с выходом конец преобразования узкодиапазонного логарифмического

- преобразователя аналог - код, шестой выход подключен к первому входу элемента ИЛИ, второй вход которого является второй шиной управления, а выход подключен к второму входу блока элементов И и четвертому входу первого .сумматора, при этом выход четвертого сумматора соединен с соответствующим информационным входом второго регистра и первым входом пятого сумматора, выход которого подключен к информационному входу третьего регистра, а второй вход подключен к выходу переключателя кодов, первый информационный вход которого является шиной задания фиксированного кода, второй информационный вход соединен с выходом второго регистра, а управляющий

вход является шиной режима измерения, ( с-вхсды второго и первого триггеров,

выход третьего регистра является выходной цифровой шиной.

20

С-вход первого триггера объединен с С-входом третьего триггера и первым входом второго распределителя импуль сов, R-вход соединен с первым выхо25

30

дом первого распределителя импульсов а инверсный выход - с первым входом первого распределителя импульсов, второй вход которого подключен через элемент задержки к выходу тактового генератора, который является вторым выходом блока, первым и третьим выходами которого являются второй и третий выходы первого распределителя импульсов, четвертый выход которого соединен с R-входом четвертого и С-входом пятого триггеров, D-вход ко торого соединен с выходом элемента ИЛИ, а инверсный выход соединен с первым входом второго элемента И, вто

,- рой вход которого объединен с вторым входом второго распределителя импульсов и подключен к инверсному выходу третьего триггера, D-вход которого соединен с прямым выходом второго

до триггера, а R-вход объединен с R-входом второго триггера и подключен к выходу первого элемента И, который является четвертым выходом блока, пятым выходом которого является выход

д5 второго элемента И, третий вход которого соединен с пятым выходом первого распределителя импульсов, шестой выход которого соединен с первым входом первого элемента И; второй вход

50 которого соединен с выходом второго распределителя импульсов, прямой выход третьего триггера соединен с С-входом четвертого триггера, прямой выход которого является шестым выходом блока, D-входы первого, второго и четвертого триггеров подключены к шине соответствующего потенциала.

55

соответственно с первой и второй шинами задания фиксированных кодов.

с-вхсды второго и первого триггеров,

0

С-вход первого триггера объединен с С-входом третьего триггера и первым входом второго распределителя импульсов, R-вход соединен с первым выхо5

0

дом первого распределителя импульсов, а инверсный выход - с первым входом первого распределителя импульсов, второй вход которого подключен через элемент задержки к выходу тактового генератора, который является вторым выходом блока, первым и третьим выходами которого являются второй и третий выходы первого распределителя импульсов, четвертый выход которого соединен с R-входом четвертого и С-входом пятого триггеров, D-вход которого соединен с выходом элемента ИЛИ, а инверсный выход соединен с первым входом второго элемента И, вто- рой вход которого объединен с вторым входом второго распределителя импульсов и подключен к инверсному выходу третьего триггера, D-вход которого соединен с прямым выходом второго

о триггера, а R-вход объединен с R-входом второго триггера и подключен к выходу первого элемента И, который является четвертым выходом блока, пятым выходом которого является выход

5 второго элемента И, третий вход которого соединен с пятым выходом первого распределителя импульсов, шестой выход которого соединен с первым входом первого элемента И; второй вход

0 которого соединен с выходом второго распределителя импульсов, прямой выход третьего триггера соединен с С-входом четвертого триггера, прямой выход которого является шестым выходом блока, D-входы первого, второго и четвертого триггеров подключены к шине соответствующего потенциала.

5

20

„J

7

31

Ж

39

«« «««f1

еекдосо-я-п

Jj

-i,

IFF

4

-, |+1

I1 J

tK4---H №3rr-

- и ,-u «f -

Гг«fto

.

d

35

34

27

«« «««f1

31

и

|+1

1 J

-H №3rr-

-u «f -

г

Li«//77Ј

JBt-U

J

4ff,

48г 48L 48n

Wn-n

48 л i

48Zn

482„„

48Zf,.z

Фиг 4

| Устройство широкодиапазонного логарифмического аналого цифрового преобразования | 1980 |

|

SU900440A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-06-15—Публикация

1988-03-25—Подача