Изобретение относится-к области вычислительной техники и может быть использовано при построении вычислительных устройств, работающих в системе осТаточйых классов.

Известен табличный сумматор-вычитатель,содержащий дешифраторы, .группы ключей, элементы ИЛИ, кодовую линейку, операционную матрицу, усилители и соответствующие связи tlЗ

Недостаток устройства - большой объем оборудования.

Наиболее близким к предложенному по техническому решению является устройство для вычитания по модулю, содержащее Первый и второй дешифраторы, входы которых являются входами операндов устройства, пе1рвую и вторую группы ключей, первую и вторую группы элементов ИЛИ, первый коммутатор, а Также выходной регистр,

. сумматор по модулю два, третью груП пу элементов ИЛИ, девять элементов ИЛИ, восемь элементов И, второй коммутатор, причем i-и и (Р-1-1)-й вы|ходы дешифраторов (1 0,1,2,..,,Р-1; Р - модуль) подключены соответствен но к первому и второму входам j-го элемента ИЛИ (,2,...,(Р-1)/2 при Р нечетном; j 1,2,...,Р/2 при Р четном) соответственно первой и второй групп, первая группа t;-ых выходов (,1,2, .. ., {Р-1)/2 при Р нечетном; 1 0,1,2 , .. . ,Р/2 при Р четном) соответственно первого и второг дешифраторов подключена к входам соответственно первого и второго элементов ИЛИ, выходы которых подключены соответственно к первому и второму входам сумматора по модулю два, вторая группа г-х выходов (г (Р-1)/2+1,...,Р-1 при Р нечетном, Г Р/2Ы , . .. ,Р-1 при Р четном) соответственно первого и второго дешифраторов подключена к входам соответственно третьего и четвертого элементов ИЛИ, выходы KOTOpblx подклк)че)ны соответственно к третьему и чет-, вертому входам сумматора по модулю два, выходы элементов ИЛИ первой и второй групп подключены к первым входам соответствующих ключей первой и второй групп, вторые входы которых объединены и подключены к вы ходам соответственно первого и второго элементов И, первые входы которых подключены соотве±ственйо к нулевому и единичному выходам сумматора по модулю два, а вторые входы объединены и являются управляющим входом устройства, выходы ключей первой и второй групп подключены соответственно к первой и второй группам входов соответственно первого и второго коммутаторов подключены к соответствующим входам пятого элемента ИЛИ и соответственно к первым и третьим входам .j х элементов ИЛИ

третьейгруппы, (P-j)-e выходы первого и второго коммутаторов подключены к соответствующим входам шестого элемента ИЛИ и соответственно к вторым н четвертым входам j-х элементов ИЛИ третьей группы, первые входы третьего и пятого, четвертого и шестого элементов И попарно объединены и подключены к выходам соответственно пятого и шестого элементов ИЛИ, вторые входы третьего, четвертого, пятого и шестого элементов И объединены и подключены к выходу седьмого элемента ИЛИ, выходы которого подключены к выходам седьмого и восьмого элементов И соответственно, первые входы которых подключены соответственно к выходам второго-и четвертого Элементов ИЛИ, а вторые входы объединены и подключены к выходу Первого элемента ИЛИ, выходы третьего и .шестого,пятого и четвертого элементов И подключены попарно к входамвосьмого и девятого элементов ИЛИ соответственно/ выходы которых подключены соответственно к первому и второму входам выходного регистра, выходы элементов ИЛИ третьей группы подключены к соответствующим 6 -М входам (3,4,...,(Р+1)/2+2 при Р нечетном, ,4,...,Р/2+2 при Р четном) выходного регистра, выходы которого являются выходами устройства Сз.

Недостаток устройства - большой объем оборудования.

Цель изобретения - уменьшение объема оборудования.

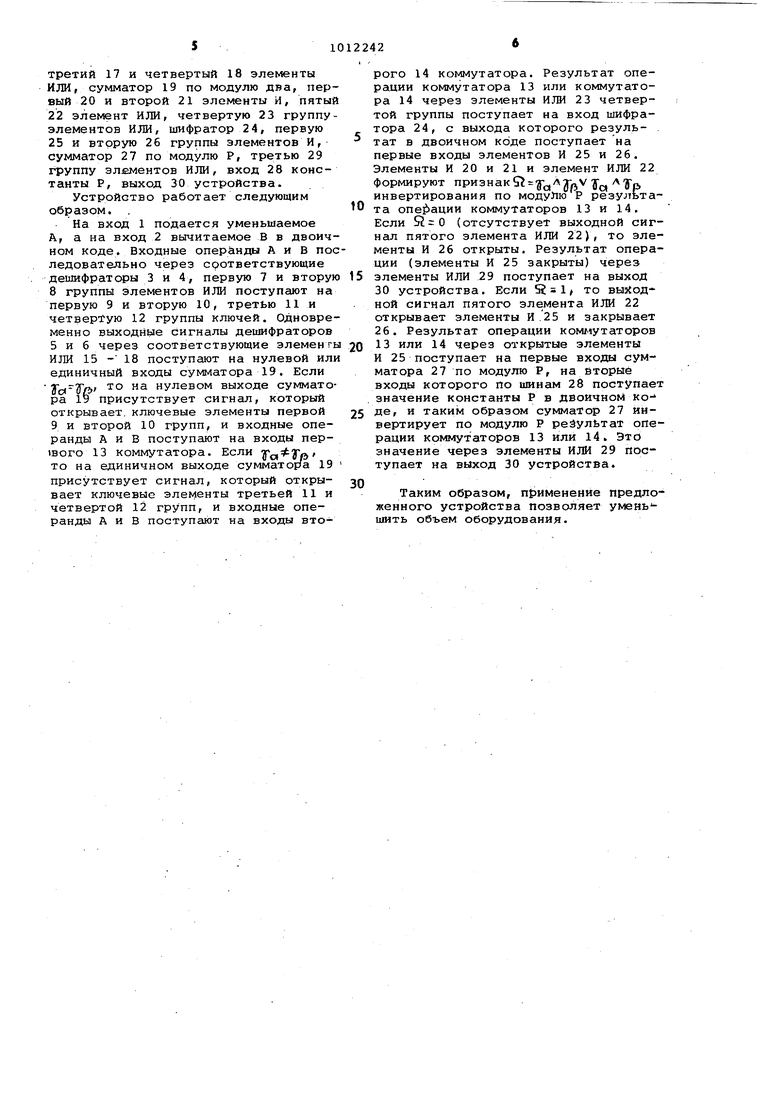

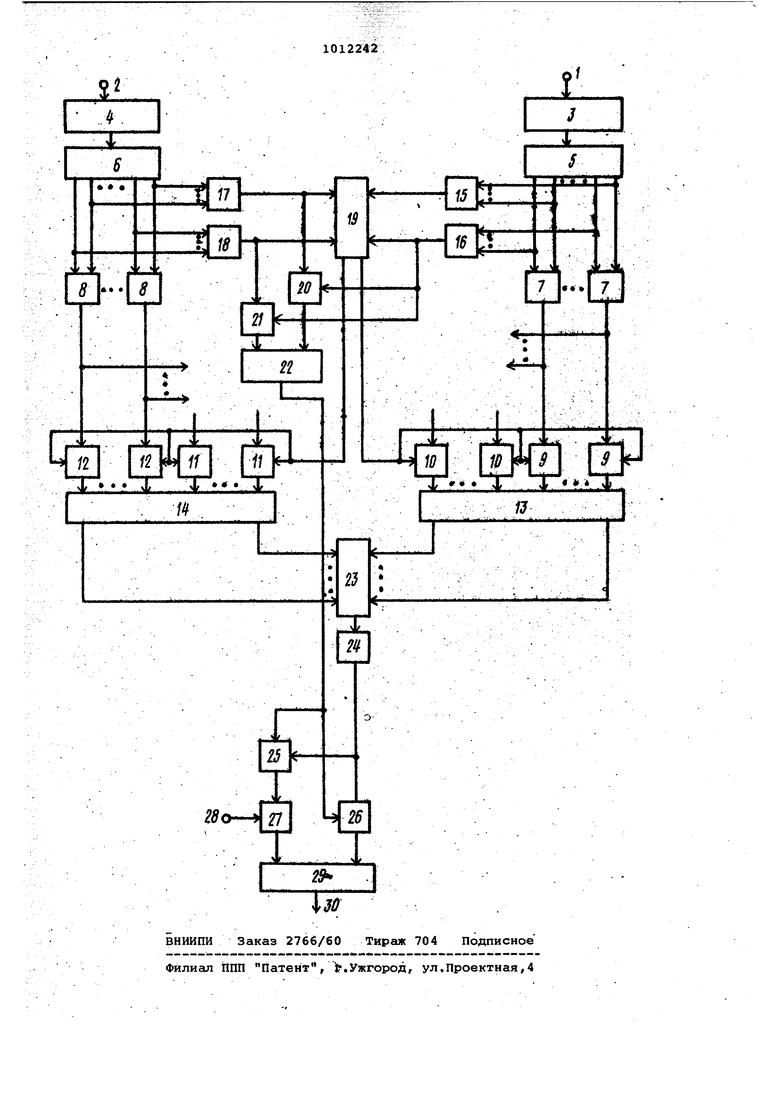

Поставленная цель достигается тем, что устройство для вычитания по модулю содержащее первый и вт.орой входные регистры, входы которых являются входами операндов устройства, а выходы подключены к вхйдам первого и второго дешифраторов, первую и вторую группы ключей, первую, вторую, третью и/ четвертую группы элементов ИЛИ, первый и второй коммутаторы,сумматор по модулю два, первый, второй/ третий, четвертый и пятый элементы Или, первый и второй элементы И,причем 1-и и ()-й выходы дешифраторов (i 0,l, 4 .. ,Р-1; Р - модуль) I подключены соответственно к первому и второму входам j-ro элемента ИЛИ (J 1/2,.. ., (Р-1)/2 при Р нечетном; ,2,..,Р/2 при Р четном) соответственно первой и второй групп, первая группа с-X выходов (,l,..., ...,(Р-1)/2 при Р нечетном; k .0,1/...,Р/2 при Р четном) соответственно первого и второго деш;:.фраторов прдключена к входам соответственно первого и второго элемента ИЛИ выходы которых подключены соответственно к первому и второму входам сумматора по модулю два, вторая группа г--X выходов (i- (P-l)/2 + 1, .. . ...,P-i при P нечетном; f-b p/2+1,.. ./ ...,P-l при P четйом) соответственно: первого и второго дешифраторов подключёна к входам соответственно третьего и четвертого элементов ИЛИ, выходы которых подключены соответственно к третьему и четвертому входам сумматора по модулю два, выхбды элементов ИЛИ первой и второй групп подключены k первым входам соответствующих ключей первой и второй групп, Ёыходы которых подключены соответственно к первой я второй гр.уппйм вхо.дов соответственно первого и второго коммутаторов, первые входы первого и второго элементов И объединены и . подключены к выходу второго элемента ИЛИ, вторые входы первого и второго элементов И подключены к выходам третьего и четвертого элементов ИЛИ соответственно, выходы первого и втО рого элементов И подключены к входам пятого элемента ИЛИ, содержит шифратор, первую и вторую группы элемент тов И/ сумматор по модулю Р, первый вход которого является входом константы Р устройства, а второй ЁХОД подключен к выходам ебответствукнйих элементов И первой группы, группа выходов сумматора по модулю Р подключена к первым входам элементов ИЛИ третьей группы, вторые входы которых подключены к выходам соответствующих элементов И второй группы, первые которых объединены с первыми входами соответствующих элементов И первой группы и подключены к соответствующим выходам шифратора, уходами подключенного к ёыхоДам .соответствующих элементов ИЛИ четвертой груйпы первые и вторые входы которых подключены к Ьоответствующим выходам соответственно первого и второго коммутаторов/ йторые входы элементов И первой и второй групп объединены и подключены к выходу пятого элеМен та ИЛИ, выходы элейентов ИЛИ третьей 1 руппы являются выходом устройства В устройстве используется свойство симметрии арифметической таблицы относительно Диагоналей. Пусть А - уменьшаемое, -В - йУчйтаемре, Р - модуль и пусть необходимо определить (А-в) mod Р/ Входные операнды можно представить в виде А (fci а) и В где у - индекс кода табличного Умножения, и 1 а {Р-1)/2. Возможные варианты модульного вычитания для соответственно 1, 11, 111 и 1У квадрантов таблицы модульного вычитания вид (P-oi): P-(c«4p)mo6I Р ( (cr-p)moj Р; О(-(Р-Р|) (oi+p)modP; (p-oib(P-p)fp-(oi-|b))tnoa Р. Из приведенных соотношений следует, что в качестве первого и рто т. рого коммутаторов размером можно использовать 11 квадранты соответственно таблиц модульных операций (А-в) mod Р и (А+В) mod Р.. В качестве первого коммутатора, реализующего операцию модульного вычитания для 11 и 1У квадрантов, используется табл. li ..Таблица 1 Для 1 у квадранта (fj,,-y- l) результат операции инвертируется по модулю Р. В качестве второгокоммутатора, реализующего операцию модульного ёычиоания для 1 и 111 квадрантов, используется второй квадрант табл.2 (AtB) mod P. /.Таблица 2. модулю р. на чертеже представлена структурная схема устройства. Устройство содержит первый 1 и второй 2 входа, первый 3 и второй 4 входные регистры, первый 5 и второй 6 дешифраторы, первую 7 и вторую 8 группы элементов ИЛИ, первую 9, вторую 10, третью 11 и четвертую 12 группы ключей, первый. 13 и второй J.4 коммутаторы, первый 15, второй 1б,

третий 17 и четвертый 18 элементы Или, сумматор 19 по модулю два, первый 20 и второй 21 элементы И, пятый 22 элемент ИЛИ, четвертую 23 группуэлементов ИЛИ, шифратор 24, первую 25 и вторую 26 группы элементов И, сумматор 27 по модулю Р, третью 29 группу элементов ИЛИ, вход 28 константы Р, выход 30 устройства.

Устройство работает следующим обраэом. .

На вход 1 подается уменьшаемое А, а на вход 2 вычитаемое В в двоичном коде. Входные операнды А и в последовательно через соответствующие дешифраторы 3 и 4, первую 7 и вторую

8группы элементов ИЛИ поступают на первую 9 и вторую 10, третью 11 и четвертую 12 группы ключей. Одновременно выходные сигналы дешифраторов

5 и б через соответствующие элемен гы ИЛИ 15 - 18 поступают на нулевой или единичный входы сумматора 19. Если Jrt-Jr нулевом выходе сумматора 1У присутствует сигнал, который открывает, ключевые элементы первой

9и второй 10 групп, и входные операнды А и В поступают на входы пер1ВОГО 13 коммутатора. Если Уо,2Гв

то на единичном выходе сумматора 19 присутствует сигнал, который открывает ключевые элементы третьей 11 и четвертой 12 групп, и входные операнды ЛИВ поступают на входы второго 14 коммутатора. Результат операции коммутатора 13 или коммутатора 14 через элементы ИЛИ 23 четвертой группы поступает на вход шифратора 24, с выхода которого резуль- . тат в двоичном коде поступает на первые входы элементов И 25 и 26. Элементы И 20 и 21 и элемент ИЛИ 22 формируют признак г 5-дЛ2рУ2-,|| A-j-p инвертирования по модуЛю Р резуль.тата операции коммутаторов 13 и 14. Если Я-О (отсутствует выходной сигнал пятого элемента ИЛИ 22), то элементы И 26 открыты. Результат операции (элементы И 25 закрыты) через элементы ИЛИ 29 поступает на выход 30 устройства. Если 5 1 то выходной сигнал пятого элемента ИЛИ 22 открывает элементы И.25 и закрывает 26. Результат операции коммутаторов 13 или 14 через открытые элементы И 25 поступает на первые входы сумматора 27 по модулю Р, на еторыё входы которого По шинам 28 поступает значение константы Р в двоичноМ ко- де, и таким образом сумматор 27 инвертирует по модулю Р реЗул1зтат операции коммутаторов 13 или 14. Это значение через элементы ИЛИ 29 поступает на выход 30 устройства.

Таким образом, п$)ИМенение предложенного устройства позволяет умень шить объем оборудования.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычитания по модулю | 1980 |

|

SU959067A1 |

| Устройство для умножения чисел по модулю | 1981 |

|

SU981990A1 |

| Устройство для умножения по модулю | 1980 |

|

SU951296A1 |

| Устройство для умножения и сложения чисел по модулю | 1979 |

|

SU885999A1 |

| Устройство для модульного умножения | 1980 |

|

SU968808A2 |

| Арифметическое устройство в системе остаточных классов | 1981 |

|

SU999050A1 |

| Устройство для умножения чисел по модулю | 1981 |

|

SU976440A2 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2015575C1 |

| Устройство для умножения в системе остаточных классов | 1984 |

|

SU1166098A1 |

| Устройство для умножения по модулю | 1980 |

|

SU896620A1 |

УСТРОЙСТВО ДЛЯ ВЫЧИЧ АНИЯ ПО МОДУЛР, содержащее первый и второй входные регистры, входы являютсй Ьходами операндов устройства, выходы подклю ены к входим первого и второго де11ЮфрахЬров, первую и вторую группы ключей, первую, вТорую, третью и четвертую группы элементов ИЛИ Первый и второй коммутёторы, сумматор по модулю два, Нервый второй, третий, четве1 тый и пятый элемейтЫ ИЛИ, перйый и второй «лемёмты И, причем i -и и ()-й выходы дешифраторов (,1, . ,. jP-l; Р модуль) подключены соответственно к Первому и второму входам j-го элеМеН а ИЛИ (j 1,2 , ...., (Р-1) /2 при Р йечетной j 1,2 ,.,Р/2 при Р четном) cdlffTBeTCTBeHHo пербой и второй групп, первая группа i-x выходов (,i,..., (Р-1)/2 при Р нечетном ,1,J..,Р/2 при Р четном) соответственно Первого и втсфого дешифратоjpoB подключена к входам соответствейно первого и второго элементов ИЛИ, выходы которых подключены соответственно к Первому и второму входам сумматора по модулю два вторая групПА -it выходов (Г (Р-1)/2+1, .. ,Р-1 при Р нечетном г гР/2+1,.. ,Р-1 при Р четном) соответственно первого и второго дешифраторов подключена Кб входам соответственно третьего и четвертого элементов ИЛИ, выходы которых подключены соответственно к третьему и четвертому входам сумме тора по модулю два, выходы элементов ИЛИ первой и второй групп подключены к первым входам соответствующих ключей первой и второй групп, вг-хойы которых подключены- соответственно к первой и второй группам входов соответственно первого и второго коммутаторов ,. первые входы первого и вто рого элементов И объединены и подключены к выходу второго элемента ИЛИ, вторые входы первого и второго элементов И noдkлючeны к выходам третьего и четвертого элементов ИЛИ соответственно, выходы первого и второго элементов И подключены к входам Пятого элеМента ИЛИ, о т л ич а ю щ е е b я там, что , с целью (/ уменьшения объема оборудования, оно содержит шифратор, первую и вторую с: группы элементов И, сумматор по модулю Р , Первый вход которого является входом константы Р устройства, а второй вход подключен к выходам соответствующих элементов И перво.й группы, группа выходов сумматора X по модулю Р подключена к первым входаМ элементов ИЛИ третьей группы, вторые входы которых подключены к выходам соотвеТствуюпдах элементов И второй группы, первые входы которых объединены с первыми входами соответствукицйх элементов И первой группы и Подключены к соответствующим выходам шифратора, входами подключенного к выходам соответствующих элементов ИЛИ четвертой группы, перBfcJe и вторые входы которьЬс подключены к соответствующим выходам соответственно перйого и второго коммутаторов, вторые входы элементов И первой и второй групп объединены и подключены к выходу пятого элемента ИЛИ, выходы элементов ИЛИ третьей группы являются, выходом устройства.

| Табличный сумматор-вычислитель в системе остаточных классов | 1971 |

|

SU446056A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-04-15—Публикация

1981-12-03—Подача