Изобретение относится к цифровой вычислительной технике и может быть использовано при построении арифметических устройств ЦВМ, работающих в системах счисления с большими основаниями.

Известно матричное вычислительное устройство, которое содержит блок расстановки операндов, блок сравнения операндов, блоки распознавания, коммутации, формирования управляющих сигналов, вторичной расстановки операндов и определения совпадения входных сигналов, причем входы блоков расстановки операндов и сравнения операндов подключены к входам устройства, вход первого блока распознавания подключен к выходу блока расстановки операндов, первый и второй входы первого блока коммутации подключены соответственно к выходам блока расстановки операндов и первого блока распознавания, соответственно к первому и второму выходам первого блока коммутации, первый и второй входы второго блока коммутации соединены соответственно с первым выходом первого блока коммутации и первым выходом блока формирования управляющих сигналов, входы которого соединены соответственно с выходами второго и третьего блоков распознавания, первые входы вторичной расстановки операндов и блока определения входных сигналов соединены с вторым выходом первого блока коммутации, вторые входы - с выходом второго блока коммутации, выход блока вторичной расстановки операндов через матрицу памяти соединен с первым входом третьего блока коммутации, второй и третий входы которого подключены соответственно к выходу блока определения совпадения входных сигналов и к второму выходу блока формирования управляющих сигналов, первый и второй входы четвертого блока коммутации подключены соответственно к выходам третьего блока коммутации и первого блока распознавания, выходы четвертого блока коммутации и блока сравнения операндов соединены с соответствующими выходами устройства [1].

Известен сумматор по модулю, состоящий из трех матриц элементов И и двух групп элементов ИЛИ. Выходы элементов И каждой матрицы, формирующих одну и ту же функцию, объединены в одну выходную шину матрицы. Входы элементов И, расположенных в одной строке (в одном столбце) матрицы, подсоединены к одной входной горизонтальной (вертикальной) шине. Входные шины первой матрицы элементов И подсоединены к выходным шинам второй и третьей матриц элементов И соответственно. При этом горизонтальные и вертикальные входные шины второй и третьей матриц подключены через элементы ИЛИ первой и второй групп элементов ИЛИ к тем входным шинам сумматора, возбуждение которых отождествляется с номерами элементов аддитивных подгрупп по модулю [2].

Наиболее близким к изобретению является сумматор по модулю, содержащий три матрицы логических элементов И и две группы элементов ИЛИ, причем выходы элементов И каждой матрицы, формирующих одну и ту же функцию, объединены в одну выходную шину матрицы, входы элементов И, расположенных в одной строке и в одном столбце матрицы, подсоединены соответственно к одной горизонтальной и одной вертикальной входной шине матрицы, горизонтальные и вертикальные входные шины первой матрицы элементов И подсоединены соответственно к выходным шинам второй и третьей матриц элементов И. При этом вертикальные и горизонтальные входные шины второй матрицы элементов И подсоединены через элементы ИЛИ первой и второй групп элементов ИЛИ к тем входным шинам сумматора, номера которых сравнимы по числу, равному округленному до ближайшего целого в большую сторону корню квадратному из модуля, с номерами вертикальных и горизонтальных входных шин второй матрицы элементов И, а горизонтальные и вертикальные входные шины третьей матрицы элементов И подсоединены через элементы ИЛИ первой и второй групп элементов ИЛИ к тем входным шинам сумматора, частные от деления номеров которых на округленный до ближайшего целого в большую сторону корень квадратный из модуля, округленные до ближайшего целого в меньшую сторону, равны номерам входных горизонтальных и вертикальных шин третьей матрицы элементов И [3].

Недостатком прототипа являются ограниченные функциональные возможности, поскольку он выполняет только логическую операцию сложения двух чисел по модулю.

Целью изобретения является расширение функциональных возможностей устройства за счет добавления функции криптографического преобразования передаваемой информации.

Цель достигается тем, что вычислительное устройство, содержащее первую и вторую группы элементов ИЛИ, первую, вторую и третью матрицы двухвходовых элементов И, причем первый и второй входы первой матрицы двухвходовых элементов И подключены соответственно к первому выходу второй группы элементов ИЛИ и второму выходу первой группы элементов ИЛИ, а первый и второй входы второй матрицы двухвходовых элементов И подключены соответственно к первому выходу группы элементов ИЛИ и второму выходу группы элементов ИЛИ, первый и второй входы третьей матрицы двухвходовых элементов И подключены к выходам соответственно первой и второй матриц двухвходовых элементов И, содержит регистр ключа, первый и второй регистры исходных чисел, первый и второй дешифраторы кодов сдвига, первый и второй дешифраторы исходных чисел, первый и второй блоки признака сдвига результата, первый и второй блоки сдвига исходных чисел, блок сдвига результата, при этом первые входы первого и второго блоков признака сдвига, входы регистра ключа, первого и второго регистров исходных чисел подключены соответственно к первому, второму, третьему, четвертому и пятому входам устройства, входы первого и второго дешифраторов кодов сдвига подключены к выходам первого и второго регистров исходных чисел,

первые входы первого и второго дешифраторов исходных чисел подключены к выходу регистра ключа, вторые (третьи) входы первого и второго дешифраторов исходных чисел подключены соответственно к выходам первого и второго дешифраторов кодов сдвига (соответственно выходам первого и второго регистров исходных чисел), вторые входы первого и второго блоков признака сдвига результата (первые входы первого и второго блоков сдвига исходных чисел) подключены соответственно к выходам первого и второго дешифратора кодов сдвига, вторые входы первого и второго блоков сдвига исходных чисел подключены соответственно к выходам первого и второго дешифраторов исходных чисел, входы первой и второй групп элементов ИЛИ - соответственно к выходам первого и второго блоков сдвига исходных чисел, первый вход блока сдвига результата подключен к выходам первого и второго блоков признака сдвига результата, второй вход блока сдвига результата - к выходу третьей матрицы двухвходовых элементов И, вход шифратора результата подключен к выходу блока сдвига результата.

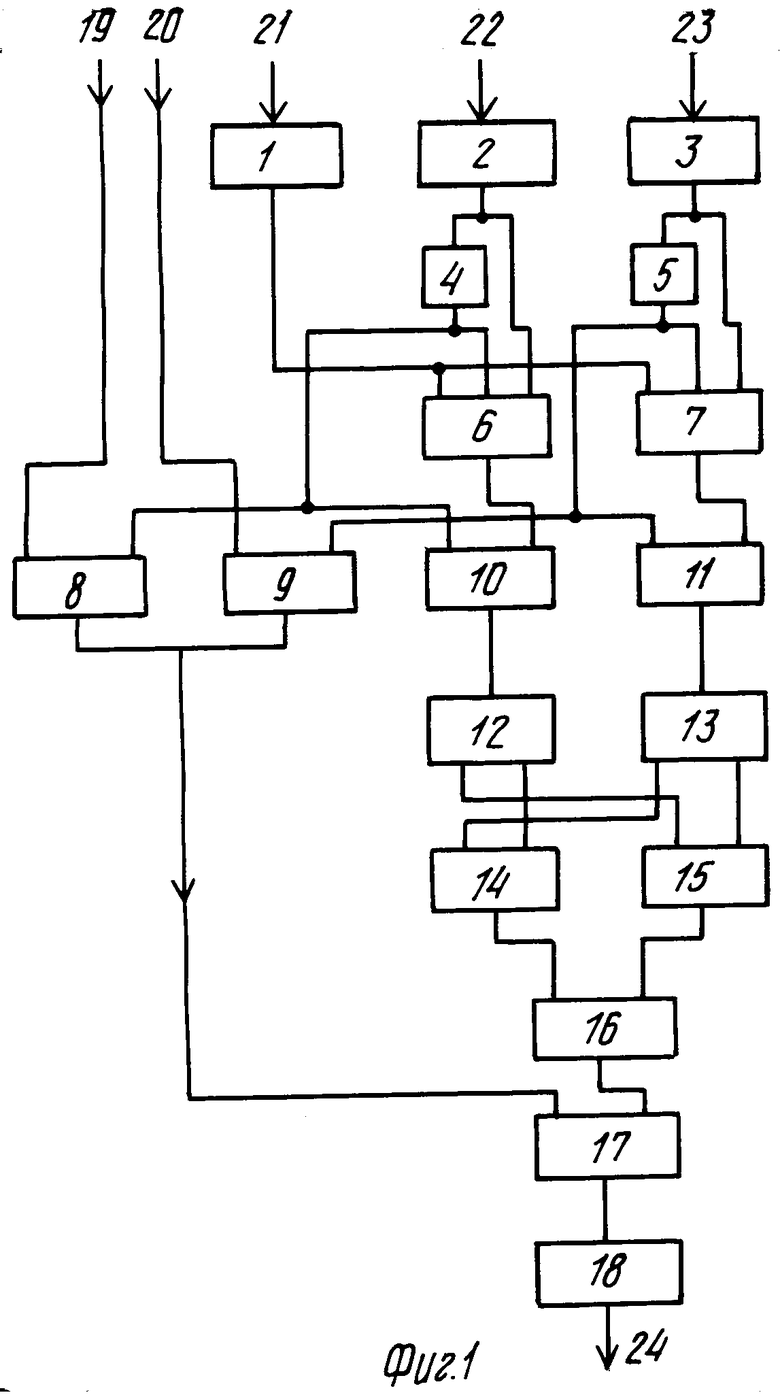

Блок-схема предлагаемого вычислительного устройства представлена на фиг. 1. Устройство содержит регистр 1 ключа, первый регистр 2 исходных чисел, второй регистр 3 исходных чисел, первый и второй дешифраторы 4 и 5 кодов сдвига, первый и второй дешифраторы 6 и 7 исходных чисел, первый и второй блоки 8 и 9 признака сдвига результата, первый и второй блоки 10 и 11 исходных чисел, первую и вторую группы 12 и 13 элементов ИЛИ, первую, вторую и третью матрицы 14,15 и 16 двухвходовых элементов И, блок 17 сдвига результата, шифратор 18 результата, входы 19-23 и выход 24.

Регистр 1 предназначен для хранения Х2-разрядного двоичного числа (Х2 = p˙l, где p - величина основания счисления, принятая для расчетов при построении блоков 12, ...,16, и l - число двоичных разрядов, используемое при кодировании каждой из цифр исходных чисел). Регистры 2 и 3 предназначены для хранения восьмиразрядных двоичных кодов.

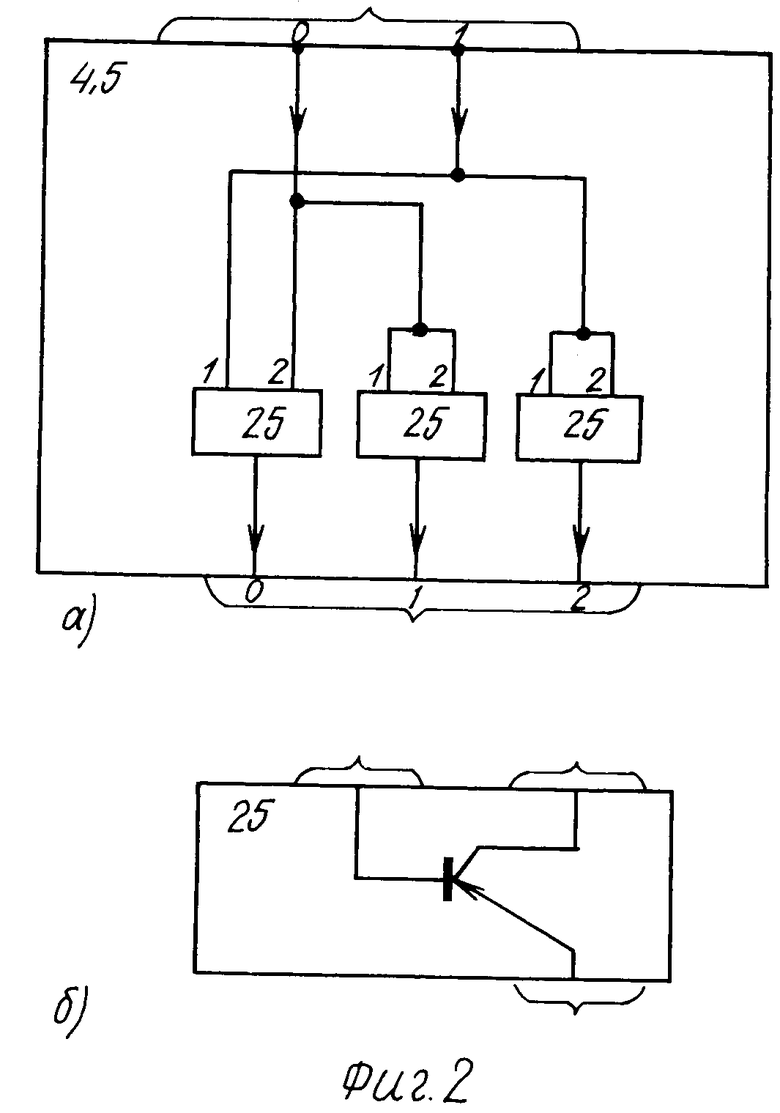

Дешифраторы 4 и 5 (фиг. 2) представляют собой комбинационные схемы, каждая из которых включает по три двухвходовых элемента И 25.

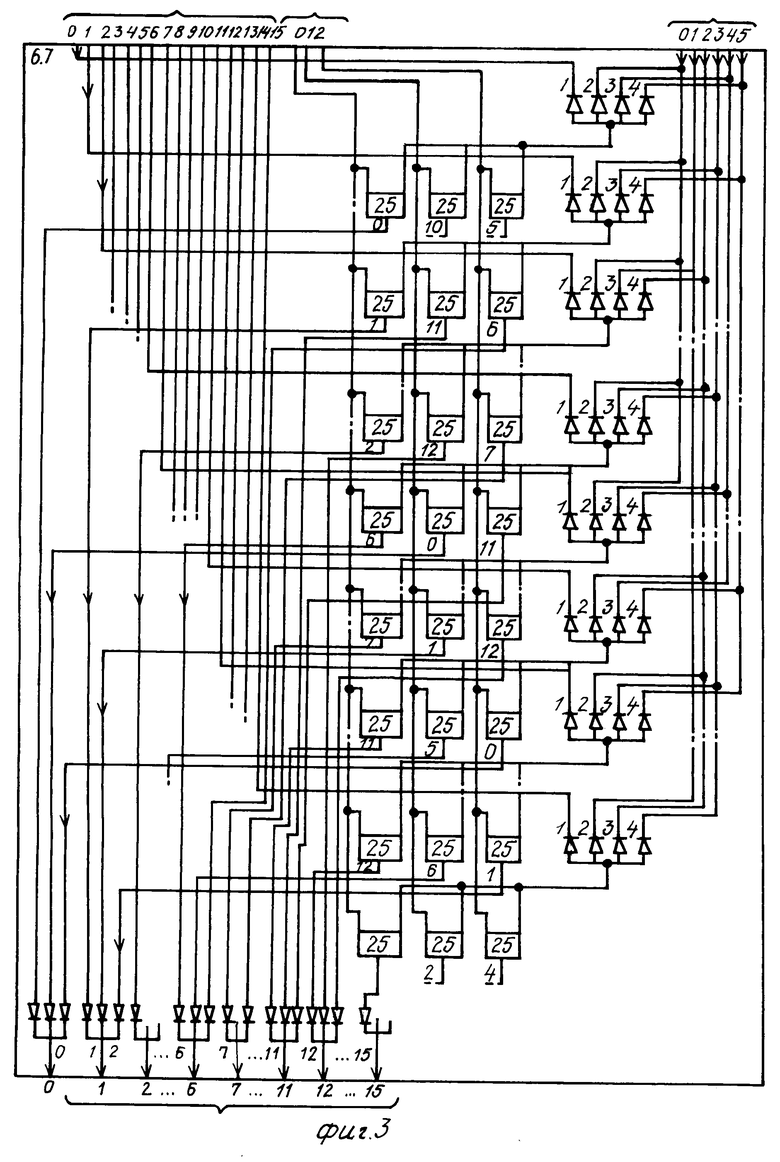

На фиг.3 показана функциональная схема дешифраторов 6,7 применительно к случаю P = 16 и l = 6. При этом дешифраторы 6 и 7 представляют собой комбинационные схемы, каждая из которых включает 3˙p двухвходовых элементов И. Кроме того, дешифраторы 6 и 7 включают P элементов И на четыре входа каждый (представлены на схеме для примера на диодных сборках) и P элементов ИЛИ на три входа каждый. Первый вход каждого из элементов И на четыре входа подключен к тому входу первой группы входов дешифратора 6 (7), номер которого совпадает с порядковым номером элемента. Набор кодов, в соответствии с которым реализована коммутация второго, третьего и четвертого входов четырехвходовых элементов И к входам третьей группы входов дешифратора 6 (7), приведен в таблице.

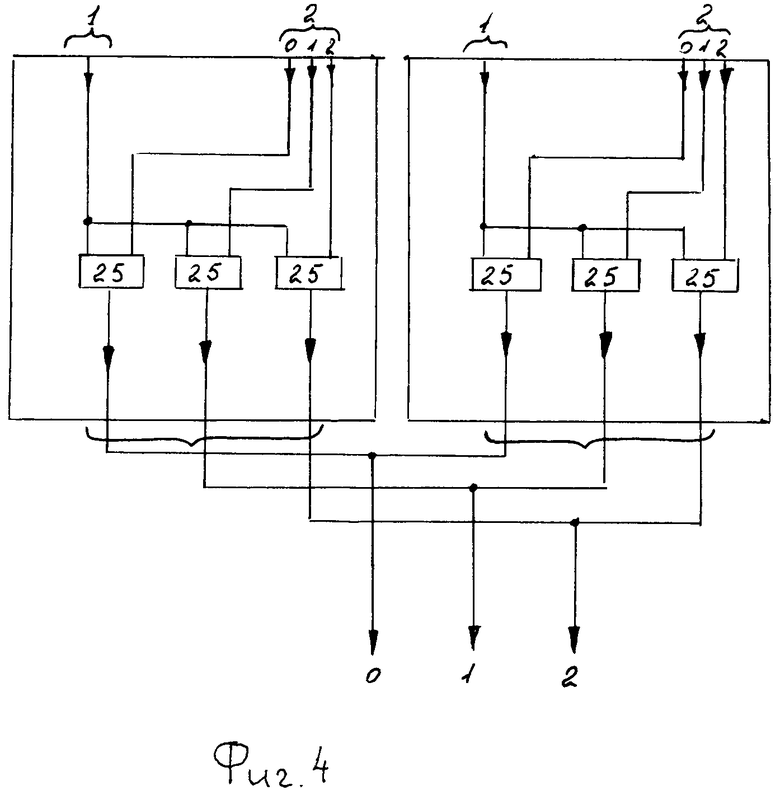

Блоки 8 и 9 (фиг.4) представляют собой два коммутатора, одноименные входы которых объединены проводной ИЛИ.

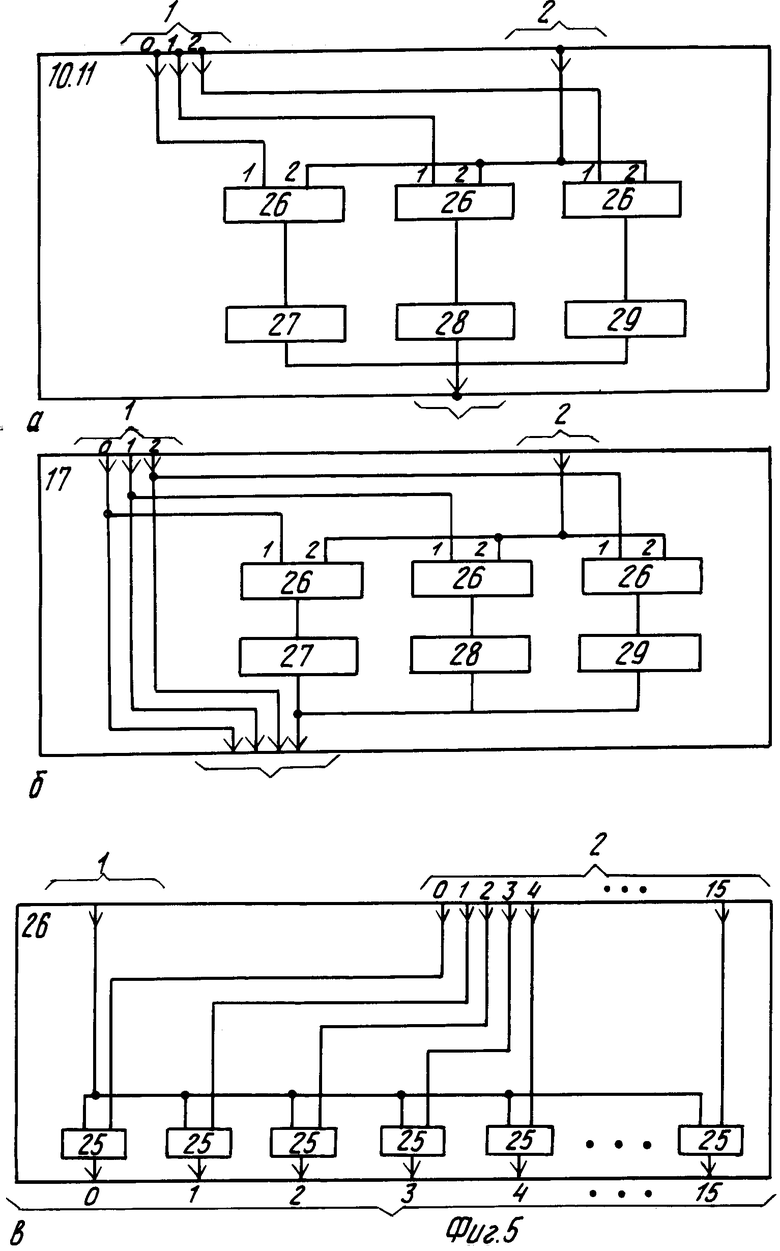

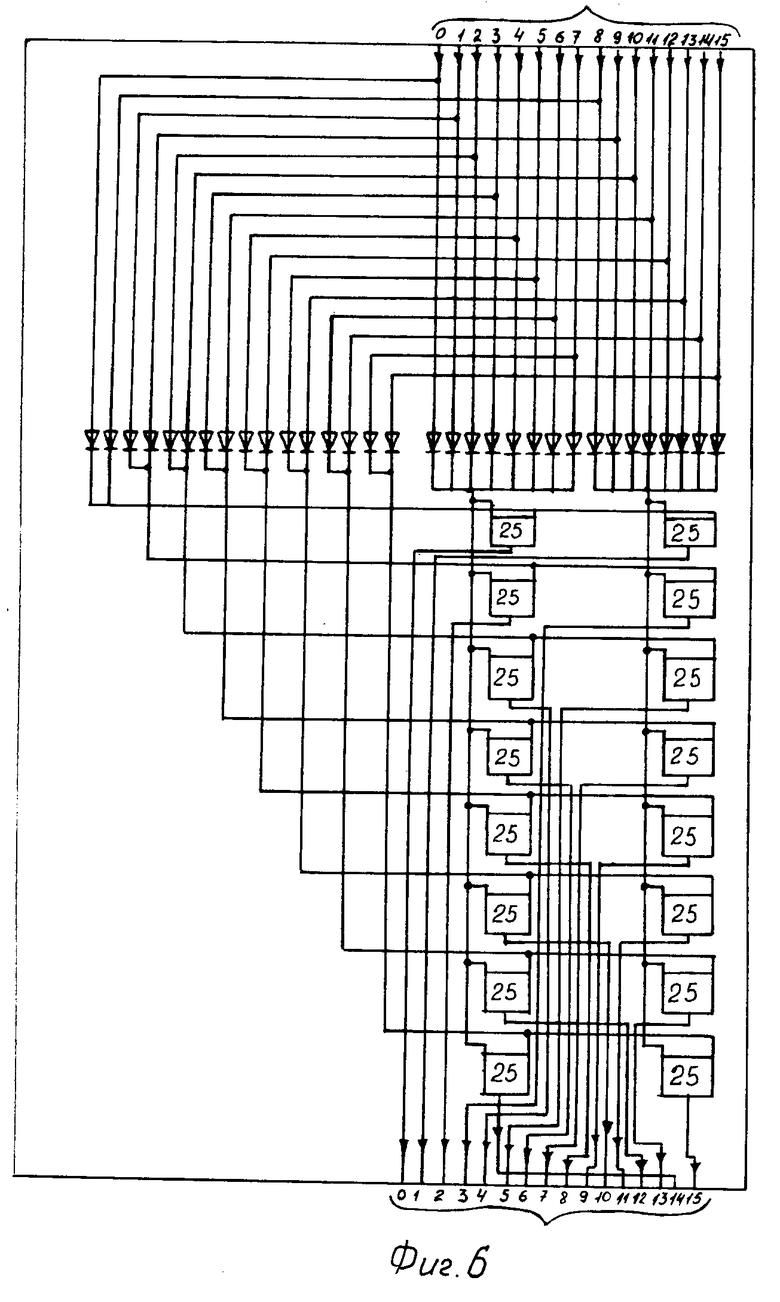

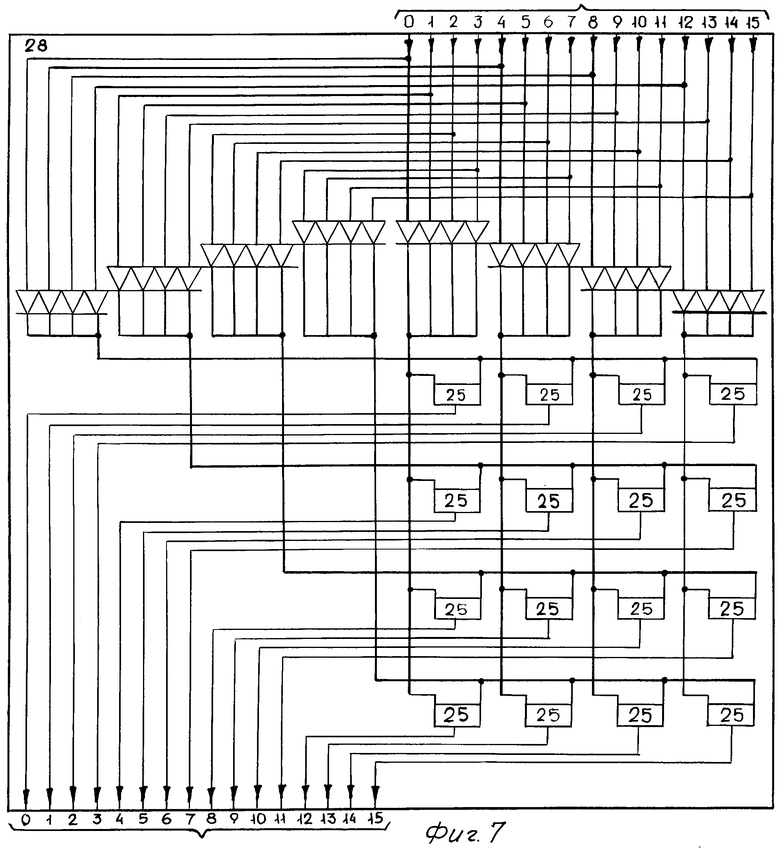

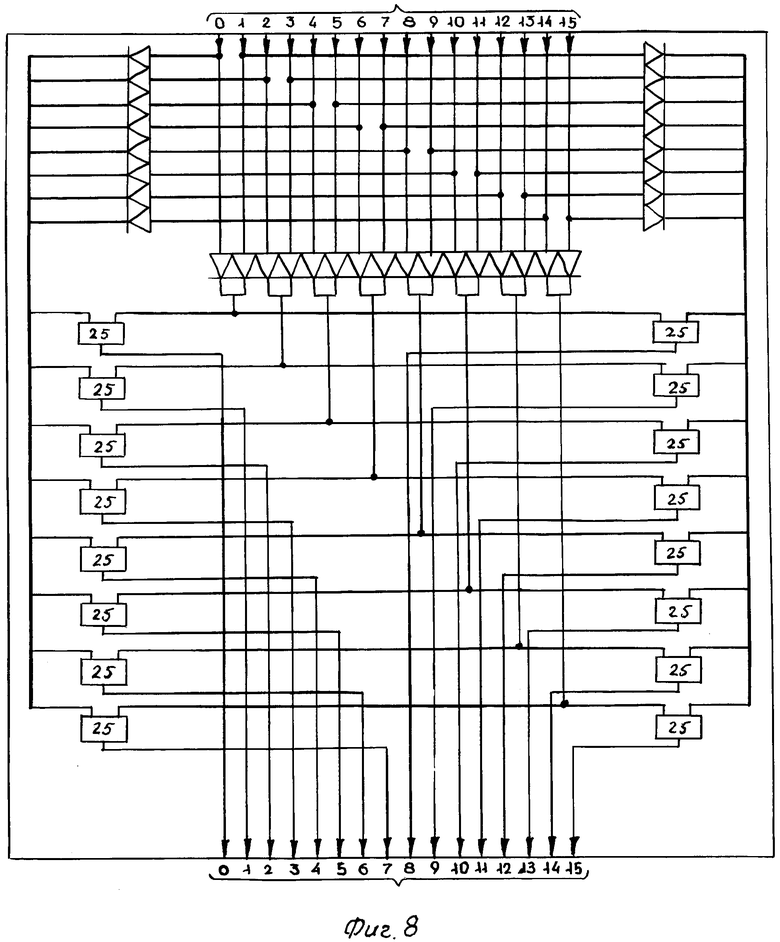

Функциональные схемы блоков 10,11 и 17 представлены на фиг.5а,б и содержат три группы 26 коммутаторов, каждая из которых (фиг.5в) включает P двухвходовых элементов И 25, а также три комбинационные схемы - блоки 27,28 и 29, функциональные схемы которых приведены соответственно на фиг.6,7 и 8.

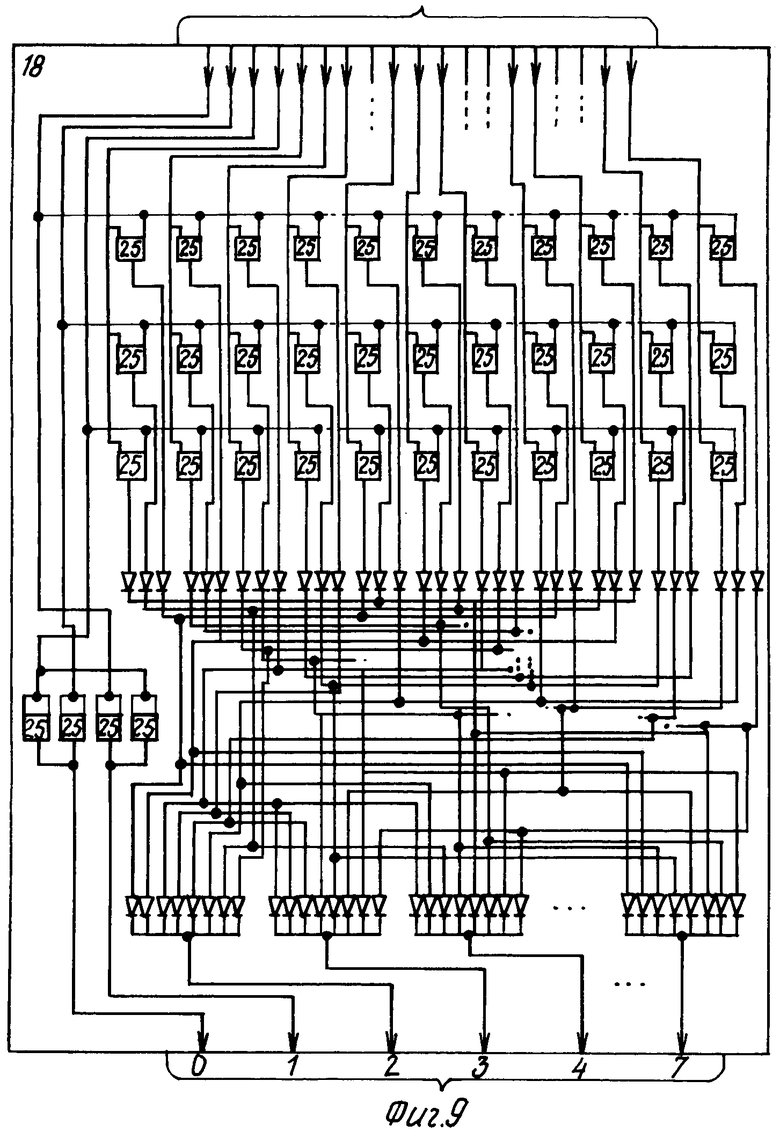

Шифратор 18 (фиг. 9) включает четыре группы коммутаторов. Три из них включают по одиннадцать двухвходовых элементов И 25, выходы которых объединены между собой посредством элементов ИЛИ (шесть элементов ИЛИ по восемь входов в каждом, диодная сборка). Четвертая группа коммутаторов включает четыре двухвходовых элемента И 25.

Устройство работает следующим образом.

Ключ, представляющий собой последовательную запись шестнадцати шестиразрядных двоичных кодов (в рассматриваемом примере реализации кодов, приведенных в таблице), от входа 21 устройства записывается в регистр 1. Операнды (два восьмиразрядных двоичных кода ) от входов 22 и 23 устройства записываются соответственно в регистры 2 и 3. Информация двух наиболее значимых операндов от регистров 2 и 3 по выходным шинам с порядковыми номерами 0 и 1 поступает на входы дешифраторов 4 и 5 соответственно. Наличие сигнала на выходе с номером 0,1 или 2 каждого из них соответствует информации о том, что поступивший операнд закодирован путем сдвига P-го числа при его пространственном представлении (предусматривающем наличие позиций и одного цифрового сигнала, причем значение цифры соответствует номеру позиции, на которой цифровой сигнал в данный момент находится) на 1,2 или 3 эквивалентных двоичных разряда влево (3,2 или 1 эквивалентный двоичный разряд вправо). С выходов регистра 2(3) и дешифратора 4(5) двоичный код исходного числа, а также информация о сдвиге его пространственного представления на группу эквивалентных двоичных разрядов поступают на второй и третий входы дешифратора 6(7). На первый вход дешифратора 6(7) подается ключ - последовательность двоичных кодов, соответствующих P возможным вариантам исходной цифры, поступающей от входа 22(23) устройства.

На вторые входы блоков 8 и 9 поступают сигналы, соответствующие одному из трех возможных вариантов преобразования исходных P-х цифр при их пространственном представлении.

Одновременно на первый вход блока 8 или 9 поступает управляющий сигнал соответственно Y1 или Y2 (от входа 19 или 20 устройства). В соответствии с управляющим сигналом в одном из этих блоков формируется признак необходимого преобразования результата вычислений в процессе его криптографического закрытия.

Сигналы, предполагающие один из возможных вариантов преобразования исходных P-цифр с выходов дешифраторов 4 и 5, поступают на первые входы блоков 10 и 11 соответственно. На вторые входы блоков 10 и 11 с выходов дешифраторов 6 и 7 исходная информация поступает не в виде двоичных кодов, а в виде p-х цифр с использованием их пространственного представления. В результате обратного преобразования на выходах блоков 10 и 11 появляются две шестнадцатиричные цифры операндов.

Процесс преобразования исходных цифр в блоках 12,...,16 идентичен процессу преобразования операндов в блоках 1,...,5 устройства-прототипа.

Результат преобразования исходных чисел с выхода матрицы 16 поступает на второй вход блока 17, на первый вход которого поступает управляющий сигнал с выхода блока 8 или 9. Этот сигнал определяет действия, связанные со сдвигом p-й цифры результата на эквивалентное число двоичных разрядов.

С выхода блока 17 результат сдвига и информация о числе эквивалентных двоичных разрядов, на которое сдвиг выполнен, поступают на вход шифратора 18, в котором достигается их замена восьмиразрядным двоичным кодом.

Таким образом, введение регистра ключа, первого и второго регистров исходных чисел, первого и второго дешифраторов кодов сдвига, первого и второго дешифраторов исходных чисел, первого и второго блоков признака сдвига результата, первого и второго блоков сдвига исходных чисел, блока сдвига результата и шифратора результата позволяет увеличить функциональные возможности предложенного вычислительного устройства за счет добавления функции криптографического преобразования передаваемой информации.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1991 |

|

RU2030792C1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2047896C1 |

| Матричный сумматор-умножитель | 1978 |

|

SU767759A1 |

| Вычислительное устройство | 1981 |

|

SU1018113A1 |

| Матричное вычислительное устройство | 1975 |

|

SU555400A1 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU981996A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Микропроцессор | 1983 |

|

SU1141419A1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ | 2011 |

|

RU2445690C2 |

| Устройство для сложения и вычитания чисел по модулю Р | 1986 |

|

SU1388850A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении арифметических устройств ЦВМ, работающих в системах счисления с большими основаниями. Целью изобретения является расширение функциональных возможностей за счет добавления функции криптографического преобразования передаваемой информации. Цель достигается тем, что вычислительное устройство, содержащее первую и вторую группы элементов ИЛИ, первую, вторую и третью матрицы двухвходовых элементов И, причем первый и второй входы первой матрицы двухвходовых элементов И подключены соответственно к первому выходу второй группы элементов ИЛИ и второму выходу первой группы элементов ИЛИ, а первый и второй входы второй матрицы двухвходовых элементов И подключены соответственно к первому выходу группы, элементов ИЛИ и второму выходу группы элементов ИЛИ, первый и второй входы третьей матрицы двухвходовых элементов И подключены к выходам соответственно к первой и второй матрицам двухвходовых элементов И, содержит регистр ключа, первый и второй регистры исходных чисел, первый и второй дешифраторы кодов сдвига, первый и второй дешифраторы кодов сдвига, первый и второй дешифраторы исходных чисел, первый и второй блоки признака сдвига результата, первый и второй блоки сдвига исходных чисел, блок сдвига результата, причем первые входы первого и второго блоков признака сдвига, входы регистра ключа, первого и второго регистров исходных чисел подключены соответственно к первому, второму, третьему, четвертому и пятому входам устройства, входы первого и второго дешифраторов кодов сдвига подключены к выходам первого и второго регистров исходных чисел, первые входы первого и второго дешифраторов исходных чисел подключены к выходу регистра ключа, вторые (третьи) входы первого и второго дешифраторов исходных чисел подключены соответственно к выходам первого и второго дешифраторов кодов сдвига (соответственно выходам первого и второго дешифраторов кодов сдвига (соответственно выходам первого и второго регистров исходных чисел), вторые входы первого и второго блоков признака сдвига результата (первые входы первого и второго блоков сдвига исходных чисел) подключены соответственно к выходам первого и второго дешифраторов кодов сдвига, вторые входы первого и второго блоков сдвига исходных чисел подключены соответственно к выходам первого и второго дешифраторов исходных чисел, входы первой и второй групп элементов ИЛИ - соответственно к выходам первого и второго блоков сдвига исходных чисел, первый вход блока сдвига результата подключен к выходам первого и второго блоков признака сдвига результата, второй вход блока сдвига результата - к выходу третьей матрицы двухвходовых элементов И, вход дешифратора результата подключен к выходу блока сдвига результата. 1 табл., 9 ил.

ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО, содержащее первую и вторую группы элементов ИЛИ, первую, вторую и третью матрицы двухвходовых элементов И, причем первый и второй входы первой матрицы двухвходовых элементов И подключены соответственно к первому выходу второй группы элементов ИЛИ и второму выходу первой группы элементов ИЛИ, а первый и второй входы второй матрицы двухвходовых элементов И подключены соответственно к первому выходу первой группы элементов ИЛИ и второму выходу второй группы элементов ИЛИ, первый и второй входы третьей матрицы двухвходовых элементов И подключены к выходам соответственно первой и второй матриц двухвходовых элементов И, отличающееся тем, что оно дополнительно содержит регистр ключа, первый и второй регистры исходных чисел, первый и второй дешифраторы кодов сдвига, первый и второй дешифраторы исходных чисел, первый и второй блоки признака сдвига результата, первый и второй блоки сдвига исходных чисел, блок сдвига результата и шифратор результата, причем первые входы первого и второго блоков признака сдвига, входы регистра ключа, первого и второго регистров исходных чисел подключены соответственно к первому, второму, третьему, четвертому и пятому входам устройства, входы первого и второго дешифраторов кодов сдвига подключены к выходам первого и второго регистров исходных чисел, первые входы первого и второго дешифраторов исходных чисел подключены к выходу регистра ключа, вторые входы первого и второго дешифраторов исходных чисел подключены соответственно к выходам первого и второго дешифраторов кодов сдвига, а третьи входы - соответственно к выходам первого и второго регистров исходных чисел, вторые входы первого и второго блоков признака сдвига результата и первые входы первого и второго блоков сдвига исходных чисел подключены соответственно к выходам первого и второго дешифраторов кодов сдвига, вторые входы первого и второго блоков сдвига исходных чисел подключены соответственно к выходам первого и второго дешифраторов исходных чисел, входы первой и второй групп элементов ИЛИ - соответственно к выходам первого и второго блоков сдвига исходных чисел, первый вход блока сдвига результата подключен к выходам первого и второго блоков признака сдвига результата, второй вход блока сдвига результата - к выходу третьей матрицы двухвходовых элементов И, вход шифратора результата подключен к выходу блока сдвига результата.

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| СУММАТОР ПО МОДУЛЮ | 0 |

|

SU352276A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Контрольный висячий замок в разъемном футляре | 1922 |

|

SU1972A1 |

Авторы

Даты

1994-06-30—Публикация

1992-01-16—Подача